ssd1306中文手册

- 格式:doc

- 大小:2.29 MB

- 文档页数:26

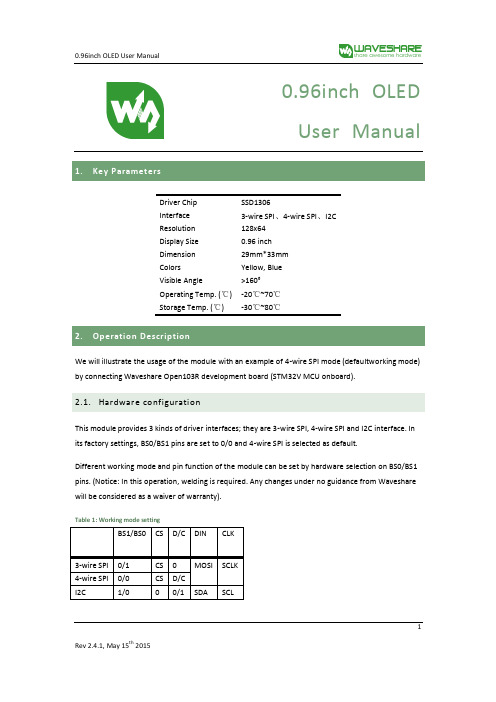

0.96inch OLEDUser Manual 1.Driver Chip SSD1306Interface 3-wire SPI、4-wire SPI、I2CResolution 128x64Display Size 0.96 inchDimension 29mm*33mmColors Yellow, BlueVisible Angle >160°Operating Temp. (℃) -20℃~70℃Storage Temp. (℃) -30℃~80℃2.We will illustrate the usage of the module with an example of 4-wire SPI mode (defaultworking mode) by connecting Waveshare Open103R development board (STM32V MCU onboard).2.1.Hardware configurationThis module provides 3 kinds of driver interfaces; they are 3-wire SPI, 4-wire SPI and I2C interface. In its factory settings, BS0/BS1 pins are set to 0/0 and 4-wire SPI is selected as default.Different working mode and pin function of the module can be set by hardware selection on BS0/BS1 pins. (Notice: In this operation, welding is required. Any changes under no guidance from Waveshare will be considered as a waiver of warranty).Table 1: Working mode setting122.2.Software configurationOpen the project file .\IDE\ OLED.uvproj in Keil, navigate to the following text, delete the ‘//’ (Double slash) before #define INTERFACE_4WIRE_SPI After compiling successfully, download the project to Open103R development board. Note: You should delete the ‘//’ (Double slash) corresponding to the mode selection2.3. Hardware connectionsConnect module to the SPI2 interface of Open103R development board, power up. OLED displays information as Figure 1 shows.Figure 1: OLED information display3. 4-wire SPI and I2C interfaces of SSD1306 OLEDThis module provides 3 kinds of driver interfaces. We introduce 4-wire SPI and I2C interfaceshere. You can read Chap. 8.1 from SSD1306-Revision_1.1.pdf for more details.The 4-wire serial interface consists of serial clock: SCLK, serial data: SDIN, D/C#, CS#. In 4-wire SPI mode,D0 acts as SCLK, D1 acts as SDIN. For the unused data pins, D2 should be left open. The pins from D3 to D7, E and R/W# (WR#)# can be connected to an external ground.Table 2: 4-wire SPI Control pins of 4-wire Serial interfaceNote(1) H stands for HIGH in signal(2) L stands for LOW in signalSDIN is shifted into an 8-bit shift register on every rising edge of SCLK in the order of D7, D6 0D/C# is sampled on every eighth clock and the data byte in the shift register is written to the Graphic Display Data RAM (GDDRAM) or command register in the same clock.Under serial mode, only write operations are allowed.Figure 2: Write procedure in 4-wire Serial interface modeThe I2C-bus interface gives access to write data and command into the device. Please referto Figure 2 for the write mode of I2C-bus in chronological order.a)Slave address bit (SA0)SSD1306 has to recognize the slave address before transmitting or receiving any information by the I2C-bus. The device will respond to the slave address following by the slave address bit (“SA0”bit) and the read/write select bit (“R/W#” bit) with the following byte format,b7 b6 b5 b4 b6 b2 b1 b00 1 1 1 1 0 SA0 R/W#“SA0” bit provides an extension bit for the slave address. Either “0111100” or3“0111101”, can be selected as the slave address of SSD1306. D/C# pin acts as SA0 for slave address selection. “R/W#” bit is used to determine the operation mode of the I2C-bus interface.R/W#=1, it is in read mode. R/W#=0, it is in write mode.b)I2C-bus data signal (SDA)SDA acts as a communication channel between the transmitter and the receiver. The data and the acknowledgement are sent through the SDA.It should be noticed that the ITO track resistance and the pulled-up resistance at “SDA” pinbecomes a voltage potential divider. As a result, the acknowledgement would not be possible to attain a valid logic 0 level in “SDA””SDAIN” and “SDAOUT” are tied together and serve as SDA. The “SDAIN” pin must be connected to act as SDA. The “SDAOUT” pin may be disconnected. When “SDAOUT” pin is disconnected, the acknowledgement signal will be ignored in the I2C-bus.c)I2C-bus clock signal (SCL)The transmission of information in the I2C-bus is following a clock signal, SCL. Each transmission of data bit is taken place during a single clock period of SCL.Table 3. I2C I2C-bus data format1)The slave address is following the start condition for recognition use. For the SSD1306, the slaveaddress is either “b0111100” or “b0111101” by changing the SA0 to LOW or HIGH (D/C pin acts as SA0).2)The write mode is established by setting the R/W# bit to logic “0”43)An acknowledgement signal will be generated after receiving one byte of data, including theslave address and the R/W# bit.4)After the transmission of the slave address, either the control byte or the data byte may be sentacross the SDA. A control byte mainly consists of Co and D/C# bits following by six “0” ‘s.a)If the Co bit is set as logic “0”, the transmission of the following information will containdata bytes only.b)The D/C# bit determines the next data byte is acted as a command or a data. If the D/C# bitis set to logic “0”, it defines the following data byte as a command. If the D/C# bit is set tologic “1”, it defines the following data byte as a data which will be stored at the GDDRAM.The GDDRAM column address pointer will be increased by one automatically after eachdata write.5)Acknowledge bit will be generated after receiving each control byte or data byte.5。

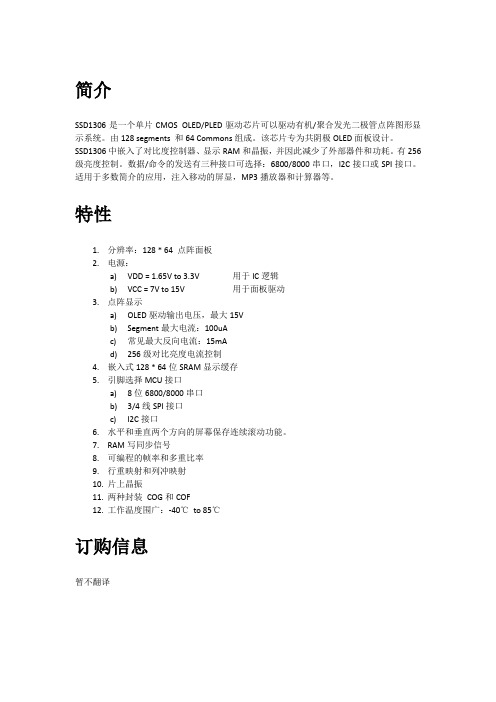

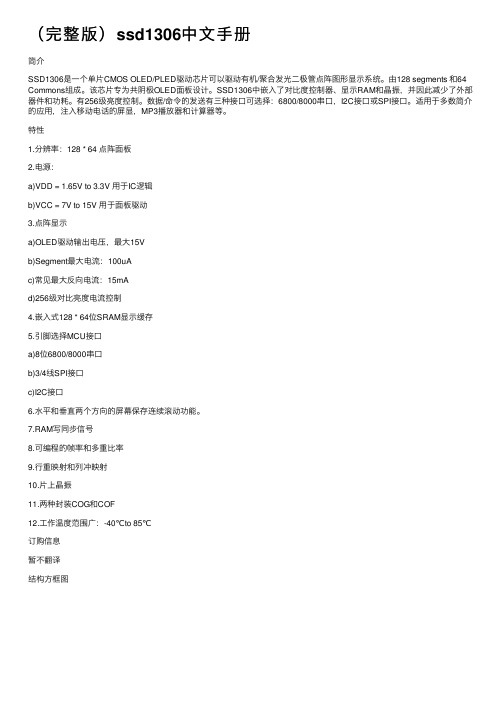

简介SSD1306是一个单片CMOS OLED/PLED驱动芯片可以驱动有机/聚合发光二极管点阵图形显示系统。

由128 segments 和64 Commons组成。

该芯片专为共阴极OLED面板设计。

SSD1306中嵌入了对比度控制器、显示RAM和晶振,并因此减少了外部器件和功耗。

有256级亮度控制。

数据/命令的发送有三种接口可选择:6800/8000串口,I2C接口或SPI接口。

适用于多数简介的应用,注入移动的屏显,MP3播放器和计算器等。

特性1.分辨率:128 * 64 点阵面板2.电源:a)VDD = 1.65V to 3.3V 用于IC逻辑b)VCC = 7V to 15V 用于面板驱动3.点阵显示a)OLED驱动输出电压,最大15Vb)Segment最大电流:100uAc)常见最大反向电流:15mAd)256级对比亮度电流控制4.嵌入式128 * 64位SRAM显示缓存5.引脚选择MCU接口a)8位6800/8000串口b)3/4线SPI接口c)I2C接口6.水平和垂直两个方向的屏幕保存连续滚动功能。

7.RAM写同步信号8.可编程的帧率和多重比率9.行重映射和列冲映射10.片上晶振11.两种封装COG和COF12.工作温度围广:-40℃to 85℃订购信息暂不翻译结构方框图功能块描述MCU接口选择SSD1306MCU接口由8个数据引脚和5个控制引脚组成。

引脚分配由不同的接口选择决定,详情如下表。

不同的MCU模块可以通过BS[2:0]引脚的硬件选择设置。

MCU 并口6800系列接口不翻译MCU 并口8080系列接口不翻译MCU串口(4-wire SPI)不翻译MCU串口(3-wire SPI)不翻译MCU I2C 接口I2C通讯接口由从机地址为SA0,I2C总线数据信号(SDAout/D2输出和SDAin/D1输入)和I2C总线时钟信号SCL(D0)组成。

数据和时钟信号线都必须接上上拉电阻。

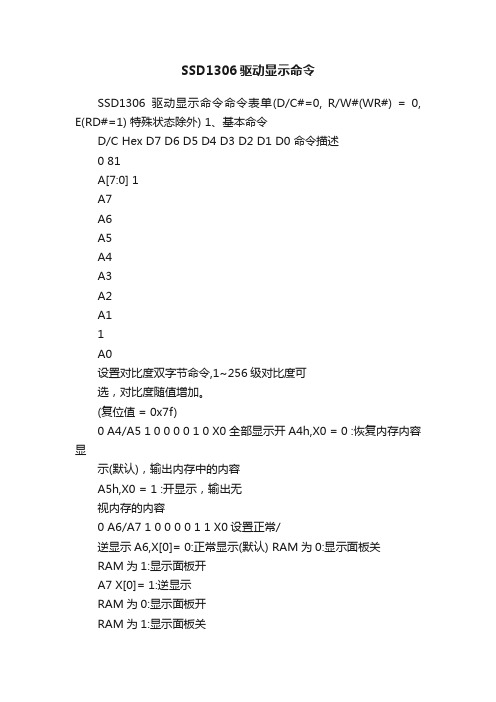

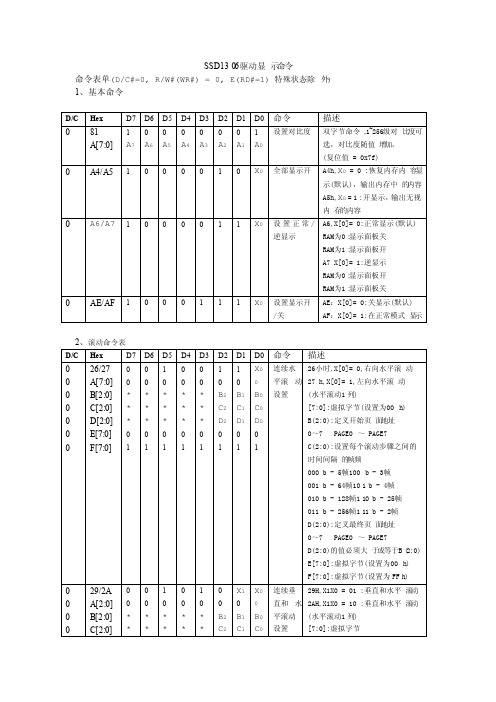

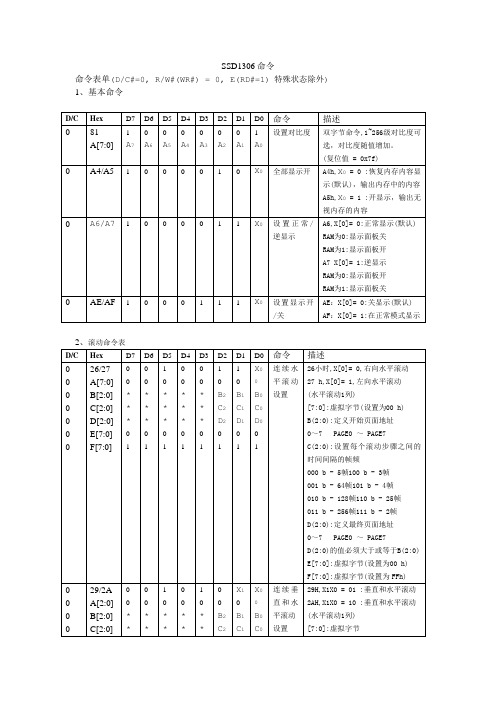

SSD1306驱动显示命令SSD1306驱动显示命令命令表单(D/C#=0, R/W#(WR#) = 0, E(RD#=1) 特殊状态除外) 1、基本命令D/C Hex D7 D6 D5 D4 D3 D2 D1 D0 命令描述0 81A[7:0] 1A7A6A5A4A3A2A11A0设置对比度双字节命令,1~256级对比度可选,对比度随值增加。

(复位值 = 0x7f)0 A4/A5 1 0 0 0 0 1 0 X0全部显示开A4h,X0 = 0 :恢复内存内容显示(默认),输出内存中的内容A5h,X0 = 1 :开显示,输出无视内存的内容0 A6/A7 1 0 0 0 0 1 1 X0设置正常/逆显示A6,X[0]= 0:正常显示(默认) RAM为0:显示面板关RAM为1:显示面板开A7 X[0]= 1:逆显示RAM为0:显示面板开RAM为1:显示面板关0 AE/AF 1 0 0 0 1 1 1 X0设置显示开/关AE:X[0]= 0:关显示(默认) AF:X[0]= 1:在正常模式显示2、滚动命令表D/C Hex D7 D6 D5 D4 D3 D2 D1 D0 命令描述0 0 0 0 0 0 0 26/27A[7:0]B[2:0]C[2:0]D[2:0]E[7:0]F[7:0]***1***11***1***1***11B2C2D211B1C1D11X0B0C0D01连续水平滚动设置26小时,X[0]= 0,右向水平滚动27 h,X[0]= 1,左向水平滚动(水平滚动1列)[7:0]:虚拟字节(设置为00 h)B(2:0):定义开始页面地址0~7 PAGE0 ~ PAGE7C(2:0):设置每个滚动步骤之间的时间间隔的帧频000 b - 5帧100 b - 3帧001 b - 64帧101 b - 4帧010 b - 128帧110 b - 25帧011 b - 256帧111 b - 2帧D(2:0):定义最终页面地址0~7 PAGE0 ~ PAGE7D(2:0)的值必须大于或等于B(2:0) E[7:0]:虚拟字节(设置为00 h)F[7:0]:虚拟字节(设置为FFh)0 0 0 0 29/2AA[2:0]B[2:0]C[2:0]****1****1**B2C2X1B1C1X0B0C0连续垂直和水平滚动设置29H,X1X0 = 01 :垂直和水平滚动2AH,X1X0 = 10 :垂直和水平滚动(水平滚动1列)[7:0]:虚拟字节0 0 D[2:0]E[5:0]***E5*E4*E3D2E2D1E1D0E0B(2:0):定义开始页面地址0~7 PAGE0 ~ PAGE7C(2:0):设置每个滚动步骤之间的时间间隔的帧频000 b - 5帧100 b - 3帧001 b - 64帧101 b - 4帧010 b - 128帧110 b - 25帧011 b - 256帧111 b - 2帧D(2:0):定义最终页面地址0~7 PAGE0 ~ PAGE7D(2:0)的值必须大于或等于B(2:0) E[5:0]:垂直滚动偏移量例如E[5:0]= 01 h指抵消= 1行E(5:0)= 3跳频是指抵消= 63行请注意(1)没有可用连续垂直滚动。

精品文档简介SSD1306是一个单片CMOS OLED/PLED驱动芯片可以驱动有机/聚合发光二极管点阵图形显示系统。

由128 segments 和64 Commons组成。

该芯片专为共阴极OLED面板设计。

SSD1306中嵌入了对比度控制器、显示RAM和晶振,并因此减少了外部器件和功耗。

有256级亮度控制。

数据/命令的发送有三种接口可选择:6800/8000串口,I2C接口或SPI接口。

适用于多数简介的应用,注入移动电话的屏显,MP3播放器和计算器等。

特性1.分辨率:128 * 64 点阵面板2.电源:a)VDD = 1.65V to 3.3V 用于IC逻辑b)VCC = 7V to 15V 用于面板驱动3.点阵显示a)OLED驱动输出电压,最大15Vb)Segment最大电流:100uAc)常见最大反向电流:15mAd)256级对比亮度电流控制4.嵌入式128 * 64位SRAM显示缓存5.引脚选择MCU接口a)8位6800/8000串口b)3/4线SPI接口c)I2C接口6.水平和垂直两个方向的屏幕保存连续滚动功能。

7.RAM写同步信号8.可编程的帧率和多重比率9.行重映射和列冲映射10.片上晶振11.两种封装COG和COF12.工作温度范围广:-40℃to 85℃订购信息暂不翻译精品文档.精品文档结构方框图功能块描述接口选择MCU个控制引脚组成。

引脚分配由不同的接口选择决定,个数据引脚和5SSD1306MCU接口由8 BS[2:0]引脚的硬件选择设置。

模块可以通过详情如下表。

不同的MCU精品文档.精品文档接控制信ER/W#CS#D2D1D0D/C#RES#D4D3RES#RD#CS#WR#D/C#RES#CS#ED/C#R/W#RES#SDINSCLKCS#Tie LOWTieNCLOWRES#D/C#Tie LOWCS#NCSDINSCLKRES#Tie LOWSDAoutSClSDAinSA0MCU 并口6800系列接口不翻译MCU 并口8080系列接口不翻译MCU串口(4-wire SPI)不翻译MCU串口(3-wire SPI)不翻译MCU I2C 接口I2C通讯接口由从机地址为SA0,I2C总线数据信号(SDAout/D2输出和SDAin/D1输入)和I2C总线时钟信号SCL(D0)组成。

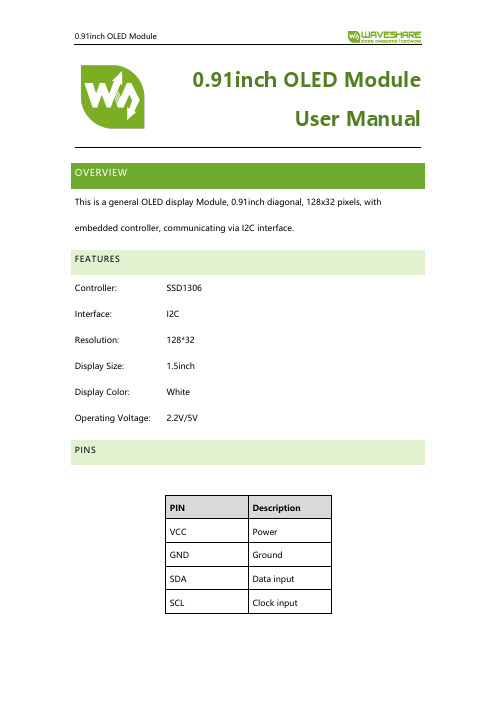

0.91inch OLED ModuleUser ManualOVERVIEWThis is a general OLED display Module, 0.91inch diagonal, 128x32 pixels, with embedded controller, communicating via I2C interface.FEATURESController: SSD1306Interface: I2CResolution: 128*32Display Size: 1.5inchDisplay Color: WhiteOperating Voltage: 2.2V/5VPINSPIN DescriptionVCC PowerGND GroundSDA Data inputSCL Clock inputWORKING PROTOCOLSSD1306 is a controller for 128*64 OLED. This OLED has only 128*32 pixels, so it uses part of SSD1306’s buffer.In theory, the OLED supports 8-bit 8080, 8-bits 6800, 3-wires SPI, 4-wires SPI and I2C, however, to save IO resources and because of the small size of OLED, we only pinout I2C interface.I2C COMMUNICATIONWhen working, MCU will first send a byte that the first 7bits are address of slave device and 1 bit write/read bit, and wait for response.After received response from slave device, MCU will send a control byte, this byte defined the data following is command or data.Slave response again, if sending command, MCU will send the command which is one byte. If sending data, MCU will sending dataFor more details about I2C, please refer to Datasheet Page20 Figure 8-7We provide STM32, Arduino and Raspberry Pi demo code for this module. The demo code will release basic functions that: draw point, draw line, draw rectangle, draw circle.STM32 DEMO CODE1.Hardware configurationDevelopment board: XNUCLEO-F103RB2.Project files:Project is compiled in MDK-ARM v5, generated by STM32CubeMX../Src:Adafruit_SSD1306.cpp: Bottom interface of OLED, provide functions that OLED initialize, basic display pixels and configure;Adafruit_GFX.cpp: Application function of OLED, provide display, drawingfunctions.glcdfont.h: LCD font, provide English fonts which size 6*8 and 8*16 RASPBERRY PI CODE1.Hardware connection2.Enable I2Csudo raspi-configchoose Interfacing Options->I2C ->Yes3.Libraries installationAbout how to install I2C libraries, you can refer to Waveshare Wiki:https:///wiki/Libraries_Installation_for_RPiingCopy demo code which you can download from Wiki to Raspberry Pi. The demo code we described are all copied to /home/pia)BCM2835(1) Install bcm2835 libraries(2) use ls command to list the files:bin:./o filesFonts: Include five fonts filesObj: project files are saved here, include main.c, OLED_Driver.c,OLED_Config.c, OLED_GUI.c and their header files.mian.c: main functionOLED_Config.c: Hardware configuration, define pins and communication type OLED_Driver.c: Hardware (OLED) driver.OLED_GUI.c: Application functions, included functions that draw point, line, rectangle, display string, pictures and so on.Show_Pic.h: Pictures data which are used to display. You should convert your pictures to data. (description in net chapter)oled_0in91: executable files, generated by command makeTo run this code, you can execute the command: sudo ./oled_0in91b)WiringPi(1) Install WiringPi libraries(2) use ls command to list the files:The folders included are similar to BCM2835’s. The only differences are that: - WiringPi oprates by read/write the device files of Linux OS. and thebcm2835 is library function of Raspberry Pi’s CPU, it operates registersdirectly. Thus, if you have used bcm2835 libraries firstly, the usage of WiringPi code will be failed. In this case, you just need to reboot the system and try again.- Due to the first difference, they underlying configuration are different. In DEV_Config.c, use wiringpiPi and the corresponding wiringPiSPI to provideunderlay interfaces.To run the code, use the command: sudo ./oled_0in91c)Python(1) use ls command to list the files:(2) Here we used Adafruit librariesbefore run code, you need to install llibraries as below:sudo apt-get updatesudo apt-get install build-essential python-dev python-pipsudo pip install RPi.GPIOsudo apt-get install python-imaging python-smbus(3) Enter directory of python code, execute commands:sudo python Adafruit_Python_SSD1306/setup.py installsudo python stats.pyd)Auto-runTo make the code run automatically after booting, you can configure/etc/rc.local file:sudo vim /etc/rc.localAdd a statement in front of exit 0:sudo python /home/pi/0in91/python/stats.py &Note that if you put the code to different directory, you need to change thepath: /home/pi/ to the correct one. & is necessary at the end, otherwise, youmay cannot login to Raspberry Pi and need to re-burn image)ARDUINO CODE1.Hardware ConnectionDevelopment board: UNO PLUS2.Files Description:../oled:oled.ino: Project file of Arduino, double click to openProject directory:Adafruit_SSD1306.cpp: Bottom interfaces of OLED, includes OLED initialize, basic display and configuration functions.Adafruit_GFX.cpp:Application functions of OLEDAdafruit_SSD1306.h、Adafruit_GFX.h: Header filesglcdfont.h:LCD font, provide English fonts which size 6*8 and 8*163.RunningBefore running the code, you should copy the libraries files of this project to the libraries directory of IDE, which is under the installation directory of Arduino IDE.Note that you cannot put files directly to the libraries directory, you need to save them on a folder, for example 0in91_OLED_Module as below:Then, open olde.ino then download the codeUse software Image2Lcd to open picture (Monochrome picture) and configure: 输出数据类型(Data types):C语言数据(*.c)扫描方式(Scanning way):数据水平(data horizonal),字节垂直(byte vertical) 输出灰度(gray scale):单色(monochrome)最大宽度和高度(height and width):128 32 (Resolution of OLED)And then check the option that color invert.。

SSD1306驱动显示命令命令表单(D/C#=0, R/W#(WR#) = 0, E(RD#=1) 特殊状态除外) 1、基本命令D/C Hex D7 D6 D5 D4 D3 D2 D1 D0 命令描述0 81A[7:0] 1A7A6A5A4A3A2A11A0设置对比度双字节命令,1~256级对比度可选,对比度随值增加。

(复位值 = 0x7f)0 A4/A5 1 0 0 0 0 1 0 X0全部显示开A4h,X0 = 0 :恢复内存内容显示(默认),输出内存中的内容A5h,X0= 1 :开显示,输出无视内存的内容0 A6/A7 1 0 0 0 0 1 1 X0设置正常/逆显示A6,X[0]= 0:正常显示(默认) RAM为0:显示面板关RAM为1:显示面板开A7 X[0]= 1:逆显示RAM为0:显示面板开RAM为1:显示面板关0 AE/AF 1 0 0 0 1 1 1 X0设置显示开/关AE:X[0]= 0:关显示(默认) AF:X[0]= 1:在正常模式显示2、滚动命令表D/C Hex D7 D6 D5 D4 D3 D2 D1 D0 命令描述0 0 0 0 0 0 0 26/27A[7:0]B[2:0]C[2:0]D[2:0]E[7:0]F[7:0]***1***11***1***1***11B2C2D211B1C1D11X0B0C0D01连续水平滚动设置26小时,X[0]= 0,右向水平滚动27 h,X[0]= 1,左向水平滚动(水平滚动1列)[7:0]:虚拟字节(设置为00 h)B(2:0):定义开始页面地址0~7 PAGE0~ PAGE7C(2:0):设置每个滚动步骤之间的时间间隔的帧频000 b - 5帧100 b - 3帧001 b - 64帧101 b - 4帧010 b - 128帧110 b - 25帧011 b - 256帧111 b - 2帧D(2:0):定义最终页面地址0~7 PAGE0~ PAGE7D(2:0)的值必须大于或等于B(2:0)E[7:0]:虚拟字节(设置为00 h)F[7:0]:虚拟字节(设置为FFh)0 0 0 0 29/2AA[2:0]B[2:0]C[2:0]****1****1**B2C2X1B1C1X0B0C0连续垂直和水平滚动设置29H,X1X0 = 01 :垂直和水平滚动2AH,X1X0 = 10 :垂直和水平滚动(水平滚动1列)[7:0]:虚拟字节0 0 D[2:0]E[5:0]***E5*E4*E3D2E2D1E1D0E0B(2:0):定义开始页面地址0~7 PAGE0~ PAGE7C(2:0):设置每个滚动步骤之间的时间间隔的帧频000 b - 5帧100 b - 3帧001 b - 64帧101 b - 4帧010 b - 128帧110 b - 25帧011 b - 256帧111 b - 2帧D(2:0):定义最终页面地址0~7 PAGE0~ PAGE7D(2:0)的值必须大于或等于B(2:0)E[5:0]:垂直滚动偏移量例如E[5:0]= 01 h指抵消= 1行E(5:0)= 3跳频是指抵消= 63行请注意(1)没有可用连续垂直滚动。

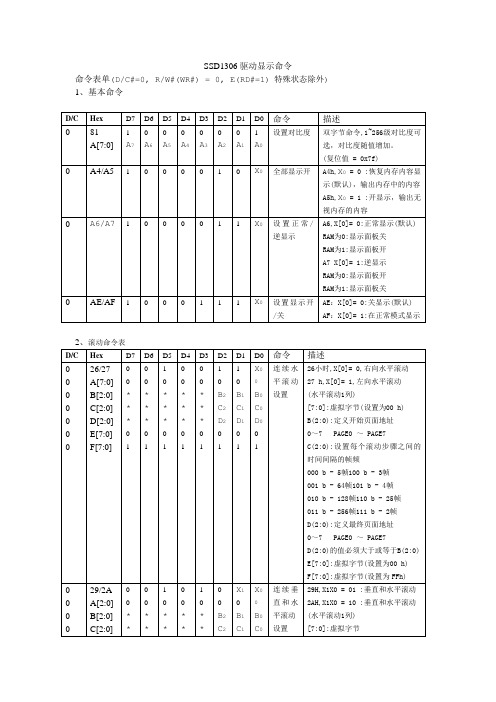

SSD1306命令命令表单(D/C#=0, R/W#(WR#) = 0, E(RD#=1) 特殊状态除外) 1、基本命令D/C Hex D7 D6 D5 D4 D3 D2 D1 D0 命令描述0 81A[7:0] 1A7A6A5A4A3A2A11A0设置对比度双字节命令,1~256级对比度可选,对比度随值增加。

(复位值 = 0x7f)0 A4/A5 1 0 0 0 0 1 0 X0全部显示开A4h,X0 = 0 :恢复内存内容显示(默认),输出内存中的内容A5h,X0 = 1 :开显示,输出无视内存的内容0 A6/A7 1 0 0 0 0 1 1 X0设置正常/逆显示A6,X[0]= 0:正常显示(默认) RAM为0:显示面板关RAM为1:显示面板开A7 X[0]= 1:逆显示RAM为0:显示面板开RAM为1:显示面板关0 AE/AF 1 0 0 0 1 1 1 X0设置显示开/关AE:X[0]= 0:关显示(默认) AF:X[0]= 1:在正常模式显示2、滚动命令表D/C Hex D7 D6 D5 D4 D3 D2 D1 D0 命令描述0 0 0 0 0 0 0 26/27A[7:0]B[2:0]C[2:0]D[2:0]E[7:0]F[7:0]***1***11***1***1***11B2C2D211B1C1D11X0B0C0D01连续水平滚动设置26小时,X[0]= 0,右向水平滚动27 h,X[0]= 1,左向水平滚动(水平滚动1列)[7:0]:虚拟字节(设置为00 h)B(2:0):定义开始页面地址0~7 PAGE0 ~ PAGE7C(2:0):设置每个滚动步骤之间的时间间隔的帧频000 b - 5帧100 b - 3帧001 b - 64帧101 b - 4帧010 b - 128帧110 b - 25帧011 b - 256帧111 b - 2帧D(2:0):定义最终页面地址0~7 PAGE0 ~ PAGE7D(2:0)的值必须大于或等于B(2:0)E[7:0]:虚拟字节(设置为00 h)F[7:0]:虚拟字节(设置为FFh)0 0 0 0 29/2AA[2:0]B[2:0]C[2:0]****1****1**B2C2X1B1C1X0B0C0连续垂直和水平滚动设置29H,X1X0 = 01 :垂直和水平滚动2AH,X1X0 = 10 :垂直和水平滚动(水平滚动1列)[7:0]:虚拟字节0 0 D[2:0]E[5:0]***E5*E4*E3D2E2D1E1D0E0B(2:0):定义开始页面地址0~7 PAGE0 ~ PAGE7C(2:0):设置每个滚动步骤之间的时间间隔的帧频000 b - 5帧100 b - 3帧001 b - 64帧101 b - 4帧010 b - 128帧110 b - 25帧011 b - 256帧111 b - 2帧D(2:0):定义最终页面地址0~7 PAGE0 ~ PAGE7D(2:0)的值必须大于或等于B(2:0)E[5:0]:垂直滚动偏移量例如E[5:0]= 01 h指抵消= 1行E(5:0)= 3跳频是指抵消= 63行请注意(1)没有可用连续垂直滚动。

(完整版)ssd1306中⽂⼿册简介SSD1306是⼀个单⽚CMOS OLED/PLED驱动芯⽚可以驱动有机/聚合发光⼆极管点阵图形显⽰系统。

由128 segments 和64 Commons组成。

该芯⽚专为共阴极OLED⾯板设计。

SSD1306中嵌⼊了对⽐度控制器、显⽰RAM和晶振,并因此减少了外部器件和功耗。

有256级亮度控制。

数据/命令的发送有三种接⼝可选择:6800/8000串⼝,I2C接⼝或SPI接⼝。

适⽤于多数简介的应⽤,注⼊移动电话的屏显,MP3播放器和计算器等。

特性1.分辨率:128 * 64 点阵⾯板2.电源:a)VDD = 1.65V to 3.3V ⽤于IC逻辑b)VCC = 7V to 15V ⽤于⾯板驱动3.点阵显⽰a)OLED驱动输出电压,最⼤15Vb)Segment最⼤电流:100uAc)常见最⼤反向电流:15mAd)256级对⽐亮度电流控制4.嵌⼊式128 * 64位SRAM显⽰缓存5.引脚选择MCU接⼝a)8位6800/8000串⼝b)3/4线SPI接⼝c)I2C接⼝6.⽔平和垂直两个⽅向的屏幕保存连续滚动功能。

7.RAM写同步信号8.可编程的帧率和多重⽐率9.⾏重映射和列冲映射10.⽚上晶振11.两种封装COG和COF12.⼯作温度范围⼴:-40℃to 85℃订购信息暂不翻译结构⽅框图功能块描述MCU接⼝选择SSD1306MCU接⼝由8个数据引脚和5个控制引脚组成。

引脚分配由不同的接⼝选择决定,详情如下表。

不同的MCU模块可以通过BS[2:0]引脚的硬件选择设置。

0.96寸OLED显示屏使用手册一、OLED简介OLED,即有机发光二极管(Organic Light Emitting Diode)。

OLED 由于同时具备自发光,不需背光源、对比度高、厚度薄、视角广、反应速度快、可用于挠曲性面板、使用温度范围广、构造及制程较简单等优异之特性,被认为是下一代的平面显示器新兴应用技术。

LCD 都需要背光,而OLED不需要,因为它是自发光的。

这样同样的显示OLED效果要来得好一些。

以目前的技术,OLED 的尺寸还难以大型化,但是分辨率确可以做到很高。

在此我们使用的是中景园电子的0.96寸OLED显示屏,该屏有以下特点:1)0.96寸OLED有黄蓝,白,蓝三种颜色可选;其中黄蓝是屏上1/4部分为黄光,下3/4为蓝;而且是固定区域显示固定颜色,颜色和显示区域均不能修改;白光则为纯白,也就是黑底白字;蓝色则为纯蓝,也就是黑底蓝字。

2)分辨率为128*643)多种接口方式;OLED裸屏总共种接口包括:6800、8080 两种并行接口方式、3线或4 线的串行SPI 接口方式、IIC 接口方式(只需要 2 根线就可以控制OLED 了!),这五种接口是通过屏上的BS0~BS2来配置的。

4)中景园电子的本屏开发了两种接口的Demo板,接口分别为七针的SPI/IIC兼容模块,四针的IIC模块。

两种模块都很方便使用;希望大家根据实际需求来选择不同的模块。

二、产品特点2.1 0.96寸OLED裸屏外观裸屏为30pin,从屏正面看左下角为1,右下角为30;在设计的时候一定要注意不要搞反了。

具体的接口定义请大家查看0.96寸OLED官方数据手册;里面有详细介绍。

2.2 0.96寸OLED模块2.2.1 SPI/IIC接口模块模块接口定义:1.GND 电源地2.VCC 电源正(3~5.5V)3.D0 OLED的D0脚,在SPI和IIC通信中为时钟管脚4.D1 OLED的D1脚,在SPI和IIC通信中为数据管脚5.RES OLED的RES#脚,用来复位(低电平复位)6.DC OLED的D/C#E脚,数据和命令控制管脚7.CS OLED的CS#脚,也就是片选管脚2.2.2 IIC接口模块1.GND 电源地2.VCC 电源正(3~5.5V)3.SCL OLED的D0脚,在IIC通信中为时钟管脚4.SDA OLED的D1脚,在IIC通信中为数据管脚2.3 0.96寸OLED驱动IC本屏所用的驱动IC为SSD1306;其具有内部升压功能;所以在设计的时候不需要再专一设计升压电路;当然了本屏也可以选用外部升压,具体的请详查数据手册。

SSD1306命令命令表单(D/C#=0, R/W#(WR#) = 0, E(RD#=1) 特殊状态除外) 1、基本命令D/C Hex D7 D6 D5 D4 D3 D2 D1 D0 命令描述0 81A[7:0] 1A7A6A5A4A3A2A11A0设置对比度双字节命令,1~256级对比度可选,对比度随值增加。

(复位值 = 0x7f)0 A4/A5 1 0 0 0 0 1 0 X0全部显示开A4h,X0 = 0 :恢复内存内容显示(默认),输出内存中的内容A5h,X0 = 1 :开显示,输出无视内存的内容0 A6/A7 1 0 0 0 0 1 1 X0设置正常/逆显示A6,X[0]= 0:正常显示(默认) RAM为0:显示面板关RAM为1:显示面板开A7 X[0]= 1:逆显示RAM为0:显示面板开RAM为1:显示面板关0 AE/AF 1 0 0 0 1 1 1 X0设置显示开/关AE:X[0]= 0:关显示(默认) AF:X[0]= 1:在正常模式显示2、滚动命令表D/C Hex D7 D6 D5 D4 D3 D2 D1 D0 命令描述0 0 0 0 0 0 0 26/27A[7:0]B[2:0]C[2:0]D[2:0]E[7:0]F[7:0]***1***11***1***1***11B2C2D211B1C1D11X0B0C0D01连续水平滚动设置26小时,X[0]= 0,右向水平滚动27 h,X[0]= 1,左向水平滚动(水平滚动1列)[7:0]:虚拟字节(设置为00 h)B(2:0):定义开始页面地址0~7 PAGE0 ~ PAGE7C(2:0):设置每个滚动步骤之间的时间间隔的帧频000 b - 5帧100 b - 3帧001 b - 64帧101 b - 4帧010 b - 128帧110 b - 25帧011 b - 256帧111 b - 2帧D(2:0):定义最终页面地址0~7 PAGE0 ~ PAGE7D(2:0)的值必须大于或等于B(2:0)E[7:0]:虚拟字节(设置为00 h)F[7:0]:虚拟字节(设置为FFh)0 0 0 0 29/2AA[2:0]B[2:0]C[2:0]****1****1**B2C2X1B1C1X0B0C0连续垂直和水平滚动设置29H,X1X0 = 01 :垂直和水平滚动2AH,X1X0 = 10 :垂直和水平滚动(水平滚动1列)[7:0]:虚拟字节0 0 D[2:0]E[5:0]***E5*E4*E3D2E2D1E1D0E0B(2:0):定义开始页面地址0~7 PAGE0 ~ PAGE7C(2:0):设置每个滚动步骤之间的时间间隔的帧频000 b - 5帧100 b - 3帧001 b - 64帧101 b - 4帧010 b - 128帧110 b - 25帧011 b - 256帧111 b - 2帧D(2:0):定义最终页面地址0~7 PAGE0 ~ PAGE7D(2:0)的值必须大于或等于B(2:0)E[5:0]:垂直滚动偏移量例如E[5:0]= 01 h指抵消= 1行E(5:0)= 3跳频是指抵消= 63行请注意(1)没有可用连续垂直滚动。

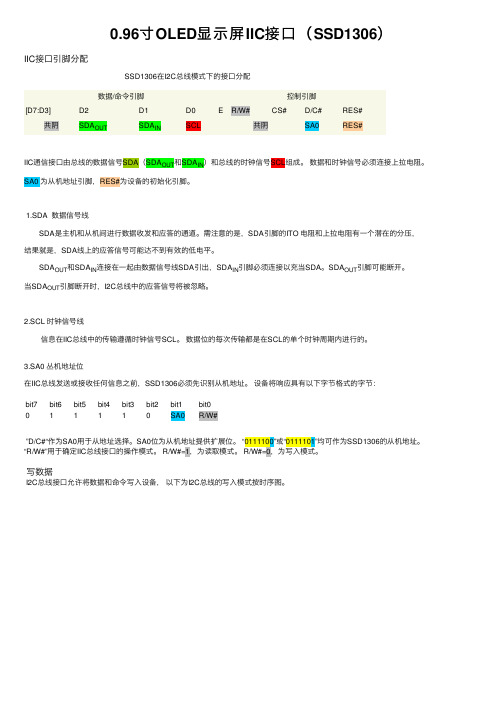

0.96⼨OLED显⽰屏IIC接⼝(SSD1306)IIC接⼝引脚分配SSD1306在I2C总线模式下的接⼝分配数据/命令引脚控制引脚[D7:D3]D2D1D0E R/W#CS#D/C#RES#共阴SDA OUT SDA IN SCL共阴SA0RES#IIC通信接⼝由总线的数据信号SDA(SDA OUT和SDA IN)和总线的时钟信号SCL组成。

数据和时钟信号必须连接上拉电阻。

SA0 为从机地址引脚,RES#为设备的初始化引脚。

1.SDA 数据信号线 SDA是主机和从机间进⾏数据收发和应答的通道。

需注意的是,SDA引脚的ITO 电阻和上拉电阻有⼀个潜在的分压,结果就是,SDA线上的应答信号可能达不到有效的低电平。

SDA OUT和SDA IN连接在⼀起由数据信号线SDA引出,SDA IN引脚必须连接以充当SDA。

SDA OUT引脚可能断开。

当SDA OUT引脚断开时,I2C总线中的应答信号将被忽略。

2.SCL 时钟信号线 信息在IIC总线中的传输遵循时钟信号SCL。

数据位的每次传输都是在SCL的单个时钟周期内进⾏的。

3.SA0 丛机地址位在IIC总线发送或接收任何信息之前,SSD1306必须先识别从机地址。

设备将响应具有以下字节格式的字节:bit7bit6bit5bit4bit3bit2bit1bit0011110SA0R/W#”D/C#“作为SA0⽤于从地址选择。

SA0位为从机地址提供扩展位。

“0111100”或“0111101”均可作为SSD1306的从机地址。

“R/W#”⽤于确定IIC总线接⼝的操作模式。

R/W#=1,为读取模式。

R/W#=0,为写⼊模式。

写数据I2C总线接⼝允许将数据和命令写⼊设备,以下为I2C总线的写⼊模式按时序图。

IIC总线写⼊数据格式IIC写⼊模式1.主机通过启动条件启动数据通信。

启动条件是在SCL保持⾼电平期间捕获到SDA的⼀个下降沿,见下图:IIC通信启动和停⽌条件2.开始通信后⾸先发送⼀个字节:从机地址和读写控制位R/W#。

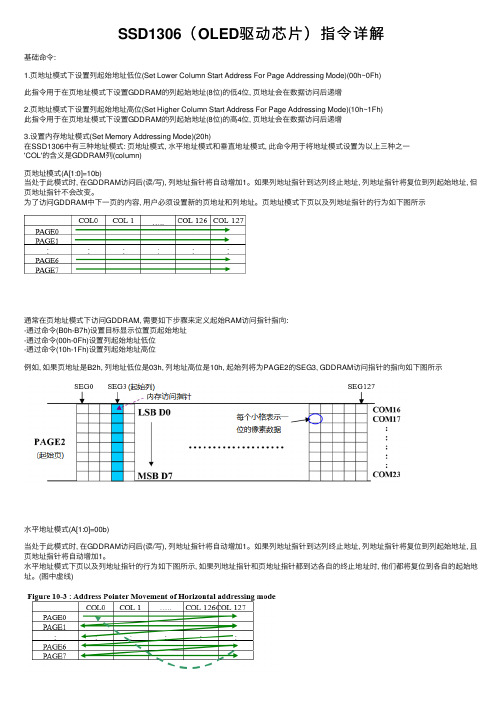

SSD1306(OLED驱动芯⽚)指令详解基础命令:1.页地址模式下设置列起始地址低位(Set Lower Column Start Address For Page Addressing Mode)(00h~0Fh)此指令⽤于在页地址模式下设置GDDRAM的列起始地址(8位)的低4位, 页地址会在数据访问后递增2.页地址模式下设置列起始地址⾼位(Set Higher Column Start Address For Page Addressing Mode)(10h~1Fh)此指令⽤于在页地址模式下设置GDDRAM的列起始地址(8位)的⾼4位, 页地址会在数据访问后递增3.设置内存地址模式(Set Memory Addressing Mode)(20h)在SSD1306中有三种地址模式: 页地址模式, ⽔平地址模式和垂直地址模式, 此命令⽤于将地址模式设置为以上三种之⼀'COL'的含义是GDDRAM列(column)页地址模式(A[1:0]=10b)当处于此模式时, 在GDDRAM访问后(读/写), 列地址指针将⾃动增加1。

如果列地址指针到达列终⽌地址, 列地址指针将复位到列起始地址, 但页地址指针不会改变。

为了访问GDDRAM中下⼀页的内容, ⽤户必须设置新的页地址和列地址。

页地址模式下页以及列地址指针的⾏为如下图所⽰通常在页地址模式下访问GDDRAM, 需要如下步骤来定义起始RAM访问指针指向:-通过命令(B0h-B7h)设置⽬标显⽰位置页起始地址-通过命令(00h-0Fh)设置列起始地址低位-通过命令(10h-1Fh)设置列起始地址⾼位例如, 如果页地址是B2h, 列地址低位是03h, 列地址⾼位是10h, 起始列将为PAGE2的SEG3, GDDRAM访问指针的指向如下图所⽰⽔平地址模式(A[1:0]=00b)当处于此模式时, 在GDDRAM访问后(读/写), 列地址指针将⾃动增加1。

简介SSD1306是一个单片CMOS OLED/PLED驱动芯片可以驱动有机/聚合发光二极管点阵图形显示系统。

由128 segments 和64 Commons组成。

该芯片专为共阴极OLED面板设计。

SSD1306中嵌入了对比度控制器、显示RAM和晶振,并因此减少了外部器件和功耗。

有256级亮度控制。

数据/命令的发送有三种接口可选择:6800/8000串口,I2C接口或SPI接口。

适用于多数简介的应用,注入移动电话的屏显,MP3播放器和计算器等。

特性1.分辨率:128 * 64 点阵面板2.电源:a)VDD = 1.65V to 3.3V 用于IC逻辑b)VCC = 7V to 15V 用于面板驱动3.点阵显示a)OLED驱动输出电压,最大15Vb)Segment最大电流:100uAc)常见最大反向电流:15mAd)256级对比亮度电流控制4.嵌入式128 * 64位SRAM显示缓存5.引脚选择MCU接口a)8位6800/8000串口b)3/4线SPI接口c)I2C接口6.水平和垂直两个方向的屏幕保存连续滚动功能。

7.RAM写同步信号8.可编程的帧率和多重比率9.行重映射和列冲映射10.片上晶振11.两种封装COG和COF12.工作温度范围广:-40℃to 85℃订购信息暂不翻译结构方框图功能块描述MCU接口选择SSD1306MCU接口由8个数据引脚和5个控制引脚组成。

引脚分配由不同的接口选择决定,详情如下表。

不同的MCU模块可以通过BS[2:0]引脚的硬件选择设置。

MCU 并口6800系列接口不翻译MCU 并口8080系列接口不翻译MCU串口(4-wire SPI)不翻译MCU串口(3-wire SPI)不翻译MCU I2C 接口I2C通讯接口由从机地址为SA0,I2C总线数据信号(SDAout/D2输出和SDAin/D1输入)和I2C总线时钟信号SCL(D0)组成。

数据和时钟信号线都必须接上上拉电阻。

RES#用来初始化设备。

a.从机地址位(SA0)SSD1306在发送或接受任何信息之前必须识别从机地址。

设备将会响应从机地址,后面跟随着从机地址位(SA0位)和读写选择位(R/W#位),格式如下:b7 b6 b5 b4 b3 b2 b1 b00 1 1 1 1 0 SA0 R/W#SA0位为从机地址提供了一个位的拓展。

0111100或0111101都可以做为SSD1306的从机地址。

D/C#引脚作为SA0用于从机地址选择。

R/W#为用来决定I2C总线接口的操作模式。

R/W# = 1,读模式。

R/W# = 0 写模式b.I2C总线数据信号SDASDA作为发送者和接受者之间的通讯通道。

数据和应答都是通过SDA发送。

应该注意的是ITO轨道电阻和SDA引脚上的上拉电阻会变成一个潜在的电压分压器。

结果就是SDA上的应答可能不能达到有效的逻辑0。

SDAin和SDAout绑定到了一起作为SDA。

SDAin引脚必须连接到SDA。

SDAout引脚可以不连接。

当SDAout引脚不连接,应答信号将会被I2C总线忽略。

c.I2C总线时钟信号SCLI2C总线上的信息传输任务是随着一个时钟信号的,SCL。

每个数据位的传输任务发生在SCL的单个的时钟周期中。

I2C总线写数据I2C总线接口提供了写数据和命令到设备的接口。

关于I2C总线的写模式的时序请参考下图:I2c的写模式1.主机设备通过开始条件初始化数据通讯。

开始条件的定义在下面的图中展示。

开始条件通过将SDA从高拉低而SCL保持高建立。

2.从机地址紧跟着开始条件作为标志用。

对于SSD1306,从机地址可以是“b0111100”或“b0111101”通过改变SA0到LOW或HIGH(D/C引脚作为SA0)。

3.写模式的建立是通过设置R/W#为到逻辑0实现的。

4.应答位信号将在接收到一个字节的数据后发生包括从机地址和R/W#位。

可以参考下面的应答位信号的图示。

应答位的定义是在应答位相关的时钟脉冲的高周期中把SDA线拉低。

5.传输完从机地址之后,控制字节或数据字节开始通过SDA传输。

一个控制字节主要由CO和D/C#位后面再加上六个0组成的。

a)如果Co为设为逻辑0,,后面传输的信息就只包含数据字节。

b)D/C为决定了下个数据字节是作为命令还是数据。

如果D/C#位设为0,下一个数据就是命令。

如果D/C#位设为1,下一个数据就是数据,将会存在GDDRAM中。

GDDRAM列地址指针将会在每次数据写之后自动加1.6.应答位将会在接收到每个控制字节或数据字节之后发生7.写模式会在用了停止条件之后结束。

停止条件:将SDA从低拉高,而SCL保持高。

请注意数据位的传输是有限制的1.数据位,在每个SCL脉冲阶段传输,必须在时钟脉冲高周期内保持稳定状态。

可以参考下面的图示。

除了开始或停止条件,数据线只能在SCL为LOW的时候转换状态。

2.SDA和SCL都必须接外接上拉电阻命令解码器这个模块决定了输入数据被解读为数据还是命令。

数据的解读是基于D/C#引脚的输入。

如果D/C#引脚是高,D[7:0]就被解读为写到图像显示数据RAM(GDDRAM)中的显示数据。

如果是低,D[7:0]的输入就被解读为一个命令。

然后数据输入就会被解码并写到相关的命令寄存器中。

晶振电路和显示时间发生器这是一个片上低功耗RC震荡电路。

操作时钟(CLK)可以由内部震荡器或外部CL引脚生成。

这个选择是通过CLS引脚完成的。

当CLS引脚拉高,内部振荡器开启,CL应该保留开启。

将CLS拉低可以静止内部振荡器,外部时钟必须连接到CL引脚上。

当选择了内部振荡器之后,输出频率Fosc可以通过命令D5h A[7:4]修改。

用于显示时钟发生器的显示时钟(DCLK)是源于CLK的。

分频因子“D”可以通过命令D5h 编程范围为1到16DCLK = Fosc/D显示的帧率是由下面的公式决定F FRM=FD∗K∗No.of MuxD 代表时钟分频。

由D5h A[3:0]设置。

范围是1到16K是每行显示时钟的数量。

值的计算如下:K = 相1周期+ 相2周期+ BANK0脉冲宽度= 2 + 2 + 50 = 54 在上电重启时Number of multiplex ratio 通过command A8h设置。

上电重启值为63 。

Fosc 是振荡器频率,可以通过命令D5h A[7:4]修改。

值越大频率越大。

FR同步不翻译重启电路当RES# 输入为LOW时,芯片初始化为下面的状态:1.显示关2.128 * 64显示模式3.正常的segment和显示数据列地址和行地址映射(SEG0映射到address 00h,COM0映射到address 00h)4.在串口中清除移位寄存器数据5.显示开始行设置为显示RAM地址06.列地址计数设为07.正常扫描COM输出方向8.对比度控制寄存器设为7Fh9.正常显示模式(等同于A4h命令)Segment 驱动/Common驱动Segment驱动实现了128个电路源来驱动OLED面板。

驱动电流的范围可以在0到100uA以内调节,有256个等级。

Common驱动产生电压脉冲。

segment驱动波形分为3个阶段:1.在阶段1,OLED用于显示上一个图片的像素停止充电目的是为了准备显示下一张图片的内容。

2.在阶段2,OLED像素被充到目标电压。

像素被从Vss驱动到相关电压水平。

阶段2时间可以通过编程在1到15个DCLK内变化。

如果OLED面板的像素的电容值比较大,那么就需要更长的时间周期来给电容充电以达到想要的电压。

3.在阶段3,OLED驱动转换为使用电流源来驱动OLED像素,这就是电流源驱动阶段了。

当完成阶段3之后,驱动芯片会回到阶段1来显示下一行图像信息。

这三部循环持续运行来刷新OLED面板上的图像显示。

在阶段3,如果电流驱动脉冲长度设为50,在电流驱动阶段完成50个DCLK后,驱动芯片回到阶段1准备下一行的显示。

图形显示数据RAM(GDDRAM)GDDRAM是一个为映射静态RAM保存位模式来显示。

该RAM的大小为128 * 64为,RAM 分为8页,从PAFE0到PAGE7,用于单色128 * 64点阵显示,如下图所示当一个数据字节写到GDDRAM中,所有当前列的同一页的行图像数据都会被被填充(比如,被列地址指针指向的整列(8位)都会被填充)。

数据位D0写到顶行,而数据位D7写到底行,如下图所示。

为了灵活性,segment和common上的重映射都可以通过软件选择。

对于显示的垂直移动,一个内部的寄存器保存了显示开始行可以用来设置控制RAM数据部分来映射显示(命令D3h)。

SEG/COM驱动块不翻译上电和断电顺序不翻译命令表(D/C# = 0,R/W#(WR#) = 0, E(RD# = 1),除非有别的状态声明)9.1数据读写为了往GDDRAM中写数据,在6800系列并口和8080系列并口模式中将R/W#(WR#)引脚置低,D/C#引脚置高。

串口模式总是处于写模式。

GDDRAM列地址指针在写完一个数据之后会自动加一。

10 命令描述10.1 基本命令10.1.1 设置低列开始地址作为页地址模式(00h~0Fh)10.1.2 设置高列开始地址作为页地址模式(10h~1Fh)10.1.3 设置内存地址模式(20h)SSD1306中有三种不同的内存地址模式:页地址模式,水平地址模式,垂直地址模式。

这个命令将内存地址模式设置成这三种中的一种。

在这里COL的意思是图形显示数据RAM列。

页地址模式(A[1:0] =10xb)在页地址模式下,在显示RAM读写之后,列地址指针自动加一。

如果列地址指针达到了列的结束地址,列地址指针重置为列开始地址并且也地址指针不会改变。

用户需要设置新的页和列地址来访问下一页RAM内从。

页地址模式下PAGE和列地址指针的移动模式参考下图在正常显示数据RAM读或写和页地址模式,要求使用下面的步骤来定义开始RAM访问的位1.通过命令B0h到B7h来设置目标显示位置的页开始地址2.通过00h~0Fh来设置低开始列地址的指针3.通过命令10h~1Fh来设置高开始列地址比如说,如果页地址设置为B2h,低列地址是03h高列地址为00h,那么就意味着开始列是PAGE2的SEG3.RAM访问指针的位置如下图所示。

输出数据字节将写到RAM列3的位置。

水平寻址模式(A[1:0]= 00b)在水平寻址模式下,当显示RAM被读写之后,列地址指针自动加一。

如果列地址指针达到列的结束地址,列地址指针重置为列的开始地址,并且页地址指针自动加1。

水平寻址模式下页和列地址的移动顺序如下图所示。

当列地址和页地址都达到了结束地址,指针重设为列地址和页地址的开始地址。

垂直寻址模式(A[1:0]=01b)在垂直寻址模式下,当显示RAM被读写之后,页地址指针自动加一。