倒装焊工艺(bumping)

- 格式:pdf

- 大小:896.83 KB

- 文档页数:18

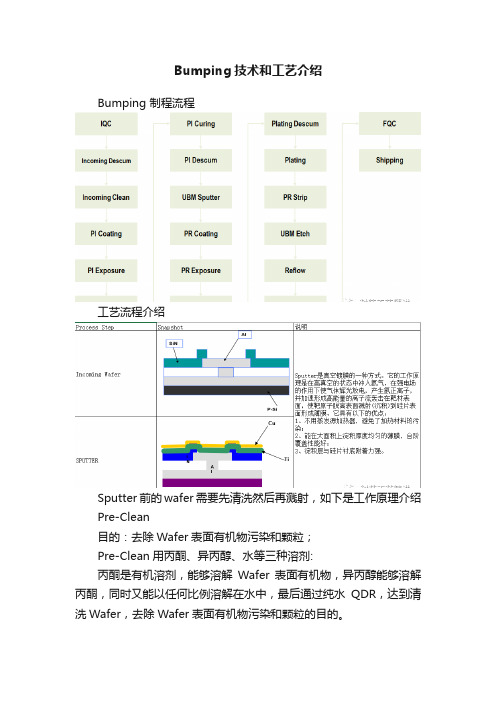

Bumping技术和工艺介绍Bumping 制程流程工艺流程介绍Sputter 前的wafer 需要先清洗然后再溅射,如下是工作原理介绍Pre-Clean目的:去除Wafer表面有机物污染和颗粒;Pre-Clean用丙酮、异丙醇、水等三种溶剂:丙酮是有机溶剂,能够溶解Wafer表面有机物,异丙醇能够溶解丙酮,同时又能以任何比例溶解在水中,最后通过纯水QDR,达到清洗Wafer,去除Wafer表面有机物污染和颗粒的目的。

使用超声波+有机溶剂清洗:超声清洗有时也被称作“无刷擦洗”,特点是速度快、质量高、易于实现自动化。

它特别适用于清洗表面形状复杂的工件,如对于精密工件上的空穴、狭缝、凹槽、微孔及暗洞等处。

通常的洗刷方法难以奏效,利用超声清洗则可取得理想效果。

对声反射强的材料,如金属、玻璃、塑料等,其清洗效果较好;对声吸收较大的材料,如橡胶、布料等,清洗效果则较差些。

采用超声波清洗时,一般应用化学清洗剂和水基清洗剂作为介质。

清洗介质本身利用的是化学去污作用,可以加速超声波清洗效果。

溅射原理Sputter原理在充入少量Ar的Stepper腔内。

靶材是阴极,Wafer是阳极。

当极间电压很小时,只有少量离子和电子存在;电流密度在10’A/era 数量极,当阴极(靶材)和阳极间电压增加时,带电粒子在电场的作用下加速运动,能量增加,与电极或中性气体原子相碰撞,产生更多的带电粒子;直至电流达到10A/era数量极,当电压再增加时,则会产生负阻效应,即“雪崩”现象。

此时离子轰击阴极,击出阴极原子和二次电子,二次电子与中性原子碰撞,产生更多离子,此离子再轰击阴极,又产生二次电子,如此反复。

当电流密度达到0.01A/era数量级左右时,电流将随电压的增加而增加,形成高密度等离子体的异常辉光放电,高能量的离子轰击阴极(靶材)产生溅射现象。

溅射出来的高能量靶材粒子沉积到阳极(Wafer)上,从而达到溅射的目的。

在磁场的作用下,电子在向阳极运动的过程中,作螺旋运动,束缚和延长了电子的运动轨迹,从而提高了电子对工艺气体的电离几率,有效地利用了电子的能量,因而在形成高密度等离子体的异常辉光放电中,正离子对靶材轰击所引起的靶材溅射更加有效。

封装基板作为芯片封装的核心材料,一方面能够保护、固定、支撑芯片,增强芯片导热散热性能,保证芯片不受物理损坏,另一方面封装基板的上层与芯片配,以及沟通芯片内部与外部电路等功能。

IC 载板性能优良,应用占比持续提升。

与常规 PCB 板相比,封装基板线宽、线距更小,板子尺寸更小,能达到主流芯片的严苛要求。

线宽/线距50μm/50μm 属于PCB 高端产品,而封装基板制造领域,线宽/线距在30μm/30μm 以内属于常规产品。

随着技术朝高密度、高精度发展,高端产品封装基板在PCB板中占比也逐步提升。

根据prismark,2000 年封装基板在PCB板中占比8.43%,2020年封装基板占比为15.68%,预测至2026 年,封装基板占比将达到21.11%,占比稳步提升。

IC 载板主要用于集成电路封装环节,是封装环节价值量最大的耗材。

根据中研网,IC 载板在中低端封装中占材料成本的40~50%,在高端封装中占70~80%。

原材料可分为结构材料(树脂、铜箔、绝缘材等)、化学品(干膜、油墨、金盐、光阻、蚀刻剂、显影剂)以及耗材(钻头)。

其中,树脂、铜箔、铜球为占IC 载板成本比重最大的原材料,比分别为35%,8%,6%。

根据华经产业研究院数据,IC 载板下游主要应用于移动终端(26%)、个人电脑(21%)、通讯设备(19%)、存储(13%)、工控医疗(8%)、航空航天(7%)、汽车电子(6%)。

从产业链上来看,IC 载板运用于集成电路封装阶段。

电子封装是器件到系统的桥梁,这一环节极大影响力微电子产品的质量和竞争力。

随着半导体技术的发展,IC 载板的特征尺寸不断缩小、集成度不断提高,相应的IC 封装向着超多引脚、窄节距、超小型化方向发展。

根据《中国半导体封装业的发展》,迄今为止全球集成电路封装技术一共经历了五个发展阶段。

当前,全球封装行业的主流技术处于以CSP、BGA 为主的第三阶段,并向以系统级封装(SiP)、倒装焊封装(FC)、芯片上制作凸点(Bumping)为代表的第四阶段和第五阶段封装技术迈进。

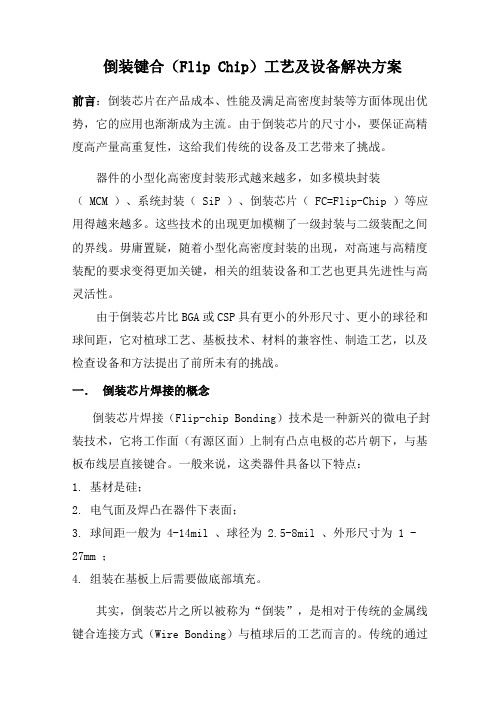

倒装键合(Flip Chip)工艺及设备解决方案前言:倒装芯片在产品成本、性能及满足高密度封装等方面体现出优势,它的应用也渐渐成为主流。

由于倒装芯片的尺寸小,要保证高精度高产量高重复性,这给我们传统的设备及工艺带来了挑战。

器件的小型化高密度封装形式越来越多,如多模块封装( MCM )、系统封装( SiP )、倒装芯片( FC=Flip-Chip )等应用得越来越多。

这些技术的出现更加模糊了一级封装与二级装配之间的界线。

毋庸置疑,随着小型化高密度封装的出现,对高速与高精度装配的要求变得更加关键,相关的组装设备和工艺也更具先进性与高灵活性。

由于倒装芯片比BGA或CSP具有更小的外形尺寸、更小的球径和球间距,它对植球工艺、基板技术、材料的兼容性、制造工艺,以及检查设备和方法提出了前所未有的挑战。

一.倒装芯片焊接的概念倒装芯片焊接(Flip-chip Bonding)技术是一种新兴的微电子封装技术,它将工作面(有源区面)上制有凸点电极的芯片朝下,与基板布线层直接键合。

一般来说,这类器件具备以下特点:1. 基材是硅;2. 电气面及焊凸在器件下表面;3. 球间距一般为 4-14mil 、球径为 2.5-8mil 、外形尺寸为 1 -27mm ;4. 组装在基板上后需要做底部填充。

其实,倒装芯片之所以被称为“倒装”,是相对于传统的金属线键合连接方式(Wire Bonding)与植球后的工艺而言的。

传统的通过金属线键合与基板连接的芯片电气面朝上(图1),而倒装芯片的电气面朝下(图2),相当于将前者翻转过来,故称其为“倒装芯片”。

在圆片(Wafer)上芯片植完球后(图3),需要将其翻转,送入贴片机以便于贴装,也由于这一翻转过程而被称为“倒装芯片”。

图1图2图3倒装芯片在1964年开始出现,1969年由IBM发明了倒装芯片的C4工艺(Controlled Collapse Chip Connection可控坍塌芯片联接)。

BUMPING INTRODUCTIONBUMPING INTRODUCTIONBumping process introduction Domestic Bumping industryReflow machineWafer bumping: planting ball on wafer padApplication: advanced package (BGA &WLP&CSP…..)Wafer bumps-gold bums-solder bumps-plating bumps-stencil printing bumps-solder ball attachMethods of wafer bumping for flip chipGold bumping (plated)Solder bumping (plated)Gold ball (stud) bumps (gold wire micro weld) Solder ball bumps placementStencil Printed solder bumpingSolder bumping process is accomplished in a foundry-like processing setting. The bumps are generally made of lead, tin, or a combination of both.Solder Bumping process flow•gold ball bumping is truly an extension of thewire bonding process.Wire bonding.Gold (stud) bumps Bumping process introductionBumping process introduction Stencil printed solder bumpingSolder ball bumps placement and reflowCosts of gold ball bumping vs. platingDomestic Bumping industry 苏州颀中Chipmore上海宏茂Chipmos上海安靠Amkor星科金朋SCC江阴长电JCAP苏州晶方WLCSP中芯国际SMIC上海宏茂Chipmos & 苏州欣中Chipmore -TCP&COG&COF for LCD Driver IC -Gold bumps上海安靠Amkor-put into production-gold &solder bumping星科金朋SCC-Bumping service from TSMC-Gold +Ni bumping & solder bumping•JCAP Bumping Services苏州Shellcase-Shellcase WLCSP process & Wafer bumping process & TSV WLCSP process氮气回流焊炉(for WAFER BUMP FORMING) -YAMATO WORKS (120000 USD)深圳敏科))系列回流焊炉炉(深圳敏科HELLER 1800EXL系列回流焊岗)大型全热风无铅回流焊炉-SNR州圣岗SNR--845P(苏州圣大型全热风无铅回流焊炉SEMIgear GENVEA STP200/300。

晶圆封装bumping工艺晶圆封装Bumping工艺是一项精密的加工技术,是一种高精度的平面组件的加工处理工艺,是一种将空白封装器件和微加工技术相结合,以实现功能封装的方法。

它将封装材料、晶圆将物理电路(PITCH 封装应用于多层晶圆封装技术,可以满足抗振性、耐热性、耐低温性、耐弯曲性以及电磁屏蔽等关键性能要求。

晶圆封装bumping工艺可分为几个步骤:第一步:晶圆针绕。

这是晶圆封装bumping工艺中的基础工序,首先将晶圆表面的针绕组件用超细金属丝缠绕起来,经过特殊的热处理过程,以达到组件的稳定性和可靠性。

第二步:热处理。

热处理将组件进行热处理,达到晶圆封装bumping工艺的要求。

在热处理过程中,靶材的表面会发生形变,使附着在其上的针绕组件贴合到靶材表面。

第三步:高温焊接。

焊接完成时,晶圆封装bumping工艺中的针绕组件实现了特殊的磁滞等特性,以及避免静电放电(ESD)的能力。

第四步:Bumping技术。

Bumping是晶圆封装bumping工艺的关键,意味着将元件的组件引出的引线连接到晶圆表面上的接点上,以满足晶圆封装bumping工艺的要求。

Bumping技术使用了微缩封装,它将元件的组件连接到晶圆表面上,以确保元件表面的牢固性和可靠度。

第五步:保护层。

晶圆封装bumping工艺最后一步是将晶圆保护层制作上去,以保护晶圆表面上的针绕组件和接点,以及防止晶圆表面上的元件组件受损或损坏。

晶圆封装bumping工艺是一项高精度、复杂的封装工艺,它在功能性电子产品设计领域应用非常广泛。

它可以使元件表面具有良好的绝缘性能,耐热性,耐低温性,抗振性等特性,为电子产品的设计和应用带来更多的可能性。

在晶圆封装bumping工艺中,还采用了微封装和微加工技术,这些技术可以提高设计的灵活性,使空白封装产品的封装密度更高、性能更好。

此外,晶圆封装bumping工艺可以实现紧凑的布线,提高部件的安装效率,进一步减少空间的要求,使复杂的电子产品封装成形成有可能。

一种芯片倒装焊接的方法

芯片倒装焊接是一种在电子制造中常用的技术,通常用于将芯片连接到印刷电路板(PCB)上。

以下是一种常见的芯片倒装焊接方法:

1.准备工作:根据设计要求,将芯片放置在PCB的指定位置上,并使用夹持器或夹子将其稳定固定。

2.涂上焊膏:在芯片引脚和PCB焊盘上涂上焊膏,使焊接更容易。

3.热风预加热:使用热风枪在芯片和PCB之间加热,将其预加热至适当温度,以减少热应力和热冲击。

4.翻转芯片:将芯片翻转,使其引脚朝向PCB。

5.再次加热:使用热风枪在PCB的底部加热,将芯片的引脚和PCB焊盘连接在一起。

6.冷却:等到焊接完成后,用冷水或冷风快速冷却电路板,以确保焊点变硬。

7.视觉检查:检查焊点是否正确连接,并清除任何残留在焊盘上的焊胶。

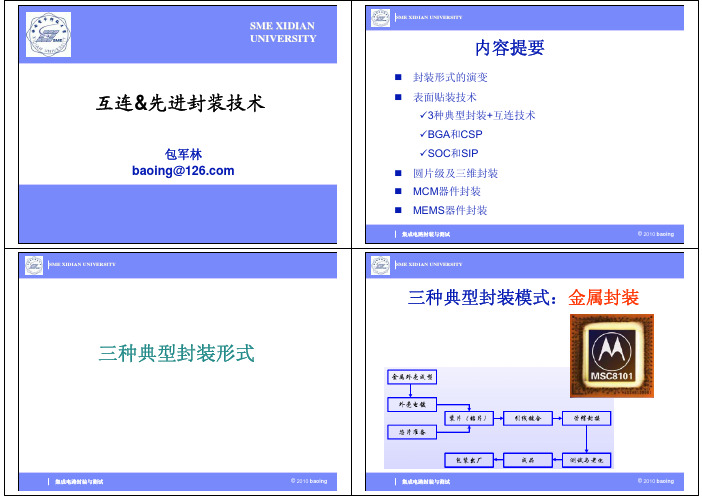

集成电路封装与测试SME XIDIAN UNIVERSITY类似于银浆粘接技术熔接温度高于外壳盖板熔封温度载带封装倒装芯片引线键合Tape-Carrier Package破坏表面氧化层和污染,产生塑性变形,2.载带封装(TAB):工艺是芯片引脚框架的一种互连工艺。

1.首先在高聚物上做好元件引脚图样;2.然后将晶片按其键合区对应放在上面;3.最后通过热电极一次将所有的引线进行键合。

•冲孔•Cu 箔叠层•照相+ 腐蚀形成Cu 图样•导电图样Cu镀锡带有Cu图样的TAB膜,齿轮孔则便于带的传送。

集成电路封装与测试©2010baoing©2010集成电路封装与测试SME XIDIAN UNIVERSITY集成电路封装与测试©2010 SME XIDIAN UNIVERSITYFlip-Chip关键工艺:两种下填料各向同性导电胶&各向异性导电胶Anisotropic conduction 集成电路封装与测试©2010baoingSME XIDIAN UNIVERSITY©2010baoing 集成电路封装与测试SME XIDIAN UNIVERSITYPBGA工艺流程©2010baoing 集成电路封装与测试等焊接的检测。

©2010baoingSME XIDIAN UNIVERSITY BGA 检测断面X-ray 检测通过一个聚焦断面,使目标区域上下平面散焦的方法对焊接区进行检测,解决了焊球与焊盘垂直重叠的问题。

根据不同部位的剖面,可得到每个剖面基本参数,便于焊点辨别。

封装基板©2010集成电路封装与测试SME XIDIAN UNIVERSITY基板:多层基板集成电路封装与测试集成电路封装与测试©2010baoingCSP集成电路封装与测试©2010baoing©2010baoingSME XIDIAN UNIVERSITYCSP的核心结构LOC-CSP集成电路封装与测试©2010集成电路封装与测试CSP工艺:Fujitsu公司MicroBGA(SME XIDIAN UNIVERSITYCSP工艺:Fujitsu公司MicroBGA(II)SME XIDIAN UNIVERSITYCSP工艺:Fujitsu公司QNP (Quad Flat Nonleaded PackageSME XIDIAN UNIVERSITY CSP应用©集成电路封装与测试©2010集成电路封装与测试再分布,把四周的引出端均匀地布置在整个管芯上。

随着超导量子比特技术的进一步发展,实验上需要可以表面误码差校正以及更复杂的高保真量子电路[1-2]。

相关报道介绍了一些平面二维阵列的设计[3-5],但是这几种现行的设计方案中控制布线和读出电路往往使得量子比特数目与器件高保真度这二者与不能同时兼顾。

例如,二维阵列的X mon单量子位就需要利用电容耦合到四个最近量子比特和读出谐振腔,此外还要考虑XY驱动线的设计[6]。

多层膜加工工艺是解决这个问题的一种直观的方案[7],但是该方案中制备的量子比特基片上制备的绝缘层会造成额外的退相干,从而影响量子比特的特性[8]。

目前国际上解决上述困难的主流方法是通过将器件分离成两部分,其中一部分是密集的布线基片并在该基片上制备绝缘层,另一部分上制备量子比特而不生长大面积的绝缘层,随后将这两种基片通过倒装焊工艺结合起来形成一种同时满足多量子比特数目与高保真度的量子比特器件。

该种工艺已经在半导体工业中得到了广泛的应用,从手机到大型强子对撞机都有应用[9]。

而在低温技术中的应用还较少。

该工艺对两部分基片的连接部分提出了如下的要求:1.连接材料应是常规的量子比特制备工艺中常用的并可以与现有的量子比特制备工艺兼容。

2.谐振腔的可加工数量与质量必须达到高要求。

(在布线基片上需加工数百个高Q值的谐振腔)。

3.在极低温的条件下可以保证两部分的联通。

4.可以在不高的温度与大气压下进行两部分基片的连接,以避免退火改变约瑟夫森结临界电流[10]。

5.两部分基片的连接部分必须在测量条件下进入超导态,以保证芯片之间的无损连接与避免局部生热破坏测量条件。

6.相互连接偏置线临界电流应大于5nA,以保证可以进行实验测量。

铟的临界温度相对较高为3.4K,室温铟焊接工艺也是一种在半导体工业中较为成熟的技术[11],而在量子比特的加工工艺中高纯度的铟可以通过常用的热蒸发工艺生长在指定的位置,因此基片之间连接材料可选高纯铟。

但是,由于量子比特的基底金属常用铝,而铝和铟接触层会形成交叠层[12]影响量子比特的性能,因此热蒸发的时候必须在铝基底上生长氮化钛介质缓冲层以防止上述现象的出现,氮化钛的临界温度高达5.64K,并且是一种高相干性能的量子比特材料[13,14]。

What is Bumping➢To generate bumps on wafer.➢The essence to advanced packaging, specifically flip chip packaging.➢Benefits of bumping:⚫High density interconnection.⚫High speed data processing (short connection path, lowerconnection resistance and higher driving current density)⚫Small package body size.⚫Real chip size achievable.⚫Cost competitive.Bump classification➢按封装形式:Flip Chip Bump,WLP(Wafer Level Package)➢按Bump结构:C4:Control Collapse Chip Connection,主要以Solder Bump(高铅,无铅)为主。

C2:Chip Connection,以Cu Pillar为主Gold Bump➢按保护层:Non-PI,PI(Polyimide),BCB➢按布线方式:RDL(Re-Distribution Line),RPI(Repassivation)➢按bump生产方式:电镀,印刷,植球What is UBM➢UBM: Under Bump Metallurgy—Interface between solder and final chip metallization—MUST HA VE : Low resistance, Good adhesion, Diffusion barrier—Must withstand thermal & mechanical stress➢UBM structure1. Solder bump—Sputter Ti/Cu+Plating Cu/Ni(for 65nm above)—Sputter Ti/Cu+Plating Ni (for n45 below, due to foundry introduce ELK dielectric material more fragile/brittle)—So when the IC migrate from n65 to n45, to reduce ELK crack issue there are 2 changes involved for bumping: Add PI re-passivation material& Reduce the UBM thickness to Ni 3um2. Cu Pillar Bump—Suptter Ti/Cu+plating Cu/NiBumping process flow(with PI)Main flow Sub flowIncoming Re-passivation Sputter Photo Plating FVI IQCScrubber BakeDescum PI coating PI exposing PIDevelopingCuring Descum Scrubber Bake SputterPR coating PR Exposing PRDevelopingDescum PlatingPR Stripper Cu Etch Ti Etch Descum Scrubber ReflowAOI➢Sputter⚫Degas: to remove the moisture by heater. because out-gassing can cause contamination and high resistivity of deposited metal film.⚫Pre-sputter Etch: to remove the Al-Oxide on the Al pad with Ar plasma.⚫UBM Deposition: metal is “sputtered” off a magnetron target onto the wafer在腔体顶部有射频感应线圈,高频电源感应加热,使Ar 气体电离产生等离子体,电场作用下,等离子体旋转加速,高速冲击放在阴极上的Wafer ,起到Etch 的作用。

微组装倒装焊工艺

1、采用倒装焊工艺应符合下列规定:

(1)芯片有源面朝下,以凸点阵列结构与基板直接安装互连实现电气连接时,应采用倒装焊工艺;

(2)倒装焊工艺应包括再流焊、超声热压、聚合物互连粘接等工序;

(3)应针对不同的凸点材料采用不同的倒装焊工艺;

(4)下填充材料填充方式应包括毛细管底部填充、助焊(非流动)型底部填充和四角(角)-点底部填充;

(5)宜根据芯片尺寸与凸点密度选择填充方法。

2、倒装焊工艺的主要工序应符合下列规定:

(1)原芯片电极焊区应制作金属过渡层,在金属过渡层上可制作金凸点、铟凸点、镀金镍凸点、锡铅凸点和无铅凸点;

(2)金凸点、镀金焊盘的组合,可采用超声热压焊实现焊接互连;

(3)双组分粘接剂使用前应按比例配制、搅拌均匀并静置排气,单组分粘接剂宜贮存在—40℃的冷冻环境中,使用前应在室温下充分解冻并搅拌均匀、静置或真空排气;

(4)由焊料构成的凸点,可在焊盘或凸点上涂敷助焊剂,然后将待安装的芯片面朝下放置在基板上,按要求固化后通过“温度-时间”曲线进行焊料再流,完成芯片与基板的倒装焊接;

(5)采用下填充和固化工艺时,下填充操作时应倾斜基板,精确控制填充胶量;

(6)倒装焊后应清洗除净焊接产生的污染,再烘干或晾干产品;

(7)芯片倒装及下填充完成后,应目检倒装焊质量,无损检测芯片凸点电极与其基板焊区间的对准精度,并应测试所倒装芯片的抗剪切强度。

3、倒装焊的工艺运行条件应符合下列规定:

(1)倒装焊工艺宜在等于或优于7级净化区中进行;

(2)倒装焊工艺中芯片的安装、互连应同时完成;

(3)倒装焊应在氮气或氮氢混合气体的保护气氛中进行。

1Institute of Microelectronics新型封装技术蔡坚清华大学微电子学研究所jamescai@2Institute of Microelectronics概要芯片到封装互连技术的发展 目前迅速增长的封装型式¾BGA和CSP圆片级及三维封装的发展 MEMS器件的封装SOC和SIP3Institute of Microelectronics芯片到封装互连技术的发展4Institute of Microelectronics 芯片到封装的互连技术在这里不讨论铜互连技术,事实上由于芯片上铜互连的实现,将给芯片到下一级的互连带来新的技术和热点。

针对目前和可以预见的将来新型封装的发展,倒装焊技术(Flip ChipTechnology)将成为非常重要的互连技术。

新型的倒装焊凸点技术(Bumping Method)不断推出。

5Institute of Microelectronics常用的凸点方法蒸发,Evaporation, (IBM C4 Process)SBB (Stud Bump Bonding) 电镀,Electrical plating (Solder/Au) 印刷,Stencil Printing 化学镀UBM结合印刷,Electroless Nickel UBM Paired with Stencil PrintingS2B (Single Solder Ball Placement & Laser Reflow Bumping) ……6Institute of MicroelectronicsSBB技术¾Matsushita and Fujitsu¾应用已有的引线键合设备和技术实现单个键合区的凸点,(微处理器和存储器)¾以金凸点为主(Solder bumps available as well)¾效率相对比较低(8bumps/s)7Institute of Microelectronics凸点电镀技术Electroplating Bumping作为一类成熟的工业技术,电镀在封装(微电子工业)中有非常广泛的应用,凸点技术是其中的一种。

声表⾯波器件⼯艺原理-9倒装焊⼯艺原理九,声表器件倒装焊⼯艺原理序:倒装芯⽚(FC)技术,是在芯⽚的焊接区⾦属上制作凸焊点,然后将芯⽚倒扣在外壳基座上,以实现机械性能和电性能的连接,由于FC是通过凸焊点直接与底座相连,因此与其它互连技术相⽐,FC具有最⾼的封装密度、最⼩的封装尺⼨(线焊可焊的最⼩陶瓷外壳为3×3mm,⽽FC可以作到芯⽚级)、最好的⾼频性能(电感⼩)、最⼩的⾼度、最轻的重量,以及产品⾼可靠、⽣产⾼⼯效等。

倒装焊⼯艺:主要由UBM的形成、凸点的制作、倒装焊接三部分组成。

(⼀)UBM的形成:当凸焊点材料与芯⽚上的焊接区⾦属不能很好浸润粘附时(或接触电阻⼤,或热匹配差,或两种材料间易形成会导致键合强度降低的⾦属间化合物),需要在凸焊点与芯⽚压焊块之间置⼊⼀层既能与芯⽚焊接区⾦属良好粘附、⼜能与凸焊点良好浸润、还能有效阻挡两者之间相互反应扩散的⾦属膜(UBM),因我们⽆法找到可同时满⾜上述要求的材料,所以通常UBM由多层⾦属膜组成。

(说明:与凸点连接的还有底座上相应的焊接点,由于在底座制作时该部位已镀有多层⾦属,能满⾜要求,固在此不于讨论。

)1,对UBM的各层要求及材料选择:1)粘附层:要求与铝膜及钝化层间的粘附性好,低阻接触,热膨涨系数接近,热应⼒⼩。

常选⽤材料有:Cr、Ti、Ti-W、Al、V等,因它们与Al浸润性很好,固该层可较薄。

2)扩散阻挡层:能有效阻挡凸焊点材料与铝间的相互扩散,以免形成不利的⾦属间化合物,特别是⾦凸焊点,在⾼温下与铝可⽣成Al2Au、AlAu、AlAu2、Al2Au5等脆性⾦属间化合物及在接触处相互扩散形成空洞,导致键合强度降低甚⾄失效。

该层常⽤材料有:Ti、Ni、Cu、Pd、Pt、Ti-W等。

(当⽤软焊料如PbSn作凸点时,由于其回流时会吃掉浸润层,直接与阻挡层接触;此时阻挡层应⾜够厚,且与凸点相浸润,不反应产⽣有害物)3)浸润层:要求⼀⽅⾯能和凸焊点材料良好浸润,可焊性好,且不会形成不利于键合的⾦属间化合物;另⼀⽅⾯还能保护粘附层和阻挡层⾦属不被氧化、粘污。

凸点芯片倒装焊接技术及靠谱性测试目录一、倒装焊工艺的选择跟着轻量化、薄型化、小型化、I/O端数的增添以及功能多样化的发展,传统的封装技术已不可以知足高密度的要求。

倒装互连技术的发展为高密度封装带来了希望。

倒装技术与传统引线键合互连技术对比拥有显然的优势,主要表此刻以下几个方面:(1)尺寸小、薄,重量更轻;(2)密度更高,使用倒装焊技术能增添单位面积内的I/O数目;(3)性能提升,短的互连减小了电感、电阻以及电容,信号完好性、频次特征更好;(4)散热能力提升,倒装芯片没有塑封体,芯片反面可用散热片等进行有效的冷却,使电路的靠谱性获取提升;倒装焊技术中重点工艺有四个,它们分别是UBM制备、凸点制备、倒装焊和底部填补技术,它们直接决定着倒装产质量量的利害。

UBM的制备多层金属膜UBM(Under Bump Metallurgy)是在芯片上的Al焊盘与凸焊点之间的一层金属化层,目的是使芯片与基板互连工艺更简单实现、互连靠谱性更高。

UBM一定与Al焊盘及凸焊点间形成优秀的欧姆接触、一定能够保证凸点或焊接资料不直接与Al焊盘接触,以使连结资料有优秀的黏附性能和机械性能,并保证优秀的电性能和导热性能。

UBM往常由黏附层、扩散阻拦层和浸润层等多层金属膜构成。

UBM在进行焊料回流或焊点退火等高温办理时,能够保证凸焊点材料不会穿透UBM而进入下边的Al焊盘中。

铝焊盘上蒸发/溅射多层金属,粘附层Cr、扩散层Cu、阻拦层Au凸点的制备倒装焊(Flip Chip)中的首个凸点制备技术是IBM企业的C4工艺(Controlled Collaps Chips Connection)。

凸点由蒸发的薄膜金属制成。

随工艺技术和设施的发展,知足不一样产品的需求,凸点制备工艺方法愈来愈多,目前比较常有的方法有1.钉头法、2.蒸发/溅射法、3.化学镀法、4.模板印刷法、5.电镀法、6.置球凸点法(SB2- Jet)等。

1、钉头凸点法:在这几种方法中,钉头凸点方法是在焊盘上溅射/蒸镀上UBM后,使用金/铜丝球焊机在UBM上点上凸点,凸点会带有尾丝,所以在点完凸点后还需要去除尾丝。

BUMPING INTRODUCTION

BUMPING INTRODUCTION

Bumping process introduction Domestic Bumping industry

Reflow machine

Wafer bumping: planting ball on wafer pad

Application: advanced package (BGA &WLP&CSP…..)

Wafer bumps

-gold bums

-solder bumps

-plating bumps

-stencil printing bumps

-solder ball attach

Methods of wafer bumping for flip chip

Gold bumping (plated)

Solder bumping (plated)

Gold ball (stud) bumps (gold wire micro weld) Solder ball bumps placement

Stencil Printed solder bumping

Solder bumping process is accomplished in a foundry-like processing setting. The bumps are generally made of lead, tin, or a combination of both.

Solder Bumping process flow

•gold ball bumping is truly an extension of the

wire bonding process.

Wire bonding.Gold (stud) bumps Bumping process introduction

Bumping process introduction Stencil printed solder bumping

Solder ball bumps placement and reflow

Costs of gold ball bumping vs. plating

Domestic Bumping industry 苏州颀中Chipmore

上海宏茂Chipmos

上海安靠Amkor

星科金朋SCC

江阴长电JCAP

苏州晶方WLCSP

中芯国际SMIC

上海宏茂Chipmos & 苏州欣中Chipmore -TCP&COG&COF for LCD Driver IC -Gold bumps

上海安靠Amkor

-put into production

-gold &solder bumping

星科金朋SCC

-Bumping service from TSMC

-Gold +Ni bumping & solder bumping

•JCAP Bumping Services

苏州Shellcase

-Shellcase WLCSP process & Wafer bumping process & TSV WLCSP process

氮气回流焊炉(for WAFER BUMP FORMING) -YAMATO WORKS (120000 USD)

深圳敏科))

系列回流焊炉炉(深圳敏科HELLER 1800EXL系列回流焊

岗)大型全热风无铅回流焊炉-SNR

州圣岗

SNR--845P(苏州圣

大型全热风无铅回流焊炉

SEMIgear GENVEA STP200/300。