301KD20NX中文资料

- 格式:pdf

- 大小:123.97 KB

- 文档页数:6

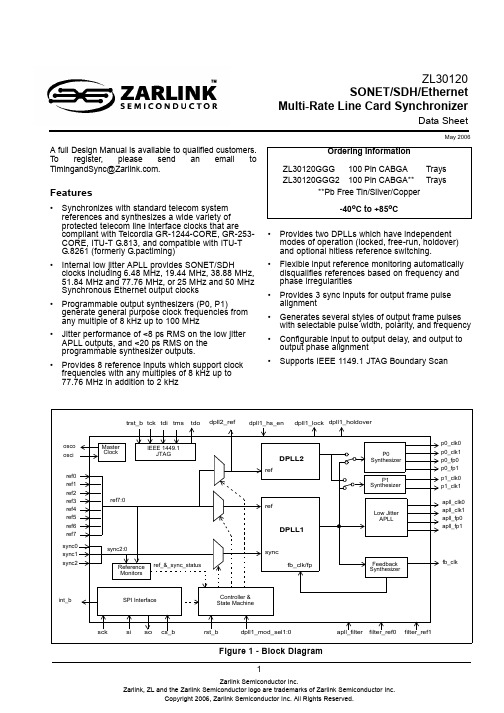

1A full Design Manual is available to qualified customers.To register, please send an email to TimingandSync@.Features•Synchronizes with standard telecom system references and synthesizes a wide variety of protected telecom line interface clocks that are compliant with Telcordia GR-1244-CORE, GR-253-CORE, ITU-T G.813, and compatible with ITU-T G.8261 (formerly G.pactiming)•Internal low jitter APLL provides SONET/SDHclocks including 6.48MHz, 19.44MHz, 38.88MHz, 51.84MHz and 77.76MHz, or 25MHz and 50MHz Synchronous Ethernet output clocks•Programmable output synthesizers (P0, P1)generate general purpose clock frequencies from any multiple of 8kHz up to 100MHz•Jitter performance of <8 ps RMS on the low jitter APLL outputs, and <20 ps RMS on the programmable synthesizer outputs.•Provides 8 reference inputs which support clock frequencies with any multiples of 8kHz up to 77.76MHz in addition to 2kHz•Provides two DPLLs which have independent modes of operation (locked, free-run, holdover) and optional hitless reference switching.•Flexible input reference monitoring automatically disqualifies references based on frequency and phase irregularities•Provides 3 sync inputs for output frame pulse alignment•Generates several styles of output frame pulses with selectable pulse width, polarity, and frequency •Configurable input to output delay, and output to output phase alignment•Supports IEEE 1149.1 JTAG Boundary ScanMay 2006Figure 1 - Block DiagramZL30120SONET/SDH/EthernetMulti-Rate Line Card SynchronizerData SheetOrdering InformationZL30120GGG 100 Pin CABGA Trays ZL30120GGG2100 Pin CABGA**Trays**Pb Free Tin/Silver/Copper-40o C to +85o CZL30120Data SheetApplications•AMCs for AdvancedTCA TM and MicroTCA Systems•Synchronous Ethernet•Multi-Service Edge Switches or Routers•DSLAM Line Cards•WAN Line Cards•RNC/Mobile Switching Center Line Cards•ADM Line CardsZL30120Data SheetTable of Contents1.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.1 DPLL Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111.2 DPLL Mode Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121.3 Ref and Sync Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131.4 Ref and Sync Monitoring. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141.5 Output Clocks and Frame Pulses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151.6 Configurable Input-to-Output and Output-to-Output Delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .172.0 Software Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183.0 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25ZL30120Data SheetList of FiguresFigure 1 - Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Automatic Mode State Machine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Figure 3 - Reference and Sync Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 4 - Output Frame Pulse Alignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 5 - Behaviour of the Guard Soak Timer during CFM or SCM Failures. . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 6 - Output Clock Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 7 - Phase Delay Adjustments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17ZL30120Data SheetList of TablesTable 1 - DPLL1 and DPLL2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Table 2 - Set of Pre-Defined Auto-Detect Clock Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 3 - Set of Pre-Defined Auto-Detect Sync Frequencies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 4 - Output Clock and Frame Pulse Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16ZL30120Data Sheet Pin DescriptionPin # Name I/OType DescriptionInput ReferenceC1 B2 A3 C3 B3 B4 C4 A4ref0ref1ref2ref3ref4ref5ref6ref7I d Input References (LVCMOS, Schmitt Trigger). These are input referencesavailable to both DPLL1 and DPLL2 for synchronizing output clocks. All eightinput references can be automatically or manually selected using softwareregisters. These pins are internally pulled down to Vss.B1 A1 A2sync0sync1sync2I d Frame Pulse Synchronization References (LVCMOS, Schmitt Trigger).These are the frame pulse synchronization inputs associated with inputreferences 0, 1 and 2. These inputs accept frame pulses in a clock format (50%duty cycle) or a basic frame pulse format with minimum pulse width of 5ns.These pins are internally pulled down to V ss.Output Clocks and Frame PulsesD10apll_clk0O APLL Output Clock 0 (LVCMOS). This output can be configured to provide anyone of the available SONET/SDH clock outputs up to 77.76MHz, or 25MHz and50MHz. The default frequency for this output is 77.76MHz.G10apll_clk1O APLL Output Clock 1 (LVCMOS). This output can be configured to provide anyone of the available SONET/APLL clock outputs up to 77.76MHz, or 25MHz and50MHz. The default frequency for this output is 19.44MHz.E10apll_fp0O APLL Output Frame Pulse 0 (LVCMOS). This output can be configured toprovide virtually any style of output frame pulse synchronized with an associatedAPLL output clock. The default frequency for this frame pulse output is 8kHz.F10apll_fp1O APLL Output Frame Pulse 1 (LVCMOS). This output can be configured toprovide virtually any style of output frame pulse synchronized with an associatedAPLL output clock. The default frequency for this frame pulse output is 2kHz.K9p0_clk0O Programmable Synthesizer 0 - Output Clock 0 (LVCMOS). This output can beconfigured to provide any frequency with a multiple of 8kHz up to 100MHz inaddition to 2kHz. The default frequency for this output is 2.048MHz.K7p0_clk1O Programmable Synthesizer 0 - Output Clock 1 (LVCMOS). This is aprogrammable clock output configurable as a multiple or division of the p0_clk0frequency within the range of 2kHz to 100MHz. The default frequency for thisoutput is 8.192MHz.K8p0_fp0O Programmable Synthesizer 0 - Output Frame Pulse 0 (LVCMOS). This outputcan be configured to provide virtually any style of output frame pulse associatedwith the p0 clocks. The default frequency for this frame pulse output is 8kHz.J7p0_fp1O Programmable Synthesizer 0 - Output Frame Pulse 1 (LVCMOS). This outputcan be configured to provide virtually any style of output frame pulse associatedwith the p0 clocks. The default frequency for this frame pulse output is 8kHz.ZL30120Data SheetJ10p1_clk0OProgrammable Synthesizer 1 - Output Clock 0 (LVCMOS). This output can be configured to provide any frequency with a multiple of 8kHz up to 100MHz in addition to 2kHz. The default frequency for this output is 1.544MHz (DS1).K10p1_clk1OProgrammable Synthesizer1 - Output Clock 1 (LVCMOS). This is aprogrammable clock output configurable as a multiple or division of the p1_clk0 frequency within the range of 2kHz to 100MHz. The default frequency for this output is 3.088MHz (2x DS1).H10fb_clk OFeedback Clock (LVCMOS). This output is a buffered copy of the feedback clock for DPLL1. The frequency of this output always equals the frequency of the selected reference.E1dpll2_ref ODPLL2 Selected Output Reference (LVCMOS). This is a buffered copy of the output of the reference selector for DPLL2. Switching between input reference clocks at this output is not hitless.Control H5rst_bIReset (LVCMOS, Schmitt Trigger). A logic low at this input resets the device. To ensure proper operation, the device must be reset after power-up. Reset should be asserted for a minimum of 300ns.J5dpll1_hs_enI uDPLL1 Hitless Switching Enable (LVCMOS, Schmitt Trigger). A logic high at this input enables hitless reference switching. A logic low disables hitless reference switching and re-aligns DPLL1’s output phase to the phase of the selected reference input. This feature can also be controlled through software registers. This pin is internally pulled up to Vdd.C2D2dpll1_mod_sel0dpll1_mod_sel1I uDPLL1 Mode Select 1:0 (LVCMOS, Schmitt Trigger). During reset, the levels on these pins determine the default mode of operation for DPLL1 (Automatic, Normal, Holdover or Freerun). After reset, the mode of operation can becontrolled directly with these pins, or by accessing the dpll1_modesel register through the serial interface. This pin is internally pulled up to Vdd.Status H1dpll1_lockOLock Indicator (LVCMOS). This is the lock indicator pin for DPLL1. This output goes high when DPLL1’s output is frequency and phase locked to the input reference.J1dpll1_holdover OHoldover Indicator (LVCMOS). This pin goes high when DPLL1 enters the holdover mode.Serial Interface E2sck I Clock for Serial Interface (LVCMOS). Serial interface clock.F1si I Serial Interface Input (LVCMOS). Serial interface data input pin.G1so O Serial Interface Output (LVCMOS). Serial interface data output pin.E3cs_bI uChip Select for Serial Interface (LVCMOS). Serial interface chip select. This pin is internally pulled up to Vdd.Pin # Name I/O Type DescriptionZL30120Data Sheet G2int_b O Interrupt Pin (LVCMOS). Indicates a change of device status prompting theprocessor to read the enabled interrupt service registers (ISR). This pin is anopen drain, active low and requires an external pulled up to VDD.APLL Loop FilterA6apll_filter A External Analog PLL Loop Filter terminal.B6filter_ref0A Analog PLL External Loop Filter Reference.C6filter_ref1A Analog PLL External Loop Filter Reference.JTAG and TestJ4tdo O Test Serial Data Out (Output). JTAG serial data is output on this pin on thefalling edge of tck. This pin is held in high impedance state when JTAG scan isnot enabled.K2tdi I u Test Serial Data In (Input). JTAG serial test instructions and data are shifted inon this pin. This pin is internally pulled up to Vdd. If this pin is not used then itshould be left unconnected.H4trst_b I u Test Reset (LVCMOS). Asynchronously initializes the JTAG TAP controller byputting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up to ensure that the device is in the normal functional state. This pin is internallypulled up to Vdd. If this pin is not used then it should be connected to GND.K3tck I Test Clock (LVCMOS): Provides the clock to the JTAG test logic. If this pin is notused then it should be pulled down to GND.J3tms I u Test Mode Select (LVCMOS). JTAG signal that controls the state transitions ofthe TAP controller. This pin is internally pulled up to V DD. If this pin is not usedthen it should be left unconnected.Master ClockK4osci I Oscillator Master Clock Input (LVCMOS). This input accepts a 20MHzreference from a clock oscillator (TCXO, OCXO). The stability and accuracy ofthe clock at this input determines the free-run accuracy and the long termholdover stability of the output clocks.K5osco O Oscillator Master Clock Output (LVCMOS). This pin must be left unconnectedwhen the osci pin is connected to a clock oscillator.MiscellaneousA9 A10 B5 B9 B10 C5 D1 D3 G3NC No Connection. Leave unconnected.Pin # Name I/OType DescriptionZL30120Data Sheet J2J6H7K1IC Internal Connection. Connect to ground.F2F3K6IC Internal Connection. Leave unconnected.Power and GroundD9 E4 G8 G9 J8 J9 H6 H8V DD PPPPPPPPPositive Supply Voltage. +3.3V DC nominal.E8 F4V CORE PPPositive Supply Voltage. +1.8V DC nominal.A5 A8 C10AV DD PPPPositive Analog Supply Voltage. +3.3V DC nominal.B7 B8 H2AV CORE PPPPositive Analog Supply Voltage. +1.8V DC nominal.D4 D5 D6 D7 E5 E6 E7 F5 F6 F7 G4 G5 G6 G7 E9 F8 F9 H9V SS GGGGGGGGGGGGGGGGGGGround. 0 Volts.Pin # Name I/OType DescriptionZL30120Data SheetI - InputI d -Input, Internally pulled down I u -Input, Internally pulled up O -Output A -Analog P -Power G -GroundA7C7C8C9D8H3AV SSG G G G G GAnalog Ground. 0 Volts.Pin # Name I/O Type DescriptionZL30120Data Sheet1.0 Functional DescriptionThe ZL30120 Multi-Rate Line Card Synchronizer is a highly integrated device that provides timing and synchronization for network interface cards. It incorporates two independent DPLLs, each capable of locking to one of eight input references and provides a wide variety of synchronized output clocks and frame pulses.1.1 DPLL FeaturesThe ZL30120 provides two independently controlled Digital Phase-Locked Loops (DPLL1, DPLL2) for clock and/or frame pulse synchronization. DPLL1 is the main DPLL and is always enabled. To save on power, DPLL2 is disabled by default. For applications where DPLL2 is required, it must be enabled using the dpll_en bit of the dpll2_ctrl_0register (0x2A). Table 1 shows a feature summary for both DPLLs.FeatureDPLL1DPLL2Modes of Operation Free-run, Normal (locked), Holdover Free-run, Normal (locked), Holdover Loop Bandwidth User selectable: 14Hz, 28Hz, or wideband 1 (890Hz / 56Hz / 14Hz)1. In the wideband mode, the loop bandwidth depends on the frequency of the reference input. For reference frequencies equal to or greater than 64kHz, the loop bandwidth = 890Hz. For reference frequencies equal to or greater than 8kHz and less than 64 kHz, the loop bandwidth = 56Hz. For reference frequencies equal to 2kHz, the loop bandwidth is equal to 14Hz.Fixed: 14HzPhase Slope Limiting User selectable: 885ns/s, 7.5µs/s, 61µs/s, or unlimited User selectable: 61µs/s, or unlimited Pull-in Range Fixed: 130ppmFixed: 130ppmHoldover ParametersSelectable Update Times: 26ms, 1s, 10s, 60s, and Selectable Holdover Post Filter BW: 18mHz, 2.5Hz, 10Hz. Fixed Update Time: 26ms No Holdover Post FilteringHoldover Frequency AccuracyBetter than 1ppb (Stratum 3E) initial frequency offset. Frequency drift depends on the 20MHz external oscillator.Better than 50ppb (Stratum 3) initial frequency offset. Frequency drift depends on the 20MHz external oscillator.Reference Inputs Ref0 to Ref7Ref0 to Ref7Sync Inputs Sync0, Sync1, Sync2Sync inputs are not supported.Input Reference Selection/Switching Automatic (based on programmable priority and revertiveness), or manual Automatic (based on programmable priority and revertiveness), or manual Hitless Ref Switching Can be enabled or disabledCan be enabled or disabled Output Clocks apll_clk0, apll_clk1, p0_clk0, p0_clk1, p1_clk0, p1_clk1, fb_clk.p0_clk0, p0_clk1, p1_clk0, p1_clk1.Output Frame Pulses apll_fp0, apll_fp1, p0_fp0, p0_fp1 synchronized to active sync reference.p0_fp0, p0_fp1 not synchronized to sync reference.External Pins Status IndicatorsLock, HoldoverNoneTable 1 - DPLL1 and DPLL2 FeaturesZL30120Data Sheet1.2 DPLL Mode ControlBoth DPLL1 and DPLL2 independently support three modes of operation - free-run, normal and holdover. The mode of operation can be manually set or controlled by an automatic state machine as shown in Figure 2.Figure 2 - Automatic Mode State MachineFree-runThe free-run mode occurs immediately after a reset cycle or when the DPLL has never been synchronized to areference input. In this mode, the frequency accuracy of the output clocks is equal to the frequency accuracy of the external master oscillator. Lock AcquisitionThe input references are continuously monitored for frequency accuracy and phase regularity. If at least one of the input references is qualified by the reference monitors, then the DPLL will begin lock acquisition on that input. Given a stable reference input, the ZL30120 will enter in the Normal (locked) mode.Normal (locked)The usual mode of operation for the DPLL is the normal mode where the DPLL phase locks to a selected qualified reference input and generates output clocks and frame pulses with a frequency accuracy equal to the frequency accuracy of the reference input. While in the normal mode, the DPLL’s clock and frame pulse outputs comply with the MTIE and TDEV wander generation specifications as described in Telcordia and ITU-T telecommunication standards.HoldoverWhen the DPLL operating in the normal mode loses its reference input, and no other qualified references are available, it will enter the holdover mode and continue to generate output clocks based on historical frequency data collected while the DPLL was synchronized.ResetAnother reference is qualified and availablefor selectionPhase lock on the selected reference is achievedLock AcquisitionNormal (Locked)No references are qualified and available for selectionFree-RunHoldoverSelected referencefailsAll references are monitored for frequency accuracy and phase regularity, and at least one reference is qualified.Normal (Locked)ZL30120Data Sheet1.3 Ref and Sync InputsThere are eight reference clock inputs (ref0 to ref7) available to both DPLL1 and DPLL2. The selected reference input is used to synchronize the output clocks. Each of the DPLLs have independent reference selectors which can be controlled using a built-in state machine or set in a manual mode.Figure 3 - Reference and Sync InputsIn addition to the reference inputs, DPLL1 has three optional frame pulse synchronization inputs (sync0 to sync2)used to align the output frame pulses. The sync n input is selected with its corresponding ref n input, where n = 0, 1,or 2. Note that the sync input cannot be used to synchronize the DPLL, it only determines the alignment of the frame pulse outputs. An example of output frame pulse alignment is shown in Figure 4.Figure 4 - Output Frame Pulse Alignmentref7:0sync2:0DPLL2DPLL1ref napll/p0/p1_clk xapll/p0_fp xWithout a frame pulse signal at the sync input, the output frame pulses will align to any arbitrary cycle of its associated output clock.sync n - no frame pulse signal presentWhen a frame pulse signal is present at the sync input, the DPLL will align the output frame pulses to the output clock edge that is aligned to the input frame pulse.ref n apll/p0/p1_clk xapll/p0_fp xsync nn = 0, 1, 2x = 0, 1n = 0, 1, 2x = 0, 1ZL30120Data Sheet Each of the ref inputs accept a single-ended LVCMOS clock with a frequency ranging from 2kHz to 77.76MHz. Built-in frequency detection circuitry automatically determines the frequency of the reference if its frequency is within the set of pre-defined frequencies as shown in Table 2. Custom frequencies definable in multiples of 8kHz are also available.2 kHz8 kHz64 kHz1.544 MHz2.048 MHz6.48 MHz8.192 MHz16.384 MHz19.44 MHz38.88 MHz77.76 MHzCustom ACustom BTable 2 - Set of Pre-Defined Auto-Detect Clock FrequenciesEach of the sync inputs accept a single-ended LVCMOS frame pulse. Since alignment is determined from the rising edge of the frame pulse, there is no duty cycle restriction on this input, but there is a minimum pulse width requirement of 5ns. Frequency detection for the sync inputs is automatic for the supported frame pulse frequencies shown in Table 3.166.67 Hz(48x 125 µs frames)400 Hz1 kHz2 kHz8 kHz64 kHzTable 3 - Set of Pre-Defined Auto-Detect Sync Frequencies1.4 Ref and Sync MonitoringAll input references (ref0 to ref7) are monitored for frequency accuracy and phase regularity. New references are qualified before they can be selected as a synchronization source, and qualified references are continuously monitored to ensure that they are suitable for synchronization. The process of qualifying a reference depends on four levels of monitoring.Single Cycle Monitor (SCM)The SCM block measures the period of each reference clock cycle to detect phase irregularities or a missing clock edge. In general, if the measured period deviates by more than 50% from the nominal period, then an SCM failure (scm_fail) is declared.ZL30120Data SheetCoarse Frequency Monitor (CFM)The CFM block monitors the reference frequency over a measurement period of 30µs so that it can quickly detect large changes in frequency. A CFM failure (cfm_fail) is triggered when the frequency has changed by more than 3%or approximately 30000ppm.Precise Frequency Monitor (PFM)The PFM block measures the frequency accuracy of the reference over a 10 second interval. To ensure an accurate frequency measurement, the PFM measurement interval is re-initiated if phase or frequency irregularities are detected by the SCM or CFM. The PFM provides a level of hysteresis between the acceptance range and the rejection range to prevent a failure indication from toggling between valid and invalid for references that are on the edge of the acceptance range.When determining the frequency accuracy of the reference input, the PFM uses the external oscillator’s output frequency (f ocsi ) as its point of reference. Guard Soak Timer (GST)The GST block mimics the operation of an analog integrator by accumulating failure events from the CFM and the SCM blocks and applying a selectable rate of decay when no failures are detected.As shown in Figure 5, a GST failure (gst_fail) is triggered when the accumulated failures have reached the upper threshold during the disqualification observation window. When there are no CFM or SCM failures, the accumulator decrements until it reaches its lower threshold during the qualification window.Figure 5 - Behaviour of the Guard Soak Timer during CFM or SCM FailuresAll sync inputs (sync0 to sync2) are continuously monitored to ensure that there is a correct number of reference clock cycles within the frame pulse period.1.5 Output Clocks and Frame PulsesThe ZL30120 offers a wide variety of outputs including two low jitter LVCMOS (apll_clk0, apll_clk1) output clocks and four programmable LVCMOS (p0_clk0, p0_clk1, p1_clk0, p1_clk1) output clocks. In addition to the clock outputs, two LVCMOS frame pulse outputs (apll_fp0, apll_fp1) and two LVCMOS programmable frame pulses (p0_fp0, p0_fp1) are also available.The feedback clock (fb_clk ) of DPLL1 is available as an output clock. Its output frequency is always equal to DPLL1’s selected input frequency.refCFM or SCM failuresupper thresholdlower thresholdt d - disqualification timet q - qualification time = n * t dt dt qgst_failZL30120Data SheetThe output clocks and frame pulses derived from the low jitter APLL are always synchronous with DPLL1, and the clocks and frame pulses generated from the programmable synthesizers can be synchronized to either DPLL1 or DPLL2. This allows the ZL30120 to have two independent timing paths.Figure 6 - Output Clock ConfigurationThe supported frequencies for the output clocks and frame pulses are shown in Table 4.apll_clk0, apll_clk1(LVCMOS)11. The apll_clk x outputs can generate either SONET/SDH or Ethernet frequencies (25MHz, 50MHz). p0_clk0, p1_clk0(LVCMOS)p0_clk1, p1_clk1(LVCMOS)apll_fp0, apll_fp1, p0_fp0, p0_fp1(LVCMOS)22. apll_fp x frequencies are available only when the low jitter apll is generating SONET/SDH frequencies6.48 MHz 2 kHz p x _clk0 p x _clk1 =2M166.67 Hz (48x 125 µs frames)9.72 MHz N * 8 kHz (up to 100MHz)400 Hz 12.96 MHz 1 kHz 19.44 MHz 2 kHz 25.92 MHz 4 kHz 38.88 MHz 8 kHz 51.84 MHz 32 kHz 77.76 MHz 64 kHz25 MHz 50 MHzTable 4 - Output Clock and Frame Pulse Frequenciesp0_clk0p0_fp0p0_clk1p0_fp1 P0 Synthesizerp1_clk0p1_clk1P1 Synthesizerapll_clk0apll_fp0apll_clk1apll_fp1Low Jitter APLLFeedback Synthesizerfb_clkDPLL2DPLL1ZL30120Data Sheet1.6 Configurable Input-to-Output and Output-to-Output DelaysThe ZL30120 allows programmable static delay compensation for controlling input-to-output and output-to-output delays of its clocks and frame pulses.All of the output synthesizers (APLL, P0, P1, Feedback) locked to DPLL1 can be configured to lead or lag the selected input reference clock using the DPLL1 Fine Delay . The delay is programmed in steps of 119.2ps with a range of -128 to +127 steps giving a total delay adjustment in the range of -15.26ns to +15.14ns. Negative values delay the output clock, positive values advance the output clock. Synthesizers that are locked to DPLL2 are unaffected by this delay adjustment.In addition to the fine delay introduced in the DPLL1 path, the APLL, P0, and P1 synthesizers have the ability to add their own fine delay adjustments using the P0 Fine Delay , P1 Fine Delay , and APLL Fine Delay . These delays are also programmable in steps of 119.2ps with a range of -128 to +127 steps.In addition to these delays, the single-ended output clocks of the APLL, P0, and P1 synthesizers can be independently offset by 90, 180 and 270 degrees using the Coarse Delay . The output frame pulses (APLL, P0) can be independently offset with respect to each other using the FP Delay .Figure 7 - Phase Delay AdjustmentsDPLL1DPLL2P0 Fine Delayp0_clk0p0_clk1p0_fp0p0_fp1 P0 SynthesizerCoarse DelayCoarse Delay FP Delay FP Delay fb_clkp1_clk0p1_clk1P1 Fine DelayLow Jitter APLLapll_clk0apll_clk1apll_fp0apll_fp1APLL Fine DelayFeedback SynthesizerDPLL1 Fine DelayCoarse DelayCoarse Delay FP Delay FP DelayCoarse Delay Coarse DelayP1 SynthesizerZL30120Data Sheet 2.0 Software ConfigurationThe ZL30120 is mainly controlled by accessing software registers through the serial peripheral interface (SPI). The device can be configured to operate in a highly automated manner which minimizes its interaction with the system’s processor, or it can operate in a manual mode where the system processor controls most of the operation of the device.The following table provides a summary of the registers available for status updates and configuration of the device.Addr (Hex)RegisterNameResetValue(Hex)Description TypeMiscellaneous Registers00id_reg A4Chip and version identification and reset readyindication registerR01use_hw_ctrl00Allows some functions of the device to becontrolled by hardware pinsR/WInterrupts02ref_fail_isr FF Reference failure interrupt service register R 03dpll1_isr70DPLL1 interrupt service register StickyR 04dpll2_isr00DPLL2 interrupt service register StickyR 05ref_mon_fail_0FF Ref0 and ref1 failure indications StickyR 06ref_mon_fail_1FF Ref2 and ref3 failure indications.StickyR 07ref_mon_fail_2FF Ref4 and ref5 failure indications StickyR 08ref_mon_fail_3FF Ref6 and ref7 failure indications StickyR 09ref_fail_isr_mask00Reference failure interrupt service registermaskR/W 0A dpll1_isr_mask00DPLL1 interrupt service register mask R/W 0B dpll2_isr_mask00DPLL2 interrupt service register mask R/W 0C ref_mon_fail_mask_0FF Control register to mask each failure indicatorfor ref0 and ref1R/W0D ref_mon_fail_mask_1FF Control register to mask each failure indicatorfor ref2 and ref3R/W0E ref_mon_fail_mask_2FF Control register to mask each failure indicatorfor ref4 and ref5R/W。

1.1 接线端子说明LXWA-O安装固定完成后,即可进行电源线和信号输出线的接线。

LXWA-O 接线端子在控制器的接线盒内,打开接线盒盖板,对照接线端子说明,按照需要进行电源和信号输出线的接线。

接线端子说明见表4.3.1。

注意: * 通讯端口通过接口上方的跳线配置为RS232或RS485模式: RS232模式: 1-4 OFF, 5-8 ON;RS485模式: 1-4 ON, 5-8 OFF;** 这些端口带有可以对人体造成危险或伤害的高电压,为了您的生命安全,请断电操作。

*** LXWA-O接地线必须按照有关标准可靠接地。

如果没有接地或接地不可靠,有可能造成LXWA-O不稳定或意外危险。

2水样取样和排放蠕动泵对水样的最大自由提升高度为1.5米,样水软管可直接插入污水池中,或者连接到外部取样管路上。

水样排放求自由排放,排放口不带压力,无阻力排放。

图6.1为取样和排放示意图。

(a) 水池取样(b) 管路取样图6.1取样和排放示意图3系统运行在LXWA-O完成安装和外部接线工作,并且检查完水样取样和排放等外围连接,正确无误以后,LXWA-O即可以投入正常使用。

本章主要讲述LXWA-O投运的步骤。

3.1 生物反应器中初始水样的加入生物反应器中初始水样的加入,可以通过直接加入的的方式,即先拔出搅拌电机部分,用容器盛被测量水样400mL,直接倒入生物反应中。

图8.1.1 初始水样的加入初始水样加入后,插入搅拌电机部分,注意,搅拌桨插入时,桨叶应稍微向溶解氧探头相反的方向倾斜。

然后,再按照第5章所述的安装过程将生物反应器安装到LXWA-O上并完成LXWA-O内部的联接。

3.2 LXWA-O通电运行8.1节所述过程完成后,首先要确认供电电源是否正确,如果符合3.1节所述的要求,LXWA-O就可以通电运行。

LXWA-O通电后,有两分钟的初始化过程,然后,LXWA-O进正常的测量过程。

如果初始水样温度较低,LXWA-O有一个加温过程(到30℃约10~30分钟),在此过程中,LXWA-O读数错误或没有读数,如果初始水样是首次加入,还需要经过4~24小时的驯化过程,才能得到正确的读数。

20系列总线应用手册技术中心2012-12-15V1.7Contents1摘要 (3)2硬件规格 (4)2.1框架图 (4)2.2硬件明细 (4)2.3驱动器和电机选型 (5)2.4规格简介 (6)2.4.1引脚定义 (7)3配线 (8)3.1配线图 (8)3.2驱动器重电配线说明 (9)3.2.1急停不控制驱动器重电 (9)3.2.2急停控制驱动器重电 (10)4参数设定 (11)4.1控制器参数设定 (11)4.2驱动器参数设定 (14)4.3驱动器通讯地址设定 (16)5功能介绍 (17)5.1串列参数设置 (17)5.2自动调机 (20)5.3绝对值读取 (24)5.3.1绝对值编码器复位 (24)5.3.1.1绝对值编码器复位方法一 (24)5.3.1.2绝对值编码器复位方法二 (25)5.3.2绝对式原点设定 (26)5.3.2.1人机画面设定绝对式原点 (26)5.3.2.2PLC设定绝对式原点 (27)5.4驱动器警报内容显示 (28)5.5扭力控制(暂无此功能) (29)5.6主轴负载率显示 (30)6Q&A (31)7附件1.驱动器警报说明及处理对策 (33)摘要新代科技20系列控制器搭载安川Mechatrolink-II总线(串行)通讯控制方式,改善传统脉波式泛用型控制器配线及扩充性问题,使系统更简化,更有扩充性,装配更容易。

20系列最多可控制16轴伺服马达同动。

I/O接点除了控制器本身提供的32组Direct Input及Output外,还可透过RIO串行接口连接外部I/O模块。

依IO点需求决定是否增配RIO模块,选择更具弹性。

20系列控制器,除总线通讯外,可控制一组传统脉波式泛用型主轴,兼容P型、V型、变频命令输出,除总线主轴外,也可以有更经济的主轴方案选择总线泛用硬件配线简单复杂单位时间数据传输量多(1Mb/sec以上) 少(500 Kb/sec)各单元间的通信Yes No伺服分辨率高低DDA指令超过警报不用考虑需经计算评估来避免驱动器警报内容显示有无主轴负载率显示有无控制器设置驱动器参数有无驱动器参数备份有无扭力回路有无绝对值读取有无硬件规格2.1框架图2.2硬件明细⏹新代20系列控制器⏹安川SigmaV总线驱动器+电机SGDV-□□□□11A 型(M-II 型)。

DESCRIPTIONSThe Hyper Red source color devices are made with AlGaInP on GaAs substrate Light Emitting Diode Electrostatic discharge and power surge could damage the LEDsIt is recommended to use a wrist band oranti-electrostatic glove when handling the LEDs All devices, equipments and machineries must be electrically groundedFEATURES3.0 x 2.0 x 1.0 mm right angle SMD LED, 1.0 mm thicknessLow power consumption Wide viewing angleIdeal for back light and indicator Package: 2000 pcs / reel Moisture sensitivity level: 3Tinned pads for improved solderability RoHS compliantAPPLICATIONSBacklightStatus indicatorHome and smart appliances Wearable and portable devicesHealthcare applicationsATTENTIONObserve precautions for handlingelectrostatic discharge sensitive devicesPACKAGE DIMENSIONSSELECTION GUIDENotes:1. θ1/2 is the angle from optical centerline where the luminous intensity is 1/2 of the optical peak value.2. Luminous intensity / luminous flux: +/-15%.* Luminous intensity value is traceable to CIE127-2007 standards.KPA-3010SURCK3.0 x 1.0 mm Right Angle SMD Chip LED LampRECOMMENDED SOLDERING PATTERN(units : mm; tolerance : ± 0.1)Part NumberEmitting Color (Material)Lens TypeIv (mcd) @ 20mA [2] Viewing Angle [1]Min.Typ.2θ1/2 KPA-3010SURCK■ Hyper Red (AlGaInP)Water Clear120 220*40 *80120°Notes:1. All dimensions are in millimeters (inches).2. Tolerance is ±0.15(0.006") unless otherwise noted.3. The specifications, characteristics and technical data described in the datasheet are subject to change without prior notice.4. The device has a single mounting surface. The device must be mounted according to the specifications.ELECTRICAL / OPTICAL CHARACTERISTICS at T A =25°CABSOLUTE MAXIMUM RATINGS at T A =25°CParameterSymbol Emitting Color Value Unit Typ. Max. Wavelength at Peak Emission I F = 20mA λpeak Hyper Red 645 - nm Dominant Wavelength I F = 20mA λdom [1] Hyper Red 630 - nm Spectral Bandwidth at 50% Φ REL MAX I F = 20mA Δλ Hyper Red 28 - nm CapacitanceC Hyper Red 35 - pF Forward Voltage I F = 20mA V F [2] Hyper Red 1.95 2.5 V Reverse Current (V R = 5V) I R Hyper Red - 10 µA Temperature Coefficient of λpeak I F = 20mA, -10°C ≤ T ≤ 85°C TC λpeak Hyper Red 0.14 - nm/°C Temperature Coefficient of λdom I F = 20mA, -10°C ≤ T ≤ 85°C TC λdom Hyper Red 0.05 - nm/°C Temperature Coefficient of V F I F = 20mA, -10°C ≤ T ≤ 85°CTC VHyper Red-1.9-mV/°CParameterSymbolValue Unit Power Dissipation P D 75 mW Reverse Voltage V R 5 V Junction Temperature T j 115 °C Operating Temperature T op -40 to +85 °C Storage Temperature T stg -40 to +85°C DC Forward Current I F 30 mA Peak Forward CurrentI FM [1]185 mA Electrostatic Discharge Threshold (HBM) -3000 V Thermal Resistance (Junction / Ambient) R th JA [2] 485 °C/W Thermal Resistance (Junction / Solder point)R th JS [2]375°C/WNotes:1. The dominant wavelength (λd) above is the setup value of the sorting machine. (Tolerance λd : ±1nm. )2. Forward voltage: ±0.1V.3. Wavelength value is traceable to CIE127-2007 standards.4. Excess driving current and / or operating temperature higher than recommended conditions may result in severe light degradation or premature failure.Notes:1. 1/10 Duty Cycle, 0.1ms Pulse Width.2. R t h JA ,R t h JS Results from mounting on PC board FR4 (pad size ≥ 16 mm 2 per pad).3. Relative humidity levels maintained between 40% and 60% in production area are recommended to avoid the build-up of static electricity – Ref JEDEC/JESD625-A and JEDEC/J-STD-033.TECHNICAL DATAHYPER REDTAPE SPECIFICATIONS (units : mm)REEL DIMENSION (units : mm)REFLOW SOLDERING PROFILE for LEAD-FREE SMD PROCESSNotes:1. Don't cause stress to the LEDs while it is exposed to high temperature.2. The maximum number of reflow soldering passes is 2 times.3. Reflow soldering is recommended. Other soldering methods are not recommended as they mightcause damage to the product.PACKING & LABEL SPECIFICATIONSPRECAUTIONARY NOTES1. The information included in this document reflects representative usage scenarios and is intended for technical reference only.2. The part number, type, and specifications mentioned in this document are subject to future change and improvement without notice. Before production usage customer should refer tothe latest datasheet for the updated specifications.3. When using the products referenced in this document, please make sure the product is being operated within the environmental and electrical limits specified in the datasheet. Ifcustomer usage exceeds the specified limits, Kingbright will not be responsible for any subsequent issues.4. The information in this document applies to typical usage in consumer electronics applications. If customer's application has special reliability requirements or have life-threateningliabilities, such as automotive or medical usage, please consult with Kingbright representative for further assistance.5. The contents and information of this document may not be reproduced or re-transmitted without permission by Kingbright.6. All design applications should refer to Kingbright application notes available at https:///application_notes。

20W,AC-DC converterFEATURES●Universal Input:85~264V AC/100~370VDC●AC and DC dual-use(input from the same terminal)●High efficiency,low power consumption,meet energy star standards ●Low ripple&noise ●Compactsize●Output shortcircuit,over-current,over–voltage protection●Mounting:PCB mounting,Chassis mounting,DIN-Rail mounting available●UL60950,EN60950approvalRoHSLD20-10Bxx series -----a 20W compact size power converter offered by MORNSUN,ultra-slim volume.It features universal input voltage,taking both DC and AC input voltage,low power consumption,low ripple&noise,high efficiency,high reliability,3000V AC safer isolation.It offers good EMC performance,meet IEC/EN61000-4,CISPR22/EN55022,UL60950and EN60950standards,and widely used in industrial,electricity,instruments,telecommunication and civil applications.Note:Please refer to Design Reference when module being used in a bad EMC environment.Selection GuideCertificationModel Output PowerNominal Output Voltage and Current(Vo/Io)Efficiency (230V AC,%/Typ.)Max.Capacitive Load(µF)UL/CELD20-10B0311.88W 3.3V/3600mA 7410000LD20-10B0518W5V/3600mA 7810000LD20-10B1220W 12V/1660mA 825400LD20-10B1515V/1330mA 832700LD20-10B2424V/833mA831500Input SpecificationsItemOperating Conditions Min.Typ.Max.Unit Input Voltage Range AC input 85--264V AC DC input100--370VDC Input frequency 47--440Hz Input current 115VAC --370--mA 230V AC --240--Inrush current115VAC --10--A230V AC--20--Recommended External Input Fuse (Special package series include fuse) 3.15A/250V,slow fusing,necessaryHot PlugUnavailableOutput SpecificationsItemOperating Conditions Min.Typ.Max.UnitOutput Voltage Accuracy 0%-100%LD20-10B03--±3--%Other models--±2--Line Regulation Full load --±0.5--Load Regulation0%-100%load--±1--Ripple&Noise*20MHz bandwidth(peak-peak value)--50120mV Temperature Coefficient--±0.02--%/°C Stand-by Power Consumption----0.3W Short Circuit Protection Continuous,self-recoveryOver-current Protection110%-250%Io,self-recoveryOver-voltage Protection Zener clamp diodeMin.Load0----%Hold-up Time 115V AC input--10--ms 230V AC input--55--Note:*Ripple and noise tested with“parallel cable”method,Testing at rated load.please see AC-DC Converter Application Notes for specific operation methods.General SpecificationsItem Operating Conditions Min.Typ.Max.Unit Isolation Voltage Input-output Test time:1min3000----VAC Operating Temperature-25--+70°C Storage Temperature-25--+105Storage Humidity----95%RHWelding Temperature Wave-soldering260±5℃;time:5~10s Manual-welding360±10℃;time:3~5sSwitching Frequency--100--kHzPower Derating +40℃~+70℃LD20-10B03/05 2.66----%/℃Others 2.33-----25℃~0℃ 1.0----Safety Standard IEC60950/EN60950/UL60950Safety-regulated Certification EN60950/UL60950Safety Class CLASS I IMTBF MIL-HDBK-217F@25°C>300,000h Physical SpecificationsCasing Material Black flame-retardant and heat-resistant plastic(UL94-V0)Package Dimensions Horizontal package53.80*28.80*23.50mm A2chassis package96.10*54.00*32.00mm A4Din-Rail package96.10*54.00*36.60mm A2S chassis package76.00*31.50*32.30mm A4S Din-Rail package76.00*31.50*36.90mmWeight Horizontal package/A2chassis package/A4Din-Railpackage/A2S chassis package/A4S Din-Rail package60g/110g/150g/80g/100g(Typ.)Cooling method Free convectionEMC SpecificationsEMICE CISPR22/EN55022,CLASS B RE CISPR22/EN55022,CLASS B EMSESD IEC/EN61000-4-2±6KV/±8KV Perf.Criteria B RS IEC/EN61000-4-310V/m perf.Criteria A EFT IEC/EN61000-4-4±4KV perf.Criteria B Surge IEC/EN61000-4-5±2KVperf.Criteria B IEC/EN61000-4-5±4KV/±6KV (See Fig.2for recommended circuit)perf.Criteria B CS IEC/EN61000-4-610Vr.m.s perf.Criteria A PFMIEC/EN61000-4-810A/m perf.Criteria A Immunities of voltage dip,drop and short interruptionIEC/EN61000-4-110%-70%perf.Criteria BProduct Characteristic Curve-25407010075130~240V AC 160~340VDC In put Voltage :20LD20-10B05Temperature Derat ing CurveO u t p u t P o w e r P e r c e n t a g e (%)Ambient Temperature()℃100802408526470340370100VAC VDC130160LD20-10B05O u t p u t P o w e r P e r c e n t a g e (%)Ambient temp erature:25℃Input Volta geInput Voltage Derat ing Curve0-25407040301007580 100~240VA C 120~340VD C Inp ut Vol tage :Ambient T emperature()℃Temperature Derat ing CurveO u t p u t P o w e r P e r c e n t a g e (%)20 3.3V Output12V/15V/24V O utpu t100801002408526470340120370100VAC VDCOthersInput Voltage Derat ing C urveAmbient temp erature:25℃Input Voltag eO u t p u t P o w e r P e r c e n t a g e (%)Note:①Input voltage should be derated based on temperature derating when it is 85~100VAC/240~264VAC/100~120VDC/340~370VDC (LD20-10B05:85~130VAC/240~264VAC/100~160VDC/340~370VDC);○2This product is suitable for use in natural air cooling environments,if in a closed environment,please contact our company’s FAE.Design Reference1.Typical application circuitA C(L)+Vo-V oAC(L)A C(N )AC (N)C 1C 2T VS RLFU SEAC DCM OV1NT CFig.1ModelFUSE NTCMOV1C1C2TVS LD20-10B03 3.15A/250V,slow fusing,necessary10D-11S20K3001µF/50V220µF/16V SMBJ7.0A LD20-10B05220µF/16V SMBJ7.0A LD20-10B12120µF/25V SMBJ20A LD20-10B15120µF/25V SMBJ20A LD20-10B2468µF/35V SMBJ30ANote:○1Output filtering capacitor C2is electrolytic capacitor,it is recommended to apply electrolytic capacitor with high frequency and low resistance.For capacitance and current of capacitor please refer to manufacture’s datasheet.Capacitance withstand voltage derating should be 80%or above.C1is ceramic capacitor,which is used to filter high-frequency S is a recommended component to protect post-circuits if converter fails.②The product in the application must connect external electrolytic capacitors C2,to achieve lower ripple noise and better dynamic load performance.③When the product’s output terminal is connected to high frequency switch type load,electrolytic capacitor C2’s selection is as following:Model C2LD20-10B03470µF/16V (Solid capacitor)LD20-10B05470µF/16V (Solid capacitor)LD20-10B12390µF/25V LD20-10B15390µF/25V LD20-10B24220µF/35V2.EMC solution-recommended circuitA C (N )A C (L )L C MA C (N )A C (L )A C D CM O V 1M O V 2C XR 1C Y 2C Y 1G D TM O V 3+Vo-V oF U S EC 1C 2T V SR LL D MC a n u s e M O R N S U N 's F C -L X 1D 2Fig 2Note :Output external circuit refer to the typical application circuit.Element modelRecommended valueMOV1S20K300MOV2S10K300MOV3S10K300CX 0.22µF/275VAC CY1/CY22.2nF/400V AC R11M Ω/2W LDM 4.7uHLCM 10mH,recommended to use MORNSUN’s FL2D-Z5-103GDT4EM3600XSFUSE 3.15A/250V,slow fusing,necessaryFC-LX1D2EMC filter3.For more information about Mornsun EMC Filter products,please visit todownload the Selection Guide of EMC FilterDimensions and Recommended Layout LD20-10BxxA2DimensionsLD20-10BxxA2S DimensionsNote:1.Packing Information please refer to'Product Packaging Information'.The Packing bag number of Horizontal package:58220011,the Packing bag number of A2/A4package:58220010,the Packing bag number of A2S/A4S package:58220022;2.Unless otherwise specified,data in this datasheet should be tested under the conditions of Ta=25°C,humidity<75%when inputtingnominal voltage and outputting rated load;3.All index testing methods in this datasheet are based on our Company’s corporate standards;4.The performance indexes of the product models listed in this manual are as above,but some indexes of non-standard model productswill exceed the above-mentioned requirements,and please directly contact our technician for specific information;5.We can provide product customization service;6.Specifications of this product are subject to changes without prior notice.Mornsun Guangzhou Science&Technology Co.,Ltd.Address:No.5,Kehui St.1,Kehui Development Center,Science Ave.,Guangzhou Science City,Luogang District,Guangzhou,P.R.China Tel:86-20-38601850-8801Fax:86-20-38601272E-mail:***************。

Hydraulic Shop PressSHIPPING DAMAGE CLAIMSWhen this equipment is shipped, title passes to the purchaser upon receipt from the carrier. Consequently, claims for the material damaged in shipment must be made by the purchaser against the transportation company at the time shipment is received.BE SAFERanger™ Shop Presses are designed and built with safety in mind. However, proper training and thoughtful operation on the part of the operator can increase your overall safety. DO NOT operate or repair this equipment without reading this manual and the important safety instructions shown inside.WARRANTY POLICYRanger Products™ are backed by over 35 years of manufacturing experience. Every Shop Press bearing the Ranger™ name is sold with the following warranty. Each Ranger Product™ is warranted to be free from defects in workmanship and material for a period of one year from the date of shipment provided that a written claim for such defect is made within that time.This warranty does not cover damage or defects caused by carelessness of the operator, misuse, abuse or abnormal use which in any way impairs the proper functioning of the equipment or by the use or addition of parts not manufactured by RangerProducts™ or its suppliers.THIS WARRANTY IS EXPRESSLY MADE IN LIEU OF ANY AND ALL OTHER WARRANTIES EXPRESSED OR IMPLIED INCLUDING THE WARRANTIES OF MERCHANTABILITY AND FITNESS FOR APARTICULAR PURPOSE.If your Ranger Products™ machine is not functioning properly, call your Ranger Products™ dealer immediately. On some occasions, an independent contractor may be hired to do the repairs. Within the warranty period, a customer should not hire his own contractor unless it is authorized in writing by Ranger Products™.If it is necessary to return equipment for repairs, your dealer will so advise you. When returning equipment for repairs, see that machines are properly crated and protected, and prepay transportation.Defective parts replaced at no charge must be returned to your dealer or Ranger Products™ within 60 days of the date that the replacement parts are shipped; otherwise, you must pay for the replacement parts at the current selling price.SHIPPING DAMAGEIf any damage is found, notify your carrierimmediately and save all packaging materials for the carrier’s inspector to examine. Failure to promptly report damage could result in denial of your claim. A trucking company’s procedure for handling damage is as follows: 1. Immediately send out an inspector. An inspection report is filled out on the spot, a copy of which isgiven to the customer.2. The customer has to call the carrier to request a claim form.3. The customer mails in the claim form.4.The claim usually takes two (2) months to process.If a unit is seriously damaged, your Ranger Products dealer may be able to intervene, requesting that the damaged unit be returned and a new unit delivered.IMPORTANT SAFETY TIPSALWAYS MAINTAIN A CLEAN WORK AREA.KEEP VISITORS AND ESPECIALLY CHILDREN AWAY FROM WORK AREA.THIS SHOP PRESS IS TO BE OPERATED BY PROPERLY TRAINED PERSONNEL ONLY.OPERATION BY UNTRAINEDPERSONNEL MAY RESULT IN INJURYAND /OR PROPERTY DAMAGE.For Parts Or Service Contact:BendPak Inc. / Ranger Products1645 Lemonwood Dr.Santa Paula, CA. 93060T el: 1-805-933-9970Toll Free: 1-800-253-2363Fax: THIS OPERATING MANUAL CONTAINSIMPORTANT DETAILS CONCERNING THE SAFE OPERATION OF THIS EQUIPMENT. THE USER MUST READ AND UNDERSTAND THESE DETAILS BEFORE ANY USE OF THE EQUIPMENT. THIS MANUAL MUST BE RETAINED FOR FUTURE REFERENCE.OWNER/OPERATOR RESPONSIBILITY:The owner and/or operator shall study the product instructions and retain them for future reference. The owner and/or operator shall have an understanding of the product operating instructions and warnings beforeoperating the equipment. Warning information shall be emphasized and understood. If the operator is not fl uent in English, the product instructions and warnings shall be read to and discussed with the operator in the operator’s native language by the purchaser/ owner or his designee, making sure that the operator comprehends its contents.INSPECTIONVisual inspection should be made before each use of the equipment. This inspection should check for abnormal conditions such as cracked welds, leaks, and damaged, loose or missing parts.Any product that appears to be damaged in any way, is found to be worn or operated abnormally, must be removed from service immediately.Any product that operates abnormally shall be removed from service until repaired by a quali fi ed repair service center.If the product is accidentally subjected to an abnormal load or shock, it must be taken out of service immediately and be inspected by a quali fi ed repair or service center. It is recommended that an annual inspection is performed on the equipment and that any damaged or worn parts, decals or warning labels be replaced with manufacturer’s speci fi ed parts.ALTERATIONSBecause of potential hazards associated with this type of equipment, no alterations shall be made to the product.WARNING!T HIS IS A PRESSING DEVICE ONLY. DO NOT EXCEED RATED CAPACITY. OVERLOADING CAN CAUSE DAMAGE TO OR FAILURE OF THE SHOP PRESS.KEEP HANDS AND BODY CLEAROF ALL PINCH POINTS.NO ALTERATIONS TO THE PRESS SHALL BE MADE. READ, STUDY AND UNDERSTAND THE OPERATINGMANUAL PACKED WITH THIS LIFT BEFOREOPERATING.ALWAYS WEAR APPROVED EYE PROTECTION DURING OPERATION.FAILURE TO HEED THESE WARNINGS MAY RESULT IN LOSS OF LOAD, DAMAGE TO THE PRESS , AND/OR FAILURE RESULTING IN PROPERTY DAMAGE,PERSONAL OR FATAL INJURY.washers. See Figure 1.5. Attach the Pump Assembly (16) to the side of the right side Post using the supplied bolts, nuts and lock washers. (See Figure 2)For Parts Or ServiceContact:BendPak Inc. / Ranger Products1645 Lemonwood Dr.Santa Paula, CA. 93060Tel: 1-805-933-9970Toll Free: 1-800-253-2363Fax: 1-805-933-9160。

NX420 Single Board Computer User Guide Rev 1.3August 10, 2007Table of ContentsFederal Communications Commission Statement (1)CE Declaration of Conformity (1)Recycling and Disposal (1)1.0 Hardware (2)1.1 CHASSIS (2)1.2 BIOS (2)2.0 External Connectors and Indicators (3)2.1 Ethernet RJ-45 Connectors (3)2.2 Console Port (3)2.3 USB 2.0 Port 1 & 2 Connector (4)2.4 Power Input (4)2.5 Power & Hard Drive LEDs (5)2.6 Ethernet LEDs (5)3.0 Internal Connectors and Jumpers (6)3.1 Serial Port 2 10 Pin Header (6)3.2 AUX Power (6)3.3 PCI 3.3V (7)3.4 User I/O (9)3.5 USB 2.0 Port 3 & 4 (9)3.6 PS2 Keyboard and Mouse (10)3.7 2.5” and 3.5” Hard Drive Connector (10)3.8 Mini PCI (12)4.0 Internal Jumpers (15)4.1 Compact Flash Master/Slave (15)4.2 Reset (15)4.3 Speaker (15)4.4 JTAG Programming Port (16)4.5 SPI (16)5.0 PCB (17)Federal Communications Commission StatementThis device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a commercial installation. This equipment generates, uses, and can radiate radio energy. If this equipment is not installed and used in accordance with the manufacturer’s instructions, it might cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference, If this equipment does cause harmful interference to radio or television reception, which can be determined by Turning the equipment off and on, the user is required to correct the interference at there expense.Shielded cables are required on LAN and serial ports to assure compliance with FCC regulations.This board is designed for installation in a metal enclosure.CE Declaration of ConformityWe, NetX86, Inc., declare that NX420 series boards, when installed in a NetX86 metal enclosure, are in conformance with:- EN 55022/EN 55024 (emissions, residential and industrial)The unit under test is in conformity with the standards mentioned above. A copy of the test report will be provided on requestRecycling and DisposalDo not discard electronic products in household trash!All waste electronics equipment should be recycled according to local regulations. Information for the recycler:Remove Lithium battery, if present, for separate recycling.NetX86 enclosures are made of steel.This document specifies the features and operation of the NX410 Single Board Computer using the Vortex86SX SOC.1.0 Hardware•300MHz 486SX SOC.•3x 10/100 PCI Ethernet Controllers. 3x RJ-45 Connector with integrated LEDs.•Standard 3.3V/5V PCI connector.•2x RS-232 Serial Ports. 1 DB9, 1 internal•2x Mini PCI connectors. Internal.•Compact Flash connector. Internal.•2x USB 2.0. Duplex connector, Internal 2x4 header, 0.1”x0.1”.•44 pin ATA connector for 2.5” hard drive.•40 pin IDE connector for CD drive.•10x I/O pins. Internal 2x5 header, 0.1”x0.1”.•256MB of DDR2.•Real Time Clock•7-12VDC input 16VDC max. 2.1mm barrel connector.•6” x 6” PCB, 0.062” thick, components two sides.•0 to 70°C operating temp.•Optional -20 to 70°C operating temp.•RoHS Lead free•FCC Class A•CE1.1 CHASSIS•Steel 0.039” Thick•Mounting bracket for 2.5” drive option•Rubber feet•Handles PCI Cards up to 4” High by 6” Long•Two plugged holes for SMA Antenna connectors1.2 BIOS•AMI BIOS•Boots to Serial Port•115200 baud2.0 External Connectors and IndicatorsThis section describes the connectors and LEDs that are accessible to the user during normal operation.2.1 Ethernet RJ-45 ConnectorsThree Ethernet ports provide 10/100 Mb connectivity. The Ethernet controllers are on the PCI bus. Each has a dedicated EEPROM for PCIconfiguration data.The RJ-45 connectors have built in LEDS to indicate Link and Activity.The Green LED on the left indicates Link. The Yellow LED on the right turns on blinks OFF when there is Activity.J1, J2 & J3 - RJ-45RJ-45 Pin Name Description1 TX+ Transmit Data +2 TX- Transmit Data -3 RX+ Receive Data +4 TERM 75 ohm Termination5 TERM 75 ohm Termination6 RX- Receive Data -7 TERM 75 ohm Termination8 TERM 75 ohm Termination2.2 Console PortCom1 provides the main console connection to the CPU. Default speed is 115,200 bps 8 bit, no parity, 1 Stop bit. Use a null modem to connect to a PC.The BIOS will boot to this port as the default.J4 - Male DB-9 ConnectorDB-9 Pin Name Description1 DCD Data Carrier Detect2 RX- Receive Data3 TX- Transmit Data4 DTR Data Terminal Ready5 GND Ground6 DSR Data Set ready7 RTS Ready to Send8 CTS Clear to Send9 RI Ring Indicate2.3 USB 2.0 Port 1 & 2 ConnectorTwo of the four available USB 2.0 ports are stacked in the same housing.USB port 1 is on the top with USB port 2 on the bottom.The power to the two ports is protected by a shared Polymer PTC fuse to prevent over current conditions harming the unit. The fuse will reset after the short is removed.J5 – USB 1 & 2 Dual Stacked ConnectorDual USB Jack Name Description1A +5V +5 V USB Supply2A Data 1 - USB Data 1 -3A Data 1 + USB Data 1 +4A GND Circuit Ground1B +5V +5 V USB Supply2B Data 2 - USB Data 2 -3B Data 2 + USB Data 2 +4B GND Circuit Ground2.4 Power Input12 Volt input is connected to center pin and ground to the barrel. Themating connector has a 5.5mm Diameter barrel and 2.1mm hole. Thisconnector is polarity protected.J6 – DC Input Power Connector2.1mm Jack Name Description1 +12 V Center Pin2 GND Barrel2.5 Power & Hard Drive LEDsA Green LED indicator is driven from the +3.3V Power Supply.A Yellow LED turns on to indicate the master or slave Hard Drives isactive. The Hard Drives are Compact Flash, 2.5” or 3.5” hard drives.The Green LED is above the Yellow LED.LED1 - Power & Hard DriveLED Color Name DescriptionGreen Power On when unit is PoweredYellow HDD On when Hard Drives are active2.6 Ethernet LEDsA Green LED indicator is on when Link is established.A Yellow LED turns off to indicate data is being transmitted or received.The Green LED is above the Yellow LED.LED4 – For LAN1 J3LED3 – For LAN2 J2LED2 – For LAN3 J1LED Color Name DescriptionGreen Link On when Link is detectedYellow Activity On when data is sent or received3.0 Internal Connectors and JumpersThis section covers the connectors on the PCB for other functions.3.1 Serial Port 2 10 Pin HeaderSerial Port 2 is connected to a 10 pin male header such that a standard10 pin IDC connector connects directly to an IDC DB-9 connector with 9 wireribbon cable.J8 - Serial Port 2 Header2x5 0.1” HeaderName DescriptionPin1 DCD Data Carrier Detect2 DSR Data Set ready3 RX- Receive Data4 RTS Ready to Send5 TX- Transmit Data6 CTS Clear to Send7 DTR Data Terminal Ready8 RI Ring Indicate9 GND Ground10 NC No Connect3.2 AUX PowerThis connector allows for the powering of an internal device such as a3.5” Hard Drive or the application of 12V power when J6 is not used. The Boardwill run from 5V when pin 3 and 4 are connected to each other.J9 - Auxiliary Power InputMTA 100 Pin Name Description1 GND Circuit Ground2 GND Circuit Ground3 +12V +12V Input /Output4 +5V +5 V Input/Output5 GPIO 4 GPIO 4 from SoC6 GPIO 0 GPIO 0 from SoC3.3 PCI 3.3VThis horizontal connector allows for the addition of a half length PCI card given a chassis that will support it. This connector shares the PCIresources of the second Mini PCI connector J16.Note: PCI connector J7 is usable only when the second Mini PCI connector J16 next to it, is not used.J7 - 3.3V PCI ConnectorPin # Name PCI Pin DescriptionPin#Name PCI Pin DescriptionA1 TRST Test Logic Reset B1 -12V -12 VDCA2 +12V +12 VDC B2 TCK Test ClockA3 TMS Test Mde Select B3 GND GroundA4 TDI Test Data Input B4 TDO Test Data Output A5 +5V +5 VDC B5 +5V +5 VDCA6 INTA Interrupt A B6 +5V +5 VDCA7 INTC Interrupt C B7 INTB Interrupt BA8 +5V +5 VDC B8 INTD Interrupt DA9 ----- Reserved B9 PRSNT1 PresentA10 +5V Power (+5 V or +3.3 V) B10 ----- ReservedA11 ----- Reserved B11 PRSNT2 PresentA12 GND03 Ground or Keyway for3.3/Universal PWBB12 GNDGround or Keyway for 3.3/UniversalPWBA13 GND05 Ground or Keyway for3.3/Universal PWBB13 GNDGround or Open (Key) for3.3/Universal PWBA14 3.3Vaux ----- B14 RES ReservedA15 RESET Reset B15 GND GroundA16 +5V Power (+5 V or +3.3 V) B16 CLK ClockA17 GNT Grant PCI use B17 GND GroundA18 GND08 Ground B18 REQ RequestA19 PME# Power Management Event B19 +5V Power (+5 V or +3.3 V)A20 AD30 Address/Data 30 B20 AD31 Address/Data 31A21 +3.3V01 +3.3 VDC B21 AD29 Address/Data 29A22 AD28 Address/Data 28 B22 GND GroundA23 AD26 Address/Data 26 B23 AD27 Address/Data 27A24 GND10 Ground B24 AD25 Address/Data 25A25 AD24 Address/Data 24 B25 +3.3V +3.3VDCA26 IDSEL Initialization Device Select B26 C/BE3 Command, Byte Enable 3 A27 +3.3V03 +3.3 VDC B27 AD23 Address/Data 23A28 AD22 Address/Data 22 B28 GND GroundA29 AD20 Address/Data 20 B29 AD21 Address/Data 21A30 GND12 Ground B30 AD19 Address/Data 19A31 AD18 Address/Data 18 B31 +3.3V +3.3 VDCA32 AD16 Address/Data 16 B32 AD17 Address/Data 17A33 +3.3V05 +3.3 VDC B33 C/BE2 Command, Byte Enable 2A34 FRAME Address or Data phase B34 GND13 GroundA35 GND14 Ground B35 IRDY# Initiator ReadyA36 TRDY# Target Ready B36 +3.3V06 +3.3 VDCA37 GND15 Ground B37 DEVSEL Device SelectA38 STOP Stop Transfer Cycle B38 GND16 GroundA39 +3.3V07 +3.3 VDC B39 LOCK# Lock busA40 ----- Reserved B40 PERR# Parity ErrorA41 ----- Reserved B41 +3.3V08 +3.3 VDCA42 GND17 Ground B42 SERR# System ErrorA43 PAR Parity B43 +3.3V09 +3.3 VDCA44 AD15 Address/Data 15 B44 C/BE1 Command, Byte Enable 1A45 +3.3V10 +3.3 VDC B45 AD14 Address/Data 14A46 AD13 Address/Data 13 B46 GND18 GroundA47 AD11 Address/Data 11 B47 AD12 Address/Data 12A48 GND19 Ground B48 AD10 Address/Data 10A49 AD9 Address/Data 9 B49 GND20 GroundA50 Keyway Open or Ground for 3.3V PWB B50 Keyway Open or Ground for 3.3V PWB A51 Keyway Open or Ground for 3.3V PWB B51 Keyway Open or Ground for 3.3V PWB A52 C/BE0 Command, Byte Enable 0 B52 AD8 Address/Data 8A53 +3.3V11 +3.3 VDC B53 AD7 Address/Data 7A54 AD6 Address/Data 6 B54 +3.3V12 +3.3 VDCA55 AD4 Address/Data 4 B55 AD5 Address/Data 5A56 GND21 Ground B56 AD3 Address/Data 3A57 AD2 Address/Data 2 B57 GND22 GroundA58 AD0 Address/Data 0 B58 AD1 Address/Data 1A59 +5V Power (+5 V or +3.3 V) B59 VCC08 Power (+5 V or +3.3 V)A60 REQ64 Request 64 bit B60 ACK64 Acknowledge 64 bitA61 VCC11 +5 VDC B61 VCC10 +5 VDCA62 VCC13 +5 VDC B62 VCC12 +5 VDC3.4 User I/OThis connector allows for the user to utilize the I/O pins of the SOC for advanced functions. J10 is a 12 pin male header.J10 - User I/O Header2x6 0.1” HeaderName DescriptionPin1 +3.3V +3.3 V Logic Supply2 +5V +5 V Logic Supply3 GPIO 0 GPIO 0 from SoC4 GPIO 1 GPIO 1 from SoC5 GPIO 2 GPIO 2 from SoC6 GPIO 3 GPIO 3 from SoC7 GPIO 4 GPIO 4 from SoC8 GPIO 5 GPIO 5 from SoC9 GPIO 6 GPIO 6 from SoC10 GPIO 7 GPIO 7 from SoC11 GND Circuit Ground12 GND Circuit Ground3.5 USB 2.0 Port 3 & 4The third and fourth USB ports are pined out to this male header.J11 - USB Port 3 & 4 Header2x4 0.1” Header Name Description1 +5V +5 V USB Supply2 +5V +5 V USB Supply3 Data 3 - USB Data 3 -4 Data 4 - USB Data 4 -5 Data 3 + USB Data 3 +6 Data 4 + USB Data 4 +7 GND Circuit Ground8 GND Circuit Ground3.6 PS2 Keyboard and MouseThe PS2 interface for a mouse and keyboard is pinned out on male header J12.J12 – PS2 Keyboard & Mouse6x1 0.1” Header Name Description1 KBDAT Keyboard Data2 MSDAT Mouse Data3 GND Circuit Ground4 +5V +5 V Supply5 KBCLK Keyboard Clock6 MSCLK Mouse Clock3.7 2.5” and 3.5” Hard Drive ConnectorThe hard drive connectors are male, shrouded and keyed connectors.The 3.5” ATA connector is a 0.1” connector and the 44 pin connector is 2mm.J13 – 40 Pin ATAJ14 - 44 Pin ATAATA 40 Pin ATA 44 Pin Name Description1 1 /RESET Reset2 2 GND Ground3 3 DD7 Data 74 4 DD8 Data 85 5 DD6 Data 66 6 DD9 Data 97 7 DD5 Data 58 8 DD10 Data 109 9 DD4 Data 410 10 DD11 Data 1111 11 DD3 Data 312 12 DD12 Data 1213 13 DD2 Data 214 14 DD13 Data 1315 15 DD1 Data 116 16 DD14 Data 1417 17 DD0 Data 018 18 DD15 Data 1519 19 GND Ground20 20 key (nc) -21 21 DMARQ DMA Request22 22 GND Ground23 23 /DIOW Write Strobe24 24 GND Ground25 25 /DIOR Read Strobe26 26 GND Ground27 27 IORDY I/O Ready28 28 Device Cfg Spindle Sync or Cable Select29 29 /DMACK DMA Acknowledge30 30 GND Ground31 31 INTRQ Interrupt Request32 32 /IOCS16 IO ChipSelect 1633 33 DA1 Address 134 34 PDIAG Passed Diagnostics35 35 DA0 Address 036 36 DA2 Address 237 37 /IDE_CS0 (1F0-1F7)38 38 /IDE_CS1 (3F6-3F7)39 39 /ACTIVE - /DASI - DASP Led driver40 40 GND Ground-- 41 VCC +5 V-- 42 VCC +5 V-- 43 GND Ground-- 44 GND Ground3.8 Mini PCITwo Mini PCI connectors provide dual 802.11 radio support. The second connector shares PCI resources with J7.J15 – Mini PCI Type IIIJ16 - Mini PCI Type IIIPIN # Signal DescriptionPIN#Signal Description1 TIP 1 Conductor, local loopwire pair63 3.3V 3.3 V Supply voltage- Key - 64 FRAME# Indicates Bulk Transfer2 RING 1 Conductor, local loopwire pair65 CLKRUN#Stops clock on certain mobilePCI devices3 8PMJ-3 Pin 3 of an 8-pin modularjack66 TRDY# Target Ready4 8PMJ-1 Pin 1 of an 8-pin modularjack67 SERR# Catastrophic system error5 8PMJ-6 Pin 6 of an 8-pin modularjack68 STOP# Target wishes to end transfer6 8PMJ-2 Pin 2 of an 8-pin modularjack69 GROUND Ground7 8PMJ-7 Pin 7 of an 8-pin modularjack70 3.3V 3.3 V Supply voltage8 8PMJ-4 Pin 4 of an 8-pin modularjack71 PERR# Indicates Parity Error9 8PMJ-8 Pin 8 of an 8-pin modularjack72 DEVSEL# PCI Device Select10 8PMJ-5 Pin 5 of an 8-pin modularjack73 C/BE[1]# Byte Enable11 LED1_GRNP Interface for externalLEDs74 GROUND Ground12 LED2_YELP Interface for externalLEDs75 AD[14] Multiplexed Address/Data Bus13 LED1_GRNN RF Silent input 76 AD[15] Multiplexed Address/Data Bus14 LED2_YELN Interface for externalLEDs77 GROUND Ground15 CHSGND Chassis Ground 78 AD[13] Multiplexed Address/Data Bus16 RESERVED - 79 AD[12] Multiplexed Address/Data Bus17 INTB# Interrupt Request B 80 AD[11] Multiplexed Address/Data Bus18 5V 5 V Supply voltage 81 AD[10] Multiplexed Address/Data Bus19 3.3V 3.3 V Supply voltage 82 GROUND Ground20 INTA# Interrupt Request A 83 GROUND Ground21 RESERVED - 84 AD[09] Multiplexed Address/Data Bus22 RESERVED - 85 AD[08] Multiplexed Address/Data Bus23 GROUND Ground 86 C/BE[0]# Byte Enable24 3.3VAUX 3.3 V supply-uninterrupted87 AD[07] Multiplexed Address/Data Bus25 CLK PCI Clock 88 3.3V 3.3 V Supply voltage26 RST# PCI Reset 89 3.3V 3.3 V Supply27 GROUND Ground 90 AD[06] Multiplexed Address/Data Bus28 3.3V 3.3 V Supply voltage 91 AD[05] Multiplexed Address/Data Bus29 REQ# PCI Bus Request 92 AD[04] Multiplexed Address/Data Bus30 GNT# PCI Bus Grant 93 RESERVED -31 3.3V 3.3 V Supply voltage 94 AD[02] Multiplexed Address/Data Bus32 GROUND Ground 95 AD[03] Multiplexed Address/Data Bus33 AD[31] Multiplexed Address/DataBus96 AD[00] Multiplexed Address/Data Bus34 PME# Power Management Event 97 5V 5 V Supply voltage35 AD[29] Multiplexed Address/DataBus98 RESERVED_WIP5 -36 RESERVED - 99 AD[01] Multiplexed Address/Data Bus37 GROUND Ground 100 RESERVED_WIP5 -38 AD[30] Multiplexed Address/DataBus101 GROUND Ground39 AD[27] Multiplexed Address/DataBus102 GROUND Ground40 3.3V 3.3 V Supply voltage 103 AC_SYNC AC97 Sync41 AD[25] Multiplexed Address/DataBus104 M66EN Enables 66 MHz PCI bus42 AD[28] Multiplexed Address/DataBus105 AC_SDATA_IN AC97 Data Input43 RESERVED - 106 AC_SDATA_OUT AC97 Data Output44 AD[26] Multiplexed 107 AC_BIT_CLK AC97 Bit Clock45 C/BE[3]# Byte Enable 108 AC_CODEC_ID0# Identifier for AC97 CODEC46 AD[24] Multiplexed Address/DataBus109 AC_CODEC_ID1# Identifier for AC97 CODEC47 AD[23] Multiplexed Address/DataBus110 AC_RESET# AC97 Reset48 IDSEL Initialization DeviceSelect111 MOD_AUDIO_MON Modern Audio Monitor49 GROUND Ground 112 RESERVED -50 GROUND Ground 113 AUDIO_GND Analog Ground for line-levelaudio51 AD[21] Multiplexed Address/DataBus114 GROUND Ground52 AD[22] Multiplexed Address/DataBus115 SYS_AUDIO_OUT Telephone Audio Out53 AD[19] Multiplexed Address/DataBus116 SYS_AUDIO_IN Telephone Audio In54 AD[20] Multiplexed Address/Data 117 SYS_AUDIO_OUT Analog Ground for telephoneBus GND audio55 GROUND Ground 118 SYS_AUDIO_IN GND Analog Ground for telephoneaudio56 PAR Parity Bit 119 AUDIO_GND Analog Ground for line-levelaudio57 AD[17] Multiplexed Address/DataBus120 AUDIO_GNDAnalog Ground for line-levelaudio58 AD[18] Multiplexed Address/DataBus121 RESERVED -59 C/BE[2]# Byte Enable 122 MPCIACT# MiniPCI Function Active60 AD[16] Multiplexed Address/DataBus123 VCC5VA 5V Analog61 IRDY# Initiator Ready 124 3.3VAUX 3.3 V supply-uninterrupted62 Ground Ground - - -4.0 Internal JumpersThis section covers the Jumpers on the PCB for other functions. 4.1 Compact Flash Master/SlaveThis 2 pin male header when shorted makes the Compact Flash the Master and when open makes it the Slave drive.Jp1 – CF Master/Slave2x1 0.1” Header Name Description1 GND Ground2 Slave Pin39 of the CF connector.4.2 ResetThis 2 pin male header when shorted resets the CPU.Jp2 – CPU Reset2x1 0.1” Header Name Description1 GND Ground2 Reset Resets VCC3 Watchdog4.3 SpeakerThis 2 pin male header connects to a speaker or buzzer.Jp3 – Speaker Out2x1 0.1” Header Name Description1 VCC 5Volts2 Drive Open Collector driver with a 22 ohm resistor4.4 JTAG Programming PortThis 6 pin male 1.25mm connects to the Jtag port of the SOC.Jp4 – JTAG Programming Port6x1 1.25mmName DescriptionHeader1 VCC 5Volts2 GND Ground3 TCK Test Clock Input4 TDO Test Data Out5 TDI Test Data In6 TMS Test Mode Select4.5 SPIThis 6 pin male header provides connection to the SOC SPI port. The SPI pins on this connector are shared with an on board SPI temp IC which is notstuffed.Jp5 – SOC SPI2x3 0.1” Header Name Description1 VCC 5Volts2 GND Ground3 SPICLK SPI Clock Out4 SPIDO SPI Data Out5 SPIDI SPI Data In6 SPICS SPI Chip Select5.0 PCB Layout of PCB。

reServer J2032datasheetIntroductionr eServer for Jetson is a powerful inference server on edge powered by the NVIDIA Jetson NX16GB.With rich extension modules,industrial peripherals,and thermal management combined with decades of Seeed’s hardware expertise,reServerJ2032is ready to help you accelerate and scale the next-gen AI product emerging diverse AI scenarios.reServer J2032is compatible with the entire NVIDIA Jetson software stack,cloud-native workflows,and industry-leading AI frameworks,helping deliver seamless AI integration.Part listreServer J2032-NVIDIA®Jetson Xavier™NX16GB -Carrier Board-Pre-installed2.5inch256GB SSD -RTC Battery-Aluminum Heatsink Cooling Fan-Bottom Fan-Aluminum Case X1 X1 X1 X1 X1 X1 X1 X112V/5A Power Adapter(without Power Cord) User ManualScrewdriver x1 x1 x1CategoryreServer J2032datasheet (2)Introduction (2)Part list (3)Category (3)Spec (4)Module-Jetson Xavier NX(16GB) (5)Seeed Carrier Board (7)Pre-installed (13)OS (13)Accessories Information (14)Dimension (14)ESD (15)Certification (16)Application (16)More information (16)SpecProcessor Module Jetson Xavier NX16GBAI Perf21TOPSGPUNVIDIA Volta architecture with384NVIDIA CUDA®cores and48Tensor coresCPU6-core NVIDIA Carmel ARM®v8.264-bit CPU6MB L2+4MB L3Memory8GB128-bit LPDDR4x@51.2GB/sStorage16GB eMMC5.1Video Encoder2x4K60|4x4K30|10x1080p60|22x1080p30(H.265)2x4K60|4x4K30|10x1080p60|20x1080p30(H.264) Video Decoder2x8K30|6x4K60|12x4K30|22x1080p60|44x1080p30(H.265)2x4K60|6x4K30|10x1080p60|22x1080p30(H.264) Co-processor Raspberry Pi®RP2040External I/O 2.5G Ethernet Port Converted from PCIe1000M Ethernet Port Native Ethernet interface of Jetson Xavier NX HDMI Interface Support up to HDMI2.0DisplayPort Interface Support up to DP1.4USB3.1GNE2Interface x2Support up to10GbitDC jack Power interface DC12V@5A,2.5mm center pinInternal I/O M.2KEY B connector With USB3.1GEN2,Support5G/4G wireless module MiNi-PCIe connector support LoRa/Series wireless moduleSIM card slotTop layer for Mini-PCIeBottom layer for M.2RTC battery connector RTC battery already installedSATA power connector x2,dataconnector x2Support2.5inch or3.5inch HDD/SSD,up to SATA3 USB TYPE-C connector for NX for NX programming2x5Pin debug Header ActiveBuzzerNetworkGiga Ethernet2.5G Ethernet Port1000M Ethernet PortWireless ConnectionM.2KEY B connector ,Support 5G/4G wireless module Mini-PCIe connector ,support LoRa/Series wireless moduleStorageSupport 2x 2.5''/3.5"SATA (HDD/SSD)2.5inch 256GB SSD x1,up to SATA3already installed LEDLED1:SATA0status LEDSleep mode or no SSD/HDD inserted -----LED OFF SSD/HDD inserted and PHY ready -----LED ON Data transfer status -----LED blinks LED2:SATA1status LED LED3M.2wireless module status LED PowerDC jack Power AdapterDC 12V @5APower button and restart buttonDimensions 132mm*124mm*233mm Operating Environment0℃~60℃Module-Jetson Xavier NX (16GB)Module Technical SpecificationsJetson Xavier NX16GB Module Technical SpecificationsAI Performance21TOPSGPU384-core NVIDIA Volta™GPU with48Tensor CoresCPU6-core NVIDIA Carmel ARM®v8.264-bit CPU6MB L2+4MB L3Memory16GB128-bit LPDDR4x59.7GB/sStorage16GB eMMC5.1Power10W|15W|20WPCIe1x1(PCIe Gen3)+1x4(PCIe Gen4),total144GT/s*CSI CameraUp to6cameras(24via virtual channels)14lanes(3x4or6x2or3x4+1x2or5x2+1x4)MIPI CSI-2D-PHY1.2(up to30Gbps)Video Encode2x4K60|4x4K30|10x1080p60|22x1080p30(H.265)2x4K60|4x4K30|10x1080p60|20x1080p30(H.264)Video Decode2x8K30|6x4K60|12x4K30|22x1080p60|44x1080p30(H.265)2x4K60|6x4K30|10x1080p60|22x1080p30(H.264)Display2multi-mode DP1.4/eDP1.4/HDMI2.0DL Accelerator2x NVDLAVision Accelerator2x PVANetworking10/100/1000BASE-T EthernetMore detail information about Nvidia Jetson Xavier NX module please check Nvidia Official website.Seeed Carrier BoardExternal I/ODC jack Power interfaceThe whole power supply should provide power12V/5A.The DC JACK interface supports an input voltage range of11.5V<Vin<12.8V,more than12.8V will enter the over-voltage protection state,at which time the whole power supply will automatically disconnect,and when the input voltage is lower than12.8V will automatically resume normal power supply.When inserted into the power supply error,the buzzer will alarm if the voltage is too high or too low.With over-voltage protection,just unplug the power supply and use the correct power.When the input power of the whole machine is less than12V/3A,it may cause the mechanical hard disk to start/work abnormally.USB3.1GNE2Interface x2Support up to10Gbit(with Xavier NX module).Attention:USB current carrying capacity is1AThe two USB TYPE-A ports support output currents of5V/1A respectively,when the USB TYPE-A port peripheral pulls a current greater than1A,it will enter the over-current protection state,re-inserting the USB device can automatically exit the over-current protection state.The two USB TYPE-A port states are independent of each other.HDMI InterfaceSupport up to HDMI2.0.Hot Plug Support.DisplayPort InterfaceSupport up to DP1.4.Hot Plug Support.2.5G Ethernet PortPlug and Play.Converted from PCIe.RX:2.35Gbits/secTX:1.4~1.6Gbits/sec1000M Ethernet PortPlug and Play.Supports10/100/1000Gigabit Ethernet.Internal I/O Top view:Bottom view260Pin SODDR4connector--T6To install the Jetson Xavier NX module correctly,follow the suggested assembly guidelines.1.Assemble any required thermal solution on the module.2.Install the moduleInsert module fully at an angle of25-35degree into the SODIMM connector.Arc down the module board until the SODIMM connector latch engages.Secure the module to the baseboard with screws into the standoff/spacer.To remove the module correctly,follow the reverse of the installation sequence.M.2KEY B connector--T2With M.2USB3.1GEN2,UART0,M.2I/O,support5G/4G wireless module.M.2and Mini PCIe can be used at the same time,these two signals are independent.Mini-PCIe connector--B1With Mini PCIe USB2.0,SPI,I2C,I/O,UART1,support LoRa/Series wireless module M.2and Mini PCIe can be used at the same time,these two signals are independent.SIM card slot--B5Top layer for Mini-PCIeBottom layer for M.2Communication modules need to be used with sim card,3G/4G/5G modules need SIM card to register on the network,without SIM card,it can not register on the network or communicate.Main Fan connector--T3For enclosure bottom fan,only supports12V fans.The bottom fan is already installed.Main FAN(Bottom fan)and Jetson Xavier NX FAN must be connected properly, otherwise,the fan will be damaged.These two fans are self-starting at power on and can be controlled by the program.Jetson Xavier NX Fan Connector--T10Only supports5V fans,Aluminum heatsink cooling fan already installedMain FAN(Bottom fan)and Jetson Xavier NX FAN must be connected properly, otherwise,the fan will be damaged.These two fans are self-starting at power on and can be controlled by the program.RTC battery connector--T5It can accommodate RTC backup battery with1.25mm pitch connector,one RTC battery(JST1.0CR20323V)already installed.This RTC battery keeps the SBC's real-time clock powered and counting.SATA power connector x2,SATA data connector x2--T11,T7Support2.5inch or3.5inch HDD/SSD,up to SATA3.r eServer's SATA theoretically does not support hot-swapping.Power off and then plug in the drive and power it up again.If you use hot-swapping there is no guarantee that data will not be lost.USB TYPE-C connector for NX--B2For installing NVIDIA System Jetpack.USB TYPE-C connector for coprocessor--B3For coprocessor RP2040firmware upgrade.AutoPower on Header--T14Short-circuit to enter key-on mode,Float into auto power-on mode.Power Button with Green LED--T13When using the carrier board alone and Short-circuit to enter key-on mode,press this key to power on.2x5Pin debug Header--T8Install NVIDIA System:Connect FC REC and GND using jumpers to enter forced recovery mode when installing NVIDIA SystemWorks as a terminal:Connects TX and RX,connects to computer and works as a terminal.Detailed operation please check wiki.F-Panel Header--T12Connect to reServer J2032Power Button.Active Buzzer--T1The buzzer will alarm when the power is inserted incorrectly and the voltage is too high or too low.Its status can be changed by programming.LED--T4,T9LED1:SATA0status LED Sleep mode or no SSD/HDD inserted-----LED OFFSSD/HDD inserted and PHY ready-----LED ONLED2:SATA1status LEDData transfer status-----LED blinksLED3M.2wireless module status LEDCoprocessorRaspberry Pi®RP204032-Bit Dual ARM Cortex-M0+@133MHz.RP2040controls the5V/SATA power on and off on the board.Encryption●Encryption ICATECC608A-MAHDA-S encryption IC with I2C interface.AT24C02C-SSHM-T EEPROM with I2C interface.Only the chip is provided,the function of encryption needs to be developed by the user.●Disk EncryptionDisk encryption encrypts a whole disk or partition to protect the data it contains. Jetson Linux offers disk encryption that is based on Linux Unified Key Setup(LUKS). For more information,please check Tegra Linux Driver.Power12V/5A Power Adapter(without power cord).Power Button&Restart button.Press“Power Button”to boot up reServer J2032.Pre-installed● 2.5inch256GB SSD x1,up to SATA3x1●RTC battery x1●Aluminum Heatsink Cooling Fan x1●Bottom Fan x1OS●Jetpack4.6.1● 2.5G network port driver(Depends on the kernel version of L4T.The kernel ofjetpack5.0.2supports rt8125driver,you don't need to install it again,but the Jetpack4.6.1with4.9kernel doesn't support it)●RP2040FirmwareThe above mentioned has been pre-installed,if you need to reflash your device please refer to the wiki.Accessories InformationPlease kindly know that the accessories below are not included in the package.We provide the information here to help you choose the appropriate accessories.AccessoriesInformation Note Product Name Remarks4Gmodule EC25/EC20Tested with Quectel (manufacturer)module 5GmoduleSIM8202G Tested with Simcom (manufacturer)moduleLoRa ModuleWM1302LoRaWAN Gateway Module (USB/SPI)US/EUWM1302LoRaWAN Gateway ModuleDimensionESDStep Pin Voltage OK/FAIL1DC12V PORT-4KV OK2DC12V PORT+4KV OK3DC12V PORT-8KV OK4DC12V PORT+8KV OK5ETH PORT-4KV OK6ETH PORT+4KV OK7ETH PORT-8KV OK8ETH PORT+8KV OK9USB Type A-4KV OK10USB Type A+4KV OK11USB Type A-8KV OK12USB Type A+8KV OK13Power Button-4KV OK14Power Button+4KV OK15Power Button-8KV OK16Power Button+8KV OK17DP+HDMI PORT-4KV OK18DP+HDMI PORT+4KV OK19DP+HDMI PORT-8KV OK20DP+HDMI PORT+8KV OK21USB Type C-4KV OK22USB Type C+4KV OK23USB Type C-8KV OK24USB Type C+8KV OK Contact discharge±4KV,air discharge±8KV.Certification●FCC●CE●UKCA●ROHS●REACHApplication●AI-enabled NVR(Network Video Recorder)●Intelligent Video Analytics●AMR●AIoT Gateway with5G and LoraMore informationPlease check our Wiki and ask question at our Forum or Discord community.For more information,you can also refer to NVIDIA official Jetson Download Center。