ACTR5504中文资料

- 格式:pdf

- 大小:65.57 KB

- 文档页数:3

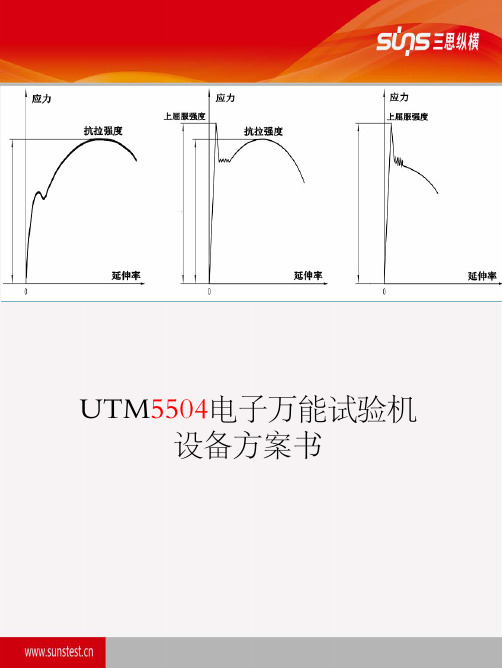

UTM 5504电子万能试验机设备方案书UTM5504电子万能试验机应用金属薄板拉伸带位移计压缩复合材料三点弯曲金属材料高温拉伸复合材料高低温拉伸螺栓拉伸主机结构特点•制造坚固耐用:粗大的滚珠丝杠,更粗壮的导向光杠和强有力的驱动系统是三思试验机提供可靠、可重复试验的保障•适用与高强度材料试验的坚固刚性机架,预加载轴承和高精密滚珠丝杠、加厚横梁及底座横梁,以及较低张紧度传动带,可以最大程度的减少试验过程存储的能量,从而得到更好的测试性能以及获取更为精确的模量和应变值。

在试验高强度材料,例如航空复合材料、金属合金时效果尤为显著•优异的对中和弯曲的精确引导,在进行轴向试验时,只有具有稳定、精准的刚性导柱的系统才能得到精准的应力和应变结果,以确保试样在载荷作用下受到的侧向力影响为最小•更大的电机,更高的可靠性,具备储备功率的大功率电机使机架更具可靠性•伺服控制驱动系统,双皮带驱动的刚性钢铸体保证丝杠的同步运动,并有助与系统对中设备性能特点(二)•试验数据的重复性高(离散性小)•为您的试验室赢得更多声誉•为您降低产品成本,增加利润•出色的刚度和对中度高刚度的机械设计在重复试验的条件下仍可确保尽可能最佳的工作状态并得出可靠结果全数字闭环控制系统•DSP+MCU的优化组合,即有DSP的快速运算,同时集成了MCU对I/O控制能力的优点,其整体性能明显优于单纯的DSP或32位单片机。

•正真实现了以硬件为基础的并行采样模式•三闭环(应力、应变、位移)控制功能底层实现软件功能用户权限分级管理功能•根据其权限开放不同软件功能•超级用户进行用户权限管理试验管理功能•两步轻松完成试验•可根据不同的标准编辑相应的试验方案试验曲线界面及试验报告模板试验曲线界面试验报告模板UTM5504电子万能试验机技术指标一、主机主要参数•(一)测量参数•1、最大试验力:__50__k N;•2、准确度等级:0.5级;•3、试验力测量范围:0.4%~100%F.S(最大负荷);•4、试验力示值误差:示值的±0.5%以内;•5、试验力分辨率:最高可达1/300000,全程不分档,且全程分辨率不变;•6、位移示值误差:示值的±0.5%以内;•7、位移分辨率:0.04μm。

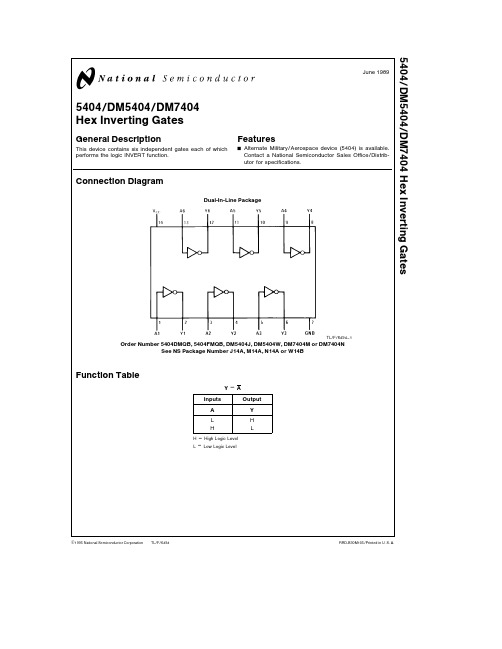

TL F 64945404 DM5404 DM7404 Hex Inverting GatesJune1989 5404 DM5404 DM7404Hex Inverting GatesGeneral DescriptionThis device contains six independent gates each of whichperforms the logic INVERT functionFeaturesY Alternate Military Aerospace device(5404)is availableContact a National Semiconductor Sales Office Distrib-utor for specificationsConnection DiagramDual-In-Line PackageTL F 6494–1Order Number5404DMQB 5404FMQB DM5404J DM5404W DM7404M or DM7404NSee NS Package Number J14A M14A N14A or W14BFunction TableY e AInputs OutputA YL HH LH e High Logic LevelL e Low Logic LevelC1995National Semiconductor Corporation RRD-B30M105 Printed in U S AAbsolute Maximum Ratings(Note)If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Supply Voltage7V Input Voltage5 5V Operating Free Air Temperature RangeDM54and54b55 C to a125 C DM740 C to a70 C Storage Temperature Range b65 C to a150 C Note The‘‘Absolute Maximum Ratings’’are those values beyond which the safety of the device cannot be guaran-teed The device should not be operated at these limits The parametric values defined in the‘‘Electrical Characteristics’’table are not guaranteed at the absolute maximum ratings The‘‘Recommended Operating Conditions’’table will define the conditions for actual device operationRecommended Operating ConditionsSymbol ParameterDM5404DM7404Units Min Nom Max Min Nom MaxV CC Supply Voltage4 555 54 7555 25V V IH High Level Input Voltage22V V IL Low Level Input Voltage0 80 8V I OH High Level Output Current b0 4b0 4mA I OL Low Level Output Current1616mA T A Free Air Operating Temperature b55125070 C Electrical Characteristicsover recommended operating free air temperature range(unless otherwise noted)Symbol Parameter Conditions MinTypMax Units (Note1)V I Input Clamp Voltage V CC e Min I I e b12mA b1 5VV OH High Level Output V CC e Min I OH e Max2 43 4VVoltage V IL e MaxV OL Low Level Output V CC e Min I OL e Max0 20 4VVoltage V IH e MinI I Input Current Max V CC e Max V I e5 5V1mA Input VoltageI IH High Level Input Current V CC e Max V I e2 4V40m AI IL Low Level Input Current V CC e Max V I e0 4V b1 6mAI OS Short Circuit V CC e Max DM54b20b55mA Output Current(Note2)DM74b18b55I CCH Supply Current with V CC e Max612mA Outputs HighI CCL Supply Current with V CC e Max1833mA Outputs LowSwitching Characteristics at V CC e5V and T A e25 C(See Section1for Test Waveforms and Output Load) Symbol Parameter Conditions Min Max Unitst PLH Propagation Delay Time C L e15pF22ns Low to High Level Output R L e400Xt PHL Propagation Delay Time15ns High to Low Level OutputNote1 All typicals are at V CC e5V T A e25 CNote2 Not more than one output should be shorted at a time23Physical Dimensions inches(millimeters)14-Lead Ceramic Dual-In-Line Package(J)Order Number5404DMQB or DM5404JNS Package Number J14A4Physical Dimensions inches(millimeters)(Continued)14-Lead Small Outline Molded Package(M)Order Number DM7404MNS Package Number M14A14-Lead Molded Dual-In-Line Package(N)Order Number DM7404NNS Package Number N14A55404 D M 5404 D M 7404H e x I n v e r t i n g G a t e sPhysical Dimensions inches (millimeters)(Continued)14-Lead Ceramic Flat Package (W)Order Number 5404FMQB or DM5404WNS Package Number W14BLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implant support device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectivenessbe reasonably expected to result in a significant injury to the userNational Semiconductor National Semiconductor National Semiconductor National Semiconductor CorporationEuropeHong Kong LtdJapan Ltd1111West Bardin RoadFax (a 49)0-180-530858613th Floor Straight Block Tel 81-043-299-2309。

AO4704AO4704SymbolTyp Max 28405475R θJL 2130SymbolTyp Max 36406775R θJL 2530Maximum Junction-to-LeadCSteady-State°C/WParameterUnits Maximum Junction-to-AmbientAt ≤ 10s R θJA °C/W Maximum Junction-to-AmbientASteady-State °C/W °C/W Maximum Junction-to-AmbientASteady-State Thermal Characteristics: Schottky Maximum Junction-to-Lead CSteady-State°C/WThermal Characteristics ParameterUnits Maximum Junction-to-AmbientAt ≤ 10s R θJA °C/W A: The value of R θJA is measured with the device mounted on 1in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any given application depends on the user's specific board design. The current rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using 80 µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating.F. The Schottky appears in parallel with the MOSFET body diode, even though it is a separate chip. Therefore, we provide the net forward drop, capacitance and recovery characteristics of the MOSFET and Schottky. However, the thermal resistance is specified for each chip separately.Rev5: August 2005THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISINGOUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.AO4704SymbolMin TypMaxUnits BV DSS 30V0.0070.053.2101220I GSS 100nA V GS(th)0.6 1.12V I D(ON)40A 9.111.5T J =125°C13.316.510.513m Ωg FS 3037S V SD 0.450.5V I S5A DYNAMIC PARAMETERS C iss 36564050pF C oss 322pF C rss 168pF R g0.86 1.1ΩSWITCHING PARAMETERS Q g (4.5V)30.536nC Q gs 4.6nC Q gd 8.6nC t D(on) 6.29ns t r 4.87ns t D(off)5575ns t f 7.311ns t rr 20.325ns Q rr8.412.5nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.Gate resistanceGate Drain Charge Body Diode+Schottky Reverse Recovery ChargeI F =13A, dI/dt=100A/µsBody Diode+Schottky Reverse Recovery Time Turn-Off DelayTime V GS =10V, V DS =15V, R L =1.1Ω, R GEN =0ΩTurn-Off Fall TimeTotal Gate Charge Gate Source Charge I F =13A, dI/dt=100A/µs On state drain currentForward TransconductanceDiode + Schottky Forward Voltage I S =1A,V GS =0VV GS =4.5V, V DS =5V Turn-On DelayTime V GS =10V, V DS =15V, I D =13AV GS =0V, V DS =0V, f=1MHzTurn-On Rise Time Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS Parameter Conditions I DSS mA Gate Threshold Voltage Drain-Source Breakdown Voltage I D =250µA, V GS =0VZero Gate Voltage Drain Current.(Set by Schottky leakage)Gate-Body leakage current V DS =V GS I D =250µA V R =30VV DS =0V, V GS = ±12V R DS(ON)Static Drain-Source On-Resistancem ΩV GS =4.5V, I D =12.2AV GS =10V, ID=13AV R =30V, T J =125°CV R =30V, T J =150°C Reverse Transfer Capacitance V DS =5V, I D =13AOutput Capacitance (FET+Schottky)Maximum Body-Diode + Schottky Continuous CurrentV GS =0V, V DS =15V, f=1MHz Input Capacitance A: The value of R θJA is measured with the device mounted on 1in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any given application depends on the user's specific board design. The current rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using 80 µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating.F. The Schottky appears in parallel with the MOSFET body diode, even though it is a separate chip. Therefore, we provide the net forward drop, capacitance and recovery characteristics of the MOSFET and Schottky. However, the thermal resistance is specified for each chip separately Rev5: August 2005.AO4704AO4704。

74ACT04中文资料74ACT04HEX INVERTERApril 1997s HIGH SPEED:t PD =4.5ns (TYP.)at V CC =3.3V sLOW POWER DISSIPATION:I CC =4μA (MAX.)at T A =25o CsCOMPATIBLE WITH TTL OUTPUTS V IH =2V (MIN),V IL =0.8V (MAX)s50?TRANSMISSION LINE DRIVING CAPABILITYsSYMMETRICAL OUTPUT IMPEDANCE:|I OH |=I OL =24mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ?t PHLsOPERATING VOLTAGE RANGE:V CC (OPR)=4.5V to 5.5VsPIN AND FUNCTION COMPATIBLE WITH 74SERIES 04sIMPROVED LATCH-UP IMMUNITYDESCRIPTIONThe ACT04is an advanced high-speed CMOS HEX INVERTER fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology.It is ideal for low power applications mantaining high speed operation similar toequivalent Bipolar Schottky TTL.The internal circuit is composed of 3stages including buffer output,which enables high noise immunity and stabe output.The device is designed to interface directly High Speed CMOS systems with TTL,NMOS and CMOS output voltage levels.All inputs and outputs are equipped with protection circuits against static discharge,giving them 2KV ESD immunity and transient excess voltage.PIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODES :74ACT04B 74ACT04M M(Micro Package)B (Plastic Package)1/7INPUT AND OUTPUT EQUIVALENT CIRCUITABSOLUTE MAXIMUM RATINGSSymbol ParameterValue Unit V CC Supply Voltage -0.5to +7V V I DC Input Voltage -0.5to V CC +0.5V V O DC Output Voltage -0.5to V CC +0.5V I IK DC Input Diode Curr ent ±20mA I OK DC Output Diode Current ±20mA I O DC Output Current ±50mA I CC or I GND DC V CC or Ground Current±300mAT stg Storage Temperature -65to +150o C T LLead Temperature (10sec)300oCAbsolute Maximum Ratings are those values beyond which damage to the device may occur.Functional operation under these condition is not implied.TRUTH TABLEA Y L H HLPIN DESCRIPTIONPIN No SYMBOL NAME AND FUNCTION 1,3,5,9,11,131A to 6A Data Inputs 2,4,6,8,10,121Y to 6Y Data Oututs 7GND Ground (0V)14V CCPositive Supply VoltageRECOMMENDED OPERATING CONDITIONSSymbol ParameterValue Unit V CC Supply Voltage 4.5to 5.5V V I Input Voltage 0to V CC V V O Output Voltage0to V CC VT op Operating Temperature:-40to +85oCdt/dvInput Rise and Fall Time V CC =4.5to 5.5V (note 1)8ns/V1)V IN from 0.8V to 2.0V74ACT042/7CAPACITIVE CHARACTERISTICSSymbolParameterTest ConditionsValueV CC (V)T A =25oC -40to 85oC Min.Typ.Max.Min.Max.C IN Input Capacitance 5.04pF C PDPower Dissipation Capacitance (note 1)5.037pF1)C PD isdefined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load.(Refer to Test Circuit).Ave rage operating current can be obtained by the following equation.I CC (opr)=C PD ?V CC ?f IN +I CC /n (per circuit)AC ELECTRICAL CHARACTERISTICS (C L =50pF,R L =500?,Input t r =t f =3ns)SymbolParameterTest ConditionValueUnitV CC (V)T A =25oC -40to 85o CMin.Typ.Max.Min.Max.t PLH t PHLPropagation Delay Time(*)1.5 4.57.5 1.08.5ns(*)Voltage range is 5V ±0.5VDC SPECIFICATIONSSymbolParameterTest ConditionsValueUnitV CC (V)T A =25oC -40to 85oC Min.Typ.Max.Min.Max.V IH High Level Input Voltage 4.5V O =0.1V or V CC -0.1V 2.0 1.5 2.0V 5.5 2.01.52.0V IL Low Level Input Voltage 4.5V O =0.1V or V CC -0.1V 1.50.80.8V 5.5 1.50.80.8V OHHigh Level Output Voltage4.5V I (*)=V IH or V ILI O =-50μA 4.4 4.49 4.4V5.5I O =-50μA 5.4 5.495.44.5I O =-24mA 3.86 3.765.5I O =-24mA 4.864.76V OLLow Level Output Voltage4.5V I (*)=V IH or V ILI O =50μA 0.0010.10.1V5.5I O =50mA 0.0010.10.14.5I O =24mA 0.360.445.5I O =24mA0.360.44I I Input Leakage Current 5.5V I =V CC or GND ±0.1±1μA I CCT Max I CC /Input 5.5V I =V CC -2.1V 0.61.5mA I CC Quiescent Supply Current5.5V I =V CC or GND 440mA I OLD Dynamic Output Current (note 1,2)5.5V OLD =1.65V max 75mA I OHDV OHD =3.85V min-75mA1)Maximum test duration 2ms,one output loaded at time2)Incident wave switch ing is guaranteed on transmission lines with impe dances as low as 50?.(*)All outputs loaded.74ACT043/774ACT04TEST CIRCUITC L=50pF or equivalent(includes jig and probe capacitance)R L=R1=500?or equiva lentR T=Z OUT of pulse generator(typically50?)WAVEFORM:PROPAGATION DELAYS(f=1MHz) 4/7DIM.mminch MIN.TYP.MAX.MIN.TYP.MAX.a10.510.020B 1.391.650.0550.065b 0.50.020b10.250.010D 200.787E 8.50.335e 2.540.100e315.240.600F 7.10.280I 5.10.201L 3.30.130Z1.272.540.0500.100P001APlastic DIP14MECHANICAL DATA 74ACT045/7DIM.mm inch MIN.TYP.MAX.MIN.TYP.MAX.A 1.750.068a10.10.20.0030.007a2 1.650.064b 0.350.460.0130.018b10.190.250.0070.010C 0.50.019c145(typ.)D 8.558.750.3360.344E 5.86.20.2280.244e 1.270.050e37.620.300F 3.8 4.00.1490.157G 4.6 5.30.1810.208L 0.5 1.270.0190.050M 0.680.026S8(max.)P013GSO14MECHANICAL DATA74ACT046/774ACT04 Information furnished is believed to be accurate and reliable.However,SGS-THOMSON Microelectronics assumesno responsabilit y for the consequences of use of such information nor for any infringemen t of patents or other rights of third parties which may results from its use.No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectr onics.Specifications mention ed in this publication are subject to change without notice.This publication supersede s and replaces all information previously supplied.SGS-THOMSON Microelectr onics products are not auth orized for use as critical compon ents in life support devices or systems without expre ss written approval of SGS-THOMSON Microelectonics.1997SGS-THOMSON Microelectronics-Printed in Italy-All Rights Reserve dSGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia-Brazil-Canada-China-France-Germany-Hong Kong-Italy-Japan-Korea-Malaysia-Malta-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A.7/7。

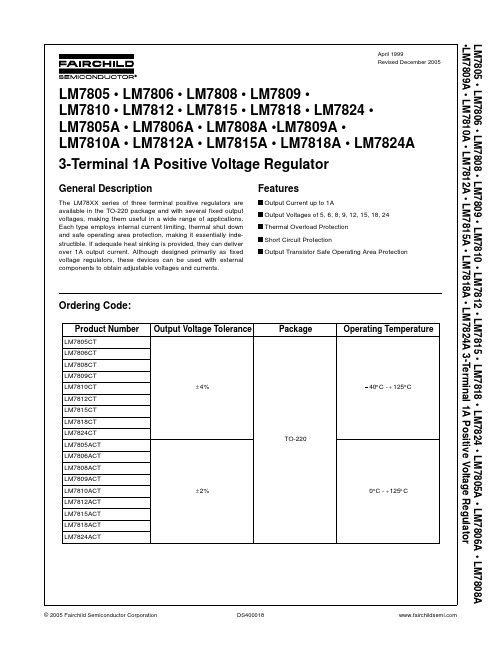

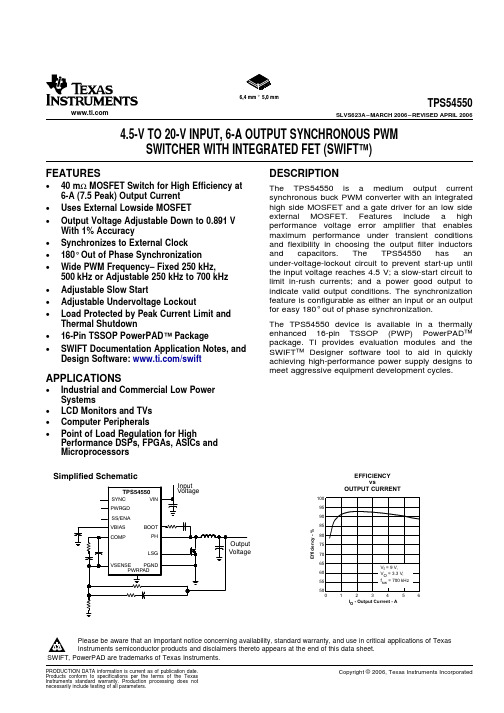

6,4 mm 55,0 mmFEATURES DESCRIPTIONAPPLICATIONSI- Output Current -AOEfficiency-%EFFICIENCYvsOUTPUT CURRENTSimplified SchematicTPS54550SLVS623A–MARCH2006–REVISED APRIL20064.5-V TO20-V INPUT,6-A OUTPUT SYNCHRONOUS PWMSWITCHER WITH INTEGRATED FET(SWIFT™)•40mΩMOSFET Switch for High Efficiency at The TPS54550is a medium output current 6-A(7.5Peak)Output Current synchronous buck PWM converter with an integratedhigh side MOSFET and a gate driver for an low side •Uses External Lowside MOSFETexternal MOSFET.Features include a high •Output Voltage Adjustable Down to0.891Vperformance voltage error amplifier that enables With1%Accuracy maximum performance under transient conditions•Synchronizes to External Clock and flexibility in choosing the output filter inductorsand capacitors.The TPS54550has an •180°Out of Phase Synchronizationunder-voltage-lockout circuit to prevent start-up until •Wide PWM Frequency–Fixed250kHz,the input voltage reaches4.5V;a slow-start circuit to500kHz or Adjustable250kHz to700kHz limit in-rush currents;and a power good output to •Adjustable Slow Start indicate valid output conditions.The synchronizationfeature is configurable as either an input or an output •Adjustable Undervoltage Lockoutfor easy180°out of phase synchronization.•Load Protected by Peak Current Limit andThe TPS54550device is available in a thermally Thermal Shutdownenhanced16-pin TSSOP(PWP)PowerPAD™•16-Pin TSSOP PowerPAD™Packagepackage.TI provides evaluation modules and the •SWIFT Documentation Application Notes,and SWIFT™Designer software tool to aid in quickly Design Software:/swift achieving high-performance power supply designs tomeet aggressive equipment development cycles.•Industrial and Commercial Low PowerSystems•LCD Monitors and TVs•Computer Peripherals•Point of Load Regulation for HighPerformance DSPs,FPGAs,ASICs andMicroprocessorsPlease be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.SWIFT,PowerPAD are trademarks of Texas Instruments.PRODUCTION DATA information is current as of publication date.Copyright©2006,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.PACKAGE DISSIPATION RATINGS (1)TPS54550SLVS623A–MARCH 2006–REVISED APRIL 2006These devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.ORDERING INFORMATIONT jOUTPUT VOLTAGE PACKAGE PART NUMBER (1)-40°C to 125°CAdjustable to 0.891VPlastic HTSSOP (PWP)TPS54550PWP (2)(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TI website at .(2)The PWP package is also available taped and reeled.Add an R suffix to the device type (i.e.,TPS54550PWPR).THERMAL IMPEDANCE T A =25°C T A =70°C T A =85°C PACKAGEJUNCTION-TO-AMBIENTPOWER RATINGPOWER RATINGPOWER RATING16-Pin PWP with solder (2)40.1°C/W2.491.371.00(1)See Figure 22for power dissipation curves.(2)Test Board Conditions a.3inch x 3inchb.Thickness:0.062inchc.2PCB layersd.2oz.Coppere.See Figure 26,Figure 27and TPS54550evaluation module user's guide for layout suggestions.2Submit Documentation FeedbackABSOLUTE MAXIMUM RATINGSELECTROSTATIC DISCHARGE RECOMMENDED OPERATING CONDITIONSTPS54550 SLVS623A–MARCH2006–REVISED APRIL2006over operating free-air temperature range unless otherwise noted(1)UNITVIN-0.3V to21.5VVSENSE-0.3V to8.0VUVLO-0.3V to8.0VV I Input voltage rangeSYNC-0.3V to4.0VSSENA-0.3V to4.0VBOOT VI(PH)+8.0VVBIAS-0.3to8.5VLSG-0.3to8.5VSYNC-0.3to4.0VV O Output voltage range RT-0.3to4.0VPWRGD-0.3to6.0VCOMP-0.3to4.0VPH-1.5V to22VPH Internally Limited(A)I O Source current LSG(Steady State Current)10mACOMP,VBIAS3mASYNC5mALSG(Steady State Current)100mAI S Sink current,PH(Steady State Current)500mACOMP3mASSENA,PWRGD10mA Voltage differential AGND to PGND±0.3VT J Junction temperature+150°CT stg Storage temperature-65°C to+150°C Lead temperature1,6mm(1/16inch)from case for10seconds260°C(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.MIN TYP MAX UNIT Human Body Model HBM JESD22-A114 1.5kV Charged Device Model CDM JESD22-C101 1.5kVMIN NOM MAX UNIT V I Input voltage range 4.520VT J Operating junction temperature-40125°C3Submit Documentation FeedbackELECTRICAL CHARACTERISTICSTPS54550SLVS623A–MARCH 2006–REVISED APRIL 2006T J =-40°C to 125°C,VIN =4.5V to 20V (unless otherwise noted)PARAMETERTEST CONDITIOINSMIN TYP MAX UNITSUPPLY CURRENT Operating Current,PH pin open,10.3mA No external low side MOSFET,RT =Hi-Z I QQuiescent current Shutdown,SSENA =0V1.1mA Start threshold voltage4.324.49V VINStop threshold voltage 3.693.97V Hysteresis350mV UNDER VOLTAGE LOCK OUT (UVLO PIN)Start threshold voltage1.201.24V UVLOStop threshold voltage 1.021.10V Hysteresis100mVBIAS VOLTAGE (VBIAS PIN)I VBIAS =1mA,VIN ≥12V 7.57.88.0VBIASOutput voltageVI VBIAS =1mA,VIN =4.5V 4.4 4.47 4.5REFERENCE SYSTEM ACCURACYT J =25°C0.8880.8910.894V Reference voltage0.8820.8910.899VOSCILLATOR (RT PIN)RT Grounded 200250300Internally set PWM switching frequency kHz RT Open400500600Externally set PWM switching frequency RT =100k Ω(1%resistor to AGND)425500575kHz FALLING EDGE TRIGGERED BIDIRECTIONAL SYNC SYSTEM (SYNC PIN)SYNC out low-to-high rise time (10%/90%)(1)25pF to ground 200500ns SYNC out high-to-low fall time (90%/10%)(1)25pF to ground510ns Delay from rising edge to rising edge of Falling edge delay time (1)180°PH pins Minimum input pulsewidth (1)RT =100k Ω100ns Delay (falling edge SYNC to rising edge PH)(1)RT =100k Ω360ns 50k Ωresistor to ground,SYNC out high level voltage 2.5V No pullup resistorSYNC out low level voltage 0.6V SYNC in low level threshold 0.8V SYNC in high level threshold 2.3V Percentage of programmed frequency-10%10%SYNC in frequency range (1)225770kHz FEED-FORWARD MODULATOR (INTERNAL SIGNAL)Modulator gainVIN =12V,T J =25°C8V/VModulator gain variation -25%25%Minimum controllable ON time (1)180nsMaximum duty factor (1)VIN =4.5V80%86%ERROR AMPLIFIER (VSENSE and COMP PINS)Error amplifier open loop voltage gain (1)6080dB Error amplifier unity gain bandwidth (1) 1.02.8MHz Input bias current,VSENSE pin500nA COMPOutput voltage slew rate (symmetric)(1)1.5V/µs (1)Specified by design,not production tested.4Submit Documentation FeedbackTPS54550 SLVS623A–MARCH2006–REVISED APRIL2006ELECTRICAL CHARACTERISTICS(continued)T J=-40°C to125°C,VIN=4.5V to20V(unless otherwise noted)PARAMETER TEST CONDITIOINS MIN TYP MAX UNIT Slow Start/ENABLE(SSENA PIN)Disable low level input voltage0.5Vf s=250kHz,RT=ground(2) 4.6Internal slow-start time(10%to90%)msf s=500kHz,RT=Hi-Z(2) 2.3Pullup current source 1.8510µAPulldown MOSFET II(SSENA)=1mA0.1V POWER GOOD(PWRGD PIN)Power good threshold Rising voltage97%f s=250kHz4Rising edge delay(2)msf s=500kHz2Output saturation voltage I sink=1mA,VIN>4.5V0.05V PWRGD Output saturation voltage I sink=100µA,VIN=0V0.76V Open drain leakage current Voltage on PWRGD=6V3µA CURRENT LIMITCurrent limit VIN=12V7.58.59.5ACurrent limit Hiccup Time(2)f s=500kHz 4.5ms THERMAL SHUTDOWNThermal shutdown trip point165°CThermal shutdown hysteresis(2)7°C LOW SIDE MOSFET DRIVER(LSG PIN)VIN=4.5V,Capacitive load=1000pF15 Turn on rise time,(10%/90%)(2)nsVIN=8V,Capacitive load=1000pF12 Deadtime(2)VIN=12V60nsVIN=4.5V sink/source7.5 Driver ON resistanceΩVIN=12V sink/source5OUTPUT POWER MOSFETS(PH PIN)Phase node voltage when disabled DC conditions and no load,SSENA=0V0.5VVIN=4.5V,Idc=100mA 1.13 1.42 Voltage drop,low side FET and diode VVIN=12V,Idc=100mA 1.08 1.38VIN=4.5V,BOOT-PH=4.5V,I O=0.5A60r DS(ON)High side power MOSFET switch(3)mΩVIN=12V,BOOT-PH=8V,I O=0.5A40(2)Specified by design,not production tested.(3)Resistance from VIN to PH pins.5Submit Documentation FeedbackPIN ASSIGNMENTSVIN VIN UVLO PWRGDRT SYNC SSENA COMPBOOT PH PH LSG VBIAS PGND AGND VSENSEPWP PACKAGE (TOP VIEW)NOTE:If there is not a Pin 1 indicator, turn device to enable reading the symbol from left to right. Pin 1 is at the lower left corner of the device.TPS54550SLVS623A–MARCH 2006–REVISED APRIL 2006Terminal FunctionsTERMINAL DESCRIPTION 1,2VIN Input supply voltage,4.5V to 20V.Must bypass with a low ESR 10-µF ceramic capacitor.3UVLO Undervoltage lockout pin.Connecting an external resistive voltage divider from VIN to the pin will override the internal default VIN start and stop thresholds.4PWRGD Power good output.Open drain output.A low on the pin indicates that the output is less than the desired output voltage.There is an internal rising edge filter on the output of the PWRGD comparator.5RT Frequency setting pin.Connect a resistor from RT to AGND to set the switching frequency.Connecting the RT pin to ground or floating will set the frequency to an internally preselected frequency.6SYNCBidirectional synchronization I/O pin.SYNC pin is an output when the RT pin is floating or connected low.The output is a falling edge signal out of phase with the rising edge of PH.SYNC may be used as an input tosynchronize to a system clock by connecting to a falling edge signal when an RT resistor is used.See 180°Out of Phase Synchronization operation in the Application Information section.7SSENASlow Start/Enable.The SSENA pin is a dual function pin which provides a logic enable/disable and a slow start time set.Below 0.5V,the device stops switching.Float pin to enable.Capacitor to ground adjusts the slow start time.See Extending Slow Start Time section.8COMP Error amplifier output.Connect frequency compensation network from COMP to VSENSE pins.9VSENSE Inverting node error amplifier.10AGND Analog ground—internally connected to the sensitive analog ground circuitry.Connect to PGND and PowerPAD.11PGND Power Ground—Noisy internal ground—Return currents from the LSG driver output return through the PGND pin.Connect to AGND and PowerPAD.12VBIAS Internal 8.0V bias voltage.A 1.0µF ceramic bypass capacitance is required on the VBIAS pin.13LSG Gate drive for low side MOSFET.Connect gate of n-channel MOSFET.14,15PH Phase node—Connect to external L-C filter.16BOOT Bootstrap for high side gate driver.Connect 24Ohm and 0.1µF ceramic capacitor from BOOT to PH pins.17PowerPADPGND and AGND pins must be connected to the exposed pad for proper operation.See Figure 26for an example PCB layout.6Submit Documentation FeedbackFUNCTIONAL BLOCK DIAGRAMPHLSGPWRGDAGNDPGNDVBIASPOWERPADTPS54550SLVS623A–MARCH 2006–REVISED APRIL 20067Submit Documentation FeedbackDETAILED DESCRIPTIONUndervoltage Lockout(UVLO)Slow Start Enable(SSENA)and Internal SlowT SS_INTERNAL(ms) 1.15kƒs(kHz)(3)Input Voltage SupplyExtending Slow Start TimeR1 VIN(start)1k p1.24V)1k p(1)VIN(stop) (R1)1k p) 1.02V1k p(2)TPS54550SLVS623A–MARCH2006–REVISED APRIL2006StartThe undervoltage lockout(UVLO)system has aninternal voltage divider from VIN to AGND.The Once the SSENA pin voltage exceeds0.5V,the defaults for the start/stop values are labeled VIN and TPS54550starts operation.The TPS54550has an given in Table1.The internal UVLO threshold can be internal digital slow start that ramps the reference overridden by placing an external resistor divider from voltage to its final value in1150switching cycles.The VIN to ground.The internal divider values are internal slow start time(10%-90%)is approximated approximately320kΩfor the high side resistor and by the following expression:125kΩfor the low side resistor.The divider ratio(andtherefore the default start/stop values)is quiteaccurate,but the absolute values of the internalresistors may vary as much as15%.If high accuracy Once the TPS54550device is in normal regulation, is required for an externally adjusted UVLO threshold,the SSENA pin is high.If the SSENA pin is pulled select lower value external resistors to set the UVLO below the stop threshold of0.5V,switching stops ing a1-kΩresistor for the low side and the internal slow start resets.If an application resistor R2(see Figure1)is recommended.Under no requires the TPS54550to be disabled,use open circumstances should the UVLO pin be connected drain or open collector output logic to interface to the directly to VIN.SSENA pin(see Figure2).The SSENA pin has aninternal pullup current source.Do not use external Table1.Start/Stop Voltage Threshold pullup resistors.START VOLTAGE STOP VOLTAGETHRESHOLD THRESHOLDVIN(Default) 4.49 3.69UVLO 1.24 1.02Figure2.Interfacing to the SSENA Pin Figure1.Circuit Using External UVLO FunctionThe equations for selecting the UVLO resistors are:In applications that use large values of outputcapacitance there may be a need to extend the slowstart time to prevent the startup current from trippingthe current limit.The current limit circuit is designedto disable the high side MOSFET and reset theinternal voltage reference for a short amount of time For applications which require an undervoltage lockwhen the high side MOSFET current exceeds the out(UVLO)threshold greater than4.49V,externalcurrent limit threshold.If the output capacitance and resistors may be implemented,see Figure1,to adjustload current cause the startup current to exceed the the start voltage threshold.For example,ancurrent limit threshold,the power supply output will application needing an UVLO start voltage ofnot reach the desired output voltage.To extend the approximately7.8V using the equation(1),R1isslow start time and to reduce the startup current,an calculated to the nearest standard resistor value ofexternal capacitor can be added to the SSENA pin.5.36kΩ.Using Equation2,the input voltage stopThe slow start capacitance is calculated using the threshold is calculated as6.48V.following equation:C SS(µF)=5.55x10-3T ss(ms)8Submit Documentation FeedbackSwitching Frequency(RT)RT(k p)46000ƒs(kHz)–35.9(4)V I(SYNC) V O(PH)TPS54550 SLVS623A–MARCH2006–REVISED APRIL2006The TPS54550has an internal oscillator thatoperates at twice the PWM switching frequency.TheThe RT pin controls the SYNC pin functions.If the RT internal oscillator frequency is controlled by the RTpin is floating or grounded,SYNC is an output.If the pin.Grounding the RT pin sets the PWM switchingswitching frequency has been programmed using a frequency to a default frequency of250kHz.Floatingresistor from RT to AGND,then SYNC functions as the RT pin sets the PWM switching frequency toan input.500kHz.The internal voltage ramp charging current increases Connecting a resistor from RT to AGND sets thelinearly with the set frequency and keeps the feed frequency according to Equation4(see Figure13).forward modulator constant(Km=8)regardless ofthe frequency set point.Table2.Switching Frequency,SYNC and RT PinsSWITCHING FREQUENCY SYNC PIN RT PIN250kHz,internally set Generates SYNC output signal AGND500kHz,internally set Generates SYNC output signal Float Externally set to250kHz to700kHz Terminate to quiet ground with10-kΩR=215kΩto69kΩresistor.Externally synchronized frequency Synchronization Signal Use110kΩwhen RT floats and237kΩwhen RT isgrounded and using the sync out signal of anotherTPS54550.Set RT resistor equal to90%to110%ofexternal synchronization frequency.180°Out of Phase Synchronization(SYNC)When operating the two TPS54550devices180°outof phase,the total RMS input current is reduced. The SYNC pin is configurable as an input or as an Thus reducing the amount of input capacitance output,per the description in the previous section.needed and increasing efficiency.When operating as an input,the SYNC pin is afalling-edge triggered signal(see Figure3and When synchronizing a TPS54550to an external Figure4).When operating as an output,the signal's signal,the timing resistor on the RT pin must be set falling edge is approximately180°out of phase with so that the oscillator is programmed to run at90%to the rising edge of the PH pins.Thus,two TPS54550110%of the synchronization frequency.devices operating in a system can share an inputNOTE:Do not use synchronization input for designs capacitor and draw ripple current at twice thewith output voltages>10V.frequency of a single unit.Figure3.SYNC Input Waveform9Submit Documentation FeedbackInternal OscillatorV O(PH)V O(SYNC)Power Good (PWRGD)Bootstrap Voltage (BOOT)Error AmplifierVoltage ReferenceT delay 1000ƒs(kHz)ms (5)Bias Voltage (VBIAS)TPS54550SLVS623A–MARCH 2006–REVISED APRIL 2006Figure 4.SYNC Output WaveformUp to 1mA of current can be drawn for use in anexternal application circuit.The VBIAS pin must have a bypass capacitor value of 1.0µF.X7R or X5R The VSENSE pin is compared to an internal grade dielectric ceramic capacitors are recommended reference signal,if the VSENSE is greater than 97%because of their stable characteristics over and no other faults are present,the PWRGD pin temperature.presents a high impedance.A low on the PWRGD pin indicates a fault.The PWRGD pin has been designed to provide a weak pull-down and indicates a fault even when the device is unpowered.If the TPS54550The BOOT capacitor obtains its charge cycle by cycle has power and has any fault flag set,the TPS54550from the VBIAS capacitor.A capacitor and small indicates the power is not good by driving the value resistor from the BOOT pin to the PH pins is PWRGD pin low.The following events,singly or in required for operation.The bootstrap connection for combination,indicate power is not good:the high side driver must have a bypass capacitor of 0.1µF and resistor 24Ohm.•VSENSE pin out of bounds •Overcurrent•Thermal shutdown The VSENSE pin is the error amplifier inverting input.•UVLO undervoltageThe error amplifier is a true voltage amplifier with 1.5•Input voltage not present (weak pull-down)mA of drive capability with a minimum of 60dB of •Slow-startingopen loop voltage gain and a unity gain bandwidth of •VBIAS voltage is low2MHz.Once the PWRGD pin presents a high impedance (i.e.,power is good),a VSENSE pin out of bounds condition forces PWRGD pin low (i.e.,power is bad)The voltage reference system produces a precision after a time delay.This time delay is a function of the reference signal by scaling the output of a switching frequency and is calculated using temperature stable bandgap circuit.During production Equation 5:testing,the bandgap and scaling circuits are trimmed to produce 0.891V at the output of the error amplifier,with the amplifier connected as a voltage follower.The trim procedure improves the regulation,since it cancels offset errors in the scaling and error amplifier circuits.The VBIAS regulator provides a stable supply for the internal analog circuits and the low side gate driver.10Submit Documentation FeedbackPWM Control and Feed ForwardDeadtime ControlLow Side Gate Driver(LSG)Thermal Shutdown TPS54550SLVS623A–MARCH2006–REVISED APRIL2006reference ramps from0V to0.891V.During theinitial slow-start interval,the internal reference voltage Signals from the error amplifier output,oscillator,and is very small resulting in a couple of skipped pulses current limit circuit are processed by the PWM control because the minimum on time causes the actual logic.Referring to the internal block diagram,the output voltage to be slightly greater than the preset control logic includes the PWM comparator,PWM output voltage until the internal reference ramps up. latch,and the adaptive dead-time control logic.During steady-state operation below the current limitthreshold,the PWM comparator output and oscillatorpulse train alternately reset and set the PWM latch.Adaptive dead time control prevents shoot throughcurrent from flowing in the integrated high-side Once the PWM latch is reset,the low-side driver andMOSFET and the external low-side MOSFET during integrated pull-down MOSFET remain on for athe switching transitions by actively controlling the minimum duration set by the oscillator pulse width.turn on times of the drivers.The high-side driver does During this period,the PWM ramp discharges rapidlynot turn on until the voltage at the gate of the to the valley voltage.When the ramp begins tolow-side MOSFET is below1V.The low-side driver charge back up,the low-side driver turns off and thedoes not turn on until the voltage at the gate of the high-side FET turns on.The peak PWM ramp voltagehigh-side MOSFET is below1V.varies inversely with input voltage to maintain aconstant modulator and power stage gain of8V/V.As the PWM ramp voltage exceeds the error amplifierLSG is the output of the low-side gate driver.The output voltage,the PWM comparator resets the latch,100-mA MOSFET driver is capable of providing gate thus turning off the high-side FET and turning on thedrive for most popular MOSFETs suitable for this low-side FET.The low-side driver remains on untile the SWIFT Designer Software Tool the next oscillator pulse discharges the PWM ramp.to find the most appropriate MOSFET for the During transient conditions,the error amplifier output application.Connect the LSG pin directly to the gate can be below the PWM ramp valley voltage or above of the low-side MOSFET.Do not use a gate resistor the PWM peak voltage.If the error amplifier is high,as the resulting turn-on time may be too slow.the PWM latch is never reset and the high-side FETremains on until the oscillator pulse signals thecontrol logic to turn the high-side FET off and theThe device uses the thermal shutdown to turn off the internal low-side FET and driver on.The deviceMOSFET drivers and controller if the junction operates at its maximum duty cycle until the outputtemperature exceeds165°C.The device is restarted voltage rises to the regulation set point,settingautomatically when the junction temperature VSENSE to approximately the same voltage as thedecreases to7°C below the thermal shutdown trip internal voltage reference.If the error amplifier outputpoint and starts up under control of the slow-start is low,the PWM latch is continually reset and thecircuit.high-side FET does not turn on.The internal low-sideFET and low side driver remain on until the VSENSEvoltage decreases to a range that allows the PWMcomparator to change states.The TPS54550iscapable of sinking current through the external lowside FET until the output voltage reaches theregulation set point.The minimum on time is designed to be180ns.During the internal slow-start interval,the internalOvercurrent ProtectionOutput Voltage LimitationsT HICCUP(ms) 2250ƒs(kHz)(6)Setting the Output VoltageR2 R1 0.891V O )0.891(7)TPS54550SLVS623A–MARCH 2006–REVISED APRIL 2006OUTPUT VOLTAGE (V)R2VALUE (k Ω)1.228.7Overcurrent protection is implemented by sensing the 1.514.7drain-to-source voltage across the high-side 1.89.76MOSFET and compared to a voltage level which represents the overcurrent threshold limit.If the2.5 5.49drain-to-source voltage exceeds the overcurrent3.33.74threshold limit for more than 100ns,the high-side MOSFET is disable,the SSENA pin is pulled low,and the internal digital slow-start is reset to 0V.SSENA is held low for approximately the time that is calculated Due to the internal design of the TPS54550there are by Equation 6:both upper and lower output voltage limits for any given input voltage.Additionally,the lower boundary of the output voltage set point range is also dependent on operating frequency.The upper limit of the output voltage set point is constrained by the Once the hiccup time is complete,the SSENA pin ismaximum duty cycle of the device and is shown in released and the converter initiates the internal Figure 12.The lower limit is constrained by the slow-start.minimum controllable on time which may be as high as 220ns.The approximate minimum output voltage for a given input voltage and range of operating The output voltage of the TPS54550can be set by frequencies is shown in Figure 8while the maximum feeding back a portion of the output to the VSENSE operating frequency versus input voltage for some pin using a resistor divider network.In the application common output voltages is shown in Figure 10.circuit of Figure 29,this divider network is comprised The curves shown in these two figures are valid for of resistors R1and R2.To calculate the resistor output currents greater than 0.5A.As output currents values to generate the required output voltage use decrease towards no load (0A),the minimum output the following equation:voltage decreases.For applications where the load current is less than 100mA,the curves shown in Figure 9and Figure 11are applicable.All of the data plotted in these curves are approximate and take into Start with a fixed value of R1and calculate theaccount a possible 20percent deviation in actual required R2value.Assuming a fixed value of 10k Ωoperating frequency relative to the intended set point.for R1,the following table gives the appropriate R2value for several common output voltages:TYPICAL CHARACTERISTICS0102030405060708090T - Junction Temperature - °CJ O n R e s i s t a n c e - m W0.89120.89100.89080.89060.89040.89020.89000.8898−50−250255075100125150V r e f − I n t e r n a l V o l t a g e R e f e r e n ce − VT J − Junction Temperature − 5CV - Input Voltage - VI C u r r e n t L i m i t -AM i n i m u m O u t p u t V o l t a g e − VV I − Input Voltage − V100200300400500600700800M a x i m u m S w i t c h i n g F r e q u e n c y − k H zV I − Input Voltage − VM i n i m u m O u t p u t V o l t a g e − VV I − Input Voltage − VM a x i m u m S w i t c h i n g F r e q u e n c y − k H zV I − Input Voltage − V5075100125150175200225200300400500600700R T R e s i s t a n c e − k WSwitching Frequency − kHz02468101214510152025− O u t p u t V o l t a g e − VV O V I − Input Voltage − VTPS54550SLVS623A–MARCH 2006–REVISED APRIL 2006ON RESISTANCECURRENT LIMITINTERNAL VOLTAGE REFERENCEvsvsvsJUNCTION TEMPERATUREINPUT VOLTAGEJUNCTION TEMPERATUREFigure 5.Figure 6.Figure 7.MINIMUM OUTPUT VOLTAGEMINIMUM OUTPUT VOLTAGEMAXIMUM SWITCHING FREQUENCYvsvsvsINPUT VOLTAGEINPUT VOLTAGEINPUT VOLTAGEFigure 8.Figure 9.Figure 10.MAXIMUM SWITCHING FREQUENCYMAXIMUM OUTPUT VOLTAGERT RESISTANCEvsvsvsINPUT VOLTAGEINPUT VOLTAGESWITCHING FREQUENCYFigure 11.Figure 12.Figure 13.。

Large Can Aluminum Electrolytic CapacitorsFEATURES• LONG LIFE (105°C, 2000 HOURS)• LOW PROFILE AND HIGH DENSITY DESIGN OPTIONS • EXPANDED CV VALUE RANGE• HIGH RIPPLE CURRENT• CAN-TOP SAFETY VENT • DESIGNED AS INPUT FILTER OF SMPS• STANDARD 10mm (.400") SNAP-IN SPACING NRLMW SeriesSPECIFICATIONSNotice for MountingThe space from the top of the can shall be more than (3mm) from chassis or other construction materials so that safety vent has room to expand in case of emer g en c y.Sleeve Color: Dark BlueCan Top Safety VentInsulation Sleeve and Minus Polarity Marking(4.0mm Leads Available As Option)D+1Max.L ± 26.3 ± 10.810(-)(+)MAXIMUM EX P AN S IONFOR SAFETY VENT Approx. 3.0mmRecommended PC Board Mounting Holes:10 ± .1∅= 2 ± 0.1D ∅ ± 0.5ChassisPC BoardPRECAUTIONSPlease review the notes on correct use, safety and precautions found on pages T10 & T11of NIC’s Electrolytic Capacitor catalog . Operating Temperature Range-40 ~ +105°C -25 ~ +105°C Rated Voltage Range 10 ~ 250Vdc 450Vdc Rated Capacitance Range 180 ~ 68,000µF 56 ~ 470µF Capacitance Tolerance ±20% (M) at 120Hz, +20°CMax. Leakage Current (µA)After 5 minutes (20°C)3 x C(µF)VMax. Tan δat 120Hz/20°CW.V. (Vdc)10162535506380100 ~ 400450Tan δ max.0.550.450.350.300.250.200.170.150.20Surge VoltageW.V. (Vdc)10162535506380100160S.V. (Vdc)132032446379100125200W.V. (Vdc)180200250400450----S.V. (Vdc)220250300450500----Ripple Current Correction Factors Frequency (Hz)50601001205001K 10K ~ 50K --Multiplier at 85°C16 ~ 100Vdc0.930.950.99 1.0 1.05 1.08 1.15--160 ~ 450Vdc0.750.800.95 1.0 1.20 1.25 1.40-Low Temperature Stability (10 to 250Vdc)Temperature (°C)0-25-40------Capacitance Change -5%-10-30%------Impedance Ratio 1.539------Load Life Test 2,000 hours at +105°C Capacitance ChangeWithin ±20% of initial measured valueTan δLess than 200% of specifi ed maximum valueLeakage Current Less than specifi ed maximum value Shelf Life Test 1,000 hours at +105°C(no load)Capacitance ChangeWithin ±20% of initial measured value Tan δLess than 200% of specifi ed maximum valueLeakage Current Less than specifi ed maximum value Surge Voltage TestPer JIS-C-5141 (table #6, #4)Surge voltage applied: 30 seconds "On" and 5.5 minutes no voltage "Off"Capacitance ChangeWithin ±20% of initial measured value Tan δLess than 200% of specifi ed maximum valueLeakage Current Less than specifi ed maximum value Soldering EffectRefer toMIL-STD-202F Method 210ACapacitance ChangeWithin ±10% of initial measured valueTan δLess than specifi ed maximum value Leakage CurrentLess than specifi ed maximum valueRoHSCompliantincludes all homogeneous materials *See Part Number System for DetailsLarge Can Aluminum Electrolytic Capacitors NRLMW SeriesLarge Can Aluminum Electrolytic CapacitorsNRLMW SeriesNRLMW 471 M 250V 30X35 FRoHS compliant Case Size (mm) Voltage Rating Tolerance Code Capacitance Code SeriesPART NUMBER SYSTEM。

Features Benefits• 2000 tag simultaneous identificationProvides high-speed data collection to facilitate warehousing and inventory-based applications• 100 tag/sec. identification rate Provides reliable identification of fast moving objects• UHF operating frequencies Operates interchangeable on standard European ISM band frequencies• Multi-tag compatibility Provides communication for the whole smTAG UHF based tag families•A unique communication interface This unique feature of the FSK-Controller family makes it easy to build a controller network and to integrate it into almost any existing IT infrastructure• Internal BuzzerThe internal buzzer allows early, security network independent onsite alarming• Real-Time operating system Meets industrial requirements for reliability and robustness• SecurityHigh security system with use of sha-256 algorithm & frequencyThe mobile RC 550X family from smTAG is an intelligent ISM wireless UHF controller. It is ideal for high-volume two-way wireless applications, for remote control systems, for home security and alarm systems, for industrial applications such as telemetry, sensor data logging, for personal/patient data logging, barcode readers and automatic meter reading. It provides highly accurate, real-time data collection without human intervention in wireless applications like: Identification, Remote Control, Tracking and Tracing, Monitoring of Assets, Temperature, Vibration, Pressure and many more. • RC 5501: RS232 Interface •RC 5502: USB 2.0 • RC 5503: Ethernet • RC 5504: Bluetooth • RC 5505: WLAN •RC 5506: GSMBy integration of advanced UHF radio frequency technology from smTAG, the RC 550X transmits and receives data at distances of up to 100m (300 feet) from an TM 4300 and up to 40m (120 feet) from a TM 2200.The highly effective anti-collision handling algorithm allows simultaneous communication with thousands of tags within the controller read zone. Because of its low power consumption, RC 550X can effectively operate from the controller internal rechargeable battery pack.SMTAGSpecification RC 550XCompatibility TM, TC family PerformanceData rate ¹2.4 to 19.2 Kbs (programmable) UID receive rate – ID only 2 Bytes @ 19’200 Baud rate Up to 5’000 UID’s per second UID receive rate –128 bit data packets @ 57’600 Baud rate (UID + data)Up to 1’000 UID’s per second Stability/Filter (Data Integrity) 8 or 16 bit CRC CommunicationBase Frequency868MHz (EC) or 915MHz (US) ISM Band (factory preset) Modulation FSK Base Band Width 67 to 405 KHz Sensitivity ¹ - 61 to 103 dBm Channel4096 per base frequency Frequency/Channel hopping Programmable Number of antennas 1Certification EN 300 220 (EC); FCC part 15 (US) Micro controller Flash Memory 7 Kb Data RAM 64 BytesExternal EEPROM 256 Kb (data logging) ElectricalPowering5 volts DC power supply4 AAA batteries mounted on the inside (optional)Voltage 5 volts regulated Power consumption Active:Idle: Stand by:25 mA max. (during RF transmit operations) 1.5 mA 2 uA EnvironmentalOperating temperature -40ºC to +85ºC / -40ºF to +185ºF Storage temperature -40ºC to +85ºC / -40ºF to +185ºF Humidity 5% to 90% (non condensing) PhysicalDimensions 87 x 153 x 55 mm Weight 150 grams ColourGrey Type of material ABSsmTAG is a global supplier of innovative RFID Technology in the UHF band.With its unique system approach smtag provides an easy to implement set of products, which reduces the time for implementation dramatically.System integrators of industrial, medical and corporate solutions gets high quality products, which offers a max. return on investment.FSK-C product line increase efficiency and qualityTo learn more about how the FSK-Cproduct family can increase profitability for business, contact one of smtag’s business partnerPartner NetworkPartner Company DetailsCopyright © 2005 smtag international All rights reservedv.1.5 (10/05)¹ in the course of Q1/06 a PC based configuration application will be downloadable from “”。

54ACT2525FMQB中文资料Original Creation Date: 07/02/96Last Update Date: 03/17/97Last Major Revision Date: 02/05/97MN54ACT2525-X REV 2A0MICROCIRCUIT DATA SHEET1-to-8 Minimum Skew Clock DriverGeneral DescriptionThe ACT2525 is a minimum skew clock driver with one input driving eight outputsspecifically designed for signal generation and clock distribution applications. The 2525is designed to distribute a single clock to eight separate receivers with low skew across all outputs during both the TPLH and TPHL transitions.NS Part Numbers54ACT2525DMQB 54ACT2525FMQB 54ACT2525LMQBIndustry Part Number54ACT2525Prime DieJ2525ProcessingMIL-STD-883, Method 5004Quality Conformance InspectionMIL-STD-883, Method 5005Subgrp Description Temp ( C)o 1Static tests at +252Static tests at +1253Static tests at -554Dynamic tests at +255Dynamic tests at +1256Dynamic tests at -557Functional tests at +258A Functional tests at +1258B Functional tests at -559Switching tests at +2510Switching testsat +12511Switching tests at-55MICROCIRCUIT DATA SHEET MN54ACT2525-X REV 2A0 Features- Ideal for signal generation and clock distribution- Guaranteed pin to pin and part to part skew- Guaranteed 4000V minimum ESD protection- 24mA output drive capability- CT has TTL-compatible inputsMICROCIRCUIT DATA SHEET MN54ACT2525-X REV 2A0 (Absolute Maximum Ratings)(Note 1)Supply Voltage (Vcc)-0.5V to +7.0VDC Input Diode Current (Iik)Vi = -0.5V-20 mAVi = Vcc +0.5V+20 mADC Input Voltage (Vi)-0.5V to Vcc +0.5VDC Output Diode Current (Iok)Vo = -0.5V-20 mAVo = Vcc +0.5V+20 mADC Output Voltage (Vo)-0.5V to Vcc +0.5VDC Output Source or Sink Current (Io)+50 mADC Vcc or Ground Current per Output Pin (Icc or Ignd)+50 mAStorage Temperature (Tstg)-65 C to +150 CJunction Temperature (Tj)CDIP175 CNote 1:Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/inputloading variables. National does not recommend operation of CGS circuits outsidedatabook specifications.Recommended Operating ConditionsSupply Voltage (Vcc)4.5V to5.5VInput Voltage (Vi)0V to VccOutput Voltage (Vo)0V to VccOperating Temperature (Ta)-55 C to +125 CMinimum Input Edge Rate (Delta V/Delta t)ACT DevicesVin from 0.8V to 2.0V********,5.5V125 mV/nsMN54ACT2525-X REV 2A0MICROCIRCUIT DATA SHEETElectrical CharacteristicsDC PARAMETERS(The following conditions apply to all the following parameters, unless otherwise specified.)DC:VCC 4.5V to 5.5V, Temperature Range: -55C to 125C. NOTE: -55C TEMPERATURE, SUBGROUP 3 IS GUARANTEED BUT NOT TESTED.SYMBOL PARAMETER CONDITIONS NOTES PIN-NAME MIN MAX UNITSUB-GROUPSIIH High Level InputCurrent VCC=5.5V, VIH=5.5V1, 2INPUT0.1uA11, 2INPUT 1.0uA2, 3IIL Low Level InputCurrent VCC=5.5V, VIL=0.0V1, 2INPUT-0.1uA11, 2INPUT-1.0uA2, 3VOL Low Level OutputVoltage VCC=4.5V, VIH=2.0V, VIL=0.8V,IOL=50.0uA1, 2OUTPUT.10V1, 2,3 VCC=5.5V, VIH=2.0V, VIL=0.8V,IOL=50.0uA1, 2OUTPUT.10V1, 2,3 VCC=4.5V, VIH=2.0V, VIL=0.8V,IOL=24.0mA1, 2OUTPUT.36V11, 2OUTPUT.50V2, 3 VCC=5.5V, VIH=2.0V, VIL=0.8V,IOL=24.0mA1, 2OUTPUT.36V11, 2OUTPUT.50V2, 3VIOL Dynamic outputcurrent Low VCC=5.5V, IOL=50.0mA, VIL=0.0V,VIH=5.5V1,2, 5OUTPUT 1.65V1, 2,3VOH Low Level OutputVoltage VCC=5.5V, IOH=-50.0uA, VIL=0.8V,VIH=2.0V1, 2OUTPUT 5.40V1, 2,3 VCC=4.5V, IOH=-50.0uA, VIL=0.8V,VIH=2.0V1, 2OUTPUT 4.40V1, 2,3 VCC=4.5V, IOH=-24.0mA, VIL=0.8V,VIH=2.0V1, 2OUTPUT 3.86V11, 2OUTPUT 3.70V2, 3 VCC=5.5V, IOH=-24.0mA, VIL=0.8V, VIH=2.0V1, 2OUTPUT 4.86V11, 2OUTPUT 4.70V2, 3VIOH Dynamic outputcurrent High VCC=5.5V, IOH=-50.0mA, VIL=0.0V,VIH=5.5V1,2, 5OUTPUT 3.85V1, 2,3ICCH Supply CurrentOutputs HIGH VCC=5.5V, VIH=5.5V1, 2VCC8.0uA11, 2VCC160uA2, 3ICCL Supply CurrentOutputs LOW VCC=5.5V, VIL=0.0V1, 2VCC8.0uA11, 2VCC160uA2, 3ICCT Supply Currentper Input VCC=5.5V, VINH=3.4V1, 2VCC 1.0mA11, 2VCC 1.6mA2, 3MN54ACT2525-X REV 2A0MICROCIRCUIT DATA SHEETElectrical CharacteristicsAC PARAMETERS(The following conditions apply to all the following parameters, unless otherwise specified.)AC:CL=50pF, RL=500 OHMS, TR/TF=3.0ns, Temp range: -55C to +125C. NOTE: -55C TEMPERATURE, SUBGROUP 11 IS GUARANTEED BUT NOT TESTED.SYMBOL PARAMETER CONDITIONS NOTES PIN-NAME MIN MAX UNITSUB-GROUPStpLH Propagation Delay VCC=4.5V3,4, 7CKIN-On 5.510.0ns93,4, 7CKIN-On7.011.5ns103,4, 7CKIN-On 4.08.5ns11tpHL Propagation Delay VCC=4.5V3,4, 7CKIN-On 1.510.0ns93,4, 7CKIN-On7.011.5ns103,4, 7CKIN-On 4.08.5ns11tosHL Maximum SkewCommon Edge VCC=4.5V6On - On Skew1.0ns9, 10,11tosLH Maximum SkewCommon Edge VCC=4.5V6On - On Skew1.0ns9, 10,11tpV Maximum SkewPart/Part VCC=4.5V6Maximum Skew4.0ns9, 10,11tost Maximum SkewOpposite Edge VCC=4.5V6Maximum Skew1.5ns9, 10,11tR/tF Maximum Rise/FallTime VCC=4.5V6 3.0ns96 4.0ns10, 11Fmax Maximum ClockFrequency VCC=4.5V6CP80Mhz96CP75Mhz10, 11Note 1:SCREEN TESTED 100% ON EACH DEVICE AT +25C & +125C TEMPERATURE, SUBGROUPS 1, 2, 7 & 8. Note 2:SAMPLE TESTED (METHOD 5005, TABLE 1) ON EACH MFG. LOT AT +25C & +125C TEMPERATURE, SUBGROUPS A1, 2, 7 & 8.Note 3:SCREEN TESTED 100% ON EACH DEVICE AT +25C TEMPERATURE ONLY, SUBGROUP A9.Note 4:SAMPLE TESTED (METHOD 5005, TABLE 1) ON EACH MFG. LOT AT +25C & +125C TEMPERATURE, SUBGROUPS A9 & 10.Note 5:TRANSMISSION LINE DRIVING TEST, GUARDBANDED LIMITS SET FOR +25C, 2 MSEC DURATION MAX.Note 6:DESIGN CHARACTERIZATION DATA.Note 7:+25C & +125C MIN LIMITS GUARANTEED FOR 5.5V BY GUARDBANDING 4.5V MINIMUM LIMITS.。

In keeping with our ongoing policy of product evolvement and improvement, the above specification is subject to change without notice.

ISO9001: 2000 Registered - Registration number 6830/2

The ACTR5504/434.42/QCC8C is a true one-port, surface-acoustic-wave (SAW ) resonator in a surface-mount ceramic QCC8C case. It provides reliable, fundamental-mode, quartz frequency stabilization i.e. in transmitters or local oscillators operating at 434.420 MHz.

1. Package Dimension (QCC8C)

2.

3. Equivalent LC Model and Test Circuit

4. Typical Application Circuits

1) Low-Power Transmitter Application 2) Local Oscillator Application

Pin Configuration 2 Input/Output 6 Input/Output 4,8

Case Ground

1,3,5,7

NC

Sign Data (unit: mm)

Sign Data (unit: mm)

A 2.08 E 1.2

B 0.6 F 1.35

C 1.27 G 5.0 D

2.54

H

5.0

Issue : 1 C1

In keeping with our ongoing policy of product evolvement and improvement, the above specification is subject to change without notice.

ISO9001: 2000 Registered - Registration number 6830/2 5. Typical Frequency Response 6. Temperature Characteristics

7.Performance

7-1.Maximum Ratings

Rating

Value

Unit

CW RF Power Dissipation

0 dBm DC Voltage Between Terminals ±30V VDC Case Temperature -40 to +85 °C Soldering Temperature

+250

°C

7-2.Electronic Characteristics

Characteristic

Sym

Minimum

Typical

Maximum

Unit

Absolute Frequency

f C 434.345

434.495

MHz Centre Frequency

(+25 °C) Tolerance from 434.420 MHz

∆f C ±75 kHz Insertion Loss IL 2.0 2.6 dB Unloaded Q Q U 7,270 Quality Factor

50 Ω Loaded Q Q L 1,500 Turnover Temperature

T 0 25 55 °C Turnover Frequency

f 0 f C kHz Temperature Stability

Frequency Temperature Coefficient

FTC 0.032 ppm/°C 2 Frequency Aging Absolute Value during the First Year |fA | ≤10 ppm/yr DC Insulation Resistance Between Any Two Terminals

1.0 M Ω Motional Resistance

R M 26 35 Ω Motional Inductance L M 69.2775 µH Motional Capacitance C M 1.9394 fF RF Equivalent RLC Model

Shunt Static Capacitance C 0

2.90

3.20

3.40

pF

Issue : 1 C1

i CAUTION: Electrostatic Sensitive Device. Observe precautions for handling!

1. The centre frequency, f C, is measured at the minimum IL point with the resonator in the 50Ωtest system.

2. Unless noted otherwise, case temperature T C = +25°C±2°C.

3. Frequency aging is the change in f C with time and is specified at +65°C or less. Aging may exceed the

specification for prolonged temperatures above +65°C. Typically, aging is greatest the first year after

manufacture, decreasing in subsequent years.

4. Turnover temperature, T0, is the temperature of maximum (or turnover) frequency, f0. The nominal frequency

at any case temperature, T C, may be calculated from: f = f0 [1 - FTC (T0 - T C)2].

5. This equivalent RLC model approximates resonator performance near the resonant frequency and is provided

for reference only. The capacitance C0 is the measured static (non-motional) capacitance between the two terminals. The measurement includes case parasitic capacitance.

6. Derived mathematically from one or more of the following directly measured parameters: f C, IL, 3 dB

bandwidth, f C versus T C, and C0.

7. The specifications of this device are based on the test circuit shown above and subject to change or

obsolescence without notice.

8. Typically, equipment utilizing this device requires emissions testing and government approval, which is the

responsibility of the equipment manufacturer.

9. Our liability is only assumed for the Surface Acoustic Wave (SAW) component(s) per se, not for applications,

processes and circuits implemented within components or assemblies.

In keeping with our ongoing policy of product evolvement and improvement, the above specification is subject to change without notice.

ISO9001: 2000 Registered - Registration number 6830/2。