Verilog HDL数字系统设计报告 9

- 格式:doc

- 大小:49.00 KB

- 文档页数:3

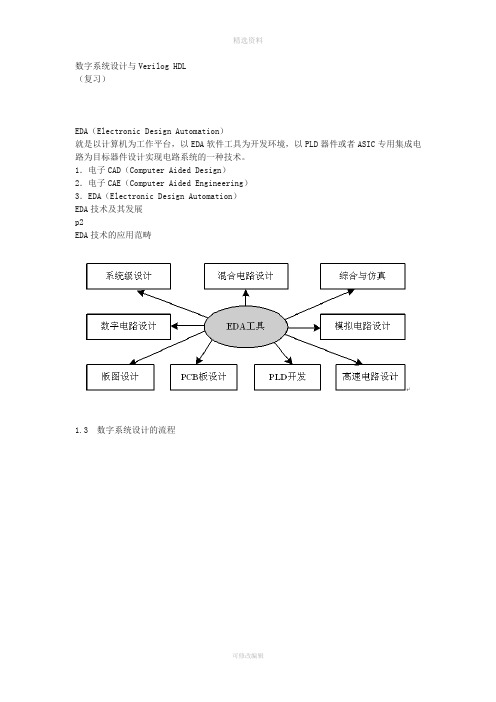

数字系统设计与Verilog HDL(复习)EDA(Electronic Design Automation)就是以计算机为工作平台,以EDA软件工具为开发环境,以PLD器件或者ASIC专用集成电路为目标器件设计实现电路系统的一种技术。

1.电子CAD(Computer Aided Design)2.电子CAE(Computer Aided Engineering)3.EDA(Electronic Design Automation)EDA技术及其发展p2EDA技术的应用范畴1.3 数字系统设计的流程基于FPGA/CPLD的数字系统设计流程1. 原理图输入(Schematic diagrams )2、硬件描述语言(HDL文本输入)设计输入硬件描述语言与软件编程语言有本质的区别综合(Synthesis)将较高层次的设计描述自动转化为较低层次描述的过程◆行为综合:从算法表示、行为描述转换到寄存器传输级(RTL)◆逻辑综合:RTL级描述转换到逻辑门级(包括触发器)◆版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到PLD器件的配置网表表示综合器是能自动实现上述转换的软件工具,是能将原理图或HDL语言描述的电路功能转化为具体电路网表的工具适配适配器也称为结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件对CPLD器件而言,产生熔丝图文件,即JEDEC文件;对FPGA器件则产生Bitstream 位流数据文件p8仿真(Simulation)功能仿真(Function Simulation)时序仿真(Timing Simulation)仿真是对所设计电路的功能的验证p9编程(Program)把适配后生成的编程文件装入到PLD器件中的过程,或称为下载。

通常将对基于EEPROM工艺的非易失结构PLD器件的下载称为编程(Program),将基于SRAM工艺结构的PLD器件的下载称为配置(Configure)。

HDL实验报告专业电子科学与技术姓名学号指导老师1 实验一Modelsim仿真软件的使用1.1 实验目的(1)熟悉Modelsim 软件;(2)掌握Modelsim 软件的编译、仿真方法;(3)熟练运用Modelsim 软件进行HDL 程序设计开发。

1.2 实验步骤(1)学习使用Modelsim软件;(2)分析原理及功能;(3)用Verilog HDL编写程序;(4)编写测试程序进行仿真;(4)观察波形,分析仿真结果是否正确。

1.3 实验内容用Verilog HDL 程序实现一个异或门,Modelsim 仿真,观察效果。

1.4.1 程序module my_xor(ina,inb,out);input ina,inb;output out;assign out=ina^inb;endmodulemodule t_xor;reg ina,inb;wire out;initialbeginina=1'b0;forever #20 ina=~ina;endinitialbegininb=1'b0;forever #10 inb=~inb;endmy_xor tt(.ina(ina),.inb(inb),.out(out));endmodule2 实验二简单组合电路设计2.1 实验目的(1)掌握基于Modelsim 的数字电路设计方法;(2)熟练掌握HDL 程序的不同实现方法2.2 实验步骤(1)分析原理及功能;(2)根据原理用Verilog HDL编写程序;(3)编写测试程序进行仿真;(4)观察波形,分析仿真结果是否正确。

2.3 实验内容设计一个三人表决器(高电平表示通过) ,实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真(要求:至少使用两种方法实现上述实验内容和testbench)。

![数字系统设计与VerilogHDL (9)[26页]](https://img.taocdn.com/s1/m/7fd8beaac5da50e2534d7f47.png)

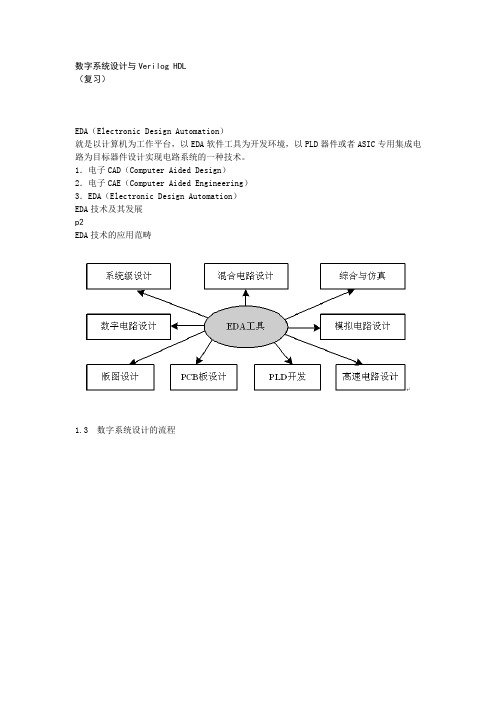

数字系统设计与Verilog HDL(复习)EDA(Electronic Design Automation)就是以计算机为工作平台,以EDA软件工具为开发环境,以PLD器件或者ASIC专用集成电路为目标器件设计实现电路系统的一种技术。

1.电子CAD(Computer Aided Design)2.电子CAE(Computer Aided Engineering)3.EDA(Electronic Design Automation)EDA技术及其发展p2EDA技术的应用范畴1.3 数字系统设计的流程基于FPGA/CPLD的数字系统设计流程1. 原理图输入(Schematic diagrams )2、硬件描述语言 (HDL文本输入)设计输入硬件描述语言与软件编程语言有本质的区别综合(Synthesis)将较高层次的设计描述自动转化为较低层次描述的过程◆行为综合:从算法表示、行为描述转换到寄存器传输级(RTL)◆逻辑综合:RTL级描述转换到逻辑门级(包括触发器)◆版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到PLD器件的配置网表表示综合器是能自动实现上述转换的软件工具,是能将原理图或HDL语言描述的电路功能转化为具体电路网表的工具适配适配器也称为结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件对CPLD器件而言,产生熔丝图文件,即JEDEC文件;对FPGA器件则产生Bitstream 位流数据文件p8仿真(Simulation)功能仿真(Function Simulation)时序仿真(Timing Simulation)仿真是对所设计电路的功能的验证p9编程(Program)把适配后生成的编程文件装入到PLD器件中的过程,或称为下载。

通常将对基于EEPROM工艺的非易失结构PLD器件的下载称为编程(Program),将基于SRAM 工艺结构的PLD器件的下载称为配置(Configure)。

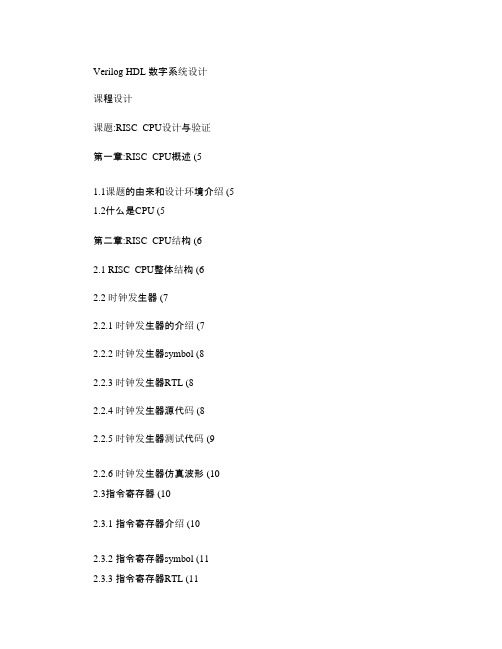

Verilog HDL数字系统设计课程设计课题:RISC_CPU设计与验证第一章:RISC_CPU概述(51.1课题的由来和设计环境介绍(5 1.2什么是CPU (5第二章:RISC_CPU结构(62.1 RISC_CPU整体结构(62.2 时钟发生器(72.2.1 时钟发生器的介绍(72.2.2 时钟发生器symbol(82.2.3 时钟发生器RTL(82.2.4 时钟发生器源代码(82.2.5 时钟发生器测试代码(92.2.6 时钟发生器仿真波形(10 2.3指令寄存器(102.3.1 指令寄存器介绍(102.3.2 指令寄存器symbol(112.3.3 指令寄存器RTL(112.3.4 指令寄存器源代码(11 2.3.5 指令寄存器测试代码(122.3.6指令寄存器仿真波形(13 2.4 累加器(132.4.1 累加器介绍(132.4.2 累加器symbol(132.4.3 累加器RTL(142.4.4 累加器源代码(142.4.5 累加器仿真代码(142.4.6 累加器仿真波形(152.5 算术运算器(152.5.1 算术运算器介绍(152.5.2 算术运算器symbol(162.5.3 算术运算器RTL(172.5.4 算术运算器源代码(182.5.5 算术元算器测试代码(192.5.6 算术运算器仿真波形(20 2.6数据控制器(202.6.1 数据控制器介绍(202.6.2 数据控制器smybol(20 2.6.3 数据控制器RTL(212.6.4 数据控制器源代码(21 2.6.5 数据控制器测试代码(222.6.6 数据控制器仿真波形(22 2.7 地址多路器(222.7.1地址多路器介绍(222.7.2 地址多路器smybol(232.7.3 地址多路器RTL(232.7.5 地址多路器测试代码(232.7.6 地址多路器仿真波形(24 2.8程序计数器(242.8.1 程序计数器介绍(242.8.2 程序计数器symbol(25 2.8.3 程序计数器RTL(252.8.4 程序计数器源代码(25 2.8.5 程序计数器测试代码(262.8.6 程序计数器仿真波形(26 2.9 状态控制器(272.9.1 状态控制器介器(272.9.2 状态控制器smybol(272.9.3 状态控制器RTL(272.9.4 状态控制器源代码(272.9.5 状态控制器测试代码(282.9.6 状态控制器仿真波形(29 2.10状态机(292.10.1状态机的介绍(292.10.2 状态机symbol(302.10.3 状态机RTL(302.10.4状态机源代码(312.10.5 状态机测试代码(352.10.6 状态机仿真波形(362.11 CPU内核模块的整合(362.11.1 CPU内核原理图(362.11.2 CPU内核smybol (37第三章:CPU外围模块的设计(37 3.1 地址译码器(373.1.1 地址译码器介绍(373.1.2 地址译码器smybol(373.1.3 地址译码器RTL(383.1.4 地址译码器源代码(383.1.5 地址译码器测试代码(383.1.6 地址译码器仿真波形(393.2 RAM (393.2.1 RAM的介绍(393.2.2 RAM smybol(393.2.3 RAM RTL(403.2.4 RAM 源代码(403.2.5 RAM 测试代码(403.2.6 RAM 仿真波形(423.3 ROM (423.3.1 ROM的介绍(423.3.3 ROM的高阻化处理(423.4 I/O模块(433.4.1 I/O模块源代码(433.4.2 I/O模块smybol(443.5 CPU外围模块连接电路原理图(443.6 烧录到FPGA上(45第四章:CPU功能验证(454.1 CPU寻址方式和指令系统(454.2 HLT指令验证(464.3 SKZ指令验证(464.4 ADD指令验证(474.5 AND指令验证(474.6 LDA、STO、JMP指令验证(47第五章:总结(48参考文献: (48第一章:RISC_CPU概述1.1课题的由来和设计环境介绍在本设计课程中,我们通过自己动脑筋,设计出CPU的软核和固核。

verilog hdl实验报告《Verilog HDL实验报告》Verilog HDL(硬件描述语言)是一种用于描述电子系统的硬件的语言,它被广泛应用于数字电路设计和硬件描述。

本实验报告将介绍Verilog HDL的基本概念和使用方法,并通过实验展示其在数字电路设计中的应用。

实验目的:1. 了解Verilog HDL的基本语法和结构2. 掌握Verilog HDL的模块化设计方法3. 熟悉Verilog HDL的仿真和综合工具的使用实验内容:1. Verilog HDL的基本语法和结构Verilog HDL是一种硬件描述语言,其语法和结构类似于C语言。

它包括模块定义、端口声明、信号赋值等基本元素。

在本实验中,我们将学习如何定义Verilog模块,并使用端口声明和信号赋值描述数字电路的行为。

2. Verilog HDL的模块化设计方法Verilog HDL支持模块化设计,可以将复杂的电路分解为多个模块,每个模块描述一个子电路的行为。

在本实验中,我们将学习如何设计和实现Verilog模块,并将多个模块组合成一个完整的数字电路。

3. Verilog HDL的仿真和综合工具的使用Verilog HDL可以通过仿真工具进行功能验证,也可以通过综合工具生成实际的硬件电路。

在本实验中,我们将使用Verilog仿真工具对设计的数字电路进行功能验证,并使用综合工具生成对应的硬件电路。

实验步骤:1. 学习Verilog HDL的基本语法和结构2. 设计一个简单的数字电路,并实现Verilog模块描述其行为3. 使用仿真工具对设计的数字电路进行功能验证4. 使用综合工具生成对应的硬件电路实验结果:通过本实验,我们学习了Verilog HDL的基本概念和使用方法,并成功设计和实现了一个简单的数字电路。

我们使用仿真工具对设计的数字电路进行了功能验证,并使用综合工具生成了对应的硬件电路。

实验结果表明,Verilog HDL在数字电路设计中具有重要的应用价值。

《数字系统设计与Verilog HDL》实验报告(二)班级:自动1003班姓名:**学号:********实验二、四位并串转换电路一、实验目的1、了解及掌握时序电路的基本结构常用数字电路;2、通过ModelSim软件编写时序电路的程序进行仿真和调试。

二、实验内容1、熟悉时序电路中时钟的同步与异步用法;2、编写一个四位并串转换设计程序以及测试该模块的测试程序,要求如下:(1)输入一个四位二进制数pin;(2)每个时钟周期按从左往右的顺序输出一位pin的二进制位的数。

三、实验步骤及源程序新建工程及文件,分别添加设计程序及测试程序,进行编译及纠错,编译通过后运行程序仿真进行调试得出结果。

设计模块:module para_to_serial4(pin,clk,reset,sout);input [3:0] pin;input clk,reset;output sout;reg sout;reg [3:0] data;always @(posedge clk or negedge reset)beginif(~reset)beginsout<=1'b0;data<=pin;endelsebegindata<={data[2:0],data[3]};sout<=data[3];endendendmodule测试模块:`timescale 1ns/1nsmodule test_para_to_ser;wire sout;reg [3:0] pin;reg clk,reset;para_to_serial4 test1(pin,clk,reset,sout);initialbeginclk=1'b0;reset=1'b0;#5 reset=1'b1;#300 $stop;endinitialpin=4'b1001;always#5 clk=~clk;endmodule四、实验结果五、实验心得体会这次试验相对于上次有了一定的难度,由于这门课程刚开始学习,我还不能很好地从宏观把握这门课程,对这门课程的认识和理解还不够深刻,所以做实验时遇到了一些困难,虽然找了一些参考资料,有一定的帮助,但最后还是有点纠结,最终在和同学的交流中才比较深刻的对实验有了了解。

张威工作总结在完成本次verilog大作业的过程中,我不仅学到了很多只靠读书学不到的知识,而且体会到了团队协作的力量,以下做一简要总结:在这次作业中,我们首先进行分工合作,我和徐建龙负责bmp图像方面的工作,首先我们通过在网上和图书馆查阅资料,了解了bmp格式图像的基本知识,以便编写具体算法实现图像的翻转。

在对bmp格式文件有了一定掌握后,我们首先尝试用c++语言将其转换为txt 文件的格式,但是在查阅了相关资料后,发现这种方法过于复杂,因此最终放弃了这个思路。

随后我们查阅资料发现可以直接利用verilog的系统任务$fread即可对bmp文件进行操作,再结合文件输出任务$fopen\$fdisplay\$fclose将bmp文件打开并通过翻转算法转换后再写入txt文件,最后用软件WinHex将其转换为2进制文件并另存为bmp格式,即完成了翻转工作。

在这个过程中,我对课上学到的语句有了更深的理解,并将其应用到了实际工程中,使自己的运用能力得到了很好的锻炼,并且,我对Modelsim仿真软件也有了一定的了解,其基本操作已经较熟练的掌握,对其中一些细节问题,如仿真时间的选取等也有了自己的理解。

实践出真知,通过在软件上反复改程序、跑程序我也学会了很多只看书本发现不了的问题,锻炼了自己的解决问题能力。

最后,我还想感谢我的队友们,这次作业的完成使我们共同努力的结果,我真正感受到了团队的力量,也体会到了老师为什么一定要求必须结对完成的良苦用心。

在做工程的过程中,我们曾经对算法,流程等诸多问题产生过分歧,在屡次失败后,我们也曾想过放弃,但是我们最终团结一致,共同努力完成了作业,在图片成功翻转的那一霎那,所有的辛苦都有了回报,我们真正明白了什么叫teamwork!刘欢verilog大作业工作报告在团队成员的合作下,经历了许多困难,终于完成了verilog的大作业,虽然过程并不是和想象中的一样,而且作业也与老师要求的有所差距,但是在紧张的考试复习中,还是努力把这个作业完成了,并且从中学习到了许多关于verilog的使用与仿真的知识,这对于今后的学习是有很大的帮助的。

verilog课程设计实验报告一、教学目标本课程旨在通过Verilog硬件描述语言的学习,让学生掌握数字电路设计的自动化工具,理解并实践硬件描述语言在数字系统设计中的应用。

通过本课程的学习,学生应达到以下目标:1.知识目标:–理解Verilog的基本语法和结构。

–掌握Verilog中的模块化设计方法。

–学习常用的Verilog描述技巧,包括逻辑门级建模、行为级建模和结构级建模。

2.技能目标:–能够运用Verilog语言进行简单的数字电路设计。

–学会使用至少一种Verilog仿真工具进行电路功能验证。

–能够阅读和理解Verilog代码,进行简单的代码优化。

3.情感态度价值观目标:–培养学生的团队合作意识,在实验报告中能够体现分工合作的精神。

–培养学生的问题解决能力,鼓励学生在遇到问题时积极寻找解决方案。

–培养学生对新技术的好奇心和学习兴趣,激发他们对电子工程领域的热爱。

二、教学内容依据教学目标,本课程的教学内容将围绕Verilog语言的基础知识、实践应用和项目设计展开。

教学大纲安排如下:1.第一部分:Verilog基础知识(2周)–介绍Verilog的背景和基本概念。

–详细讲解Verilog的数据类型、运算符和语句。

2.第二部分:模块化设计(2周)–讲解模块的定义和封装。

–实践模块的端口声明和模块实例化。

3.第三部分:数字电路的Verilog描述(2周)–通过实例教学,掌握逻辑门、触发器等基本组件的Verilog建模。

–学习组合逻辑和时序逻辑的设计方法。

4.第四部分:仿真与测试(1周)–学习使用仿真工具进行电路功能验证。

–理解并实践测试台(testbench)的编写。

5.第五部分:项目设计(3周)–小组合作完成一个较为复杂的数字系统设计项目。

–包括系统模块的划分、编码、仿真和测试。

三、教学方法为了提高学生的学习效果,将采用多种教学方法相结合的方式进行授课:1.讲授法:用于讲解Verilog的基本概念和语法。

HDL(Verilog)课程设计报告(自动售货机)摘要本设计是以现场可编程逻辑器件(FPGA)为核心的自动售货机,利用QuartusⅡ软件编写verilog HDL 硬件描述语言程序以实现自动售货功能。

本设计主要以程序为主,硬件方面则使用实验箱,将程序各变量端口与实验箱管脚进行相应的配置,用八个开关分别代表商品价格、所投钱币价格及确认付款找零操作。

当选择好商品并投币后,数码管显示所选商品价格及投入钱币价格;按下确认付款开关,数码管显示应找多少钱,蜂鸣器响,对应商品LED灯亮。

若所投钱币不足所选商品价格,对应警告钱币不足的LED灯亮。

关键字:FPGA、Verilog HDL、自动售货机、Quartus ⅡAbstractThis design is an auto-vending machine based on field programmable logic devices (FPGA) . We use QuartusⅡto write procedure in verilog HDL which is a language to describe hardware. The procedure will realize the function of auto-vending machine.This design is mainly about procedure. For the hardware, we use experimental box. We allocate all variable quantities in the procedure to the feet in experimental box. We use eight switch respectively represent commodity prices and throw money price and confirm payment change operation. When choosing good commodities and coin, digital pipe display selected commodity prices and money price. When pressing confirm payment switch, digital pipe display should find how much money, buzzer sounded, corresponding commodity LED lights. If throw money shortage selected commodity prices, corresponding warning money shortage of LED lights.Keywords: FPGA、Verilog HDL、auto-vending machine、QuartusⅡ目录摘要 I第一章系统设计 11.1 系统设计 11.2 系统设计方案比较 11.2.1 总体设计 11.2.1 设计方案比较 1第二章详细设计 22.1 自动售货机状态描述 22.2 详细状态描述 32.2.1 初始状态 32.2.2 选商品状态 32.2.3 投币状态 32.2.4 找零状态 3第三章软件设计 33.1 程序总流程图 33.2 程序 4第四章结果与讨论 74.1 实验调试 74.1.1 调试步骤 74.1.2 实验现象 74.2 结果与分析 8总结 8参考文献 8附录 9第一章系统设计1.1系统设计(1)用四个发光二极管分别模拟售出价值为5角、1元、1.5元和2元的小商品,购买者可以通过开关选择任意一种标价中的小商品。

![[数字系统设计与Verilog HDL(第7版 (9)[24页]](https://img.taocdn.com/s1/m/b3ae09846f1aff00bfd51e1e.png)

Verilog HDL高级数字设计实验报告题目:“俄罗斯方块”FPGA实现实验目的通过此次项目,完成以下目的:1)熟悉Xilinx FPGA的架构及开发流程2)设计一个功能完整的系统,掌握FSM + Datapath的设计方法。

实验内容1.项目介绍本项目主要在FPGA上实现了一个经典小游戏“俄罗斯方块”。

本项目基本解决方案是,使用Xilinx Zynq系列开发板ZedBoard作为平台,实现主控模块,通过VGA接口来控制屏幕进行显示。

2.系统框架整个系统由四部分组成,按键输入处理模块、控制模块、数据路径模块以及VGA显示接口模块。

整个系统的结构如下图所示:图1:系统框图下面分别对四个模块进行介绍:1)按键输入处理模块按键处理模块的主要功能是对输入系统的up,down,left,right四个控制信号进行消抖处理,并对其进行上升沿检测。

消抖模块采用上课所提出的结构,采用了一个4位的移位寄存器,先将输入信号延迟4个时钟周期,再对其以一个较低的时钟频率进行采用。

消抖模块的结构如下图所示:图2:消抖模块结构示意图为了简化控制系统,在本系统的设计过程中,不考虑长时间按键产生连按效果。

因而,需要对按键进行上升沿检测。

上升沿检测的基本实现方案是加入一组寄存器,对前一个的按键信号进行暂存,将暂存的值与当前值进行比较,当上一个值为0而当前值为1时,即认为其检测到了一个上升沿。

2)控制模块控制模块采用FSM的方式进行控制。

在控制模块中,定义了10个状态:S_idle:上电复位后进入的空状态,当start信号为1时进入S_new状态S_new:用于产生新的俄罗斯方块。

S_hold:保持状态。

在这个状态中进行计时,当时间到达一定间隔时,转到S_down 状态;或者等待输入信号(up,down,left,right)时,转到S_down(按键为down)或者S_move(up,left,right)状态。

S_down:判断当前俄罗斯块能否下移一格。

FPGA设计与实践题目:姓名:学号:学院:专业:年级:指导教师:2017年01月07日FPGA设计与实践评分表目录实验一与或非 01.1实验目的 01.2实验要求 01.3实验内容 01.3.1 设计 01.3.2 源程序 01.3.3 测试程序 (1)1.4仿真结果 (1)1.5分析总结 (1)实验二半加器 (2)2.1实验要求 (2)2.2实验内容 (2)2.2.1 设计 (2)2.2.2 源程序 (2)2.2.3 测试程序 (3)2.3仿真结果 (3)实验三全加器 (3)3.1实验要求 (3)3.2实验内容 (3)3.2.1 设计 (3)3.2.2 源程序 (4)3.2.3 测试程序 (4)3.3仿真结果 (4)实验四 2选1MUX (5)4.1实验要求 (5)4.2实验内容 (5)4.2.1 设计 (5)4.2.2 源程序 (5)4.2.3 测试程序 (5)4.3仿真结果 (6)实验五奇偶校验器 (6)5.1实验要求 (6)5.2实验内容 (6)5.2.1 设计 (6)5.2.2 源程序 (6)5.2.3 测试程序 (7)5.3仿真结果 (7)实验六比较器 (7)6.1实验要求 (7)6.2实验内容 (8)6.2.1 设计 (8)6.2.2 源程序 (8)6.2.3 测试程序 (8)6.3仿真结果 (9)实验七计数器 (9)7.1实验要求 (9)7.2实验内容 (9)7.2.1 设计 (9)7.2.2 源程序 (10)7.2.3 测试程序 (10)7.3仿真结果 (11)实验八 LATCH (11)8.1实验要求 (11)8.2实验内容 (11)8.2.1 设计 (11)8.2.2 源程序 (12)8.2.3 测试程序 (12)8.3仿真结果 (13)实验九移位寄存器 (13)9.1实验要求 (13)9.2实验内容 (13)9.2.1 设计 (13)9.2.2 源程序 (14)9.2.3 测试程序 (14)9.3仿真结果 (15)实验十 ALU (15)10.1实验要求 (15)10.2实验内容 (15)10.2.2 源程序 (16)10.2.3 测试程序 (17)10.3仿真结果 (17)实验十一优先编码器 (18)11.1实验要求 (18)11.2实验内容 (18)11.2.1 设计 (18)11.2.2 源程序 (19)11.2.3 测试程序 (20)11.3仿真结果 (20)实验十二四位加法器 (21)12.1实验要求 (21)12.2实验内容 (21)12.2.1 设计 (21)12.2.2 源程序 (21)12.2.3 测试程序 (22)12.3仿真结果 (22)实验十三状态机 (23)13.1实验要求 (23)13.2实验内容 (23)13.2.1 设计 (23)13.2.2 源程序 (23)13.2.3 测试程序 (24)13.3仿真结果 (25)实验十四偶分频 (25)14.1实验要求 (25)14.2实验内容 (25)14.2.1 设计 (25)14.2.2 源程序 (26)14.2.3 测试程序 (26)14.3仿真结果 (27)实验十五奇分频 (27)15.1实验要求 (27)15.2实验内容 (27)15.2.1 设计 (27)15.2.3 测试程序 (28)15.3仿真结果 (28)实验一与或非1.1 实验目的(1)熟悉Modelsim软件;(2)掌握Modelsim软件的编译、仿真方法;(3)熟练运用Modelsim 软件进行Verilog HDL 程序设计开发.1.2 实验要求自行设计“与-或-非”门电路,根据设计的门级电路模型,设计verilog模型。

实验三:verilog HDL中任务与函数的数字系统设计班级:通信二班姓名:孔晓悦学号:10082207作业完成后,以班级为单位,班长或课代表收集齐电子版实验报告,统一提交.文件命名规则如“通1_王五_学号”一、实验目的1、了解verilog HDL任务与函数的定义及格式2、掌握函数与任务的定义与调用3、掌握函数与任务在使用时的区别4、掌握任务与函数的具体应用二、预习要求1.复习veirlogHDL行为语句。

2. 预习任务与函数的相关定义和格式要求。

3.简单电路系统设计的流程和方法。

三、实验基本概念1、任务定义☐任务定义格式:task <任务名>;//注意无端口列表端口及数据类型声明语句;其它语句;endtask☐任务调用的格式为:<任务名>(端口1,端口2,……);☐需要注意的是:任务调用时和定义时的端口变量应是一一对应的。

☐注意事项:●任务的定义与调用须在一个module模块内。

●定义任务时,没有端口名列表,但需要紧接着进行输入输出端口和数据类型的说明。

●当任务被调用时,任务被激活。

任务的调用与模块调用一样通过任务名调用实现,调用时,需列出端口名列表,端口名的排序和类型必须与任务定义中的相一致。

●一个任务可以调用别的任务和函数,可以调用的任务和函数个数不限。

2、函数定义☐函数的目的是返回一个值,以用于表达式计算☐函数的定义格式:function <返回值位宽或类型说明> 函数名;端口声明;局部变量定义;其它语句;endfunction☐<返回值位宽或类型说明>是一个可选项,如果缺省,则返回值为1位寄存器类型的数据。

☐注意事项:●函数的定义与调用须在一个module模块内。

●函数只允许有输入变量且必须至少有一个输入变量,输出变量由函数名本身担任,在定义函数时,需对函数名说明其类型和位宽。

●定义函数时,没有端口名列表,但调用函数时,需列出端口名列表,端口名的排序和类型必须与定义时的相一致。

Verilog数字电路设计实验名称Verilog数字电路设计班级130324姓名张先炳13031205同组者廖瑞13031191自动化与电气工程学院2016年4月25日目录目录 (2)实验一简单组合逻辑设计 (1)1 实验目的 (1)2 实验设备 (1)3 实验内容 (1)4 实验代码 (1)5 仿真结果 (2)选作一:设计一个字节的比较器 (3)1 实验要求 (3)2 模块代码 (3)3 测试代码 (3)4 仿真结果 (4)实验二简单分频时序逻辑电路的设计 (4)1 实验目的 (4)2 实验设备 (4)3 实验内容 (5)4 实验代码 (5)5 仿真结果 (6)选作二:七段数码管译码电路 (6)1 实验要求 (6)2 模块代码 (7)3 测试代码 (8)4 仿真结果 (8)实验三:利用条件语句实现计数分频时序电路 (9)1 实验目的 (9)2 实验设备 (9)3 实验内容 (9)4 实验代码 (9)5 仿真结果 (11)6 实验分析 (11)选作三:设计一个单周期形状的周期波形。

(11)1 实验要求 (11)2 模块代码 (11)3 测试代码 (12)4 仿真结果 (13)实验四:用always块实现较复杂的组合逻辑 (13)1 实验目的 (13)2 实验设备 (13)3 实验内容 (13)4 实验代码 (14)5 仿真结果 (16)选作四:运用always块设计一个8路数据选择器。

(16)1 实验要求 (16)2 模块代码 (16)3 测试代码 (17)4 仿真结果 (18)实验五:在Verilog HDL中使用函数 (19)1 实验目的 (19)2 实验设备 (19)3 实验内容 (19)4 实验代码 (19)5 仿真结果 (21)选作五:设计一个带控制端的逻辑运算电路 (22)1 实验要求 (22)2 模块代码 (22)3 测试代码 (23)4 仿真结果 (25)实验六:在Verilog HDL中使用任务(task) (25)1 实验目的 (25)2 实验设备 (25)3 实验内容 (25)4 实验代码 (25)5 仿真结果 (28)选作六:冒泡法排序 (28)1 实验要求 (28)2 模块代码 (28)3 测试代码 (29)4 仿真结果 (30)选作七:串行输入排序 (30)1 实验要求 (30)2 模块代码 (31)3 测试代码 (32)4 仿真结果 (33)5 实验分析 (34)实验七:利用有限状态机进行时序逻辑的设计 (34)1 实验目的 (34)2 实验设备 (34)3 实验内容 (35)4 实验代码 (35)5 仿真结果 (37)6 实验分析 (37)选作八:楼梯灯 (37)1 实验要求 (37)2 模块代码 (38)3 测试代码 (45)4 仿真结果 (47)5 实验分析 (47)附:分工明细 (49)实验一简单组合逻辑设计1 实验目的1、掌握基本组合逻辑电路的实现方法。

可编程逻辑器件设计实验报告实验名称:第二部分:VerilogHDL基础实验实验目的:掌握Quartus II 软件的基本使用方法,完成基本时序电路设计实验时间: 2014 年 06 月 19 日地点: 803实验室学生姓名:学号:实验名称:简单D触发器实验一简单D触发器1、实验步骤(1)创建工程启动New Project Wizard,创建一个工程。

(2)创建文件选择菜单File—>New—>Verilog HDL File,创建一个Verilog HDL文件,在Verilog HDL文件中编写能够完成实验功能的Verilog HDL代码。

(3)编译工程选择菜单Processing —>Start Compilation,或者单击按钮。

(4)观察RTL视图选择菜单Tools—>Netlist Viewers—>RTL Viewer即可生成RTL视图。

(5)仿真1).创建VWF文件选择菜单File—>New—>Vector Waveform File2). 设定“End Time”选择菜单Edit File—> End Time,在弹出的对话框中将Time设置为20us。

3).在VWF文件中输入信号节点选择菜单View—>Utility Windows—>Node Finder,在出现的对话框中将Filter框中设置为Pins:all,再单击List按钮,从端口列表中选择需要观察的并拖到波形编辑窗口中。

4).编辑输入信号波形5).观察仿真结果选择菜单Processing—>Start Simulation,或者单击按钮,观察输出波形。

2. VerilogHDL代码module _DFF (clk,d,q);input clk,d;output q;reg q;always@ (posedge clk)beginq<=d;endendmodule3. RTL 视图4.仿真波形实验二同步置数的D触发器1.实验步骤(1)创建工程启动New Project Wizard,创建一个工程。

Verilog HDL 数字系统设计报告 9

姓名 林勇 学号 11122240

时间 2013.10.02 地点 II 教102 实验室

实验题目 利用状态机实现比较复杂的接口设计

一. 实验目的与要求

(1)学习运用由状态机控制的逻辑开关,设计出一个比较复杂的接口逻辑;

(2)在复杂设计中使用任务(task )结构,以提高程序的可读性;

(3)加深对可综合风格模块的认识。

二. 实验环境

CPU 型号:Intel(R) Core(TM)i3 CPU 内存容量:2.00GB

操作系统类型:32位Win7操作系统 仿真软件:ModelSim SE 6.2b

三. 实验内容

该例是一个并行数据转换为串行位流的变换,利用双向总线输出。

通过基本时钟的运行,使得并行数据一位一位的输出。

四. 系统框图

input

clk

五. 实验波形图

六、体会

状态译码器 状态寄存器 输出译码器 output

在这个实验中,由于代码是复制粘贴的,不知道为什么刚开始编译的时候总有一行会出现错误,但是回去仔细分析代码的时候却怎么也找不出错在哪里,后来解决的办法是在那行之前的代码通过自己手动输入进去,后来就做好了。

针对这个错误的分析我认为是在复制粘贴的时候出现了乱码。

这个实验是第一次接触到状态机和task结构,对我来说读懂这个代码有一定的难度,直到现在我还是不能完全理解这整个代码的过程。

七、代码

// ------------- 测试模块源代码:----------------

`timescale 1ns/100ps

`define clk_cycle 50

module writingTop;

reg reset,clk;

reg[7:0] data,address;

wire ack,sda;

always #`clk_cycle clk = ~clk;

initial

begin

clk=0;

reset=1;

data=0;

address=0;

#(2*`clk_cycle) reset=0;

#(2*`clk_cycle) reset=1;

#(100*`clk_cycle) $stop;

end

always @(posedge ack) //接收到应答信号后,给出下一个处理对象。

begin

data=data+1;

address=address+1;

end

writing writing(.reset(reset),.clk(clk),.data(data),

.address(address),.ack(ack),.sda(sda));

endmodule。