0500_w12_qp_32

- 格式:pdf

- 大小:68.91 KB

- 文档页数:4

ALC5621I2S AUDIO CODEC + 1.3W CLASS AB/D MONO SPEAKER AMPLIFIERDATASHEETRev. 1.027 December 2007Track ID: JATR-1076-21Realtek Semiconductor Corp.No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, TaiwanTel.: +886-3-578-0211. Fax: +886-3-577-6047I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifierii Track ID: JATR-1076-21 Rev. 1.0COPYRIGHT ©2007 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp.DISCLAIMERRealtek provides this document “as is”, without warranty of any kind, neither expressed nor implied, including, but not limited to, the particular purpose. Realtek may make improvements and/or changes in this document or in the product described in this document at any time. This document could include technical inaccuracies or typographical errors.TRADEMARKSRealtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners.USING THIS DOCUMENTThis document is intended for the hardware and software engineer’s general information on the Realtek ALC5621 Audio Codec IC.Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this guide. In that event, please contact your Realtek representative for additional information that may help in the development process. REVISION HISTORYRevision Release Date Summary1.0 2007/12/27 First releaseTable of Contents1.GENERAL DESCRIPTION (1)2.FEATURES (2)3.SYSTEM APPLICATIONS (2)4.BLOCK DIAGRAMS (3)4.1.F UNCTION B LOCK (3)4.2.A UDIO M IXER P ATH (4)5.PIN ASSIGNMENTS (5)5.1.G REEN P ACKAGE AND V ERSION I DENTIFICATION (5)6.PIN DESCRIPTIONS (6)6.1.D IGITAL I/O P INS (6)6.2.A NALOG I/O P INS (6)6.3.F ILTER/R EFERENCE (7)6.4.P OWER/G ROUND (7)7.FUNCTIONAL DESCRIPTION (8)7.1.P OWER (8)7.2.R ESET (8)7.2.1.Power-On Reset (POR) (8)7.3.C LOCKING (9)7.3.1.Phase-Locked Loop (9)7.3.2.I2C and Stereo I2S (10)7.4.D IGITAL D ATA I NTERFACE (11)7.4.1.Stereo I2S/PCM Interface (11)7.5.A UDIO D ATA P ATH (14)7.5.1.Vref (14)7.5.2.Stereo ADC (14)7.5.3.Stereo DAC (14)7.6.M IXERS (15)7.6.1.Headphone Mixer (15)7.6.2.MONO Mixer (16)7.6.3.Speaker Mixer (16)7.6.4.ADC Record Mixer (17)7.7.A NALOG A UDIO I NPUT P ATH (18)7.7.1.Line Input (18)7.7.2.AUXiliary Input (18)7.7.3.Microphone Input (18)7.8.A NALOG A UDIO O UTPUT D ATA P ATH (19)7.8.1.Speaker Output (19)7.8.2.Headphone Output (20)7.8.3.MONO Output (20)7.9.AVC C ONTROL (21)7.10.H ARDWARE S OUND E FFECTS (23)7.10.1.Equalizer Block (23)7.10.2.Pseudo Stereo and Spatial 3D Sound (23)7.11.I2C C ONTROL I NTERFACE (24)7.11.1.Addressing Setting (24)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier iii Track ID: JATR-1076-21 Rev. 1.0plete Data Transfer (24)7.12.O DD-A DDRESSED R EGISTER A CCESS (25)7.13.P OWER M ANAGEMENT (25)7.14.GPIO AND J ACK D ETECT F UNCTION (26)7.15.I NTERNAL E VENT S IGNAL I NTERRUPTS (27)7.16.H EADPHONE D EPOP (27)8.MIXER REGISTERS LIST (28)8.1.R EG-00H:R ESET (28)8.2.R EG-02H:S PEAKER O UTPUT V OLUME (28)8.3.R EG-04H:H EADPHONE O UTPUT V OLUME (29)8.4.R EG-06H:MONO_OUT/AUXOUT V OLUME (30)8.5.R EG-08H:AUXIN V OLUME (30)8.6.R EG-0A H:LINE_IN V OLUME (31)8.7.R EG-0C H:STEREO DAC V OLUME (31)8.8.R EG-0E H:MIC V OLUME (32)8.9.R EG-10H:MIC R OUTING C ONTROL (32)8.10.R EG-12H:ADC R ECORD G AIN (33)8.11.R EG-14H:ADC R ECORD M IXER C ONTROL (33)8.12.R EG-16H:A VOL S OFT V OLUME C ONTROL T IME (34)8.13.R EG-1C H:O UTPUT M IXER C ONTROL (34)8.14.R EG-22H:M ICROPHONE C ONTROL (35)8.15.R EG-34H:D IGITAL A UDIO I NTERFACE C ONTROL (35)8.16.R EG-36A H:S TEREO AD/DA C LOCK C ONTROL (36)8.17.R EG-38H:C OMPANDING C ONTROL (37)8.18.R EG-3A H:P OWER M ANAGEMENT A DDITION 1 (37)8.18.1.Headphone Output Amplifier Configuration (38)8.18.2.Auxiliary Output Amplifier Configuration (38)8.19.R EG-3C H:P OWER M ANAGEMENT A DDITION 2 (39)8.20.R EG-3E H:P OWER M ANAGEMENT A DDITION 3 (40)8.21.R EG-40H:A DDITIONAL C ONTROL R EGISTER (41)8.22.R EG-42H:G LOBAL C LOCK C ONTROL R EGISTER (42)8.23.R EG-44H:PLL C ONTROL R EGISTER (42)8.23.1.Reg-44h: PLL Control Register (42)8.23.2.PLL Clock Setting Table for 48K: (Unit: MHz) (43)8.23.3.PLL Clock Setting Table for 44.1K: (Unit: MHz) (43)8.24.R EG-4A H:GPIO_O UTPUT P IN C ONTROL (43)8.25.R EG-4C H:GPIO P IN C ONFIGURATION (44)8.26.R EG-4E H:GPIO P IN P OLARITY (44)8.27.R EG-50H:GPIO P IN S TICKY (45)8.28.R EG-52H:GPIO P IN W AKE-U P (45)8.29.R EG-54H:GPIO P IN S TATUS (46)8.30.R EG-56H:P IN S HARING (46)8.31.R EG-58H:O VER-C URRENT S TATUS (47)8.32.R EG-5A H:J ACK D ETECT C ONTROL R EGISTER (47)8.33.R EG-5E H:MISC C ONTROL (48)8.34.R EG-60H:S TEREO AND S PATIAL E FFECT B LOCK C ONTROL (49)8.35.R EG-62H:EQ C ONTROL (50)8.36.R EG-66H:EQ M ODE C HANGE E NABLE (51)8.37.R EG-68H:AVC C ONTROL (51)8.38.R EG-6A H:I NDEX A DDRESS (52)8.39.R EG-6C H:I NDEX D ATA (52)8.40.I NDEX-00H:EQ B AND-0C OEFFICIENT (LP0: A1) (52)8.41.I NDEX-01H:EQ B AND-0G AIN (LP0:H O) (52)8.42.I NDEX-02H:EQ B AND-1C OEFFICIENT (BP1: A1) (53)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier iv Track ID: JATR-1076-21 Rev. 1.08.43.I NDEX-03H:EQ B AND-1C OEFFICIENT (BP1: A2) (53)8.44.I NDEX-04H:EQ B AND-1G AIN (BP1:H O) (53)8.45.I NDEX-05H:EQ B AND-2C OEFFICIENT (BP2: A1) (53)8.46.I NDEX-06H:EQ B AND-2C OEFFICIENT (BP2: A2) (54)8.47.I NDEX-07H:EQ B AND-2G AIN (BP2:H O) (54)8.48.I NDEX-08H:EQ B AND-3C OEFFICIENT (BP3: A1) (54)8.49.I NDEX-09H:EQ B AND-3C OEFFICIENT (BP3: A2) (54)8.50.I NDEX-0A H:EQ B AND-3G AIN (BP3:H O) (55)8.51.I NDEX-0B H:EQ B AND-4C OEFFICIENT (HPF: A1) (55)8.52.I NDEX-0C H:EQ B AND-4G AIN (HPF:H O) (55)8.53.I NDEX-11H:EQ I NPUT V OLUME C ONTROL (55)8.54.I NDEX-12H:EQ O UTPUT V OLUME C ONTROL (56)8.55.I NDEX-21H:A UTO V OLUME C ONTROL R EGISTER 1 (56)8.56.I NDEX-22H:A UTO V OLUME C ONTROL R EGISTER 2 (56)8.57.I NDEX-23H:A UTO V OLUME C ONTROL R EGISTER 3 (56)8.58.I NDEX-24H:A UTO V OLUME C ONTROL R EGISTER 4 (57)8.59.I NDEX-25H:A UTO V OLUME C ONTROL R EGISTER 5 (57)8.60.I NDEX-39H:D IGITAL I NTERNAL R EGISTER (57)8.61.I NDEX-46H:C LASS D I NTERNAL R EGISTER (58)8.62.R EG-7C H:VENDOR ID1 (58)8.63.R EG-7E H:VENDOR ID2 (58)9.ELECTRICAL CHARACTERISTICS (59)9.1.DC C HARACTERISTICS (59)9.1.1.Absolute Maximum Ratings (59)9.1.2.Recommended Operating Conditions (59)9.1.3.Static Characteristics (59)9.2.A NALOG P ERFORMANCE C HARACTERISTICS (60)9.3.S IGNAL T IMING (62)9.3.1.I2C Control Interface (62)9.3.2.I2S Master Mode (63)9.3.3.I2S Slave Mode (64)10.APPLICATION CIRCUIT (65)11.MECHANICAL DIMENSIONS (66)12.APPENDIX A: STEREO I2S CLOCK TABLE (68)13.ORDERING INFORMATION (69)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier v Track ID: JATR-1076-21 Rev. 1.0List of TablesT ABLE 1.D IGITAL I/O P INS (6)T ABLE 2.A NALOG I/O P INS (6)T ABLE 3.F ILTER/R EFERENCE (7)T ABLE 4.P OWER/G ROUND (7)T ABLE 5.R ESET O PERATION (8)T ABLE 6.P OWER-O N R ESET V OLTAGE (8)T ABLE 7.C LOCK S ETTING T ABLE FOR 48K(U NIT:MH Z) (9)T ABLE 8.C LOCK S ETTING T ABLE FOR 44.1K(U NIT:MH Z) (10)T ABLE 9.MONO/AUXOUT O UTPUT S IGNAL T ABLE (20)T ABLE 10.A DDRESSING S ETTING (24)T ABLE 11.W RITE WORD P ROTOCOL (25)T ABLE 12.R EAD WORD P ROTOCOL (25)T ABLE 13.R EG-00H:R ESET (28)T ABLE 14.R EG-02H:S PEAKER O UTPUT V OLUME (28)T ABLE 15.R EG-04H:H EADPHONE O UTPUT V OLUME (29)T ABLE 16.R EG-06H:MONO_OUT/AUXOUT V OLUME (30)T ABLE 17.R EG-08H:AUXIN V OLUME (30)T ABLE 18.R EG-0A H:LINE_IN V OLUME (31)T ABLE 19.R EG-0C H:STEREO DAC V OLUME (31)T ABLE 20.R EG-0E H:MIC V OLUME (32)T ABLE 21.R EG-10H:MIC R OUTING C ONTROL (32)T ABLE 22.R EG-12H:ADC R ECORD G AIN (33)T ABLE 23.R EG-14H:ADC R ECORD M IXER C ONTROL (33)T ABLE 24.R EG-16H:A VOL S OFT V OLUME C ONTROL T IME (34)T ABLE 25.R EG-1C H:O UTPUT M IXER C ONTROL (34)T ABLE 26.R EG-22H:M ICROPHONE C ONTROL (35)T ABLE 27.R EG-34H:A UDIO I NTERFACE (35)T ABLE 28.R EG-36H:S TEREO AD/DA C LOCK C ONTROL (36)T ABLE 29.R EG-38H:C OMPANDING C ONTROL (37)T ABLE 30.R EG-3A H:P OWER M ANAGEMENT A DDITION 1 (37)T ABLE 31.H EADPHONE O UTPUT A MPLIFIER C ONFIGURATION (38)T ABLE 32.A UXILIARY O UTPUT A MPLIFIER C ONFIGURATION (38)T ABLE 33.R EG-3C H:P OWER M ANAGEMENT A DDITION 2 (39)T ABLE 34.R EG-3E H:P OWER M ANAGEMENT A DDITION 3 (40)T ABLE 35.R EG-40H:A DDITIONAL C ONTROL R EGISTER (41)T ABLE 36.R EG-42H:G LOBAL C LOCK C ONTROL R EGISTER (42)T ABLE 37.R EG-44H:PLL C ONTROL R EGISTER (42)T ABLE 38.PLL C LOCK S ETTING T ABLE FOR 48K:(U NIT:MH Z) (43)T ABLE 39.PLL C LOCK S ETTING T ABLE FOR 44.1K:(U NIT:MH Z) (43)T ABLE 40.R EG-4C H:GPIO_O UTPUT P IN C ONTROL (43)T ABLE 41.R EG-4C H:GPIO P IN C ONFIGURATION (44)T ABLE 42.R EG-4E H:GPIO P IN P OLARITY (44)T ABLE 43.R EG-50H:GPIO P IN S TICKY (45)T ABLE 44.R EG-52H:GPIO P IN W AKE-U P (45)T ABLE 45.R EG-54H:GPIO P IN S TATUS (46)T ABLE 46.R EG-56H:P IN S HARING (46)T ABLE 47.R EG-58H:O VER-C URRENT S TATUS (47)T ABLE 48.R EG-5A H:J ACK D ETECT C ONTROL R EGISTER (47)T ABLE 49.R EG-5E H:MISC C ONTROL (48)T ABLE 50.R EG-60H:S TEREO AND S PATIAL E FFECT B LOCK C ONTROL (49)T ABLE 51.R EG-62H:EQ C ONTROL (50)T ABLE 52.R EG-66H:EQ M ODE C HANGE E NABLE (51)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier vi Track ID: JATR-1076-21 Rev. 1.0T ABLE 53.R EG-68H:AVC C ONTROL (51)T ABLE 54.R EG-6A H:I NDEX A DDRESS (52)T ABLE 55.R EG-6C H:I NDEX D ATA (52)T ABLE 56.I NDEX-00H:EQ B AND-0C OEFFICIENT (LP0: A1) (52)T ABLE 57.I NDEX-01H:EQ B AND-0G AIN (LP0:H O) (52)T ABLE 58.I NDEX-02H:EQ B AND-1C OEFFICIENT (BP1: A1) (53)T ABLE 59.I NDEX-03H:EQ B AND-1C OEFFICIENT (BP1: A2) (53)T ABLE 60.I NDEX-04H:EQ B AND-1G AIN (BP1:H O) (53)T ABLE 61.I NDEX-05H:EQ B AND-2C OEFFICIENT (BP2: A1) (53)T ABLE 62.I NDEX-06H:EQ B AND-2C OEFFICIENT (BP2: A2) (54)T ABLE 63.I NDEX-07H:EQ B AND-2G AIN (BP2:H O) (54)T ABLE 64.I NDEX-08H:EQ B AND-3C OEFFICIENT (BP3: A1) (54)T ABLE 65.I NDEX-09H:EQ B AND-3C OEFFICIENT (BP3: A2) (54)T ABLE 66.I NDEX-0A H:EQ B AND-3G AIN (BP3:H O) (55)T ABLE 67.I NDEX-0B H:EQ B AND-4C OEFFICIENT (HPF: A1) (55)T ABLE 68.I NDEX-0C H:EQ B AND-4G AIN (HPF:H O) (55)T ABLE 69.I NDEX-11H:EQ I NPUT V OLUME C ONTROL (55)T ABLE 70.I NDEX-12H:EQ O UTPUT V OLUME C ONTROL (56)T ABLE 71.I NDEX-21H:A UTO V OLUME C ONTROL R EGISTER 1 (56)T ABLE 72.I NDEX-22H:A UTO V OLUME C ONTROL R EGISTER 2 (56)T ABLE 73.I NDEX-23H:A UTO V OLUME C ONTROL R EGISTER 3 (56)T ABLE 74.I NDEX-24H:A UTO V OLUME C ONTROL R EGISTER 4 (57)T ABLE 75.I NDEX-25H:A UTO V OLUME C ONTROL R EGISTER 5 (57)T ABLE 76.I NDEX-39H:D IGITAL I NTERNAL R EGISTER (57)T ABLE 77.I NDEX-46H:C LASS D I NTERNAL R EGISTER (58)T ABLE 78.R EG-7C H:VENDOR ID1 (58)T ABLE 79.R EG-7E H:VENDOR ID2 (58)T ABLE 80.A BSOLUTE M AXIMUM R ATINGS (59)T ABLE 81.R ECOMMENDED O PERATING C ONDITIONS (59)T ABLE 82.S TATIC C HARACTERISTICS (59)T ABLE 83.A NALOG P ERFORMANCE C HARACTERISTICS (60)T ABLE 84.I2C T IMING (62)T ABLE 85.T IMING OF I2S M ASTER M ODE (63)T ABLE 86.I2S S LAVE M ODE T IMING (64)T ABLE 87.O RDERING I NFORMATION (69)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier vii Track ID: JATR-1076-21 Rev. 1.0List of FiguresF IGURE 1.B LOCK D IAGRAM (3)F IGURE 2.A UDIO M IXER P ATH (4)F IGURE 3.P IN A SSIGNMENTS (5)F IGURE 4.A UDIO SYSCLK (9)F IGURE 5.PCM M ONO D ATA M ODE A F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0, PCM_MODE_SEL=0) (11)F IGURE 6.PCM M ONO D ATA M ODE A F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=1, PCM_MODE_SEL=0) (11)F IGURE 7.PCM M ONO D ATA M ODE B F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0, PCM_MODE_SEL=1) (12)F IGURE 8.PCM S TEREO D ATA M ODE A F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0, PCM_MODE_SEL=0) (12)F IGURE 9.PCM S TEREO D ATA M ODE B F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0, PCM_MODE_SEL=1) (12)F IGURE 10.I2S D ATA F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0) (13)F IGURE 11.L EFT J USTIFIED D ATA F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0) (13)F IGURE 12.R IGHT J USTIFIED D ATA F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0) (13)F IGURE 13.A UTO V OLUME C ONTROL B LOCK D IAGRAM (22)F IGURE 14.AVC B EHAVIOR (22)F IGURE 15.D ATA T RANSFER O VER I2C C ONTROL I NTERFACE (24)F IGURE 16.GPIO I MPLEMENTATION (26)F IGURE 17.J ACK D ETECT AND IRQ L OGIC (27)F IGURE 18.P OWER C ONTROL TO MIC I NPUT (41)F IGURE 19.J ACK-I NSERT-D ETECT P ULL U P R ESISTER I MPLEMENTED VIA AN E XTERNAL C IRCUIT (49)F IGURE 20.I2C C ONTROL I NTERFACE (62)F IGURE 21.T IMING OF I2S M ASTER M ODE (63)F IGURE 22.I2S S LAVE M ODE T IMING (64)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier viii Track ID: JATR-1076-21 Rev. 1.01.General DescriptionThe ALC5621 is a highly-integrated I2S/PCM interface audio codec with multiple input/output ports and is designed for mobile computing and communications. It provides a Stereo Hi-Fi DAC for playback and Stereo ADC for recording via the I2S/PCM interface.To reduce component count, the device can connect directly to:•MONO or stereo differential analog inputs•LINE_IN stereo Single-Ended analog inputs•AUX_IN Single-Ended analog inputs•Stereo Headphone Output•Single-end stereo configurable to AUXOUT or BTL MONO_OUT•MONO or Stereo Bridge-Tied Load (BTL) speakerMultiple analog input and output pins are provided for seamless integration with analog connected wireless communication devices. Differential input/output connections efficiently reduce noise interference, providing better sound quality. Class AB or Class D amplifiers are easily swapped via simple register configuration, and the 1.3 Watt Mono speaker removes the need for an additional amplifier, further cutting both cost and required board area. Additionally, a flexible hardware 5-band equalizer with configurable gain, bandwidth, and center frequency, enriches the sound experience.The ALC5621 AVDD operates at supply voltages from 2.3V to 3.6V. DVDD operates from 1.71 to 3.6V, and SPKVDD operates from 2.3 to 5V. To extend battery life, each section of the device can be powered down individually under software control. Leakage current in maximum power saving state is less than 10µA.The ALC5621 is available in a 5x5mm ‘Green’ QFN-32 package, making it ideal for use in handheld portable systems.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 1Track ID: JATR-1076-21 Rev. 1.0I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 2Track ID: JATR-1076-21 Rev. 1.0 2. FeaturesDigital-to-Analog Converter with 92dB SNR and –85dB THD+N Analog-to-Digital Converter with 85dB SNR and –80dB THD+N Two analog stereo single-ended inputs, LINE-IN_L/R and AUXIN_L/R Stereo differential analog microphone inputs, with boost pre-amplifiers (+20/+30/+40dB) BTL (Bridge-Tied Load) Speaker output with on-chip 1.3W speaker driver (SPKVDD=5V, 4.7Ω load with THD+N=40dB) Mono Speaker output supports Class AB or Class D optional Stereo headphone output with on-chip 45mW headphone driver (AVDD=3.3V, 16Ω load) 25mW SE or 75mW BTL Single-Ended differential MONO_OUT configurable to AUXOUT (AVDD=3.3V, 32Ω load)Audio jack insert detection and microphoneswitch detectionPower management and enhanced powersavingSupports digital 5-band equalizer (EQ) Supports digital spatial sound and pseudostereo effectSupports pop noise suppressionInternal PLL can receive wide range of clockinputDigital power supplies from 1.71V to 3.6V;speaker amplifier power supplies from 2.3V to 5VAnalog power and headphone power suppliedfrom 2.3V to 3.6VSupports soft-mute function32-pin QFN package3. System Applications Tablet PC system/Ultra-Mobile PC (UMPC) Personal Digital Assistants (PDA) or PDA Phone Multimedia Phone ApplicationsPortable Navigation Device (PND)Bluetooth HeadphoneI S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier3Track ID: JATR-1076-21 Rev. 1.04.Block Diagrams4.1.Function BlockMICBIASSDAM C L KSCLK SPK_OUT_NSPK_OUT AUXOUT_RAUXOUT_L LINE_IN_R LINE_IN_L MIC1P MIC1N MIC2P MIC2N ALC5621D A C D A TA D C D A TB C L KL R C KAUXIN_L AUXIN_RG P I O /I R QPLL_OUTFigure 1. Block DiagramI S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 4Track ID: JATR-1076-21 Rev. 1.04.2.Audio Mixer Path)10[1210[4]5]L +R+RR+RFigure 2. Audio Mixer PathI S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 5Track ID: JATR-1076-21 Rev. 1.0M I C 1PM I C 2PM I C 1NL I N E _I N _L /J D 1M I C 2NL I N E _I N _R /J D 2L R C KB C L KADCDATDACDAT MCLK DGND DCVDD DBVDD GPIO/IRQ/PLL_OUT SCLKS D AC d e p o pA U X I N _LA U X I N _RA U X O U T _L /M O N O _O U TA U X O U T _R /M O N O _O U T _NS P K _O U TS P K G N DSPKVDD SPK_OUT_NVREF AGND HP_OUT_R HP_OUT_LAVDD MICBIASN C /Figure 3. Pin Assignments5.1. Green Package and Version IdentificationGreen package is indicated by a ‘G’ in the location marked ‘T’ in Figure 3. The version number is shownin the location marked ‘V’.6.1.Digital I/O PinsTable 1. Digital I/O PinsName Type Pin Description Characteristic DefinitionLRCK IO7DigitalAudioSynchronousSignal Master:V OL =0.1*DVDD, V OH =0.9*DVDDSlave: Schmitt triggerBCLK IO8DigitalAudioSerialClock Master:V OL =0.1*DVDD, V OH =0.9*DVDDSlave: Schmitt triggerADCDAT O 9 SerialADCDataOutput V OL =0.1*DVDD, V OH =0.9*DVDD DACDAT I 10 Serial DAC Data Input Schmitt triggerMCLK I 11 Master Clock Input Schmitt triggerGPIO/ IRQ/PLL_OUT IO/O/O15 General Purpose Input And Output/Interrupt Output/PLL OutputGPIO: Input/OutputIRQOUT: OutputPLL_OUT: OutputSCLK I16I2C Clock Schmitt triggerSDA IO17I2C Data Schmitt triggerTotal: 8 Pins6.2.Analog I/O PinsTable 2. Analog I/O PinsName Type Pin Description Characteristic Definition MIC1P I 1 First Mic Positive Input Analog Input (1Vrms) MIC1N I 2 First Mic Negative Input Analog Input (1Vrms) LINE_IN_L/JD1 I 3 Line Input Left Channel/Jack DetectInput_1Analog Input (1Vrms) MIC2P I 4 Second Mic Positive Input Analog Input (1Vrms) MIC2N I 5 Second Mic Negative Input Analog Input (1Vrms) LINE_IN_R/JD2 I 6 Line Input Right Channel/Jack DetectInput_2Analog Input (1Vrms) AUXIN_L I 19 Auxiliary Input Left Channel Analog Input (1Vrms) AUXIN_R I 20 Auxiliary Input Right Channel Analog Input (1Vrms)AUXOUT_L/ MONO_OUT O 21 Positive Mono Output/AuxiliaryOutput Left ChannelAnalog Output (1Vrms)AUXOUT_R/ MONO_OUT_N O 22 Negative Mono Output/AuxiliaryOutput Right ChannelAnalog Output (1Vrms)SPK_OUT O 23 Speaker Output Analog Output (1.5Vrms, SPKVDD=5V) SPK_OUT_N O 25 Negative Speaker Output Analog Output (1.5Vrms, SPKVDD=5V) HP_OUT_R O 29 Headphone Output Right Channel Analog Output (1Vrms)HP_OUT_L O 30 Headphone Output Left Channel Analog Output (1Vrms)Total: 14 PinsI S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 6Track ID: JATR-1076-21 Rev. 1.0I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 7Track ID: JATR-1076-21 Rev. 1.06.3. Filter/ReferenceTable 3. Filter/ReferenceName Type Pin Description Characteristic Definition NC/Cdepop IO 18 NC/De-Pop Capacitor 1µf capacitor to analog ground VREF O 27 Internal Reference V oltage 1µf capacitor to analog ground MICBIAS O 32 MIC BIAS V oltage Output Programmable Analog DC output with 3mA drive Total: 3 Pins6.4. Power/GroundTable 4. Power/Ground Name Type Pin Description Characteristic Definition DGND P 12 Digital GND - DCVDD P 13 Digital VDD 1.71V~3.6V (Core) DBVDD P 14 Digital VDD 1.71V~3.6V (IO Buffer) SPKGND P 24 Analog GND for Speaker Amps - SPKVDD P 26 Analog VDD for Speaker Amps 2.3V~5V AGND P 28 Analog GND - A VDD P 31 Analog VDD 2.3V~3.6V Total: 7 Pins7.Functional Description7.1.PowerThe ALC5621 has many power blocks. SPKVDD operates between 2.3V and 3.0V for weak Class AB amplifiers, and between 3.0V and 5V for strong Class AB amplifiers. The full range is available for ClassD amplifiers.AVDD operates between 2.3V and 3.6V. DBVDD and DCVDD operate between 1.71V and 3.6V. TheALC5621 must handle ratio control between the different power blocks. The power supplier limit conditions are DBVDD ≥ DCVDD, and SPKVDD ≥ AVDD ≥ DCVDD.7.2.ResetThere are two types of reset operation: Power-On Reset (POR) and Register reset.Table 5. Reset OperationReset Type Trigger Condition CODEC ResponsePOR Monitor digital power supply voltage reach V POR Reset all hardware logic and all registers to defaultvalues.Register Reset Write Reg-00h Reset all registers to default values except PLLrelated register7.2.1.Power-On Reset (POR)When powered on, DCVDD passes through the V POR band of ALC5621 (V PORH ~V PORL). A Power-On Reset (POR) will generate an internal reset signal (POR reset ‘LOW’) to reset the whole chip.Table 6. Power-On Reset VoltageSymbol Min Typical Max UnitV POR_ON 1.0 - 1.6 V V POR_OFF- 1.3 - V Note: V POR_OFF must be below V POR_ON.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 8Track ID: JATR-1076-21 Rev. 1.0I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 9Track ID: JATR-1076-21 Rev. 1.07.3. ClockingThe Audio SYSCLK can be selected from MCLK or PLL. The clock source of PLL can be selected from MCLK or BCLK. The ALC5621 only supports 256Fs or 384Fs as Audio SYSCLK (used as Stereo I 2Sclock).Figure 4. Audio SYSCLK7.3.1. Phase-Locked LoopA Phase-Locked Loop (PLL) is used to provide a flexible input clock from 2.048MHz to 40MHz. Typicalchoices are 2.048MHz, 4.096MHz, and 13MHz. The source of the PLL can be set to MCLK or BCLK by setting pll_sour_sel (Reg42[14]).The source clock of MCLK must be able to drive I 2C, and F/W can setup PLL to output the desired frequency as the SYSCLK.The PLL transmit formula is: F OUT = (MCLK * (N+2)) / ((M+2) * (K+2)) {Typical K=2}Table 7. Clock Setting Table for 48K (Unit: MHz)MCLK N M F VCO K F OUT13 66 7 98.222 2 24.555 3.6864 78 1 98.304 2 24.576 2.048 94 0 98.304 2 24.576 4.096 70 1 98.304 2 24.576 12 80 8 98.4 2 24.6 15.36 81 11 98.068 2 24.517 16 78 11 98.462 2 24.615 19.2 80 14 98.4 2 24.6 19.68 78 14 98.4 2 24.6Table 8. Clock Setting Table for 44.1K (Unit: MHz)MCLK N M F VCO K F OUT13 68 8 91 2 22.753.6864 72 1 90.931 2 22.7332.048 86 0 90.112 2 22.5284.096 64 1 90.112 2 22.52812 66 7 90.667 2 22.66715.36 63 9 90.764 2 22.69116 66 10 90.667 2 22.66719.2 64 12 90.514 2 22.62919.68 67 13 90.528 2 22.632 After a Cold Reset, PLL related Registers are reset to default values, however, they are not reset to default values after a soft-reset (write Reg00).7.3.2.I2C and Stereo I2SThe ALC5621 supports the I2S digital interface for Stereo Audio. The stereo audio digital interface is used to input data to the stereo DAC or output data from the stereo ADC. The Stereo Audio Digital Interface can be configured as Master mode or Slave mode. For the Stereo I2S Interface, the source system clock is always input from MCLK. Refer to section 12 Appendix A: Stereo I2S Clock Table, page 68 for details.Master ModeIn master mode (stereo_i2s_mode_sel=0), BCLK and LRCK are configured as output. Whensel_sysclk=0, MCLK is used as Stereo SYSCLK. When PLL is enabled and sel_sysclk=1, MCLK is suggested to provide frequencies shown in Table 7 Clock Setting Table for 48K (Unit: MHz) and Table 8 Clock Setting Table for 44.1K (Unit: MHz). PLL can be configured to support 44.1K and 48K base sampling rate.Slave ModeIn slave mode (stereo_i2s_mode_sel=1), BCLK/LRCK is configured as input. MCLK should provide the BCLK synchronized clock externally as the Stereo_SYSCLK.Note: The ALC5621 does not support different sample rates between SDAC and ADC in Stereo_I2S/PCM.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 10Track ID: JATR-1076-21 Rev. 1.0I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 11Track ID: JATR-1076-21 Rev. 1.07.4.Digital Data Interface7.4.1.Stereo I 2S/PCM InterfaceThe stereo I 2S/PCM interface can be configured as Master mode or Slave mode. Four audio data formats are supported: • PCM mode • Left justified mode • Right justified mode • I 2S modeFigure 5. PCM Mono Data Mode A Format (stereo_i2s_bclk_polarity_ctrl=0, pcm_mode_sel=0)Figure 6. PCM Mono Data Mode A Format (stereo_i2s_bclk_polarity_ctrl=1, pcm_mode_sel=0)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 12Track ID: JATR-1076-21 Rev. 1.0Figure 7. PCM Mono Data Mode B Format (stereo_i2s_bclk_polarity_ctrl=0, pcm_mode_sel=1)Figure 8. PCM Stereo Data Mode A Format (stereo_i2s_bclk_polarity_ctrl=0, pcm_mode_sel=0)Figure 9. PCM Stereo Data Mode B Format (stereo_i2s_bclk_polarity_ctrl=0, pcm_mode_sel=1)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier13Track ID: JATR-1076-21 Rev. 1.0Figure 10. I 2S Data Format (stereo_i2s_bclk_polarity_ctrl=0)Figure 11. Left Justified Data Format (stereo_i2s_bclk_polarity_ctrl=0)Figure 12. Right Justified Data Format (stereo_i2s_bclk_polarity_ctrl=0)7.5.Audio Data Path7.5.1.VrefVref is the reference voltage for all analog blocks. An external 1µF Capacitor connected to AGND is required. The default status of Vref is enabled after power on. Driver can set Index-39[11]=0b in order to enable power control bit of Reg-3C[13]:pow_vref.7.5.2.Stereo ADCThe stereo ADC is used for recording stereo sound. The sample rate of the stereo ADC is independent of the stereo DAC sample rate. In order to save power, the left and right ADC can be powered down separately by setting adc_l_vol & adc_r_volThe sample rate of the Stereo ADC is the same as the sample rate of Stereo DAC (described in the following section).7.5.3.Stereo DACThe stereo DAC can be configured to different sample rates by driving 256Fs/384Fs into audio SYSCLK with setting divider properly (Reg36). adda_osr is used to control the over sample rate clock divider of the DA filter to 128Fs or 64Fs.Performance of 128Fs is better than 64Fs but with much higher power consumption. Refer to section 12 Appendix A: Stereo I2S Clock Table, page 68 for detailed settings.dac_l_vol & dac_r_vol can be used to control the DAC output volume.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 14Track ID: JATR-1076-21 Rev. 1.07.6.MixersThe ALC5621 supports four mixers for all audio function requirements:•Headphone mixer for 2 channels•MONO mixer•Speaker mixer•ADC record mixer7.6.1.Headphone MixerThe headphone mixer is used to drive stereo output, including HP_OUT_L/R, SPK_OUT, and MONO_OUT (AUXOUT_L/R). The output of the headphone mixer can be input to the ADC record mixer.The following signals can be mixed into the headphone mixer:•LINE-IN_L/R (Controlled by Reg0A)•PHONEP/N (Controlled by Reg08)•MIC1P/N and MIC2P/N (Controlled by Reg22 & Reg10)•Stereo DAC output (Controlled by Reg0C)•ADC record mixer output (Controlled by Reg12 & Reg14).When the SPK_OUT source is from the HP_mixer, SPK_OUT can be configured to L/R, L+R, and L/LN by setting spk_outn_source. The headphone mixer can be powered down by setting pow_mix_hp_l & pow_mix_hp_r.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 15Track ID: JATR-1076-21 Rev. 1.0。

ZFM32F030系列32位微控制器数据手册V1.02版本记录版本日期更改者描述V1.002021.11.01第一版V1.012022.03.18第二版V1.022022.05.25第三版目录1简介 (1)1.1概述 (1)1.2主要特点 (1)2管脚描述 (3)2.1TSSOP20封装管脚排布图 (3)2.2QFN32封装管脚排布图 (3)2.3管脚定义表 (4)2.4管脚对应外设表 (7)3系统框图 (9)4系统描述 (10)4.1ARM Cortex®-M0内核 (10)4.2内存映射 (11)4.3嵌套向量中断控制器(NVIC) (13)4.4系统复位 (14)4.5时钟控制 (14)4.6I/O复用配置 (15)5外设描述 (16)5.1GPIO(通用输入/输出接口) (16)5.2UART(通用异步收发器) (16)5.3I2C总线 (16)5.4SPI(串行外设接口) (16)5.5TIM(定时/计数器) (17)5.6PWM(脉冲宽度调制)模块 (17)5.7WDT(看门狗定时器) (17)5.8ADC(模拟/数字转换器) (17)5.9存储器 (18)5.10电源管理 (18)5.10.1睡眠模式 (18)5.10.2停止模式 (18)5.11SWD调试口 (19)6电气规范 (20)6.1绝对最大额定值 (20)6.2电特性表 (20)6.2.1MCU参数 (20)6.2.2BOD参数 (21)6.2.3ADC参数 (21)6.2.4Flash参数 (22)6.2.5SPI参数 (22)6.2.6I2C参数 (24)7封装尺寸 (25)7.1TSSOP20封装 (25)7.2QFN32封装 (26)1简介1.1概述ZFM32F030系列是内嵌ARM Cortex®-M0核的32位低成本通用微控制器。

最高频率可达48MHz,片内集成32KB Flash存储器,4KB SRAM存储器。

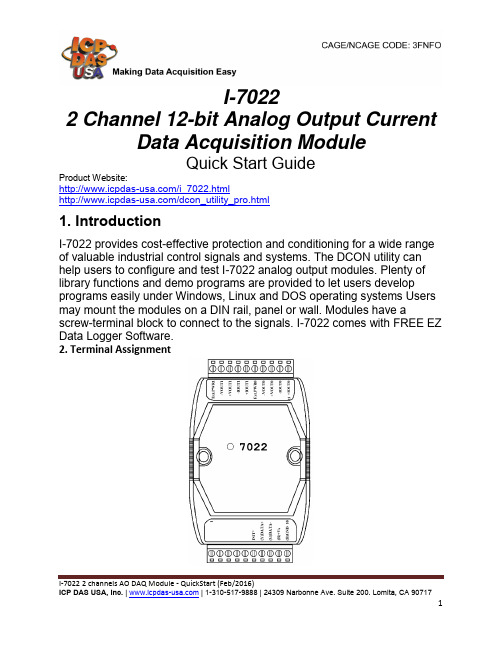

I-70222 Channel 12-bit Analog Output CurrentData Acquisition ModuleQuick Start GuideProduct Website:/i_7022.html/dcon_utility_pro.html1. IntroductionI-7022 provides cost-effective protection and conditioning for a wide range of valuable industrial control signals and systems. The DCON utility can help users to configure and test I-7022 analog output modules. Plenty of library functions and demo programs are provided to let users develop programs easily under Windows, Linux and DOS operating systems Users may mount the modules on a DIN rail, panel or wall. Modules have ascrew-terminal block to connect to the signals. I-7022 comes with FREE EZ Data Logger Software.2. Terminal Assignment3. Block/ Wiring Diagram4. Default SettingsDefault setting for I-7021, I-7021P, I-7022 and I-7024 : Address : 01Analog Output Type : 0 to +10V Baudrate : 9600 bpsChecksum disable, change immediate, engineer unit format I-7021, I-7021P, I-7022 jumper setting : internal power.5. ConfigurationTo install the module, follow the steps below:1. Connect the analog output.2. Connect the module to the RS-485 network using the DATA+ and DATA- terminals. If the host is only equipped with an RS-232 interface, then an RS-232 to RS-485 converter will be required.3. Connect the module to the power supply using the +Vs and GND terminals. Note that the voltage supplied should be in the range of +10 to +30V DC.4. Open DCON utility proclick on COM port(first icon).It can select multi-options such as Baud Rate, Protocol, Checksum, and Format to search module. The default settings for the module can be found in Section 3. Click OK after selecting the COM port setting.5. DCON utility pro will search for the selected COM port according the setting previously set. DCON Utility Pro supports DCON and Modbus protocol for all ICPDAS and the others modules.6. Configuration I/O module setting on PC7. For I-7000 modules, DCON utility pro terminal can send command to the module. See user manual Sections 2 for details command.Configure the module: sending the %AANNTTCCFF command. See user manual Section 2 for details.Read data from the input channels: send either the #AA or #AAN command to the module.8. If user doesn’t know command, user can select Address and ID, it will show some refer commands as below. User can select necessary command to test or debug modules.。

数据手册DatasheetAPM32F072x8xB基于Arm® Cortex®-M0+内核的32位微控制器版本:V1.5产品特性⏹内核32位Arm®w Cortex®-M0+内核最高48MHz工作频率⏹片上存储器Flash:64~128KBSRAM:16KB⏹时钟4~32MHz晶体振荡器带校准的32.768KHzw晶体/陶瓷振荡器内部8MHzwRC振荡器内部48MHz自动校正RC振荡器内部40KHzwRC振荡器PLL支持2~16倍频⏹复位、电源管理上电/掉电复位(POR/PDR)可编程电压调节器数字供电电压:V DD=2.0~3.6V模拟供电电压:V DDA=V DD~3.6V部分I/O供电电压:V DDIO2=1.65~3.6V支持外部电池V BAT为RTC供电:V BAT=1.65~3.6V⏹低功耗模式睡眠、停机、待机模式⏹串行线调试(SWD)⏹I/O最多87个I/Os所有I/O可映射到外部中断向量最多68个容忍5V输入的I/O,19个I/O由V DDIO2供电⏹通信接口2个I2C接口(1Mbit/s),全部支持SMBus/PMBus和唤醒。

4个USART接口,全部支持主同步SPI和调制解调控制,其中2个支持ISO7816、LIN、IrDA接口、自动波特率检测和唤醒。

2个SPI接口(18Mbit/s),全部支持I2S接口复用1个CAN接口1个全速USBD2.0接口,无需外挂晶振,支持BCD和LPMHDMIwCEC⏹模拟外设1个12位ADC,最多支持16个外部通道,转换范围0~3.6V,独立模拟电源输入:2.4~3.6V1个双通道、12位DAC2个可编程模拟比较器最多24个电容传感通道,可用于接近、触键、线性或旋转传感器⏹定时器1个可提供最多7通道PWM输出的16位的高级控制定时器,支持死区生成和刹车输入功能1个32位和5个16位通用定时器,每个定时器最多有4个独立通道用于输入捕获/输出比较。

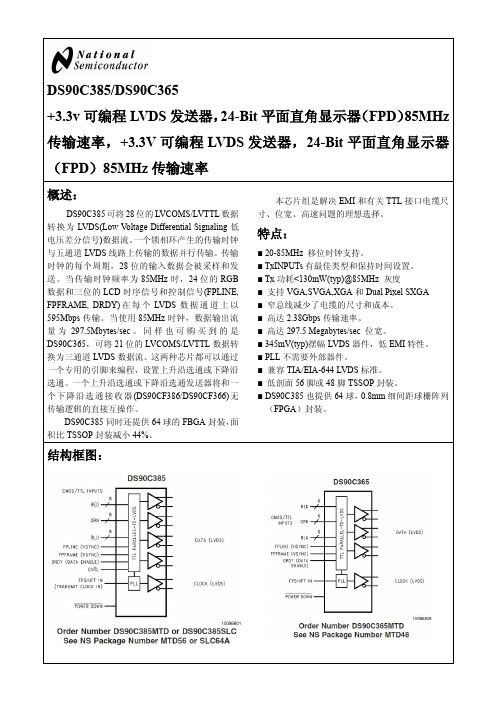

DS90C385/DS90C365+3.3v可编程LVDS发送器,24-Bit平面直角显示器(FPD)85MHz 传输速率,+3.3V可编程LVDS发送器,24-Bit平面直角显示器(FPD)85MHz传输速率概述:DS90C385可将28位的LVCOMS/LVTTL数据转换为LVDS(Low Voltage Differential Signaling低电压差分信号)数据流。

一个锁相环产生的传输时钟与五通道LVDS线路上传输的数据并行传输。

传输时钟的每个周期,28位的输入数据会被采样和发送。

当传输时钟频率为85MHz时,24位的RGB数据和三位的LCD时序信号和控制信号(FPLINE,FPFRAME,DRDY)在每个LVDS数据通道上以595Mbps传输。

当使用85MHz时钟,数据输出流量为297.5Mbytes/sec。

同样也可购买到的是DS90C365,可将21位的LVCOMS/LVTTL数据转换为三通道LVDS数据流。

这两种芯片都可以通过一个专用的引脚来编程,设置上升沿选通或下降沿选通。

一个上升沿选通或下降沿选通发送器将和一个下降沿选通接收器(DS90CF386/DS90CF366)无传输逻辑的直接互操作。

DS90C385同时还提供64球的FBGA封装,面积比TSSOP封装减小44%。

本芯片组是解决EMI和有关TTL接口电缆尺寸、位宽、高速问题的理想选择。

特点:■20-85MHz移位时钟支持。

■TxINPUTs有最佳类型和保持时间设置。

■Tx功耗<130mW(typ)@85MHz灰度■支持VGA,SVGA,XGA和Dual Pixel SXGA■窄总线减少了电缆的尺寸和成本。

■高达2.38Gbps传输速率。

■高达297.5Megabytes/sec位宽。

■345mV(typ)摆幅LVDS器件,低EMI特性。

■PLL不需要外部器件。

■兼容TIA/EIA-644LVDS标准。

■低剖面56脚或48脚TSSOP封装。

第1共13页页ATM8F8040数据手册版本号更新时间更新内容V1.02020-09-05V1.0正式版本发布V1.12020-09-16V1.1版本发布,修正DNL参数V1.22020-12-10统一数据手册和应用手册的关于T2CAP的描述V1.32021-3-1增加16脚SOP16封装信息V1.42021-3-8更新IDD2测试条件第2页1.主要特色CPU 特性通信8位1T 8051内核支持两路UART 支持1/2/4/8系统分频模拟模块支持双DPTR 支持12路12位ADC 支持双线调试支持上电复位ROM支持低压复位16K 字节FLASH(擦写寿命1000次)时钟128字节EEPROM(擦写寿命10000次)内部时钟频率最高到32MHz,1%精度数据保持时间:10年内部时钟32KHz 低频振荡器RAM支持外部1-20MHz 晶振256字节内部IRAM 工作模式512字节外部XRAM 正常模式GPIO待机模式(IDLE)最多支持18个GPIO 停机模式(Stop),最小电流<1uA 支持任意端口变化中断工作条件Timer/PWM工作频率:最大32MHz 16位8051标准定时器T0/T1工作电压: 2.7~5.5V 带捕获和可编程输出的16位定时器T2工作温度:-40℃~85℃7路16位带互补输出PWM 输出模块封装唤醒Timer 20-TSSOP 看门狗定时器20-QFN 4x4SOP16其他CRC16循环冗余检测模块可配置逻辑计算单元(CPL)外部晶振停振检测1.主要特色 (2)2.概述 (4)2.1.说明 (4)2.2.应用方向 (4)3.设计框图 (4)4.引脚分布图 (5)5.封装尺寸图 (7)5.1.20-TSSOP (7)5.2.20-QFN (8)5.3.SOP16 (9)6.电气特性 (10)6.1.极限参数 (10)6.2.DC特性 (10)6.3.ADC特性 (11)6.4.内部高频振荡器特性 (11)6.5.内部低频振荡器特性 (11)6.6.外部振荡器特性 (12)6.7.存储器工作特性 (12)6.8.外部复位及中断管脚特性 (12)7.芯片选型 (13)2.概述2.1.说明ATM8F8040是一款内嵌16K字节FLASH的8位单片机。

32位微控制器KF32LS500数据手册芯片特征●CPU32位高性能KungFu32内核工作频率最高为48MHz,可软件调节;基于16位/32位混合指令的高效指令集;3级流水线;32×32单周期乘法,32÷32硬件除法;支持中断优先级处理,实现自动中断堆栈;13个32位通用寄存器R0~R12;链接寄存器(R13/LR);堆栈指针寄存器(R14/MSP/PSP);程序计数器(R15/PC);24位系统节拍定时器;●存储器最高512KByte FLASH,带ECC校验;最高96KByteRAM,最多32KByte带ECC 校验;1个512Byte双端口RAM,带ECC校验;1个256Byte双端口RAM,带ECC校验;16KByte引导ROM;FLASH可经受100000次写操作;●特殊功能内嵌上电复位电路;低电压检测及低电压复位;可编程电压检测;硬件双看门狗;系统时钟6种时钟源可选;支持两线串行编程/在线调试;●I/O口配置LQFP-100封装有94个通用I/O;LQFP-64封装有60个通用I/O;支持输入输出口设置;支持内置上拉/下拉功能;支持推挽输出和开漏输出模式;支持数字/模拟引脚设置;支持引脚功能重映射;施密特电平输入;●定时器/计数器定时器0:16位低功耗通用定时器,支持CCP0;定时器1/2/3/4为16位通用定时器,其中定时器1/2/3/4支持CCP1/2/3/4;定时器5/6为高级定时器,其中定时器5/6支持ECCP5;定时器14/15:基本定时器;定时器7支持QEI0;●其它外设2个7通道DMA;1个硬件CRC32模块;1个AES128加密模块;2个SPI总线模块(兼容I2S);2个I2C总线模块(兼容SMBUS/PMBUS);最多8个USART模块(兼容7816/LIN/IRDA 功能),其中1个为低功耗USART;1个CAN2.0B模块;1个USB模块;1个CFGL可配置逻辑单元模块;1个独立的RTC(万年历);1个LCD显示模块,最多可以驱动8x48模式;1个触摸模块;1个12位ADC模块,支持最多28个通道;2个CMP比较器模块;●功耗管理7种功耗模式:正常运行模式、休眠模式、低功耗运行模式、低功耗休眠模式、停止模式,待机模式,关断模式●工作条件工作电压: 1.71V~3.6V工作温度范围:A:-40~85℃目录芯片特征 (2)目录 (3)1芯片资源 (6)1.1产品订购信息 (6)1.2KF32LS500X QT(LQFP-64) (7)1.3KF32LS500X QV(LQFP-100) (8)2系统概述 (9)2.1指令集 (9)2.2系统概述 (9)2.3系统框图 (10)2.4KF32LS500外设资源对照表 (11)2.5芯片引脚图 (12)3I/O端口介绍 (13)3.1概述 (13)3.2引脚重映射说明(数字功能) (14)3.3引脚重映射说明(系统以及模拟功能) (17)3.4引脚重映射表-低功耗外设功能重映射 (19)3.5引脚重映射表-外部唤醒引脚、侵入检测和时间戳引脚映射 (19)4资源介绍 (20)4.1DMA (20)4.2节拍定时器(SYSTICK) (20)4.3基本定时/计数器(T14/T15) (20)4.4通用定时/计数器(T0/T1/T2/T3/T4) (21)4.5高级定时/计数器(T5/T6) (21)4.6通用捕捉/比较/PWM模块(CCP0/1/2/3/4) (21)4.7增强型捕捉/比较/PWM模块(ECCP5) (22)4.8正交编码脉冲电路(QEI0) (22)4.9模数转换模块(A/D) (23)4.10模拟比较器模块(CMP) (23)4.11通用全/半双工收发器(USART) (23)4.12串行外设接口(SPI) (24)4.13内部集成电路接口(I2C) (24)4.14液晶显示(LCD) (25)4.15实时时钟(RTC) (25)4.16独立看门狗(IWDT) (25)4.17窗口看门狗(WWDT) (26)4.18电容触摸(CTOUCH) (26)4.19控制器局域网总线(CAN) (27)4.20USB模块(USB) (27)4.21CFGL模块(CFGL) (27)4.22复位(RESET) (28)4.23外设模块时钟使能模块(CLK_EN) (28)4.24备份域(BKP) (29)4.25循环冗余校验单元(CRC) (29)4.26AES加密模块(AES) (29)5电气特性 (30)5.1概述 (30)5.1.1最大值和最小值说明 (30)5.1.2典型值 (30)5.1.3线性曲线 (30)5.2最大范围 (30)5.3运行条件 (31)5.3.1常规运行条件 (31)5.3.2上电/掉电的运行条件 (32)5.3.3复位和电源控制模块特性BOR,PVD (32)5.3.4BAT PVD (33)5.3.5电源电流特性 (33)5.3.6VREG (33)5.4时钟源特性 (34)5.4.1HSE (34)5.4.2LSE (35)5.4.3HSI (36)5.4.4LP4M (36)5.4.5LSI (37)5.4.6PLL (37)5.5IO端口特性 (38)5.5.1静态特性 (38)5.5.2IO输出特性 (38)5.5.3IO AC特性 (38)5.5.4NRST pin特性 (39)5.5.5外部中断特性 (39)5.6外设 (40)5.6.1ADC12BIT特性 (40)5.6.2电压参考buffer特性 (41)5.6.3LCD特性 (42)5.6.4USB全低速收发器模块电气特性 (42)5.6.5比较器CMP特性 (43)5.6.6Touch触摸电气特性 (43)6封装信息 (45)6.1LQFP64封装 (45)6.2LQFP100封装 (45)7ROHS认证 (46)8声明及销售网络 (47)9版本更新记录 (48)KF32LS500数据手册V2.0芯旺微电子-6/48-1芯片资源1.1产品订购信息型号订货号封装GPIOFLASH (KB )RAM (KB)频率(Hz)16位定时器32位定时器E C C PQ E IE X I CS P II 2CU A R T低功耗U A R TC A N低功耗C A NU S B12位A D C12位D A C运放比较器T O U C HL C DR T CC F G LC R CA E S 128工作电压(V )基本通用高级低功耗K F 32L S 500KF32LS500GQT LQFP6460643248M 2421N 1X8ch 1N 22211N Y 1(28)N N 2238X36Y Y Y Y 1.71~3.6V KF32LS500IQT LQFP64601283248M 2421N 1X8ch 1N 22211N Y 1(28)N N 2238X36Y Y Y Y 1.71~3.6V KF32LS500KQT LQFP64602564848M 2421N 1X8ch 1N 22711N Y 1(28)N N 2238X36Y Y Y Y 1.71~3.6V KF32LS500MQT LQFP64605129648M 2421N 1X8ch 1N 22711N Y 1(28)N N 2238X36Y Y Y Y 1.71~3.6V KF32LS500KQV LQFP100942569648M 2421N 1X8ch 1N 22711N Y 1(28)N N 2308X48Y Y Y Y 1.71~3.6V KF32LS500MQV LQFP100945129648M 2421N 1X8ch1N22711NY1(28)NN2308X48YYYY1.71~3.6V1.2KF32LS500xQT(LQFP-64)表1-1KF32LS50064封装资源表型号KF32LS500订货号KF32LS500GQT KF32LS500IQT KF32LS500KQT KF32LS500MQT封装LQFP-64GPIO60FLASH64Kbyte,带ECC校验128Kbyte,带ECC校验256Kbyte,带ECC校验512Kbyte,带ECC校验RAM32Kbyte,带ECC校验48Kbyte,低32K带ECC校验96Kbyte,低32K带ECC校验ROM16Kbyte16位Timer2个高级定时器(T5/T6),支持1个增强型ECCP54个通用定时器(T1/2/3/4),支持4个通用CCP(CCP1/2/3/4)2个基本定时器(T14/T15)1个低功耗通用定时器(T0)QEI112位ADC1*2812位DAC NCMP2PGA NUSART27低功耗UART1I2C2SPI2CAN1低功耗CAN NUSB2.01DMA2x7CFGL YRTC YLCD8x36CT23CRC YAES128Y内部高频振荡器16MHz内部低频振荡器32KHz外部高频时钟4~32MHz外部低频时钟32.768KHz内部参考 1.5/2/2.5/3V器件ID号含出厂版本号等指令系统V0工作电压 1.71V~3.6V工作温度-40~85℃1.3KF32LS500xQV(LQFP-100)表1-2KF32LS500100封装资源表型号KF32LS500订货号KF32LS500KQV KF32LS500MQV封装LQFP-100GPIO94FLASH256Kbyte,带ECC校验512Kbyte,带ECC校验RAM96Kbyte,低32K带ECC校验ROM16Kbyte16位Timer2个高级定时器(T5/T6),支持1个增强型ECCP54个通用定时器(T1/2/3/4),支持4个通用CCP(CCP1/2/3/4)2个基本定时器(T14/T15)1个低功耗通用定时器(T0)QEI112位ADC1*2812位DAC NCMP2PGA NUSART7低功耗UART1 I2C2SPI2CAN1低功耗CAN NUSB2.01DMA2x7CFGL YRTC YLCD8X48CT32CRC YAES Y内部高频振荡器16MHz内部低频振荡器32KHz外部高频时钟4~32MHz外部低频时钟32.768KHz 内部参考 1.5/2/2.5/3V 器件ID号含出厂版本号等指令系统V0工作电压 1.71V~3.6V 工作温度-40~85℃2系统概述2.1指令集KF32LS500系列单片机拥有基于16位/32位混合指令的高效指令集,拥有多种操作模式。

0 引言目前,大多数汽车油量仪表盘利用模拟电子技术通过机械式指针指示油箱油量,精度低,抗干扰能力差,显示不直观。

数字式油量计采用单片机技术,利用数字标定的方法能对任何形状的油箱进行测量,实时精确地显示汽车油箱的油量,并可实现数据的无线传送。

在系统设计中,由于要适配任意形状的油箱,并设置各种报警参数,需要EEPROM 来存储这些数并能进行查表输出,选用具有高速串行SPI接口的可擦除X25045存储器作为标定存储元件时采用无线收发模块PTR2000,实现了采集数据的远距离传送,可与手持式设备或其他监测中心通信,使用简单方便。

1 系统主要芯片介绍1.1 X25045介绍X25045是具有可编程看门狗EEPROM 的高性能集成芯片,它集成了3个主要功能:看门狗定时器、电压监测和EEPROM。

其EEPROM为512~8Bits,可以进行阵列保护,具有高速串行口SPI,控制器可通过SPI通信口实现对数据的存取。

X25045引脚功能图及功能如图1Cs:芯片选择输入;SO:串行输出;SI:串行输入;SCK:串行时钟输入;:写保护输入;Vss:地;Vcc:电源电压;RESET:复位输出。

X25045操作必须写入相应的指令,其指令集如表1所示。

表1 X25045指令集指令名指令格式操作指令名指令格式操作WREN 000001 1O 允许写操作 WRSR 00000001 写状态寄存器WRD1 000001O0 禁止写操作 READ 0000A801 1 读数据RDSR 00000101 读状态寄存器、ⅣIUTE 0000A8Ol0 写数据X25045的读写有严格的时序要求,具体参照其应用资料。

1.2 无线收发模块PTR2000介绍PTR2000是一种新型的单片无线收发数传MODEM模块,该模块在内部集成了高频接收、PLL合成、FSK调制解调、参量放大、功率放大、频道切换等功能,其工作频率稳定可靠、外围元件少、功耗极低且便于设计生产,可满足无线管制的要求且无需使用许可证,是目前低功率无线数传的理想选择,可广泛应用于车辆监控、遥控、工业数据采集系统、无线遥控系统等设计领域l 2_。

CMS32L051 数据手册CMS32L051数据手册基于ARM® Cortex®-M0+的超低功耗32位微控制器 内置64K 字节Flash,丰富的模拟功能,定时器及各种通讯接口 V1.9.3请注意以下有关CMS 知识产权政策*中微半导体(深圳)股份有限公司(以下简称本公司)已申请了专利,享有绝对的合法权益。

与本公司MCU或其他产品有关的专利权并未被同意授权使用,任何经由不当手段侵害本公司专利权的公司、组织或个人,本公司将采取一切可能的法律行动,遏止侵权者不当的侵权行为,并追讨本公司因侵权行为所受的损失、或侵权者所得的不法利益。

*中微半导体(深圳)股份有限公司的名称和标识都是本公司的注册商标。

*本公司保留对规格书中产品在可靠性、功能和设计方面的改进作进一步说明的权利。

然而本公司对于规格内容的使用不负责任。

文中提到的应用其目的仅仅是用来做说明,本公司不保证和不表示这些应用没有更深入的修改就能适用,也不推荐它的产品使用在会由于故障或其它原因可能会对人身造成危害的地方。

本公司的产品不授权适用于救生、维生器件或系统中作为关键器件。

本公司拥有不事先通知而修改产品的功能⚫超低功耗工作环境:➢电源电压范围:1.8V到5.5V➢温度范围:-40℃到105℃➢低功耗模式:睡眠模式,深度睡眠模式➢运行功耗:70uA/MHz@64MHz➢深度睡眠模式下功耗:80uA➢部分掉电的深度睡眠模式下功耗:4.5uA➢部分掉电深度睡眠+32.768K+RTC:5uA⚫内核:➢ARM®32-bitCortex®-M0+ CPU➢工作频率:32KHz~64MHz⚫存储器:➢64KB Flash存储器,程序与数据存储共享➢ 1.5KB 专用数据Flash存储器➢8KB SRAM存储器,附带奇偶校验⚫电源和复位管理:➢内置上电复位(POR)电路➢内置电压检测(LVD)电路(门限电压可设)⚫时钟管理:➢内置高速发振器,精度(±1%)。

芯海科技产品手册CHIPSEA PRODUCT MANUAL芯海科技成立于2003年9月,是一家集感知、计算、控制、连接于一体的全信号链集成电路设计企业。

专注于高精度ADC、高可靠性MCU、测量算法以及AIoT 一站式解决方案的研发设计。

产品和方案广泛应用于工业测量与工业控制、通信与计算机、锂电管理、消费电子、汽车电子、智慧家居、智能仪表、智慧健康等领域。

公司总部位于深圳,在合肥、西安、上海、成都设立子公司,是国家级高新技术企业,被广东省科技厅认定为“广东省物联网芯片开发与应用工程技术研究中心”,获得国家级专精特新“小巨人”称号。

建有可靠性检测中心、健康测量实验室、感知实验室、MCU实验室。

公司年均研发投入超过20%,研发人员占比近70%,核心成员均有10年以上工作经验。

截止到2022年上半年,芯海科技累计拥有全球专利申请近800件,累计拥有已授权专利近350件(含美国专利),拥有专利数量在科创板芯片设计上市公司中名列前茅。

企业简介ABOUT CHIPSEA1523健康测量信号调理数据转换器模拟前端32位MCU 8位MCU010406091113信号链无线产品低功耗蓝牙开发生态开发生态鸿蒙智联解决方案OKOK智能物联解决方案健身行业SaaS 解决方案2021221719电源管理AIoT产品快 充电池管理MCUC H I P S E A32位MCU系列产品概述芯海科技的CS32系列32位MCU基于Arm®Cortex®-M处理器,内嵌Flash存储器,集成高精度ADC和丰富的模拟外设。

该产品系列品类齐全,同时保持了集成度高和易于开发的特点,提供了丰富的软件和开发工具支持,广泛应用于工业控制、汽车电子、智能家居、消费类电子等领域。

产品特色典型应用高可靠低功耗高精度32KB64KB 128KB 256KB 512KB 1024KB ��TWS电子烟电表电动自行车扫地机器人无人机C H I P S E A 产品选型C H I P S E AC H I P S E A8位MCU系列产品概述芯海科技的8位MCU采用芯海科技自主知识产权的8位RISC内核,并集成12位ADC、内部基准电压、OTP或Flash存储器、PWM等资源,支持C语言开发,具有低功耗、易开发等特点。

FM33LG0低功耗MCU芯片产品说明书2022.03本资料是为了让用户根据用途选择合适的上海复旦微电子集团股份有限公司(以下简称复旦微电子)的产品而提供的参考资料,不转让属于复旦微电子或者第三者所有的知识产权以及其他权利的许可。

在使用本资料所记载的信息最终做出有关信息和产品是否适用的判断前,请您务必将所有信息作为一个整体系统来进行评价。

采购方对于选择与使用本文描述的复旦微电子的产品和服务全权负责,复旦微电子不承担采购方选择与使用本文描述的产品和服务的责任。

除非以书面形式明确地认可,复旦微电子的产品不推荐、不授权、不担保用于包括军事、航空、航天、救生及生命维持系统在内的,由于失效或故障可能导致人身伤亡、严重的财产或环境损失的产品或系统中。

未经复旦微电子的许可,不得翻印或者复制全部或部分本资料的内容。

今后日常的产品更新会在适当的时候发布,恕不另行通知。

在购买本资料所记载的产品时,请预先向复旦微电子在当地的销售办事处确认最新信息,并请您通过各种方式关注复旦微电子公布的信息,包括复旦微电子的网站(/)。

如果您需要了解有关本资料所记载的信息或产品的详情,请与上海复旦微电子集团股份有限公司在当地的销售办事处联系。

商标上海复旦微电子集团股份有限公司的公司名称、徽标以及“复旦”徽标均为上海复旦微电子集团股份有限公司及其分公司在中国的商标或注册商标。

上海复旦微电子集团股份有限公司在中国发布,版权所有。

章节列表章节列表 (3)表目录 (23)图目录 (26)1产品综述 (33)1.1概述 (33)1.2芯片结构框图 (36)1.3产品型号列表 (37)1.4产品特性对照表 (38)2引脚和封装 (39)2.1封装和引脚排列 (39)2.1.1LQFP80封装图(FM33LG0x8) (39)2.1.2LQFP64封装图(FM33LG0x6) (40)2.1.3LQFP48封装图(FM33LG0x5) (41)2.1.4QFN32封装图(FM33LG0x3) (42)2.1.5引脚功能定义(FM33LG0xx) (43)2.1.6封装尺寸图 (50)2.2焊接安装说明 (56)2.3MSL等级 (57)2.4热阻特性 (58)3电参数 (59)3.1参数说明 (59)3.2参数测试条件 (59)3.2.1供电方案 (59)3.3极限参数 (61)3.4性能参数 (62)3.4.1典型工作条件 (62)3.4.2功耗参数 (62)3.4.3复位和电源监控 (64)3.4.4高精度基准源 (65)3.4.5低功耗模式唤醒时间 (67)3.4.6外部时钟源特性 (68)3.4.7内部时钟源特性 (70)3.4.8PLL特性 (71)3.4.9ADC特性 (72)3.4.10DAC特性 (78)3.4.11温度传感器 (81)3.4.12运算放大器特性 (83)3.4.13模拟比较器特性 (85)3.4.14Flash存储器特性 (86)3.4.15GPIO特性 (87)3.4.16LCD特性 (89)3.4.17VBAT测量特性 (90)4总线与存储 (91)4.1系统总线 (91)4.2存储空间分配 (92)4.2.1概述 (92)4.2.2外设模块寄存器地址分配 (95)4.3RAM (97)4.3.1概述 (97)4.4F LASH (98)4.4.1概述 (98)4.4.2特殊信息扇区说明 (98)4.4.3指令Prefetch (103)4.4.4Flash编程 (103)4.4.5Data Flash (108)4.4.6Flash的内容保护 (109)4.5寄存器 (112)4.5.1Flash读取控制寄存器(FLS_RDCR) (112)4.5.2预取指控制寄存器(FLS_PFCR) (113)4.5.3用户配置字寄存器(FLS_OPTBR) (113)4.5.4ACLOCK寄存器1(FLS_ACLOCK1) (114)4.5.5ACLOCK寄存器2(FLS_ACLOCK2) (115)4.5.6Flash擦写控制寄存器(FLS_EPCR) (115)4.5.7Flash Key输入寄存器(FLS_KEY) (116)4.5.8Flash中断使能寄存器(FLS_IER) (116)4.5.9Flash标志寄存器(FLS_ISR) (117)5电源管理单元(PMU) (119)5.1芯片工作电源 (119)5.1.1电源域划分 (119)5.1.2电源结构图 (120)5.1.3ADC和基准电压的独立供电 (120)5.1.4片内快速基准源(AVREF) (121)5.1.5片内高精度基准源(VREF1p2) (121)5.1.6VREFP产生(VREFP_VREG) (121)5.2功耗模式 (122)5.2.1概述 (122)5.2.2功耗模式与系统频率 (123)5.2.3Active模式 (124)5.2.4LP Active模式 (124)5.2.5LP Run模式 (125)5.2.6SLEEP模式 (125)5.2.7DEEPSLEEP模式 (126)5.2.8VBAT模式 (127)5.3唤醒源 (128)5.3.1VREF1p2延迟唤醒功能 (129)5.4休眠唤醒后的时钟控制 (130)5.5寄存器 (131)5.5.1低功耗控制寄存器(PMU_CR) (131)5.5.2唤醒时间控制寄存器(PMU_WKTR) (132)5.5.3唤醒源标志查询寄存器(PMU_WKFR) (133)5.5.4PMU中断使能寄存器(PMU_IER) (134)5.5.5PMU中断标志寄存器(PMU_ISR) (135)5.5.6ULPBG调校寄存器(PMU_ULPB_TR) (135)5.5.7VREFP控制寄存器(PMU_VREFP_CR) (136)5.5.8VREFP配置寄存器(PMU_VREFP_CFGR) (136)5.5.9VREFP状态标志寄存器(PMU_VREFP_ISR) (137)5.5.10VREFP调校寄存器(PMU_VREFP_TR) (138)6.1概述 (139)6.2基准电压的应用 (139)6.3温度传感器 (139)6.4输出缓冲器 (140)6.5芯片休眠 (140)6.6寄存器 (141)6.6.1VREF1p2控制寄存器(VREF_CR) (141)6.6.2VREF1p2配置寄存器(VREF_CFGR) (141)6.6.3VREF1p2标志寄存器(VREF_ISR) (142)6.6.4VREF1p2中断使能寄存器(VREF_IER) (143)6.6.5模拟BUFFER控制寄存器(VREF_BUFCR) (143)7VREFP基准电压(VREFP_VREG) (145)7.1概述 (145)7.2功能描述 (145)7.2.1概述 (145)7.2.2时钟和复位 (150)7.2.3参考电压 (150)7.2.4输出电压 (150)7.2.5工作模式 (151)7.2.6中断和标志 (152)7.3寄存器 (153)8备份电源域(VAO DOMAIN) (154)8.1概述 (154)8.2结构框图 (155)8.3电源切换 (155)8.4复位 (155)8.5低频晶体振荡电路(XTLF) (156)8.5.1概述 (156)8.5.2工作方式 (156)8.5.3停振检测 (156)8.6实时时钟(RTCB) (157)8.7IO (157)8.7.1使用PH15输入实现tamper检测 (157)8.8寄存器 (159)8.8.1VAO复位控制寄存器(VAO_RSTCR) (159)8.8.2XTLF控制寄存器(VAO_XTLFCR) (160)8.8.3XTLF振荡强度寄存器(VAO_XTLFPR) (160)8.8.4停振检测中断使能寄存器(VAO_FDIER) (161)8.8.5停振检测中断标志寄存器(VAO_FDISR) (162)8.8.6VAO IO输入使能寄存器(VAO_INEN) (162)8.8.7VAO IO上拉使能寄存器(VAO_PUEN) (163)8.8.8VAO IO开漏使能寄存器(VAO_ODEN) (163)8.8.9VAO IO功能选择寄存器(VAO_FCR) (164)8.8.10VAO IO输出数据寄存器(VAO_DOR) (164)8.8.11VAO IO输入数据寄存器(VAO_DIR) (165)8.8.12VAO IO输入低阈值配置寄存器(VAO_VILR) (165)9跨电源域接口(CDIF) (167)9.1概述 (167)9.2总线地址 (167)9.4寄存器(CPU DOMAIN) (168)9.4.1接口控制寄存器(CDIF_CR) (168)9.4.2接口预分频寄存器(CDIF_PRSC) (168)10处理器(CPU) (170)10.1概述 (170)10.1.1处理器配置 (170)10.2内核寄存器 (171)10.3异常和中断 (172)10.3.1中断向量表 (172)10.3.2中断优先级 (173)10.3.3错误处理 (173)10.3.4锁定(Lockup) (174)10.4MPU (174)10.4.1MPU寄存器 (175)10.5调试特性 (179)10.5.1调试功能引脚 (179)10.5.2调试状态下的看门狗控制 (179)10.5.3DEBUG的复位 (179)11复位管理单元(RMU) (180)11.1概述 (180)11.2模块框图 (181)11.3VDD上下电复位 (182)11.4软件复位 (183)11.5NRST引脚复位 (183)11.6寄存器 (184)11.6.1PDR配置寄存器(RMU_PDRCR) (184)11.6.2BOR配置寄存器(RMU_BORCR) (185)11.6.3复位配置寄存器(RMU_LKPCR) (185)11.6.4软件复位寄存器(RMU_SOFTRST) (186)11.6.5复位标志寄存器(RMU_RSTFR) (186)11.6.6外设复位使能寄存器(RMU_PRSTEN) (187)11.6.7AHB外设复位寄存器(RMU_AHBRSTCR) (187)11.6.8APB1外设复位寄存器(RMU_APBRSTCR1) (188)11.6.9APB2外设复位寄存器(RMU_APBRSTCR2) (190)12独立看门狗(IWDT) (192)12.1概述 (192)12.2结构框图 (192)12.3IWDT功能描述 (192)12.4IWDT窗口功能 (193)12.5IWDT冻结 (194)12.6寄存器 (195)12.6.1IWDT清除寄存器(IWDT_SERV) (195)12.6.2IWDT配置寄存器(IWDT_CR) (195)12.6.3IWDT计数值寄存器(IWDT_CNT) (196)12.6.4IWDT窗口寄存器(IWDT_WIN) (197)12.6.5IWDT中断使能寄存器(IWDT_IER) (197)12.6.6IWDT中断标志寄存器(IWDT_ISR) (197)13窗口看门狗(WWDT) (199)13.1功能描述 (199)13.3WWDT工作方式 (200)13.4寄存器 (202)13.4.1WWDT控制寄存器(WWDT_CR) (202)13.4.2WWDT配置寄存器(WWDT_CFGR) (202)13.4.3WWDT计数寄存器(WWDT_CNT) (203)13.4.4WWDT中断使能寄存器(WWDT_IER) (203)13.4.5WWDT中断标志寄存器(WWDT_ISR) (204)13.4.6WWDT预分频寄存器(WWDT_PSC) (204)14时钟管理单元(CMU) (206)14.1概述 (206)14.2时钟架构 (207)14.2.1时钟树 (207)14.2.2SYSCLK切换说明 (208)14.2.3时钟安全性 (208)14.2.4主要时钟说明 (208)14.2.5外设模块的总线时钟和工作时钟 (209)14.2.6休眠模式下的外设时钟 (210)14.2.7LSCLK切换逻辑 (211)14.3高频RC振荡器(RCHF) (212)14.3.1概述 (212)14.3.2软件使用指南 (212)14.4低频RC振荡器(RCLF) (213)14.4.1概述 (213)14.5低功耗RC振荡器(RCLP) (214)14.5.1概述 (214)14.5.2软件使用指南 (214)14.6高频晶体振荡电路(XTHF) (215)14.6.1概述 (215)14.6.2工作方式 (215)14.6.3停振检测(HFDET) (215)14.7锁相环(PLL) (216)14.7.1概述 (216)14.7.2软件应用指南 (216)14.8时钟校准 (217)14.9低功耗模式下的时钟源 (218)14.10休眠唤醒的时钟处理 (218)14.11寄存器 (219)14.11.1系统时钟配置寄存器(CMU_SYSCLKCR) (220)14.11.2RCHF时钟控制寄存器(CMU_RCHCR) (221)14.11.3RCHF调校寄存器(CMU_RCHFTR) (222)14.11.4PLL控制寄存器(CMU_PLLCR) (222)14.11.5RCLP控制寄存器(CMU_RCLPCR) (223)14.11.6RCLP调校寄存器(CMU_RCLPTR) (224)14.11.7LSCLK选择寄存器(CMU_LSCLKSEL) (224)14.11.8XTHF控制寄存器(CMU_XTHFCR) (225)14.11.9RCLF控制寄存器(CMU_RCLFCR) (225)14.11.10RCLF调校寄存器(CMU_RCLFTR) (226)14.11.11CMU中断使能寄存器(CMU_IER) (226)14.11.12CMU中断标志寄存器(CMU_ISR) (227)14.11.13外设总线时钟控制寄存器1(CMU_PCLKCR1) (228)14.11.14外设总线时钟控制寄存器2(CMU_PCLKCR2) (228)14.11.15外设总线时钟控制寄存器3(CMU_PCLKCR3) (229)14.11.16外设总线时钟控制寄存器4(CMU_PCLKCR4) (230)14.11.17外设工作时钟配置寄存器1(CMU_OPCCR1) (231)14.11.18外设工作时钟配置寄存器2(CMU_OPCCR2) (232)14.11.19外设工作时钟配置寄存器3(CMU_OPCCR3) (233)14.11.20AHB Master控制寄存器(CMU_AHBMCR) (234)14.11.21时钟校准控制寄存器(CMU_CCCR) (235)14.11.22时钟校准配置寄存器(CMU_CCFR) (235)14.11.23时钟校准计数值寄存器(CMU_CCNR) (236)14.11.24时钟校准中断标志寄存器(CMU_CCISR) (237)15电源电压监测(SVD) (238)15.1概述 (238)15.2结构框图 (238)15.3引脚定义 (239)15.4功能描述 (239)15.5间歇使能模式 (241)15.6外部电源检测 (241)15.7电源检测阈值 (242)15.8寄存器 (246)15.8.1SVD配置寄存器(SVD_CFGR) (246)15.8.2SVD控制寄存器(SVD_CR) (247)15.8.3SVD中断使能寄存器(SVD_IER) (247)15.8.4SVD状态和标志寄存器(SVD_ISR) (248)15.8.5SVD参考电压选择寄存器(SVD_VSR) (248)16AES硬件运算单元(AES) (250)16.1功能描述 (250)16.2工作模式 (250)16.3AES数据流处理模式 (251)16.3.1ECB模式 (251)16.3.2CBC模式 (252)16.3.3暂停模式 (254)16.3.4CTR模式 (255)16.3.5CTR模式下的暂停模式 (256)16.3.6GCM模式 (256)16.3.7MultH模块 (259)16.3.8推荐的GCM流程 (260)16.4数据类型 (261)16.5工作流程 (262)16.5.1模式1:加密 (262)16.5.2模式2:密钥扩展 (263)16.5.3模式3:解密 (264)16.5.4模式4:密钥扩展+解密 (264)16.5.5使用MultH模块 (265)16.6DMA接口 (266)16.6.1MultH模块与DMA间接口 (267)16.7错误标志 (267)16.8寄存器 (268)16.8.1AES控制寄存器(AES_CR) (268)16.8.2AES中断使能寄存器(AES_IER) (270)16.8.3AES中断标志寄存器(AES_ISR) (271)16.8.4AES数据输入寄存器(AES_DIR) (271)16.8.6AES秘钥寄存器(AES_KEYx) (272)16.8.7AES初始向量寄存器(AES_IVRx) (273)16.8.8AES MultH参数寄存器(AES_Hx) (273)17随机数发生器(TRNG) (274)17.1概述 (274)17.2功能描述 (275)17.2.1随机数产生 (275)17.2.2工作时钟 (275)17.2.3随机数读取 (276)17.2.4CRC运算 (276)17.3寄存器 (277)17.3.1随机数控制寄存器(RNG_CR) (277)17.3.2随机数/CRC结果输出寄存器(RNG_DOR) (277)17.3.3RNG标志寄存器(RNG_SR) (278)17.3.4CRC控制寄存器(RNG_CRCCR) (278)17.3.5CRC输入数据寄存器(RNG_CRCDIR) (279)17.3.6CRC标志寄存器(RNG_CRCSR) (279)18运算放大器(OPA1) (281)18.1概述 (281)18.2结构框图 (282)18.3引脚定义 (283)18.4功能描述 (283)18.4.1时钟和复位 (283)18.4.2Standalone模式(non-inverting amplifier) (284)18.4.3Standalone模式(inverting amplifier) (285)18.4.4Buffer模式 (285)18.4.5同相PGA模式 (286)18.4.6反相PGA模式 (288)18.4.7Offset校准 (290)18.4.8低功耗模式 (291)18.4.9休眠模式下的OPA (292)18.5寄存器 (293)18.5.1OPA1控制寄存器(OPA1_CR) (293)18.5.2OPA1校准寄存器(OPA1_CALR) (294)18.5.3OPA1校准输出寄存器(OPA1_COR) (295)19模拟比较器(COMPARATOR) (297)19.1概述 (297)19.2结构框图 (298)19.3功能描述 (299)19.3.1基本功能 (299)19.3.2内部比较基准选择和产生 (299)19.3.3时钟和复位 (300)19.3.4引脚和内部信号连接 (300)19.3.5窗口功能 (301)19.3.6功耗和速度模式 (302)19.3.1比较器中断 (303)19.3.2比较器输出和触发输出 (303)19.3.3输出数字滤波 (305)19.4寄存器 (306)控制寄存器()19.4.3COMP3控制寄存器(COMP3_CR) (309)19.4.4COMP中断配置寄存器(COMP_ICR) (310)19.4.5COMP中断标志寄存器(COMP_IF) (311)19.4.6COMP缓冲器控制寄存器(COMP_BUFCR) (311)20除法/开方运算加速器(DIVAS) (313)20.1概述 (313)20.2时钟和复位 (313)20.3硬件除法工作流程 (313)20.4硬件开方工作流程 (314)20.5寄存器 (315)20.5.1操作数寄存器 (315)20.5.2除数寄存器 (315)20.5.3商寄存器 (316)20.5.4余数寄存器 (316)20.5.5根寄存器 (317)20.5.6状态标志寄存器 (317)20.5.7控制寄存器 (318)21双线串行总线(I2C) (319)21.1概述 (319)21.2结构框图 (319)21.3引脚定义和上拉电阻范围 (320)21.4时钟和复位 (324)21.5接口时序 (325)21.5.1接口时序图 (325)21.5.2接口时序描述 (326)21.6I2C工作模式 (328)21.7I2C从机地址格式 (329)21.8I2C初始化 (330)21.8.1IO配置 (330)21.8.2主机波特率配置 (330)21.8.3从机的输入模拟滤波和输出延迟 (331)21.9I2C主机功能 (332)21.9.17bit寻址 (332)21.9.210bit寻址 (337)21.9.3DMA (340)21.9.4SCL延展(Slave Clock Stretching) (344)21.9.5超时机制 (344)21.9.6可编程时序 (344)21.10I2C从机功能 (346)21.10.1从机寻址 (346)21.10.2从机发送数据 (346)21.10.3从机接收数据 (347)21.10.4从机低功耗接收唤醒 (349)21.10.5DMA (349)21.10.6从机时序 (353)21.11寄存器 (354)21.11.1I2C主机配置寄存器(I2C_MSPCFGR) (354)21.11.2I2C主机控制寄存器(I2C_MSPCR) (355)21.11.3I2C主机中断使能寄存器(I2C_MSPIER) (356)21.11.4I2C主机中断标志寄存器(I2C_MSPISR) (357)21.11.5I2C主机状态寄存器(I2C_MSPSR) (357)21.11.6I2C主机波特率设置寄存器(I2C_MSPBGR) (358)21.11.7I2C主机收发缓冲寄存器(I2C_MSPBUF) (359)21.11.8I2C主机时序控制寄存器(I2C_MSPTCR) (359)21.11.9I2C主机超时寄存器(I2C_MSPTOR) (360)21.11.10I2C从机控制寄存器(I2C_SSPCR) (360)21.11.11I2C从机中断使能寄存器(I2C_SSPIER) (361)21.11.12I2C从机中断标志寄存器(I2C_SSPISR) (362)21.11.13I2C从机状态寄存器(I2C_SSPSR) (363)21.11.14I2C从机收发缓冲寄存器(I2C_SSPBUF) (364)21.11.15I2C从机地址寄存器(I2C_SSPADR) (364)22通用异步收发传输器(UART) (366)22.1概述 (366)22.2结构框图 (367)22.3引脚定义 (368)22.4UART类型区分 (369)22.5UART字符描述 (369)22.6功能描述 (371)22.6.1时钟和复位 (371)22.6.2位接收采样 (371)22.6.3数据发送 (372)22.6.4数据接收 (374)22.6.5低功耗休眠唤醒(UART0/1) (375)22.6.6使用DMA进行UART收发 (375)22.6.7DMA模式下的发送完成中断 (376)22.7波特率发生 (376)22.7.1波特率发生 (376)22.7.1波特率自适应 (377)22.8红外调制 (378)22.9接收超时 (379)22.10发送延迟 (379)22.11寄存器 (380)22.11.1红外调制寄存器(UART_IRCR) (381)22.11.2UARTx控制状态寄存器(UARTx_CSR) (382)22.11.3UARTx中断使能寄存器(UARTx_IER) (383)22.11.4UARTx中断标志寄存器(UARTx_ISR) (384)22.11.5UARTx超时和延迟寄存器(UARTx_TODR) (385)22.11.6UARTx接收缓冲寄存器(UARTx_RXBUF) (385)22.11.7UARTx发送缓冲寄存器(UARTx_TXBUF) (386)22.11.8UATRx波特率产生寄存器(UARTx_BGR) (386)23低功耗UART(LPUART) (388)23.1概述 (388)23.2结构框图 (389)23.3引脚定义 (390)23.4时钟和复位 (390)23.5字符描述 (391)23.6功能描述 (393)23.6.1位接收采样和发送 (393)23.6.2接收流程 (394)23.6.3发送流程 (394)23.6.4使用DMA进行LPUART收发 (394)23.6.5休眠模式下的数据接收唤醒 (395)23.6.6LPRUN模式下的数据DMA收发 (395)23.6.7DMA模式下的发送完成中断 (395)23.7寄存器 (397)23.7.1LPUARTx控制状态寄存器(LPUARTx_CSR) (398)23.7.2LPUARTx中断使能寄存器(LPUARTx _IER) (399)23.7.3LPUARTx中断标志寄存器(LPUARTx _ISR) (400)23.7.4LPUARTx波特率调制寄存器(LPUARTx _BMR) (400)23.7.5LPUARTx接收数据寄存器(LPUARTx _RXBUF) (401)23.7.6LPUARTx发送数据寄存器(LPUARTx _TXBUF) (402)23.7.7LPUARTx数据匹配寄存器(LPUARTx _DMR) (402)24串行外设接口(SPI) (404)24.1概述 (404)24.2结构框图 (404)24.3引脚定义 (406)24.4时钟和复位 (406)24.5接口时序 (406)24.5.1CPHA=0 (406)24.5.2CPHA=1 (407)24.5.14线半双工模式(主机) (407)24.6功能描述 (409)24.6.1I/O配置 (409)24.6.2全双工数据通信 (410)24.6.3TX-ONLY模式 (411)24.6.4RX-ONLY模式 (412)24.6.5主机SSN控制 (412)24.6.6数据冲突 (413)24.6.7使用DMA进行SPI收发 (413)24.7寄存器 (415)24.7.1SPI控制寄存器1(SPIx_CR1) (416)24.7.2SPI控制寄存器2(SPIx_CR2) (417)24.7.3SPI控制寄存器3(SPIx_CR3) (418)24.7.4SPI中断控制寄存器(SPIx_IER) (419)24.7.5SPI中断标志寄存器(SPIx_ISR) (419)24.7.6SPI发送缓存寄存器(SPIx_TXBUF) (420)24.7.7SPI发送缓存寄存器(SPIx_RXBUF) (420)25智能卡接口(ISO7816) (422)25.1概述 (422)25.2结构框图 (422)25.3时钟和复位 (423)25.4接口时序 (423)25.5功能描述 (424)25.5.1数据接收 (424)25.5.2数据发送 (424)25.5.3使用DMA进行7816收发 (426)25.6寄存器 (427)25.6.1U7816控制寄存器(U7816_CR) (427)25.6.2U7816帧格式控制寄存器(U7816_FFR) (428)25.6.3U7816额外保护时间寄存器(U7816_EGTR) (429)25.6.4U7816工作时钟分频寄存器(U7816_PSC) (429)25.6.5U7816波特率寄存器(U7816_BGR) (430)25.6.6U7816数据接收缓冲寄存器(U7816_RXBUF) (430)25.6.7U7816数据发送缓冲寄存器(U7816_TXBUF) (431)25.6.8U7816中断使能寄存器(U7816_IER) (431)25.6.9U7816状态标志寄存器(U7816_ISR) (432)26控制器区域网络(CAN) (434)26.1概述 (434)26.2结构框图 (434)26.3引脚定义 (435)26.4功能描述 (435)26.4.1时钟和复位 (435)26.4.2Bit timing (435)26.4.3Bit stream processor (436)26.4.4控制器工作模式 (436)26.4.5消息帧存储和消息帧结构(Message storage and structure) (437)26.4.6消息滤波器(Acceptance Filter) (439)26.4.7错误管理 (439)26.5编程模型 (443)26.5.1寄存器配置 (443)26.5.2消息传输 (443)26.6寄存器 (445)26.6.1CAN控制寄存器(CAN_CR) (446)26.6.2CAN模式选择寄存器(CAN_MSR) (447)26.6.3CAN波特率预分频寄存器(CAN_BRPR) (447)26.6.4CAN位时序寄存器(CAN_BTR) (448)26.6.5CAN错误计数寄存器(CAN_ECR) (448)26.6.6CAN错误状态寄存器(CAN_ESR) (449)26.6.7CAN状态标志寄存器(CAN_SR) (450)26.6.8CAN中断标志寄存器(CAN_ISR) (451)26.6.9CAN中断使能寄存器(CAN_IER) (452)26.6.10CAN中断清除寄存器(CAN_ICR) (453)26.6.11CAN发送FIFO ID寄存器(CAN_TXFIDR) (453)26.6.12CAN发送FIFO DLC寄存器(CAN_TXFDLCR) (454)26.6.13CAN发送FIFO DataWord1寄存器(CAN_TXFDW1R) (454)26.6.14CAN发送FIFO DataWord2寄存器(CAN_TXFDW2R) (455)26.6.15CAN高优先级发送缓冲ID寄存器(CAN_HPBIDR) (455)26.6.16CAN高优先级发送缓冲DLC寄存器(CAN_HPBDLCR) (456)26.6.17CAN高优先级发送缓冲DataWord1寄存器(CAN_HPBDW1R) (456)26.6.18CAN高优先级发送缓冲DataWord2寄存器(CAN_HPBDW2R) (457)26.6.19CAN接收FIFO ID寄存器(CAN_RXF_IDR) (457)26.6.20CAN接收FIFO DLC寄存器(CAN_RXFDLCR) (458)26.6.21CAN接收FIFO DataWord1寄存器(CAN_RXFDW1R) (458)26.6.22CAN接收FIFO DataWord2寄存器(CAN_RXFDW2R) (459)26.6.23CAN接收滤波寄存器(CAN_AFR) (459)26.6.24CAN接收滤波掩码寄存器x(CAN_AFMRx) (460)26.6.25CAN接收滤波ID寄存器x(CAN_AFIRx) (461)27直接存储访问控制器(DMA) (462)27.1概述 (462)27.2工作原理 (463)27.3结构框图 (464)27.4工作流程 (464)27.5访问带宽 (466)27.6通道控制 (467)27.6.1DMA请求映射 (467)27.6.2通道优先级 (468)27.6.3传输方向定义 (468)27.6.4循环模式 (468)27.7寄存器 (469)27.7.1DMA全局控制寄存器(DMA_GCR) (469)27.7.2通道x控制寄存器(DMA_CHxCR) (470)27.7.3通道x存储器指针寄存器(DMA_CHxMAD) (471)27.7.4通道7控制寄存器(DMA_CH7CR) (472)27.7.5通道7 Flash指针寄存器(DMA_CH7FLSAD) (473)27.7.6通道7 RAM指针寄存器(DMA_CH7RAMAD) (473)27.7.7DMA状态标志寄存器(DMA_ISR) (474)28循环冗余校验(CRC) (475)28.1概述 (475)28.2软件配置过程 (476)28.3G OLDEN 数据 (477)28.4DMA接口 (477)28.5F LASH数据完整性校验 (478)28.6寄存器 (479)28.6.1CRC数据寄存器(CRC_DR) (479)28.6.2CRC控制状态寄存器(CRC_CR) (479)28.6.3CRC LFSR寄存器(CRC_LFSR) (481)28.6.4CRC输出异或寄存器(CRC_XOR) (481)28.6.5CRC多项式寄存器(CRC_POLY) (481)29高级定时器(ATIM) (483)29.1概述 (483)29.2主要特性 (483)29.3结构框图 (484)29.4功能描述 (485)29.4.1定时单元 (485)29.4.2定时器工作模式 (487)29.4.3重复计数器 (494)29.4.4Preload寄存器 (495)29.4.5计数器工作时钟 (496)29.4.6内部触发信号(ITRx) (501)29.4.7捕捉/比较通道 (502)29.4.8输入捕捉模式 (504)29.4.9软件Force输出 (506)29.4.10输出比较模式 (507)29.4.11PWM输出 (508)29.4.12互补输出和死区插入 (510)29.4.13刹车功能 (511)29.4.14互补输出通道信号状态逻辑表 (513)29.4.156-step PWM输出 (514)29.4.16单脉冲输出 (515)29.4.17外部事件清除OCxREF (517)29.4.18编码器接口模式(encoder interface) (518)29.4.19TIM从机模式 (520)29.4.20DMA访问 (523)29.4.21DMA Burst (524)29.4.22输入异或功能 (525)29.4.23霍尔传感器接口 (525)29.4.24Debug模式 (526)29.5.1ATIM控制寄存器1(ATIM_CR1) (527)29.5.2ATIM控制寄存器2(ATIM_CR2) (529)29.5.3ATIM从机模式控制寄存器(ATIM_SMCR) (530)29.5.4ATIM DMA和中断使能寄存器(ATIM_DIER) (532)29.5.5ATIM状态寄存器(ATIM_ISR) (533)29.5.6ATIM事件产生寄存器(ATIM_EGR) (535)29.5.7ATIM捕捉/比较模式寄存器1(ATIM_CCMR1) (535)29.5.8ATIM捕捉/比较模式寄存器2(ATIM_CCMR2) (538)29.5.9ATIM捕捉/比较使能寄存器(ATIM_CCER) (540)29.5.10ATIM计数器寄存器(ATIM_CNT) (541)29.5.11ATIM预分频寄存器(ATIM_PSC) (541)29.5.12ATIM自动重载寄存器(ATIM_ARR) (542)29.5.13ATIM重复计数寄存器(ATIM_RCR) (542)29.5.14ATIM捕捉/比较寄存器1(ATIM_CCR1) (543)29.5.15ATIM捕捉/比较寄存器2(ATIM_CCR2) (544)29.5.16ATIM捕捉/比较寄存器3(ATIM_CCR3) (544)29.5.17ATIM捕捉/比较寄存器4(ATIM_CCR4) (545)29.5.18ATIM刹车和死区控制寄存器(ATIM_BDTR) (545)29.5.19ATIM DMA控制寄存器(ATIM_DCR) (547)29.5.20ATIM DMA访问寄存器(ATIM_DMAR) (548)29.5.21ATIM刹车输入控制寄存器(ATIM_BKCR) (548)30通用定时器(GPTIM0,1,2) (550)30.1概述 (550)30.2主要特性 (550)30.3结构框图 (551)30.4功能描述 (552)30.4.1定时单元 (552)30.4.2定时器工作模式 (554)30.4.3计数器工作时钟 (561)30.4.4内部触发信号(ITRx)的捕捉 (567)30.4.5捕捉/比较通道 (568)30.4.6输入捕捉模式 (569)30.4.7软件Force输出 (571)30.4.8输出比较模式 (571)30.4.9PWM模式 (572)30.4.10单脉冲输出 (573)30.4.11外部事件清除OCxREF (575)30.4.12编码器接口模式(encoder interface) (575)30.4.13GPTIM从机模式 (576)30.4.14DMA访问 (579)30.4.15DMA Burst (580)30.4.16输入异或功能 (580)30.4.17Debug模式 (580)30.5寄存器 (581)30.5.1GPTIMx控制寄存器1(GPTIMx_CR1) (583)30.5.2GPTIMx控制寄存器2(GPTIMx_CR2) (584)30.5.3GPTIMx从机模式控制寄存器(GPTIMx_SMCR) (585)30.5.4GPTIMx DMA和中断使能寄存器(GPTIMx_DIER) (587)30.5.5GPTIMx状态寄存器(GPTIMx_ISR) (588)30.5.6GPTIMx事件产生寄存器(GPTIMx_EGR) (589)30.5.7GPTIMx捕捉/比较模式寄存器1(GPTIMx_CCMR1) (590)30.5.8GPTIMx捕捉/比较模式寄存器2(GPTIMx_CCMR2) (592)30.5.9GPTIMx捕捉/比较使能寄存器(GPTIMx_CCER) (595)30.5.10GPTIMx计数器寄存器(GPTIMx_CNT) (596)30.5.11GPTIMx预分频寄存器(GPTIMx_PSC) (596)30.5.12GPTIMx自动重载寄存器(GPTIMx_ARR) (597)30.5.13GPTIMx捕捉/比较寄存器1(GPTIMx_CCR1) (597)30.5.14GPTIMx捕捉/比较寄存器2(GPTIMx_CCR2) (598)30.5.15GPTIMx捕捉/比较寄存器3(GPTIMx_CCR3) (598)30.5.16GPTIMx捕捉/比较寄存器4(GPTIMx_CCR4) (599)30.5.17GPTIMx DMA控制寄存器(GPTIMx_DCR) (599)30.5.18GPTIMx DMA访问寄存器(GPTIMx_DMAR) (600)30.5.19GPTIMx ITR选择寄存器(GPTIMx_ITRSEL) (601)3132位基本定时器(BSTIM32) (603)31.1概述 (603)31.2主要特性 (603)31.3结构框图 (603)31.4功能描述 (604)31.4.1定时单元 (604)31.4.2定时器工作模式 (606)31.4.3计数器工作时钟 (608)31.4.1Debug模式 (609)31.5寄存器 (610)31.5.1BSTIM32控制寄存器1(BSTIM32_CR1) (610)31.5.2BSTIM32控制寄存器2(BSTIM32_CR2) (611)31.5.3BSTIM32中断使能寄存器(BSTIM32_IER) (611)31.5.4BSTIM32中断标志寄存器(BSTIM32_ISR) (612)31.5.5BSTIM32事件产生寄存器(BSTIM32_EGR) (613)31.5.6BSTIM32计数器寄存器(BSTIM32_CNT) (613)31.5.7BSTIM32预分频寄存器(BSTIM_PSC) (614)31.5.8BSTIM32自动重载寄存器(BSTIM32_ARR) (614)3216位基本定时器(BSTIM16) (615)32.1概述 (615)32.2主要特性 (615)32.3结构框图 (615)32.4功能描述 (616)32.4.1定时单元 (616)32.4.2定时器工作模式 (618)32.4.3计数器工作时钟 (620)32.4.4Debug模式 (621)32.5寄存器 (622)32.5.1BSTIM16控制寄存器1(BSTIM16_CR1) (622)32.5.2BSTIM16控制寄存器2(BSTIM16_CR2) (623)32.5.3BSTIM16中断使能寄存器(BSTIM16_IER) (624)32.5.4BSTIM16中断标志寄存器(BSTIM16_ISR) (624)32.5.5BSTIM16事件产生寄存器(BSTIM16_EGR) (625)32.5.1BSTIM16计数器寄存器(BSTIM16_CNT) (625)32.5.1BSTIM16预分频寄存器(BSTIM16_PSC) (626)32.5.1BSTIM16自动重载寄存器(BSTIM16_ARR) (626)3332位低功耗定时器(LPTIM32) (628)33.1概述 (628)33.2结构框图 (629)33.5定时器功能 (630)33.5.1普通定时器 (630)33.5.2外部脉冲触发计数 (630)33.5.3外部异步脉冲计数 (631)33.5.4Timeout模式 (631)33.6捕捉比较功能 (632)33.6.132bit PWM (632)33.6.2输入捕捉 (633)33.7触发信号输出 (634)33.8寄存器 (635)33.8.1LPTIM32配置寄存器(LPTIM32_CFGR) (635)33.8.2LPTIM32计数值寄存器(LPTIM32_CNT) (637)33.8.3LPTIM32捕捉比较控制和状态寄存器(LPTIM32_CCSR) (637)33.8.4LPTIM32目标值寄存器(LPTIM32_ARR) (639)33.8.5LPTIM32中断使能寄存器(LPTIM32_IER) (640)33.8.6LPTIM32中断标志寄存器(LPTIM32_ISR) (641)33.8.7LPTIM32控制寄存器(LPTIM32_CR) (642)33.8.8LPTIM32捕捉比较寄存器1(LPTIM32_CCR1) (643)33.8.9LPTIM32捕捉比较寄存器2(LPTIM32_CCR2) (643)33.8.10LPTIM32捕捉比较寄存器3(LPTIM32_CCR3) (644)33.8.11LPTIM32捕捉比较寄存器4(LPTIM32_CCR4) (644)3416位低功耗定时器(LPTIM16) (645)34.1概述 (645)34.2结构框图 (646)34.3时钟和复位 (646)34.4相关引脚 (647)34.5定时器功能 (647)34.5.1普通定时器 (647)34.5.2外部脉冲触发计数 (647)34.5.3外部异步脉冲计数 (648)34.5.4Timeout模式 (648)34.6捕捉比较功能 (649)34.6.116bit PWM (649)34.6.2输入捕捉 (650)34.6.3输入数字滤波 (651)34.7正交编码器 (652)34.8触发信号输出 (653)34.9寄存器 (654)34.9.1LPTIM16配置寄存器(LPTIM16_CFGR) (654)34.9.2LPTIM16计数值寄存器(LPTIM16_CNT) (656)34.9.3LPTIM16捕捉比较控制和状态寄存器(LPTIM16_CCSR) (656)34.9.4LPTIM16目标值寄存器(LPTIM16_ARR) (658)34.9.5LPTIM中断使能寄存器(LPTIM_IER) (659)34.9.6LPTIM16中断标志寄存器(LPTIM16_ISR) (659)34.9.7LPTIM16控制寄存器(LPTIM16_CR) (660)34.9.8LPTIM16捕捉比较寄存器1(LPTIM16_CCR1) (661)34.9.9LPTIM16捕捉比较寄存器2(LPTIM16_CCR2) (661)35实时时钟(RTCA) (663)35.1概述 (663)35.2结构框图 (663)35.3工作原理 (664)35.3.2LTBC数字调校 (665)35.3.3BCD时间 (666)35.3.4RTC使能与停止 (667)35.3.5RTC时间设置 (667)35.3.6RTC时间读取 (667)35.3.7闰年判断 (668)35.4寄存器 (669)35.4.1RTCA写使能寄存器(RTCA_WER) (669)35.4.2RTCA中断使能寄存器(RTCA_IER) (670)35.4.3RTCA中断标志寄存器(RTCA_ISR) (671)35.4.4BCD时间秒寄存器(RTCA_BCDSEC) (672)35.4.5BCD时间分钟寄存器(RTCA_BCDMIN) (673)35.4.6BCD时间小时寄存器(RTCA_BCDHOUR) (673)35.4.7BCD时间天寄存器(RTCA_BCDDAY) (674)35.4.8BCD时间星期寄存器(RTCA_BCDWEEK) (674)35.4.9BCD时间月寄存器(RTCA_BCDMONTH) (675)35.4.10BCD时间年寄存器(RTCA_BCDYEAR) (675)35.4.11闹钟寄存器(RTCA_ALARM) (676)35.4.12RTC时间信号输出寄存器(RTCA_TMSEL) (676)35.4.13LTBC数值调整寄存器(RTCA_ADJUST) (677)35.4.14毫秒计数值寄存器(RTCA_SBSCNT) (678)35.4.15RTCA控制寄存器RTCA_CR (678)36实时时钟(RTCB) (679)36.1概述 (679)36.2结构框图 (679)36.3工作原理 (680)36.3.1工作时钟 (680)36.3.2时基计数器(LTBC) (680)36.3.3LTBC数字调校 (680)36.3.4BCD时间 (682)36.3.5RTC使能与停止 (682)36.3.6RTC时间设置 (683)36.3.7RTC时间读取 (683)36.3.8闰年判断 (684)36.3.9RTC时间戳 (684)36.3.10备份寄存器 (685)36.4寄存器 (686)36.4.1RTCB写使能寄存器(RTCB_WER) (687)36.4.2RTCB中断使能寄存器(RTCB_IER) (687)36.4.3RTCB中断标志寄存器(RTCB_ISR) (688)36.4.4BCD时间秒寄存器(RTCB_BCDSEC) (689)36.4.5BCD时间分钟寄存器(RTCB_BCDMIN) (689)36.4.6BCD时间小时寄存器(RTCB_BCDHOUR) (690)36.4.7BCD时间天寄存器(RTCB_BCDDAY) (690)36.4.8BCD时间星期寄存器(RTCB_BCDWEEK) (691)36.4.9BCD时间月寄存器(RTCB_BCDMONTH) (691)36.4.10BCD时间年寄存器(RTCB_BCDYEAR) (692)36.4.11RTCB时间信号输出寄存器(RTCB_TMSEL) (692)36.4.12RTCB时钟调校寄存器(RTCB_ADJR) (693)36.4.13RTCB控制寄存器(RTCB_CR) (693)36.4.14RTCB时间戳控制寄存器(RTCB_STPCR) (694)36.4.15RTCB时间戳时钟寄存器(RTCB_STPCLKRR) (695)36.4.16RTCB时间戳日历寄存器(RTCB_STPCALRR) (695)36.4.17RTCB备份寄存器组(RTCB_BKRx) (696)37段码液晶驱动(LCD) (697)37.1概述 (697)37.2结构框图 (697)37.3IO配置 (699)37.4功能说明 (699)37.4.1工作时钟和显示帧频率 (699)37.4.2LCD Type A扫描波形 (699)37.4.3LCD Type B扫描波形 (704)37.4.4片内buffer驱动模式 (708)37.4.5片外电容驱动模式 (708)37.4.6显示闪烁功能 (709)37.4.7偏置电压调整 (709)37.5低功耗模式 (710)37.6寄存器 (711)37.6.1显示控制寄存器(LCD_CR) (711)37.6.2显示测试控制寄存器(LCD_TEST) (713)37.6.3显示频率控制寄存器(LCD_FCR) (714)37.6.4闪烁时间寄存器(LCD_FLKT) (715)37.6.5显示中断使能寄存器(LCD_IER) (715)37.6.6显示中断标志寄存器(LCD_ISR) (716)37.6.7显示数据寄存器(LCD_DATAx) (716)37.6.8LCD COM使能控制寄存器(LCD_COMEN) (723)37.6.9LCD SEG使能控制寄存器0(LCD_SEGEN0) (723)37.6.10LCD SEG使能控制寄存器1(LCD_SEGEN1) (724)38模数转换器(ADC) (725)38.1概述 (725)38.2结构框图 (726)38.3输入通道 (727)38.4单端和差分输入 (728)38.5工作时序 (730)38.6功能描述 (732)38.6.1使用VDDA作为基准 (732)38.6.2使用VREFP作为基准 (733)38.6.3温度传感器 (733)38.6.4温度传感器的斜率和标定 (734)38.6.5可编程采样时间 (734)38.6.6输出位宽选择 (736)38.6.7输入缓冲器 (736)38.6.8VBAT和VDD电源电压采样 (737)38.6.9内部信号采样 (737)38.6.10转换模式 (738)38.6.11转换触发 (741)38.6.12过采样和硬件平均 (742)38.6.13ADC工作时钟 (743)38.6.14数据冲突和自动等待 (743)38.6.15DMA (744)38.6.16模拟窗口看门狗(AWD) (750)38.6.17ADC校准 (751)38.8寄存器 (753)38.8.1ADC中断和状态寄存器(ADC_ISR) (753)38.8.2ADC中断使能寄存器(ADC_IER) (754)38.8.3ADC控制寄存器1(ADC_CR1) (755)38.8.4ADC控制寄存器2(ADC_CR2) (755)38.8.5ADC校准控制寄存器(ADC_CALR) (756)38.8.6ADC配置寄存器1(ADC_CFGR1) (757)38.8.7ADC配置寄存器2(ADC_CFGR2) (758)38.8.8ADC采样时间控制寄存器(ADC_SMTR) (760)38.8.9ADC通道控制寄存器(ADC_CHER) (762)38.8.10ADC通道差分控制寄存器(ADC_DCR) (763)38.8.11ADC数据寄存器(ADC_DR) (763)38.8.12AWD阈值寄存器(ADC_HLTR) (764)39数模转换器(DAC) (765)39.1概述 (765)39.2结构框图 (765)39.3引脚定义 (766)39.4DAC输出与引脚和其他模块的互联 (766)39.5功能描述 (767)39.5.1工作时钟与信号时序 (767)39.5.2DAC输出模式 (767)39.5.3DAC触发源选择 (769)39.5.4DAC输出电压 (769)39.5.5DMA (769)39.5.6采样保持 (770)39.5.7DAC输出Buffer (772)39.5.8低功耗模式下的DAC (773)39.6寄存器 (774)39.6.1DAC控制寄存器1(DAC_CR1) (774)39.6.2DAC控制寄存器2(DAC_CR2) (774)39.6.1DAC配置寄存器(DAC_CFGR) (775)39.6.2DAC软件触发寄存器(DAC_SWTRGR) (776)39.6.3DAC数据保持寄存器(DAC_DHR) (776)39.6.4DAC状态标志寄存器(DAC_ISR) (777)39.6.5DAC中断使能寄存器(DAC_IER) (777)39.6.1DAC采样保持时间寄存器(DAC_SHTR) (778)40可编程胶合逻辑(PGL) (780)40.1概述 (780)40.2结构框图 (780)40.3引脚定义 (782)40.4功能描述 (783)40.4.1LUT真值表 (783)40.4.2LUT输入 (784)40.4.3LUT输出 (784)40.4.4滤波和采样 (784)40.4.5中断和触发 (785)40.4.6低功耗模式 (786)40.5寄存器 (787)40.5.1PGL控制寄存器(PGL_CR) (787)40.5.2PGL配置寄存器0(PGL_CFGR0) (788)40.5.3PGL配置寄存器1(PGL_CFGR1) (789)40.5.5PGL配置寄存器3(PGL_CFGR3) (791)40.5.6PGL中断使能寄存器(PGL_IER) (792)40.5.7PGL中断标志寄存器(PGL_ISR) (793)40.5.8LUT0真值表寄存器(PGL_LUT0) (793)40.5.9LUT1真值表寄存器(PGL_LUT1) (794)40.5.10LUT2真值表寄存器(PGL_LUT2) (794)40.5.11LUT3真值表寄存器(PGL_LUT3) (795)41I/O端口(GPIO) (796)41.1概述 (796)41.2引脚类型 (796)41.2.1GPIO,输入输出使能,可控上拉电阻,可控开漏输出 (797)41.2.2GPIO,输入输出使能,2个可控上拉电阻,可控开漏输出(仅PC12-7816数据口) (798)41.3IO端口功能定义 (798)41.3.1GPIO输入 (798)41.3.2GPIO输出 (799)41.3.3数字外设功能 (799)41.3.4模拟功能 (801)41.3.5使用外部晶体引脚 (802)41.4VBAT供电引脚 (802)41.5SWD引脚 (803)41.6WKUP X引脚 (803)41.7外部引脚中断(EXTI) (804)41.7.1功能说明 (804)41.7.2应用指南 (805)41.8快速GPIO输出 (806)41.9寄存器 (807)41.9.1GPIO输入使能寄存器(GPIOx_INEN) (810)41.9.2GPIO上拉使能寄存器(GPIOx_PUEN) (810)41.9.3GPIO开漏使能寄存器(GPIOx_ODEN) (811)41.9.4GPIO功能选择寄存器(GPIOx_FCR) (811)41.9.5GPIO输出数据寄存器(GPIOx_DO) (813)41.9.6GPIO输出数据置位寄存器(GPIOx_DSET) (814)41.9.7GPIO输出数据复位寄存器(GPIOx_DRST) (814)41.9.8GPIO输入数据寄存器(GPIOx_DIN) (815)41.9.9GPIO额外数字功能选择寄存器(GPIOx_DFS) (816)41.9.10GPIO模拟开关使能寄存器(GPIOx_ANEN) (816)41.9.11GPIO输入低阈值配置寄存器(GPIOx_VILR) (817)41.9.12EXTI输入选择寄存器0(GPIO_EXTISEL0) (817)41.9.13EXTI输入选择寄存器1(GPIO_EXTISEL1) (819)41.9.14EXTI边沿选择和使能寄存器0(GPIO_EXTIEDS0) (820)41.9.1EXTI边沿选择和使能寄存器1(GPIO_EXTIEDS1) (821)41.9.2EXTI数字滤波控制寄存器(GPIO_EXTIDF) (822)41.9.3EXTI中断标志(GPIO_EXTIISR) (822)41.9.4EXTI输入信号寄存器(GPIO_EXTIDI) (823)41.9.5FOUT配置寄存器(GPIO_FOUTSEL) (823)41.9.6WKUP控制寄存器(GPIO_PINWKEN) (824)42专用编程接口 (826)42.1概述 (826)42.2编程器使用 (826)43调试支持 (827)43.1概述 (827)43.2D EBUG引脚 (828)43.2.1SWD引脚 (828)43.2.2上拉电阻 (828)43.3SWD接口协议 (829)43.3.1协议简介 (829)43.3.2传输序列 (829)43.3.3SW-DP ID code (830)43.3.4主机读操作 (830)43.3.5主机写操作 (831)43.4SWD-DP寄存器 (832)43.4.1寄存器列表 (832)43.5C ORE DEBUG寄存器 (832)43.6低功耗调试支持 (832)43.7D EBUG相关的配置项 (833)43.8寄存器 (833)43.8.1系统模式配置寄存器 (833)43.8.2MCU DEBUG配置寄存器 (834)43.8.3HardFault查询寄存器 (835)44器件签名信息 (837)44.1存储器容量查询 (837)44.2器件UID (838)版本列表 (839)上海复旦微电子集团股份有限公司销售及服务网点 (840)。

PCI总线200Ksps/12位32通道AD4通道DA板4通道脉冲计数8通道数字输入/8通道数字输出RBH7272使用说明书北京瑞博华控制技术有限公司二00七年十月200Ksps/12位32通道AD4通道DA板4通道脉冲计数(1个旋转编码器)8通道数字输入/8通道数字输出RBH7272使用说明书一、性能特点:本板采用PCI总线接口。

本板通过采用高速高精度AD芯片、高精度的仪器放大器、高密度CPLD逻辑芯片、精细地布线以及优良的制版工艺,实现了高速、高精度实时数据采集,具有以下性能特点:1、AD高精度:综合误差小于+/-1LSB 。

2、4通道脉冲功能:第一通道脉冲与第二通道脉冲可以构成一个旋转编码器输入,实时直接给出正向与反向脉冲数;第一通道同时输出脉冲的瞬态周期,时间分辨率为1微秒;第二、第三、第四通道输出16位的计数值,输入最高脉冲频率为采样频率×255,如采样频率10000,则输入最高脉冲频率为2.55MHz。

3、开关量同步采集输入:8路开关量与4路脉冲量合成第一通道与模拟量同步采集。

便于用户对开关量的高速采集。

可以用于外部同步触发等功能。

4、DA通道数:4通道独立锁存,精度12位5、AD高速度:多通道采集速度达到200Ksps(Sample Per Second),单通道方式也能够达到70Ksps以上,特别适合于工业控制中的数据采集。

6、程控放大器功能,可以设置放大倍数为1、2、4、8或1、10、100、1000。

7、AD硬件定时:板上提供硬件定时器,可以根据需要发出定时中断,采集软件在定时中断程序中采集,从而保证准确地时间基准,适于大部分的工业实时控制和高速数据采集的应用,特别是在WINDOWS95/98/2000的环境下,由于PC系统很难提供高精度的定时,采用本板的定时器,能够提供高精度的定时,同时能够实现高精度的数据采集,因此,在WINDOWS环境下采用本板具有特别的优点。

7.3Read Device IdentifierThe Read Device Identifier command instructs the device to output manufacturer code, device identifier code, block-lock status, OTP Register data, or Read ConfigurationRegister data (see Section 6.2, “Device Command Bus Cycles” on page 18 for details on issuing the Read Device Identifier command). Table 7, “Device Identifier Information” on page 21 and T able 8, “Device ID codes” on page 21 show the address offsets and data values for this device.7.4Read CFIThe Read CFI command instructs the device to output Common Flash Interface data when read. See Section 6.1, “Device Command Codes” on page 16 for detail on issuing the CFI Query command. Section A.1, “Common Flash Interface” on page 60 shows CFI information and address offsets within the CFI database.Table 7:Device Identifier InformationItemAddress (1,2)Data Manufacturer Code 0x000x89hDevice ID Code0x01ID (see T able8)Block Lock Configuration:BBA + 0x02Lock Bit:• Block Is Unlocked DQ0 = 0b0• Block Is LockedDQ0 = 0b1• Block Is not Locked-Down DQ1 = 0b0• Block Is Locked-Down DQ1 = 0b1Read Configuration Register 0x05RCR Contents General Purpose Register (3)DBA + 0x07GPR data Lock Register 00x80PR-LK064-bit Factory-Programmed OTP Register 0x81–0x84Numonyx Factory OTP Register data64-bit User-Programmable OTP Register 0x85–0x88User OTP Register data Lock Register 10x89OTP Register lock data 128-bit User-Programmable OTP Registers0x8A–0x109User OTP Register dataNotes:1.BBA = Block Base Address.2.DBA = Device base Address, Numonyx reserves other configuration address locations.3.In P33-65nm SBC, the GPR is used as read out register for Extended Function interface command.Table 8:Device ID codesID Code TypeDevice DensityDevice Identifier Codes–T(Top Parameter)–B(Bottom Parameter)Device Code64-Mbit 881D 8820128-Mbit881E88218.0Program OperationThe device supports three programming methods: Word Programming (40h/10h),Buffered Programming (E8h, D0h), and Buffered Enhanced Factory Programming (80h,D0h). The following sections describe device programming in detail.Successful programming requires the addressed block to be unlocked. If the block islocked down, WP# must be deasserted and the block must be unlocked beforeattempting to program the block. Attempting to program a locked block causes aprogram error (SR.4 and SR.1 set) and termination of the operation. See Section 10.0,“Security” on page29 for details on locking and unlocking blocks.8.1Word ProgrammingWord programming operations are initiated by writing the Word Program Setupcommand to the device. This is followed by a second write to the device with theaddress and data to be programmed. The device outputs Status Register data whenread. See Figure29, “Word Program Flowchart” on page72. VPP must be above V PPLK,and within the specified V PPL Min/Max values.During programming, the WSM executes a sequence of internally-timed events thatprogram the desired data bits at the addressed location, and verifies that the bits aresufficiently programmed. Programming the flash memory array changes “ones” to“zeros”. Memory array bits that are zeros can be changed to ones only by erasing theblock.The Status Register can be examined for programming progress and errors by readingat any address. The device remains in the Read Status Register state until anothercommand is written to the device.Status Register bit SR.7 indicates the programming status while the sequenceexecutes. Commands that can be issued to the device during programming areProgram Suspend, Read Status Register, Read Device Identifier, Read CFI, and ReadArray (this returns unknown data).When programming has finished, Status Register bit SR.4 (when set) indicates aprogramming failure. If SR.3 is set, the WSM could not perform the word programmingoperation because VPP was outside of its acceptable limits. If SR.1 is set, the wordprogramming operation attempted to program a locked block, causing the operation toabort.Before issuing a new command, the Status Register contents should be examined andthen cleared using the Clear Status Register command. Any valid command can follow,when word programming has completed.8.2Buffered ProgrammingThe device features a 256-word buffer to enable optimum programming performance.For Buffered Programming, data is first written to an on-chip write buffer. Then thebuffer data is programmed into the flash memory array in buffer-size increments. Thiscan improve system programming performance significantly over non-bufferedprogramming. (see Figure32, “Buffer Program Flowchart” on page75).When the Buffered Programming Setup command is issued, Status Register informationis updated and reflects the availability of the buffer. SR.7 indicates buffer availability: ifset, the buffer is available; if cleared, the buffer is not available.Note:The device defaults to output SR data after the Buffered Programming Setup Command (E8h) is issued. CE# or OE# must be toggled to update Status Register. Don’t issue theprogram operation that is running during an erase suspend can be suspended toperform a read operation (see Figure30, “Program Suspend/Resume Flowchart” onpage73).When a programming operation is executing, issuing the Program Suspend commandrequests the WSM to suspend the programming algorithm at predetermined points. Thedevice continues to output Status Register data after the Program Suspend command isissued. Programming is suspended when Status Register bits SR[7,2] are set. Suspendlatency is specified in Section 15.5, “Program and Erase Characteristics” on page58.To read data from the device, the Read Array command must be issued. Read Array,Read Status Register, Read Device Identifier, Read CFI, and Program Resume are validcommands during a program suspend.During a program suspend, deasserting CE# places the device in standby, reducingactive current. VPP must remain at its programming level, and WP# must remainunchanged while in program suspend. If RST# is asserted, the device is reset.8.5Program ResumeThe Resume command instructs the device to continue programming, andautomatically clears Status Register bits SR[7,2]. This command can be written to anyaddress. If error bits are set, the Status Register should be cleared before issuing thenext instruction. RST# must remain deasserted (see Figure30, “Program Suspend/Resume Flowchart” on page73).8.6Program ProtectionWhen VPP = V IL, absolute hardware write protection is provided for all device blocks. IfVPP is at or below V PPLK, programming operations halt and SR.3 is set indicating a VPP-level error. Block Lock Registers are not affected by the voltage level on VPP; they maystill be programmed and read, even if VPP is less than V PPLK.Figure 6:Example VPP Supply ConnectionsP33-65nm SBCP33-65nm10.1.4Block Lock StatusThe Read Device Identifier command is used to determine a block’s lock status (seeSection 7.3, “Read Device Identifier” on page21). Data bits DQ[1:0] display theaddressed block’s lock status; DQ0 is the addressed block’s lock bit, while DQ1 is theaddressed block’s lock-down bit.Figure 7:Block Locking State Diagramsuspended and ready to accept another command.Next, write the desired lock command sequence to a block, which changes the lockstate of that block. After completing block lock or unlock operations, resume the eraseoperation using the Erase Resume command.Note: A Lock Block Setup command followed by any command other than Lock Block, Unlock Block, or Lock-Down Block produces a command sequence error and set StatusRegister bits SR.4 and SR.5. If a command sequence error occurs during an erasesuspend, SR.4 and SR.5 remains set, even after the erase operation is resumed. Unlessthe Status Register is cleared using the Clear Status Register command beforeresuming the erase operation, possible erase errors may be masked by the commandsequence error.P33-65nm SBC质量等级领域:宇航级IC、特军级IC、超军级IC、普军级IC、禁运IC、工业级IC,军级二三极管,功率管等;应用领域:航空航天、船舶、汽车电子、军用计算机、铁路、医疗电子、通信网络、电力工业以及大型工业设备祝您:工作顺利,生活愉快!以深圳市美光存储技术有限公司提供的参数为例,以下为PC28F640P33BF60A的详细参数,仅供参考P33-65nm11.0Status RegisterTo read the Status Register , issue the Read Status Register command at any address. Status Register information is available to which the Read Status Register , Word Program, or Block Erase command was issued. SRD is automatically made available following a Word Program, Block Erase, or Block Lock command sequence. Reads from the device after any of these command sequences outputs the device’s status until another valid command is written (e.g. the Read Array command).The Status Register is read using single asynchronous-mode or synchronous burst mode reads. SRD is output on DQ[7:0], while 0x00 is output on DQ[15:8]. Inasynchronous mode the falling edge of OE#, or CE# (whichever occurs first) updates and latches the Status Register contents. However , when reading the Status Register in synchronous burst mode, CE# or ADV# must be toggled to update SRD.The Device Ready Status bit (SR.7) provides overall status of the device. SR[6:1] present status and error information about the program, erase, suspend, VPP , and block-locked operations.Table 11:Status Register DescriptionStatus Register (SR)Default Value = 0x80Device ReadyStatusErase Suspend Status 11.Always clear the Status Register before resuming erase operations afer an Erase Suspend command; this prevents ambiguity inStatus Register information. For example, if a command sequence error occurs during an erase suspend state, the Status Register contains the command sequence error status (SR[7,5,4] set). When the erase operation resumes and finishes, possible errors during the erase operation cannot be deteted via the Stauts Register because it contains the previous error status.Erase/Blank Check StatusProgram Status VPP Status Program Suspend Status Block-LockedStatusBEFP Write StatusDRS ESS ES PS VPPS PSS BLS BWS 7654321Bit NameDescription7Device Ready Status 0 = Device is busy; program or erase cycle in progress; SR.0 valid.1 = Device is ready; SR[6:1] are valid.6Erase Suspend Status 0 = Erase suspend not in effect.1 = Erase suspend in effect.5Erase/Blank Check Status Command Sequence ErrorSR.5SR.4Description4Program Status00110101Program or Erase operation successful.Program error -operation aborted.Erase or Blank Check error - operation mand sequence error - command aborted.3VPP Status0 = VPP within acceptable limits during program or erase operation.1 = VPP < V PPLK during program or erase operation.2Program Suspend Status 0 = Program suspend not in effect.1 = Program suspend in effect.1Block-Locked Status0 = Block not locked during program or erase.1 = Block locked during program or erase; operation aborted.0BEFP Write Status22.BEFP mode is only valid in array.After Buffered Enhanced Factory Programming (BEFP) data is loaded into the buffer:0 = BEFP complete.1 = BEFP in-progress.。

D i s c l a im er : T h i s d o c u m e n t a t i o n i s n o t i n t e n d e d a s a s u b s t i t u t e f o r a n d i s n o t t o b e u s e d f o r d e t e r m i n i n g s u i t a b i l i t y o r r e l i a b i l i t y o f t h e s e p r o d u c t s f o r s p e c i f i c u s e r a p p l i c a t i o n sProduct data sheetCharacteristics140DDO35300discrete output module Modicon Quantum - 32 O solid stateMainRange of productModicon Quantum automation platform Product or component type Dc discrete output module Discrete output number32ComplementaryGroup of channels 4 groups of 8Discrete output logic Positive logic (source)Addressing requirement 2 output words Discrete output voltage 24 V DC Output voltage limits 19.2...30 VAbsolute maximum output 56 V for 1.3 s decaying pulse Voltage drop0.4 V 0.5 A Maximum load current16 A per module 16 A per module 4 A per group 4 A per group Surge current <= 5 A for 0.0005 s Response time <= 1 ms at state 0 to state 1<= 1 ms at state 1 to state 0Leakage current 0.4 mA 30 VLoad inductance Inductance(H) = 0.5/((current(A))² x (switching frequency(Hz))) 50 Hz Fault indication Blown fuseLoss of field power Associated fuse rating3 A each point 3 A each point 5 A per group 5 A per groupIsolation between channels and bus 1780 Vrms DC for 1 minute Isolation between group 500 Vrms DC for 1 minuteProtection typeInternal output protection by 5 A fuse per groupPower dissipation 1.75 W + (0.4 V x total module load current)Marking CELocal signalling1 LED green bus communication is present (Active)1 LED red external fault detected (F)32 LEDs green input status Bus current requirement 330 mA 330 mA Module format Standard Product weight0.45 kgEnvironmentProduct certificationsABS BV C-Tick DNVFM Class 1 Division 2GL GOST RINA RMRSSafety certification non interfering StandardsCSA C22.2 No 142UL 508Resistance to electrostatic discharge 4 kV contact conforming to IEC 801-28 kV on air conforming to IEC 801-2Resistance to electromagnetic fields 10 V/m 80...2000 MHz conforming to IEC 801-3Ambient air temperature for operation 0...60 °C Ambient air temperature for storage -40...85 °CRelative humidity 95 % without condensation Operating altitude<= 5000 mOffer SustainabilitySustainable offer status Green Premium productRoHS (date code: YYWW)Compliant - since 0848 - Schneider Electric declaration of conformity Schneider Electric declaration of conformity REAChReference not containing SVHC above the threshold Reference not containing SVHC above the threshold Product environmental profileAvailableProduct environmental Product end of life instructionsAvailableEnd of life manualContractual warrantyWarranty period18 monthsDimensions DrawingsRacks for Modules MountingDimensions of Modules and Racks(1) 2 slots (2) 3 slots (3) 4 slots (4) 6 slots (5)10 slots (6)16 slotsConnections and Schema24 Vdc Discrete Output Source Module Wiring Diagram。

HK32C005数据手册版本:1.3发布日期:2023-08-15深圳市航顺芯片技术研发有限公司前言前言编写目的本文档介绍了HK32C005系列芯片的结构框图、存储器映射、外设接口、电气特性、引脚封装等,旨在帮助用户快速了解该系列芯片的特点及功能。

读者对象本文适用于以下读者:•开发工程师•芯片测试工程师•芯片选型工程师版本说明本文档对应的产品系列为HK32C005系列芯片。