STM8S和STM32选型手册(中文版)

- 格式:pdf

- 大小:916.30 KB

- 文档页数:6

23 串行外设接口(SPI)小容量产品是指闪存存储器容量在16K 至32K 字节之间的STM32F101xx、STM32F102xx和STM32F103xx微控制器。

中容量产品是指闪存存储器容量在64K至128K字节之间的STM32F101xx、STM32F102xx和STM32F103xx微控制器。

大容量产品是指闪存存储器容量在256K至512K字节之间的STM32F101xx和STM32F103xx微控制器。

互联型产品是指STM32F105xx和STM32F107xx微控制器。

除非特别说明,本章描述的模块适用于整个STM32F10xxx微控制器系列。

23.1 SPI简介在大容量产品和互联型产品上,SPI接口可以配置为支持SPI协议或者支持I2S音频协议。

SPI接口默认工作在SPI方式,可以通过软件把功能从SPI模式切换到I2S模式。

在小容量和中容量产品上,不支持I2S音频协议。

串行外设接口(SPI)允许芯片与外部设备以半/全双工、同步、串行方式通信。

此接口可以被配置成主模式,并为外部从设备提供通信时钟(SCK)。

接口还能以多主配置方式工作。

它可用于多种用途,包括使用一条双向数据线的双线单工同步传输,还可使用CRC校验的可靠通信。

I2S也是一种3引脚的同步串行接口通讯协议。

它支持四种音频标准,包括飞利浦I2S标准,MSB 和LSB对齐标准,以及PCM标准。

它在半双工通讯中,可以工作在主和从2种模式下。

当它作为主设备时,通过接口向外部的从设备提供时钟信号。

警告:由于 SPI3/I2S3 的部分引脚与 JTAG 引脚共享 (SPI3_NSS/I2S3_WS 与 JTDI ,SPI3_SCK/I2S3_CK与JTDO),因此这些引脚不受IO控制器控制,他们(在每次复位后)被默认保留为JTAG用途。

如果用户想把引脚配置给SPI3/I2S3,必须(在调试时)关闭JTAG并切换至SWD接口,或者(在标准应用时)同时关闭JTAG和SWD接口。

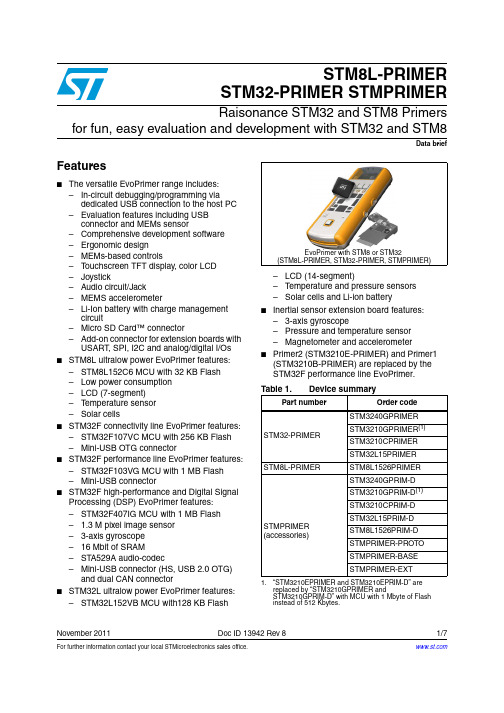

STM32F10xxx参考手册参考手册小,中和大容量的STM32F101xx, STM32F102xx和STM32F103xxARM内核32位高性能微控制器导言本参考手册针对应用开发,提供关于如何使用小容量、中容量和大容量的STM32F101xx、STM32F102xx或者STM32F103xx微控制器的存储器和外设的详细信息。

在本参考手册中STM32F101xx、STM32F102xx和STM32F103xx被统称为STM32F10xxx。

STM32F10xxx系列拥有不同的存储器容量,封装和外设配置。

关于订货编号、电气和物理性能参数,请参考STM32F101xx、STM32F102xx和STM32F103xx 的数据手册。

关于芯片内部闪存的编程,擦除和保护操作,请参考STM32F10xxx闪存编程手册。

关于ARM Cortex™-M3内核的具体信息,请参考Cortex™-M3技术参考手册。

相关文档● Cortex™-M3技术参考手册,可按下述链接下载:/help/topic/com.arm.doc.ddi0337e/DDI0337E_cortex_m3_r1p1_trm.pdf下述文档可在ST网站下载(/mcu/):● STM32F101xx、STM32F102xx和STM32F103xx的数据手册。

● STM32F10xxx闪存编程手册。

* 感谢南京万利提供原始翻译文档目录1文中的缩写 161.1寄存器描述表中使用的缩写列表 161.2术语表161.3可用的外设16 2存储器和总线构架 172.1系统构架172.2存储器组织182.3存储器映像192.3.1嵌入式SRAM 202.3.2位段202.3.3嵌入式闪存 212.4启动配置23 3CRC计算单元(CRC) 253.1CRC简介253.2CRC主要特性253.3CRC功能描述253.4CRC寄存器263.4.1数据寄存器(CRC_DR) 263.4.2独立数据寄存器(CRC_IDR) 263.4.3控制寄存器(CRC_CR) 273.4.4CRC寄存器映像 27 4电源控制(PWR) 284.1电源284.1.1独立的A/D转换器供电和参考电压 284.1.2电池备份区域 294.1.3电压调节器 294.2电源管理器294.2.1上电复位(POR)和掉电复位(PDR) 294.2.2可编程电压监测器(PVD) 304.3低功耗模式304.3.1降低系统时钟 314.3.2外部时钟的控制 314.3.3睡眠模式 314.3.4停止模式 324.3.5待机模式 334.3.6低功耗模式下的自动唤醒(AWU) 344.4电源控制寄存器 354.4.1电源控制寄存器(PWR_CR) 354.4.2电源控制/状态寄存器 364.4.3PWR寄存器地址映像 37 5备份寄存器(BKP) 385.1BKP简介385.2BKP特性385.3BKP功能描述385.3.1侵入检测 385.3.2RTC校准 395.4BKP寄存器描述 395.4.1备份数据寄存器x(BKP_DRx) (x = 1 … 10) 395.4.2RTC时钟校准寄存器(BKP_RTCCR) 395.4.3备份控制寄存器(BKP_CR) 405.4.4备份控制/状态寄存器(BKP_CSR) 405.4.5BKP寄存器映像 42 6复位和时钟控制(RCC) 456.1复位456.1.1系统复位 456.1.2电源复位 456.1.3备份域复位 466.2时钟466.2.1HSE时钟 486.2.2HSI时钟 486.2.3PLL 496.2.4LSE时钟 496.2.5LSI时钟496.2.6系统时钟(SYSCLK)选择 506.2.7时钟安全系统(CSS) 506.2.8RTC时钟 506.2.9看门狗时钟 506.2.10时钟输出 506.3RCC寄存器描述 516.3.1时钟控制寄存器(RCC_CR) 516.3.2时钟配置寄存器(RCC_CFGR) 526.3.3时钟中断寄存器 (RCC_CIR) 546.3.4APB2外设复位寄存器 (RCC_APB2RSTR) 566.3.5APB1外设复位寄存器 (RCC_APB1RSTR) 586.3.6AHB外设时钟使能寄存器 (RCC_AHBENR) 606.3.7APB2外设时钟使能寄存器(RCC_APB2ENR) 616.3.8APB1外设时钟使能寄存器(RCC_APB1ENR) 626.3.9备份域控制寄存器 (RCC_BDCR) 656.3.10控制/状态寄存器 (RCC_CSR) 666.3.11RCC寄存器地址映像 68 7通用和复用功能I/O(GPIO和AFIO) 697.1GPIO功能描述697.1.1通用I/O(GPIO) 707.1.2单独的位设置或位清除 717.1.3外部中断/唤醒线 717.1.4复用功能(AF) 717.1.5软件重新映射I/O复用功能 717.1.6GPIO锁定机制 717.1.7输入配置 717.1.8输出配置 727.1.9复用功能配置 737.1.10模拟输入配置 737.2GPIO寄存器描述 757.2.1端口配置低寄存器(GPIOx_CRL) (x=A..E) 757.2.2端口配置高寄存器(GPIOx_CRH) (x=A..E) 757.2.3端口输入数据寄存器(GPIOx_IDR) (x=A..E) 767.2.4端口输出数据寄存器(GPIOx_ODR) (x=A..E) 767.2.5端口位设置/清除寄存器(GPIOx_BSRR) (x=A..E) 777.2.6端口位清除寄存器(GPIOx_BRR) (x=A..E) 777.2.7端口配置锁定寄存器(GPIOx_LCKR) (x=A..E) 777.3复用功能I/O和调试配置(AFIO) 787.3.1把OSC32_IN/OSC32_OUT作为GPIO 端口PC14/PC15 787.3.2把OSC_IN/OSC_OUT引脚作为GPIO端口PD0/PD1 787.3.3CAN复用功能重映射 797.3.4JTAG/SWD复用功能重映射 797.3.5ADC复用功能重映射 807.3.6定时器复用功能重映射 807.3.7USART复用功能重映射 817.3.8I2C 1 复用功能重映射 827.3.9SPI 1复用功能重映射 827.4AFIO寄存器描述 837.4.1事件控制寄存器(AFIO_EVCR) 837.4.2复用重映射和调试I/O配置寄存器(AFIO_MAPR) 837.4.3外部中断配置寄存器1(AFIO_EXTICR1) 867.4.4外部中断配置寄存器2(AFIO_EXTICR2) 867.4.5外部中断配置寄存器3(AFIO_EXTICR3) 877.4.6外部中断配置寄存器4(AFIO_EXTICR4) 877.5GPIO 和AFIO寄存器地址映象 88 8中断和事件 898.1嵌套向量中断控制器 898.1.1系统嘀嗒(SysTick)校准值寄存器 898.1.2中断和异常向量 898.2外部中断/事件控制器(EXTI) 918.2.1主要特性 918.2.2框图928.2.3唤醒事件管理 928.2.4功能说明 928.2.5外部中断/事件线路映像 948.3EXTI 寄存器描述 958.3.1中断屏蔽寄存器(EXTI_IMR) 958.3.2事件屏蔽寄存器(EXTI_EMR) 958.3.3上升沿触发选择寄存器(EXTI_RTSR) 968.3.4下降沿触发选择寄存器(EXTI_FTSR) 968.3.5软件中断事件寄存器(EXTI_SWIER) 978.3.6挂起寄存器(EXTI_PR) 978.3.7外部中断/事件寄存器映像 98 9DMA 控制器(DMA) 999.1DMA简介999.2DMA主要特性999.3功能描述1009.3.1DMA处理 1009.3.2仲裁器1009.3.3DMA 通道 1019.3.4可编程的数据传输宽度,对齐方式和数据大小端 1029.3.5错误管理 1039.3.6中断1039.3.7DMA请求映像 1049.4DMA寄存器1079.4.1DMA中断状态寄存器(DMA_ISR) 1079.4.2DMA中断标志清除寄存器(DMA_IFCR) 1089.4.3DMA通道x配置寄存器(DMA_CCRx)(x = 1…7) 1089.4.4DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1…7) 1109.4.5DMA通道x外设地址寄存器(DMA_CPARx)(x = 1…7) 1109.4.6DMA通道x存储器地址寄存器(DMA_CPARx)(x = 1…7) 1109.4.7DMA寄存器映像 111 10模拟/数字转换(ADC) 11310.1ADC介绍11310.2ADC主要特征11310.3ADC功能描述11410.3.1ADC开关控制 11510.3.2ADC时钟 11510.3.3通道选择 11510.3.4单次转换模式 11510.3.5连续转换模式 11610.3.6时序图11610.3.7模拟看门狗 11610.3.8扫描模式 11710.3.9注入通道管理 11710.3.10间断模式 11810.4校准11910.5数据对齐11910.6可编程的通道采样时间 12010.7外部触发转换12010.8DMA请求12110.9双ADC模式12110.9.1同步注入模式 12210.9.2同步规则模式 12310.9.3快速交替模式 12310.9.4慢速交替模式 12410.9.5交替触发模式 12410.9.6独立模式 12510.9.7混合的规则/注入同步模式 12510.9.8混合的同步规则+交替触发模式 12510.9.9混合同步注入+交替模式 12610.10温度传感器12610.11ADC中断12710.12ADC寄存器描述 12810.12.1ADC状态寄存器(ADC_SR) 12810.12.2ADC控制寄存器1(ADC_CR1) 12910.12.3ADC控制寄存器2(ADC_CR2) 13110.12.4ADC采样时间寄存器1(ADC_SMPR1) 13310.12.5ADC采样时间寄存器2(ADC_SMPR2) 13310.12.6ADC注入通道数据偏移寄存器x (ADC_JOFRx)(x=1..4) 13410.12.7ADC看门狗高阀值寄存器(ADC_HTR) 13410.12.8ADC看门狗低阀值寄存器(ADC_LRT) 13410.12.9ADC规则序列寄存器1(ADC_SQR1) 13510.12.10ADC规则序列寄存器2(ADC_SQR2) 13510.12.11ADC规则序列寄存器3(ADC_SQR3) 13610.12.12ADC注入序列寄存器(ADC_JSQR) 13610.12.13ADC 注入数据寄存器x (ADC_JDRx) (x= 1..4) 13710.12.14ADC规则数据寄存器(ADC_DR) 13710.12.15ADC寄存器地址映像 138 11数字/模拟转换(DAC) 14011.1DAC简介14011.2DAC主要特征14011.3DAC功能描述14111.3.1使能DAC通道 14111.3.2使能DAC输出缓存 14111.3.3DAC数据格式 14211.3.4DAC转换 14211.3.5DAC输出电压 14311.3.6选择DAC触发 14311.3.7DMA请求 14411.3.8噪声生成 14411.3.9三角波生成 14511.4双DAC通道转换 14511.4.1无波形生成的独立触发 14511.4.2带相同LFSR生成的独立触发 14611.4.3带不同LFSR生成的独立触发 14611.4.4带相同三角波生成的独立触发 14611.4.5带不同三角波生成的独立触发 14611.4.6同时软件启动 14711.4.7不带波形生成的同时触发 14711.4.8带相同LFSR生成的同时触发 14711.4.9带不同LFSR生成的同时触发 14711.4.10带相同三角波生成的同时触发 14711.4.11带不同三角波生成的同时触发 14811.5DAC寄存器14911.5.1DAC控制寄存器(DAC_CR) 14911.5.2DAC软件触发寄存器(DAC_SWTRIGR) 15111.5.3DAC通道1的12位右对齐数据保持寄存器(DAC_DHR12R1) 15211.5.4DAC通道1的12位左对齐数据保持寄存器(DAC_DHR12L1) 15211.5.5DAC通道1的8位右对齐数据保持寄存器(DAC_DHR8R1) 15211.5.6DAC通道2的12位右对齐数据保持寄存器(DAC_DHR12R2) 15311.5.7DAC通道2的12位左对齐数据保持寄存器(DAC_DHR12L2) 15311.5.8DAC通道2的8位右对齐数据保持寄存器(DAC_DHR8R2) 15311.5.9双DAC的12位右对齐数据保持寄存器(DAC_DHR12RD) 15411.5.10双DAC的12位左对齐数据保持寄存器(DAC_DHR12LD) 15411.5.11双DAC的8位右对齐数据保持寄存器(DAC_DHR8RD) 15411.5.12DAC通道1数据输出寄存器(DAC_DOR1) 15511.5.13DAC通道2数据输出寄存器(DAC_DOR2) 15511.5.14DAC寄存器映像 156 12高级控制定时器(TIM1和TIM8) 15712.1TIM1和TIM8简介 15712.2TIM1和TIM8主要特性 15712.3TIM1和TIM8功能描述 15812.3.1时基单元 15812.3.2计数器模式 16012.3.3重复计数器 16712.3.4时钟选择 16812.3.5捕获/比较通道 17112.3.6输入捕获模式 17312.3.7PWM输入模式 17412.3.8强置输出模式 17412.3.9输出比较模式 17512.3.10PWM模式 17612.3.11互补输出和死区插入 17812.3.12使用刹车功能 17912.3.13在外部事件时清除OCxREF信号 18012.3.14产生六步PWM输出 18112.3.15单脉冲模式 18212.3.16编码器接口模式 18312.3.17定时器输入异或功能 18512.3.18与霍尔传感器的接口 18512.3.19TIMx定时器和外部触发的同步 18712.3.20定时器同步 19012.3.21调试模式 19012.4TIM1和TIM8寄存器描述 19112.4.1控制寄存器1(TIMx_CR1) 19112.4.2控制寄存器2(TIMx_CR2) 19212.4.3从模式控制寄存器(TIMx_SMCR) 19312.4.4DMA/中断使能寄存器(TIMx_DIER) 19512.4.5状态寄存器(TIMx_SR) 19612.4.6事件产生寄存器(TIMx_EGR) 19712.4.7捕获/比较模式寄存器1(TIMx_CCMR1) 19812.4.8捕获/比较模式寄存器2(TIMx_CCMR2) 20012.4.9捕获/比较使能寄存器(TIMx_CCER) 20212.4.10计数器(TIMx_CNT) 20312.4.11预分频器(TIMx_PSC) 20412.4.12自动重装载寄存器(TIMx_ARR) 20412.4.13重复计数寄存器(TIMx_RCR) 20412.4.14捕获/比较寄存器1(TIMx_CCR1) 20512.4.15捕获/比较寄存器2(TIMx_CCR2) 20512.4.16捕获/比较寄存器3(TIMx_CCR3) 20512.4.17捕获/比较寄存器(TIMx_CCR4) 20612.4.18刹车和死区寄存器(TIMx_BDTR) 20612.4.19DMA控制寄存器(TIMx_DCR) 20812.4.20连续模式的DMA地址(TIMx_DMAR) 20812.4.21TIM1和TIM8寄存器图 209 13通用定时器(TIMx) 21113.1TIMx简介21113.2TIMx主要功能21113.3TIMx功能描述21213.3.1时基单元 21213.3.2计数器模式 21313.3.3时钟选择 22113.3.4捕获/比较通道 22313.3.5输入捕获模式 22513.3.6PWM输入模式 22513.3.7强置输出模式 22613.3.8输出比较模式 22613.3.9PWM 模式 22713.3.10单脉冲模式 22913.3.11在外部事件时清除OCxREF信号 23113.3.12编码器接口模式 23113.3.13定时器输入异或功能 23313.3.14定时器和外部触发的同步 23313.3.15定时器同步 23513.3.16调试模式 23913.4TIMx寄存器描述 24013.4.1控制寄存器1(TIMx_CR1) 24013.4.2控制寄存器2(TIMx_CR2) 24113.4.3从模式控制寄存器(TIMx_SMCR) 24213.4.4DMA/中断使能寄存器(TIMx_DIER) 24313.4.5状态寄存器(TIMx_SR) 24413.4.6事件产生寄存器(TIMx_EGR) 24513.4.7捕获/比较模式寄存器1(TIMx_CCMR1) 24613.4.8捕获/比较模式寄存器2(TIMx_CCMR2) 24913.4.9捕获/比较使能寄存器(TIMx_CCER) 25113.4.10计数器(TIMx_CNT) 25213.4.11预分频器(TIMx_PSC) 25213.4.12自动重装载寄存器(TIMx_ARR) 25213.4.13捕获/比较寄存器1(TIMx_CCR1) 25213.4.14捕获/比较寄存器2(TIMx_CCR2) 25313.4.15捕获/比较寄存器3(TIMx_CCR3) 25313.4.16捕获/比较寄存器4(TIMx_CCR4) 25313.4.17DMA控制寄存器(TIMx_DCR) 25413.4.18连续模式的DMA地址(TIMx_DMAR) 25413.4.19TIMx寄存器图 255 14基本定时器(TIM6和TIM7) 25714.1TIM6和TIM7简介 25714.2TIM6和TIM7的主要特性 25714.3TIM6和TIM7的功能 25814.3.1时基单元 25814.3.2计数模式 25914.3.3时钟源26114.3.4调试模式 26214.4TIM6和TIM7寄存器 26214.4.1控制寄存器1(TIMx_CR1) 26214.4.2控制寄存器2(TIMx_CR2) 26314.4.3DMA/中断使能寄存器(TIMx_DIER) 26314.4.4状态寄存器(TIMx_SR) 26414.4.5事件产生寄存器(TIMx_EGR) 26414.4.6计数器(TIMx_CNT) 26414.4.7预分频器(TIMx_PSC) 26514.4.8自动重装载寄存器(TIMx_ARR) 26514.4.9TIM6和TIM7寄存器图 266 15实时时钟(RTC) 26715.1RTC简介26715.2主要特性26715.3功能描述26715.3.1概述26715.3.2复位过程 26815.3.3读RTC寄存器 26815.3.4配置RTC寄存器 26915.3.5RTC标志的设置 26915.4RTC寄存器描述 27015.4.1RTC控制寄存器高位(RTC_CRH) 27015.4.2RTC控制寄存器低位(RTC_CRL) 27015.4.3RTC预分频装载寄存器(RTC_PRLH/RTC_PRLL) 27115.4.4RTC预分频器余数寄存器(RTC_DIVH / RTC_DIVL) 27215.4.5RTC计数器寄存器 (RTC_CNTH / RTC_CNTL) 27215.4.6RTC闹钟寄存器(RTC_ALRH/RTC_ALRL) 27315.4.7RTC寄存器映像 275 16独立看门狗(IWDG) 27616.1简介27616.2IWDG主要性能27616.3IWDG功能描述27616.3.1硬件看门狗 27616.3.2寄存器访问保护 27616.3.3调试模式 27616.4IWDG寄存器描述 27716.4.1键寄存器(IWDG_KR) 27716.4.2预分频寄存器(IWDG_PR) 27816.4.3重装载寄存器(IWDG_RLR) 27816.4.4状态寄存器(IWDG_SR) 27916.4.5IWDG寄存器映像 279 17窗口看门狗(WWDG) 28017.1WWDG简介28017.2WWDG主要特性 28017.3WWDG功能描述 28017.4如何编写看门狗超时程序 28117.5调试模式28217.6寄存器描述28217.6.1控制寄存器(WWDG_CR) 28217.6.2配置寄存器(WWDG_CFR) 28317.6.3状态寄存器(WWDG_SR) 28317.6.4WWDG寄存器映像 284 18灵活的静态存储器控制器(FSMC) 28518.1FSMC功能描述28518.2框图28518.3AHB接口28618.3.1支持的存储器和操作 28618.4外部设备地址映像 28718.4.1NOR和PSRAM地址映像 28818.4.2NAND和PC卡地址映像 28818.5NOR闪存和PSRAM控制器 28918.5.1外部存储器接口信号 29018.5.2支持的存储器及其操作 29118.5.3时序规则 29118.5.4NOR闪存和PSRAM时序图 29118.5.5同步的成组读 30418.5.6NOR闪存和PSRAM控制器寄存器 30818.6NAND闪存和PC卡控制器 31318.6.1外部存储器接口信号 31318.6.2NAND闪存/PC卡支持的存储器及其操作 31418.6.3NAND闪存、ATA和PC卡时序图 31418.6.4NAND闪存操作 31518.6.5NAND闪存预等待功能 31618.6.6NAND闪存的纠错码ECC计算(NAND闪存) 31718.6.7NAND闪存和PC卡控制器寄存器 31718.7FSMC寄存器地址映象 324 19SDIO接口(SDIO) 32519.1SDIO主要功能32519.2SDIO总线拓扑32519.3SDIO功能描述32819.3.1SDIO适配器 32919.3.2SDIO AHB接口 33619.4卡功能描述33619.4.1卡识别模式 33619.4.2卡复位33619.4.3操作电压范围确认 33719.4.4卡识别过程 33719.4.5写数据块 33819.4.6读数据块 33819.4.7数据流操作,数据流写入和数据流读出(只适用于多媒体卡) 33819.4.8擦除:成组擦除和扇区擦除 33919.4.9宽总线选择和解除选择 34019.4.10保护管理 34019.4.11卡状态寄存器 34219.4.12SD状态寄存器 34419.4.13SD I/O模式 34719.4.14命令与响应 34819.5响应格式35019.5.1R1(普通响应命令) 35119.5.2R1b 35119.5.3R2(CID、CSD寄存器) 35119.5.4R3(OCR寄存器) 35119.5.5R4(快速I/O) 35219.5.6R4b 35219.5.7R5(中断请求) 35219.5.8R6(中断请求) 35319.6SDIO I/O卡特定的操作 35319.6.1使用SDIO_D2信号线的SDIO I/O读等待操作 35319.6.2使用停止SDIO_CK的SDIO读等待操作 35319.6.3SDIO暂停/恢复操作 35419.6.4SDIO中断 35419.7CE-ATA特定操作 35419.7.1命令完成指示关闭 35419.7.2命令完成指示使能 35419.7.3CE-ATA中断 35419.7.4中止CMD61 35419.8硬件流控制35419.9SDIO寄存器35519.9.1SDIO电源控制寄存器(SDIO_POWER) 35519.9.2SDIO时钟控制寄存器(SDIO_CLKCR) 35519.9.3SDIO参数寄存器(SDIO_ARG) 35619.9.4SDIO命令寄存器(SDIO_CMD) 35619.9.5SDIO命令响应寄存器(SDIO_RESPCMD) 35719.9.6SDIO响应1..4寄存器(SDIO_RESPx) 35719.9.7SDIO数据定时器寄存器(SDIO_DTIMER) 35819.9.8SDIO数据长度寄存器(SDIO_DLEN) 35819.9.9SDIO数据控制寄存器(SDIO_DCTRL) 35819.9.10SDIO数据计数器寄存器(SDIO_DCOUNT) 36019.9.11SDIO状态寄存器(SDIO_STA) 36019.9.12SDIO清除中断寄存器(SDIO_ICR) 36119.9.13SDIO中断屏蔽寄存器(SDIO_MASK) 36219.9.14SDIO FIFO计数器寄存器(SDIO_FIFOCNT) 36419.9.15SDIO数据FIFO寄存器(SDIO_FIFO) 36419.9.16SDIO寄存器映像 365 20USB全速设备接口(USB) 36620.1USB简介36620.2USB主要特征36620.3USB功能描述36720.3.1USB功能模块描述 36820.4编程中需要考虑的问题 36920.4.1通用USB设备编程 36920.4.2系统复位和上电复位 36920.4.3双缓冲端点 37220.4.4同步传输 37320.4.5挂起/恢复事件 37420.5USB寄存器描述 37520.5.1通用寄存器 37520.5.2端点寄存器 38020.5.3缓冲区描述表 38220.5.4USB寄存器映像 385 21控制器局域网(bxCAN) 38721.1bxCAN简介38721.2bxCAN主要特点 38721.2.1总体描述 38821.3bxCAN工作模式 38921.3.1初始化模式 39021.3.2正常模式 39021.3.3睡眠模式(低功耗) 39021.3.4测试模式 39021.3.5静默模式 39021.3.6环回模式 39121.3.7环回静默模式 39121.4bxCAN功能描述 39221.4.1发送处理 39221.4.2时间触发通信模式 39321.4.3接收管理 39321.4.4标识符过滤 39521.4.5报文存储 39821.4.6出错管理 39921.4.7位时间特性 40021.5bxCAN中断40221.6CAN 寄存器描述 40321.6.1寄存器访问保护 40321.6.2控制和状态寄存器 40321.6.3邮箱寄存器 41121.6.4CAN过滤器寄存器 41521.6.5bxCAN寄存器列表 419 22串行外设接口(SPI) 42222.1SPI简介42222.2SPI和I2S主要特征 42222.2.1SPI特征42222.2.2I2S功能42322.3SPI功能描述42422.3.1概述42422.3.2SPI从模式 42622.3.3SPI主模式 42722.3.4单工通信 42822.3.5状态标志 42822.3.6CRC计算 42922.3.7利用DMA的SPI通信 42922.3.8错误标志 43022.3.9关闭SPI 43022.3.10SPI中断43022.4I2S功能描述43122.4.1I2S功能描述 43122.4.2支持的音频协议 43222.4.3时钟发生器 43722.4.4I2S主模式 43822.4.5I2S从模式 43922.4.6状态标志位 44022.4.7错误标志位 44122.4.8I2S中断44122.4.9DMA功能 44122.5SPI和I2S寄存器描述 44222.5.1SPI控制寄存器1(SPI_CR1)(I2S模式下不使用) 44222.5.2SPI控制寄存器2(SPI_CR2) 44322.5.3SPI 状态寄存器(SPI_SR) 44422.5.4SPI 数据寄存器(SPI_DR) 44522.5.5SPI CRC多项式寄存器(SPI_CRCPR) 44622.5.6SPI Rx CRC寄存器(SPI_RXCRCR) 44622.5.7SPI Tx CRC寄存器(SPI_TXCRCR) 44622.5.8SPI_I2S配置寄存器(SPI_I2S_CFGR) 44722.5.9SPI_I2S预分频寄存器(SPI_I2SPR) 44822.5.10SPI 寄存器地址映象 449 23I2C接口45023.1I2C简介45023.2I2C主要特点45023.3I2C功能描述45123.3.1模式选择 45123.3.2I2C从模式 45223.3.3I2C主模式 45423.3.4错误条件 45623.3.5SDA/SCL线控制 45723.3.6SMBus 45723.3.7DMA请求 45923.3.8包错误校验(PEC) 46023.4I2C中断请求46123.5I2C调试模式46223.6I2C寄存器描述46223.6.1控制寄存器1(I2C_CR1) 46223.6.2控制寄存器2(I2C_CR2) 46423.6.3自身地址寄存器1(I2C_OAR1) 46523.6.4自身地址寄存器2(I2C_OAR2) 46523.6.5数据寄存器(I2C_DR) 46523.6.6状态寄存器1(I2C_SR1) 46623.6.7状态寄存器2 (I2C_SR2) 46823.6.8时钟控制寄存器(I2C_CCR) 46923.6.9TRISE寄存器(I2C_TRISE) 47023.6.10I2C寄存器地址映象 471 24通用同步异步收发器(USART) 47224.1USART介绍47224.2USART主要特性 47224.3USART功能概述 47324.3.1USART 特性描述 47424.3.2发送器47524.3.3接收器47724.3.4分数波特率的产生 48024.3.5多处理器通信 48124.3.6校验控制 48224.3.7LIN(局域互联网)模式 48324.3.8USART 同步模式 48524.3.9单线半双工通信 48724.3.10智能卡48724.3.11IrDA SIR ENDEC 功能块 48824.3.12利用DMA连续通信 49024.3.13硬件流控制 49124.4USART中断请求 49224.5USART模式配置 49324.6USART寄存器描述 49424.6.1状态寄存器(USART_SR) 49424.6.2数据寄存器(USART_DR) 49524.6.3波特比率寄存器(USART_BRR) 49624.6.4控制寄存器1(USART_CR1) 49624.6.5控制寄存器2(USART_CR2) 49824.6.6控制寄存器3(USART_CR3) 49924.6.7保护时间和预分频寄存器(USART_GTPR) 50124.6.8USART寄存器地址映象 502 25器件电子签名 50325.1存储器容量寄存器 50325.1.1闪存容量寄存器 50325.2产品唯一身份标识寄存器(96位) 503 26调试支持(DBG) 50526.1概况50526.2ARM参考文献50626.3SWJ调试端口(serial wire and JTAG) 50626.3.1JTAG-DP和SW-DP切换的机制 50726.4引脚分布和调试端口脚 50726.4.1SWJ调试端口脚 50726.4.2灵活的SWJ-DP脚分配 50726.4.3JTAG脚上的内部上拉和下拉 50826.4.4利用串行接口并释放不用的调试脚作为普通I/O口 50826.5STM32F10xxx JTAG TAP 连接 50926.6ID 代码和锁定机制 50926.6.1微控制器设备ID编码 50926.6.2边界扫描TAP 51026.6.3Cortex-M3 TAP 51026.6.4Cortex-M3 JEDEC-106 ID代码 51126.7JTAG调试端口51126.8SW调试端口51226.8.1SW协议介绍 51226.8.2SW协议序列 51226.8.3SW-DP状态机(Reset, idle states, ID code) 51326.8.4DP和AP读/写访问 51326.8.5SW-DP寄存器 51326.8.6SW-AP寄存器 514 26.9对于JTAG-DP或SWDP都有效的AHB-AP (AHB 访问端口) 514 26.10内核调试515 26.11调试器主机在系统复位下的连接能力 515 26.12FPB (Flash patch breakpoint) 515 26.13DWT(data watchpoint trigger) 516 26.14ITM (instrumentation trace macrocell) 51626.14.1概述51626.14.2时间戳包,同步和溢出包 516 26.15MCU调试模块(MCUDBG) 51726.15.1低功耗模式的调试支持 51726.15.2支持定时器、看门狗、bxCAN和I2C的调试 51826.15.3调试MCU配置寄存器 518 26.16TPIU (trace port interface unit) 52026.16.1导言52026.16.2跟踪引脚分配 52026.16.3TPUI格式器 52226.16.4TPUI帧异步包 52226.16.5同步帧包的发送 52226.16.6同步模式 52226.16.7异步模式 52326.16.8TRACECLKIN在STM32F10xxx内部的连接 52326.16.9TPIU寄存器 52326.16.10配置的例子 524 26.17DBG寄存器地址映象 5241 文中的缩写1.1 寄存器描述表中使用的缩写列表在对寄存器的描述中使用了下列缩写:read / write (rw) 软件能读写此位。

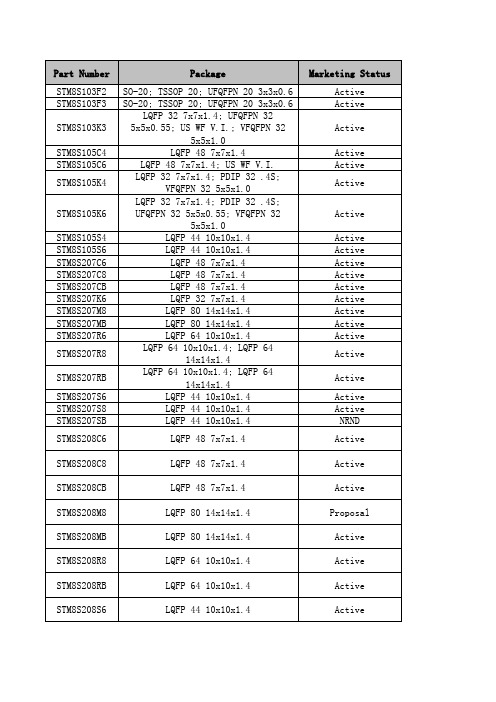

STM8S MCU family 8-bit microcontroller/mcuSeptember 2008STMicroelectronics’ STM8S family of general-purpose 8-bit Flash microcontrollers offers ideal solutions for industrial and appliance market requirements. An advanced core version combined with a 3-stage pipeline ranks the STM8S microcontroller in the top position for performance. The true embedded EEPROM and the calibrated RC oscillator bring a significant cost effectiveness to the majority of applications. An easy-to-use and intuitive development environment contributes to improving time to market.STM8S: robust and reliableIn addition to performance, comprehensive design specifications and specific peripheral features make the STM8S robust and reliable:n 2 internal RC oscillators with dual independent watchdogsn Clock security system (CSS) to monitor the failure of external clock source n Complementary copy of configuration option bytes and EMS reset n Low emission in accordance with the IEC 61967 standardsn Outstanding robustness performance according to IEC 1000-4-2 and IEC 1000-4-4 standards n High current injection immunity (1 µA leakage current when 4 mA current is injected in adjacent pin)n Dedicated firmware library compliant to Class B of IEC 60335STM8S20x Performance lineUp to 6 KB SRAM2nd UARTSTM8 core @ 24 MHzUARTLIN/Smartcard/IrDA I²C400 kHz multimasterSPI 10 MHz Up to 3 x 16-bit timer8-bit timer 2 x Watchdog (IWDG and WWDG)AWUBeeper 1/2/4 Khz 10-bit ADC Up to 16 channelXTAL16 MHz int.RC osc.128 MHz int.RC osc.SWIM Debug module STM8S10x Access lineSTM8 core @ 16 MHzCAN 2.0BUp to 2 KB SRAMSTM8 core @ 16 MHz Up to 2 KB EEPROMUp to 1 KB EEPROMUp to 128 KB FlashUp to 32 KB FlashSTM8S product linesSTM8 coren 1.6 CPI average n 20 MIPs peak @ 24 MHzn32-bit memory interface n 3-stage pipelinen 16-bit index registers n 20 addressing modesSTM8S MCU familySTM8S portfolioTSSOP20LQFP32LQFP44LQFP64LQFP80LQFP48(*) w/wo EEPROMPerformance linePin count Memory sizeVQFN20, VQFN32 and VQFN48 packages are under qualification Access line (*)Under development© STMicroelectronics - September 2008 - Printed in Italy - All rights reservedThe STMicroelectronics corporate logo is a registered trademark of the STMicroelectronics group of companies.All other names are the property of their respective owners.For more information on ST products and solutions,visit Order code: BRSTM8S0908Device summaryHardware and software development tools 1。

UM0560User manualSTM8 bootloader 1 IntroductionThis document describes the features and operation of the STM8 integrated bootloaderprogram. This code embedded in the system memory of the device (ROM memory allowsmemories, including Flash program, data EEPROM, and RAM, to be written into the deviceusing the standard serial interfaces LINUART/UART/USART, SPI, and CAN.The bootloader code is similar for all STM8 versions. However, even though a peripheralmay be present in a product, the product may not support it (for example the SPI is notsupported in 128 Kbyte devices. In addition, different STM8 device types support differentperipherals (see Table5: Serial interfaces associated with STM8 devices for detailedinformation.For further information on the STM8 family features, pinout, electrical characteristics,mechanical data and ordering information, please refer to the STM8 datasheets.March 2011Doc ID 14798 Rev 41/70Contents UM0560Contents1Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12Bootloader introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62.1Bootloader activation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73Peripheral settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.1USART/UARTs settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 3.1.1LINUART/UARTs in “reply” mode settings . . . . . . . . . . . . . . . . . . . . . . . 11 3.2SPI settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123.3CAN settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134Bootloader command set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144.1Get command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154.1.1Get command via USART/LINUART/UART1/ UART2/UART3 . . . . . . . . 15 4.1.2Get command via SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174.1.3Get command via CAN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194.2Read memory command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214.2.1Read memory command via USART/LINUART/UART1/UART2/UART3 214.2.2Read memory command via SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234.2.3Read memory command via CAN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264.3Erase memory command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274.3.1Erase memory command via USART/LINUART/UART1/UART2/UART3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284.3.2Erase memory command via SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 314.3.3Erase memory command via CAN . . . . . . . . . . . . . . . . . . . . . . . . . . . . 334.4Write memory command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 354.4.1Write memory command via USART/LINUART/UART1/UART2/UART3 364.4.2Write memory command via SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 384.4.3Write memory command via CAN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 414.5Speed command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 434.5.1Speed command via CAN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 434.6Go command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 454.6.1Go command via USART/LINUART/UART1/UART2/UART3 . . . . . . . . . 454.6.2Go command via SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 472/70Doc ID 14798 Rev 4UM0560Contents4.6.3Go command via CAN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 494.7Sector codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 504.8Software model (STM8A/L/S . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 564.8.1RAM erase/write routines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 575Error management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 586Programming time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59Appendix A How to upload ROP protected device . . . . . . . . . . . . . . . . . . . . . . . 60A.1Rules for upgrading ROP protected devices. . . . . . . . . . . . . . . . . . . . . . . 60 Appendix B Bootloader entry points . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61Appendix C SPI peripheral timing options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62C.1SPI with busy state checking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62C.2Modified erase/write RAM routines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62 Appendix D PC software support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63Appendix E Bootloader UART limitation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64E.1Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64E.1.1UART automatic baudrate calculation. . . . . . . . . . . . . . . . . . . . . . . . . . . 64E.1.2Description of UART limitation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64E.2Workaround for UART limitation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65 Appendix F Limitations and improvements versus bootloader versions. . . . . 66 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68Doc ID 14798 Rev 43/70List of tables UM0560 List of tablesTable 1.STM8 subfamilies featuring abootloader. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Table 2. STM8 subfamilies without bootloader . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Table3.Bootloader versions for which bootloader activation flowchart isvalid. . . . . . . . . . . . . . . . . 7 Table 4.Initialchecking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Table 5.Serial interfaces associated with STM8devices. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Table 6.Bootloadercommands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 7.Bootloader codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Table 8.Examples ofdelay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 Table9.STM8 sector codes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50 Table 10.Errortable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58 Table ART/LINUART/UART1/UART2/UART3 programmingtimes. . . . . . . . . . . . . . . . . . . . . 59 Table 12.SPI programmingtime . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59 Table 13.CAN programming time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59 Table 14.Bootloader entrypoints. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61 Table15.Description of limitation, improvements and addedfeatures . . . . . . . . . . . . . . . . . . . . . . . 66 Table 16.Document revisionhistory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68 4/70Doc ID 14798 Rev 4UM0560List of figures List of figuresFigure 1.Bootloader activation flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 2.CANframe . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 3.Get command via USART/LINUART/UART1/UART2/UART3 - hostside . . . . . . . . . . . . . 15 Figure 4.Get command viaUSART/LINUART/UART1/UART2/UART3 - device side. . . . . . . . . . . . 16 Figure5.Get command via SPI - host side. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17 Figure 6.Get command via SPI - deviceside . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 7.Get command via CAN - host side. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Figure 8.Get command via CAN - device side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Figure 9.Read memory command via USART/LINUART/UART1/UART2/UART3 - host side. . . . . 21 Figure 10.Read memory command viaUSART/LINUART/UART1/UART2/UART3 - device side . . . 22 Figure 11.Read memory command via SPI - host side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Figure 12.Read memory command via SPI - deviceside. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Figure 13.Read memory command via CAN - host side. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Figure 14.Read memory command via CAN - device side. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Figure 15.Erase memory command via USART/LINUART/UART1/UART2/UART3 - host side. . . . . 28 Figure 16.Erase memory command viaUSART/LINUART/UART1/UART2/UART3 - device side. . . 30 Figure 17.Erase memory command via SPI - host side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Figure 18.Erase memory command via SPI - deviceside . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 Figure 19.Erase memory command via CAN - host side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Figure 20.Erase memory command via CAN - device side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Figure 21.Write memory command via USART/LINUART/UART1/UART2/UART3 - hostside . . . . . 36 Figure 22.Write memory command viaUSART/LINUART/UART1/UART2/UART3 - device side . . . 37 Figure 23.Write memory command via SPI - host side. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 Figure 24.Write memory command via SPI - deviceside. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 Figure 25.Write memory command via CAN - host side. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Figure 26.Write memory command via CAN - device side. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42 Figure 27.Speed command via CAN - hostside. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43 Figure 28.Speed command via CAN - device side. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44 Figure 29.Go command via USART/LINUART/UART1/UART2/UART3 - host side. . . . . . . . . . . . . .45 Figure 30.Go command via USART/LINUART/UART1/UART2/UART3 - device side . . . . . . . . . . . . 46 Figure 31.Go command via SPI - hostside . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47 Figure 32.Go command via SPI - device side. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 Figure 33.Go command via CAN - hostside . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49 Figure 34.Go command via CAN - device side. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49 Figure35.Delay elimination in modified RAMroutines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62 Figure 36."Flash loader demonstrator" software. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63Doc ID 14798 Rev 45/706/70Doc ID 14798 Rev 42 Bootloader introductionThe main task of the bootloader is to download the application program into the internalmemories through the integrated peripherals (UARTs, SPI, or CAN without using the SWIM protocol and dedicated hardware. Data are provided by any device (host which is capable of sending information through one of the above-mentioned serial interfaces.The bootloader permits downloading of application software into the device memories, including RAM, program and data memory, using standard serial interfaces. It is a complementary solution to programming via the SWIM debugging interface.The bootloader code is stored in the internal boot ROM memory. After a reset, thebootloader code checks whether the program memory is virgin or whether a specific option byte is set allowing code modifications.If these conditions are not fulfilled, the bootloader resumes and the user application is started.In case of a successful check the bootloader is executed.When the bootloader procedure starts, the main tasks are:●Polling all supported serial interfaces to check which peripheral is used●Programming code, data, option bytes and/or vector tables at the address(es received from the host.Each STM8 device embeds a specific bootloader code which is common to a whole group of STM8 devices. The correspondence between STM8 groups and STM8 part numbers is given in Table 1. Group names are used all over this user manual.Table 2 gives the list of STM8 devices without embedded bootloader (no ROM bootloader is implemented inside the microcontroller. When using these devices, youhave to write your own bootloader code and save it in the UBC program area (refer to STM8S and STM8A families reference manual for information on the UBC area.Table 1.STM8 subfamilies featuring a bootloaderSTM8 group STM8 part numbersSTM8A/S-128KSTM8AF52xx, STM8AF6269/8x/Ax, STM8AF51xx, STM8AF6169/7x/8x/9x/Ax,STM8S20xxx STM8A/S-32KSTM8AF622x/4x, STM8AF6266/68, STM8AF612x/4x, STM8AF6166/68,STM8S105xxSTM8L-64k STM8L15xx8, STM8L15xR6, STM8L16xx8STM8L-32KSTM8L15xC4, STM8L15xK4, STM8L15xG4,STM8L15xC6, STM8L15xK6, STM8L15xG6(x = 1 or 2STM8L-8KSTM8L15xC2, STM8L15xK2, STM8L15xG2, STM8L15xC3, STM8L15xK3, STM8L15xG3(x = 1 or 2Doc ID 14798 Rev 47/702.1 Bootloader activationThe STM8 hardware reset vector is located at the beginning of the boot ROM(0x006000,while the other interrupt vectors are in the Flash program memory starting at address 0x008004.The device executes the boot ROM (jumps inside the boot ROM area and after checking certain address locations (see Table 4: Initial checking on page 10, it starts to execute the bootloader or the user code defined by the reset vector (0x008000.The bootloader activation flowchart is described in Figure 1: Bootloader activation flowchart . In previous bootloader versions, a return to the “wait for SYNCHR” state (see dashed line in Figure 1 was performed when the “Flash virgin” test was positive. In newer versions, it has been replaced by a software (SW reset to prevent the customer firmware from remaining in a infinite loop (e.g. due to EMC disturbance. This bootloader modification is referred to as "EMC lockup protection" in T able 15. Table 3 lists the bootloader versions for which the dashed line was replaced by a SW reset.The bootloader version number of a given device is obtained by the “Get command” (see Section 4.1: Get command . The bootloader version is represented by a two-digitbinary-coded decimal (BCD number (with a decimal point between the two digits which is coded into one byte in the “Get command” result. For example, 0x21 version byte is bootloader version 2.1.Table 2.STM8 subfamilies without bootloaderSTM8 group STM8 part numbersSTM8A/S-8K STM8Sx03xx STM8L-8KSTM8L101xxTable 3.Bootloader versions for which bootloader activation flowchart is validSTM8 group Bootloader versionSTM8A/S-128K v2.2STM8A/S-32K v1.3STM8L-64K v1.0STM8L-32K v1.2STM8L-8Kv1.01.See Flow chart description on page9 for explanation of points 1 to 8.2.See Table4: Initial checking.3.Dotted routines are loaded in RAM by the host. They are removed by the go command before jumping to the Flash programmemory to execute an application.8/70Doc ID 14798 Rev 4Flow chart description1.Disable all interrupt sources.2. The host can start the bootloader process according to checks shown in Table4 (inkeeping with the content of the first Flash program memory location (0x008000 and “bootloader enable” option bytes. The host checks the following bootloader startconditions:Condition 1: the host checks if the device memory is empty by inspecting the content of address 0x00 8000 (reset vector. If the content is not equal to 0x82 or 0xAC, thedevice is recognized as being empty and the bootloader remains active and waits for host commands without timeouts.Condition 2: the host checks if the bootloader option bytes (two bytes are set to enable the bootloader or not. The bootloader is enabled with a value of 0x55AA and disabled by all other values (see the device datasheets for the bootloader option byte locations.If the option bytes are enabled, the bootloader remains active and waits for hostcommands with a 1-second timeout. If the host does not send a command within this timeout, the bootloader jumps directly to the application user vector (jump to address0x008000.Condition 3: If the option bytes disable the bootloader (by a value different from0x55AA, the bootloader jumps directly to the application user vector (jump to address 0x00 8000.The above checking process is summarized in T able4.3. When readout protection (ROP is active, the Flash program memory is readoutprotected. In this case, the bootloader stops and the user application starts. If ROP is inactive, the bootloader continues to be executed (see Appendix A: How to upload ROP protected device.4. The CAN peripheral can only be used if an external clock (8 MHz, 16 MHz, or 24 MHzis present. It is initialized at 125 kbps. The UARTs and SPI peripherals do not require an external clock.5. Set the high speed internal RC oscillator (HSI to 16 MHz and initialize the UARTsreceiver pins in input pull-up mode in the GPIO registers. Initialize the SPI in slave mode. Then, wait 4 ms for I/O pin voltage level stabilization. It is recommended that the host waits 10 ms from the STM8 reset before sending the SYNCHR byte/message.This is the time needed for bootloader initialization.Doc ID 14798 Rev 49/7010/70Doc ID 14798 Rev 46.Interface polling: The bootloader polls all peripherals waiting for a synchronizationbyte/message (SYNCHR = 0x7F within a timeout of 1 s. If a timeout occurs, either the Flash program memory is virgin in which case it waits for a synchronizationbyte/message in an infinite loop through a software reset, or the Flash programmemory is not virgin and the bootloader re stores the registers’ reset status and jumps to the memory address given by the reset vector (located at 0x008000. For thebootloader versions listed in Table 3, a software reset is generated after a timeout has elapsed, in case the Flash program memory is empty (this is because it is safer to stay in an infinite loop if there is a hardware chip error.Note:When synchronization fails (the bootloader receives a byte/message different to‘SYNCHR’ = 0x7F two different situations can be distinguished according to the peripheral:With the UART peripherals, a device reset or power-down is necessary beforesynchronization can be tried again. Refer to Appendix E: Bootloader UART limitation With the CAN or SPI peripheral, the user can continue to poll the interfaces until a synchronization or a timeout occurs.7.If the synchronization message is received by the UARTs, the bootloader automatically detects the baud rate, initializes the UART and goes to step 8 below. If thesynchronization message is received by the CAN or SPI, the bootloader goes directly to step 8 below.Note: Once one of the available interfaces receives the synchronization message, all others are disabled.8.Waiting for commands: Commands are checked in an infinite loop and executed. To exit from the bootloader, the host has to send a ‘GO’ command. When this is done, the bootloader removes the EM and WM routines from the RAM memory and jumps to the address selected by the host.Note:To be able to write/erase data in Flash and EEPROM the host must write into RAMexecutable routines for writing and erasing. Those routines (*.s19 files are provided with the bootloader. Host must upload those routines at address 0xA0. See section 4.8.1: RAM erase/write routines for more information.Note:After interface initialization, the ROP bit is checked to avoid non-authorized reading of the Flash program memory and data EEPROM.Table 4.Initial checkingChecksProgram memory byte location [0x008000]Bootloader check option bytes[BL_OPT](11.See device datasheet for the [BL_OPT] location in the option byte area memory map.Actual Flash program memory status-> Flash action1st [0x00 8000] <>(0x82 or 0xAC[BL_OPT] = 0x00XXXX Flash program memory virgin.-> jump to bootloader 2nd[0x00 8000] <>(0x82 or 0xAC[BL_OPT] = 0x0055AA Flash program memory already written, bootloader enabled by option bytes.-> jump to bootloader 3rd[0x00 8000] <>(0x82 or 0xAC[BL_OPT] <> 0x0055AAFlash program memory already written,bootloader disabled by option bytes.-> jump to Flash program memory resetUM0560Peripheral settingsDoc ID 14798 Rev 411/703 Peripheral settingsThis section describes the hardware settings of the STM8 communication peripherals:●UARTs/LINUART ●SPI ●CANNote:During bootloading only one peripheral (first addressed is enabled. All others are disabled.3.1 USART/UARTs settingsThis peripheral supports asynchronous serial communication.The USART/UARTs settings are:●Data frame: 1 start bit, 8 data bit, 1 parity bit set to even, 1 stop bit●Baud rate: The baud rate is automatically detected by the bootloader. When the usersends the synchronization byte, 0x7F , the bootloader automatically detects the baud rate and sets the USART/UARTs to the same baud rate. Maximum baud rate = 1 Mbps (115200 baud for STM8L-64K; minimum baud rate = 4800 bps.To perform the automatic speed detection, the RxD line must be stable in the application board (internal pull-up is enabled on the RxD line by the bootloader.3.1.1 LINUART/UARTs in “reply” mode settingsSettings are:●Data frame: 1 start bit, 8 data bit, no parity bit, 1 stop bit●Baud rate: The baud rate is automatically detected by the bootloader. When the user sends the synchronization byte 0x7F , the bootloader automatically detects the baud rate and sets the UARTs to the same baud rate. Maximum baud rate = 550 kbps (115200 baud for STM8L-64K; minimum baud rate = 4800 bps.To perform automatic speed detection, the RxD line must be stable in the application board (internal pull-up is enabled on the RxD line by the bootloader.Table 5.Serial interfaces associated with STM8 devices (11.The above table reflects only current bootloader versions and device states.STM8 groups Serial interfaceSTM8A-128K USART , LINUART (in “reply” mode, CAN STM8A-32K LINUART, SPISTM8S-128K UART1, UAR T3 (in “reply” mode, CAN STM8S-32K UART2 (in “reply” mode, SPI STM8L-8K UART, SPI STM8L-32K UARTSTM8L-64KUART1, UART2, UART3 (in “reply” mode,SPI1, SPI2Peripheral settings UM056012/70Doc ID 14798 Rev 4Reply modeThe host must reply to all the bytes sent from the bootloader. If TxD and RxD lines share the same physical medium (for example, 1-wire communication, then host replies are not necessary since RxD and TxD pins coincide.3.2 SPI settingsThe SPI settings are:●8 data bit, MSB first●Bit rate: S et by the host which acts as a master●Peripheral set in slave mode with software management of NSS●Data polarity : CPOL = 0 (SCK to 0 when idle, CPHA = 0 (the first clock transition is thefirst data capture edge.Note:1Before sending a ‘token’ byte, th e host has to wait for a delay of a specified period of time. If this period is not quantified, it is equal to 6 µs.2The SPI peripheral is accessible via SPI_SCK, SPI_MOSI and SPI_MISO pins.UM0560Peripheral settingsDoc ID 14798 Rev 413/703.3 CAN settingsTo address additional devices on the same bus, the CAN protocol provides a standardidentifier field (11-bit and an optional extended identifier field (18-bit in the frame. Figure 2 shows the CAN frame that uses the standard identifier only.The CAN settings are as follows:●Standard identifier (not extended●Bit rateBy default, it is 125 kbps. The runtime can be changed via the speed command to achieve a maximum bitrate of 1 Mbps.The transmit settings (from the STM8 to the host are:●Tx mailbox0: On●Tx mailbox1 and Tx mailbox2: Off ●Tx identifier: 0x02●Outgoing messages contain 1 data byteThe receive settings (from the host to the STM8 are:●The synchronization byte, 0x7F , is in the RX identifier and not in the data field●The RX identifier depends on the command (0x00, 0x03, 0x11, 0x21, 0x31, 0x43●Error checking: If the error field (bit [6:4] in the CESR register is different from 000b, the message is discarded and a NACK is sent to the host.●In FIFO overrun condition, the message is discarde d and a NACK is sent to the host.●Incoming messages can contain from 1 to 8 data bytes.Note:The CAN peripheral is accessible via CAN_TX and CAN_RX pins.Bootloader command set UM056014/70Doc ID 14798 Rev 44 Bootloader command setThe commands supported by the bootloader are listed in Table 6 below.Table 7.Bootloader codesWhen the bootloader receives a command via the UARTs, CAN or SPI peripherals, the general protocol is as follows:1.The bootloader sends an ACK byte (0x79 to the host and waits for an address and for a checksum byte, both of which are checked when received.2.When the address is valid and the checksum is correct, the bootloader transmits an ACK byte (0x79, otherwise it transmits a NACK byte (0x1F and aborts the command. The bootloader waits for the number of bytes to be transmitted (N bytes and for its complemented byte (checksum. –If the checksum is correct, it then carries out the command, starting from the received address.–If the checksum is incorrect, it sends a NACK (0x1F byte before aborting the command.Table 6.Bootloader commandsCommandCommand codeCommand descriptionGet 0x00Gets the version and the allowed commands supported bythe current version of the bootloaderRead memory 0x11Reads up to 256 bytes of memory starting from an address specified by the hostErase memory0x43Erases from one to all of the Flash program memory/data EEPROM sectorsWrite memory0x31Writes up to 128 bytes to RAM or the Flash programmemory/data EEPROM starting from an address specified by the hostSpeed 0x03Allows the baud rate for CAN runtime to be changed Go0x21。

Content1STM32 – 32-bit microcontroller families (3)STM32 F0 series - ARM Cortex™-M0 Entry-level MCUs (3)STM32 F1 series - ARM Cortex™-M3 Mainstream MCUs (12)STM32 F2 series - ARM Cortex™-M3 High-performance MCUs (17)STM32 F3 series - ARM Cortex™-M4 Mixed-signal MCUswith DSP and FPU (5)STM32 F4 series - ARM Cortex™-M4 High-performance MCUswith DSP and FPU (7)STM32 L1 series - ARM Cortex™-M3 Ultra-low-power MCUs (20)STM32W series - ARM Cortex™-M3 Wireless MCUs (23)STM8 – 8-bit microcontroller families (24)STM8S series – Mainstream MCUs (24)STM8AF series – Mainstream Automotive MCUs (27)STM8AL series – Ultra-low-power Automotive MCUs (29)STM8L series – Ultra-low-power MCUs (30)2STM32 – 32-bit microcontroller families STM32 F0 SERIES - ARM CORTEX™-M0 ENTRY-LEVEL MCUS3STM32 F0 SERIES - ARM CORTEX™-M0 ENTRY-LEVEL MCUSNote:* Available in mass market Week03/201445- Supply voltage 2.0 to 3.6 V for all devices or 1.8 V +/-8% dedicated sales type - WLCSP66 package available in 1.8 V +/-8% dedicated sales type only67891. HS requires an external PHY connected to ULPI interface2. Crypto/hash processor on STM32F417, STM32F415, STM32F437, STM32F4393. Marked in the table (3+2) means 3 USART and 2 UART. All UARTs have LIN master/slave function. All USARTs have IrDA, ISO 7816, modem control and LIN master/slave functions.4. 1.7 V requires external reset circuitry and the device operates in the 0 to 70 °C temperature range1. Marked in the table (3+2) means 3 USART and 2 UART. All UARTs have LIN master/slave function. All USARTs have IrDA, ISO 7816, modem control and LIN master/slave functions.1. HS requires an external PHY connected to ULPI interface2. Crypto/hash processor on STM32F217 and STM32F2153. Marked in the table (3+2) means 3 USART and 2 UART. All UARTs have LIN master/slave function. All USARTs have IrDA, ISO 7816, modem control and LIN master/slave functions.‑ Touch‑sensing FW library available for all STM32L15x and STM32L16x devices ‑ Operating temperature is ‑ 40 to +85 °C for all STM32L1 devicesSTM32W SERIES - ARM CORTEX™-M3 WIRELESS MCUS1. On demand onlySTM8AL SERIES – ULTRA-LOW-POWER AUTOMOTIVE MCUS‑ All STM8AL part numbers have DMA with 4 channels except STM8AL301. Up to 2 Kbytes of EEPROMADC :Analog-to-digital converter ART :Auto-reload timerATAPI :AT attachment packet interface AWU :Auto wake-up from haltBLPD :Byte level protocol decoder BOD :Brown-out detectorCAN :Controller area networkCAPCOM :Capture compareCSS :Clock security systemDALI :Digital addressable lighting interface DDC :Data display channelDiSEqC :Digital satellite equipment control DMA :Direct memory accessDSC :Dual supply controlDTC :Data transfer coprocessor ETM :Embedded trace macrocell EMI :External memory interface HDLC :High-level data link control IAP :In-application programming IC/OC :Input capture/output compare ICP :programmingIR :InfraredIrDA :Infrared data associationISP :In-situ programmingI²C :Inter-integrated circuitAbbreviations and packages LCD :Liquid crystal display LIN :Local interconnect network LVD :Low voltage detection MAC :Multiply accumulator MC :Motor control MFT :Multifunction timer MMC :MultiMediaCard NMI :Non-maskable interrupt OSG :Oscillator safeguard PCA :Programmable counter array PDR :Power-down reset PHW :Programmable halt wake-up PEC :Peripheral event controller PLD :Programmable logic device PLL :Phase locked loop POR :Power-on reset PVD :Programmable voltage detector PVR :Programmable voltage regulator PWM :Pulse width modulation ROP :Readout protection RTC :Real-time clock timer SC :Smartcard SCI :Serial communication interface SCR :Smartcard reader SDIO :Secure digital input output ABBREVIATIONSPACKAGES DIP :Dual in-line package LCC :Leaded chip carrier PDIP Shrink :Shrink Plastic Dual In-line Package PQFP :SO :Small outline LQFP :PBGA :Plastic ball grid array DFN :QFN :SPI :Serial peripheral interface SSC :Single-cycle switching support SSP :Synchronous serial port TBU :Time base unit TLI :Top level interrupt UART :Universal asynchronous receiver transmitter USART :Universal sync/async receiver transmitter USB :Universal Serial Bus WDG :Watchdog timer WWDG :Window watchdog timer© STMicroelectronics - November 2013 - Printed in China - All rights reserved。

STM8L微控制器中⽂参考⼿册本参考⼿册的⽬标应⽤程序开发⼈员。

它提供了完整的信息如何使⽤stm8l05xx,stm8l15xx和stm8l16xx 微控制器的存储器和外围设备。

该stm8l05xx / stm8l15xx / stm8l16xx是⼀个家庭的不同存储密度的微控制器和外围设备。

这些产品是专为超低功耗应⽤。

可⽤的外设的完整列表,请参阅产品数据表。

订购信息,引脚说明,机械和电⽓设备的特点,请参阅产品数据表。

关于STM8 SWIM通信协议信息和调试模块,请参阅⽤户⼿册(um0470)。

在STM8的核⼼信息,请参阅STM8的CPU编程⼿册(pm0044)。

关于编程,擦除和保护的内部快闪记忆体,请参阅STM8L 闪存编程⼿册(pm0054)。

1 中央处理单元(CPU)。

30。

1.1 引⾔301.2 CPU的寄存器。

30。

1.2.1 描述CPU寄存器。

..。

301.2.2 STM8 CPU寄存器图。

..。

341.3 全球配置寄存器(cfg_gcr)。

34。

1.3.1 激活⽔平。

..。

341.3.2 游泳禁⽤。

..。

351.3.3 描述全局配置寄存器(cfg_gcr)。

..。

35 1.3.4 全局配置寄存器图及复位值。

..。

352 启动ROM . . . 363程序存储器和数据存储器。

37。

3.1引⾔373.2术语。

37。

3.3个主要的快闪存储器的特点。

38。

3.4记忆的组织。

39。

3.4.1低密度设备的存储器组织。

393.4.2介质密度的装置记忆的组织。

..。

40 3.4.3介质+密度装置记忆的组织。

..。

41 3.4.4⾼密度存储器组织。

..。

423.4.5专有代码区(译)。

433.4.6⽤户区(UBC)。

433.4.7数据的EEPROM(数据)。

..。

463.4.8主程序区。

463.4.9选项字节。

..。

463.5内存保护。

47。

3.5.1读出保护。

473.5.2内存访问安全系统(质量)。

本参考手册的目标应用程序开发人员。

它提供了完整的信息如何使用stm8l05xx,stm8l15xx和stm8l16xx微控制器的存储器和外围设备。

该stm8l05xx / stm8l15xx / stm8l16xx是一个家庭的不同存储密度的微控制器和外围设备。

这些产品是专为超低功耗应用。

可用的外设的完整列表,请参阅产品数据表。

订购信息,引脚说明,机械和电气设备的特点,请参阅产品数据表。

关于STM8 SWIM通信协议信息和调试模块,请参阅用户手册(um0470)。

在STM8的核心信息,请参阅STM8的CPU编程手册(pm0044)。

关于编程,擦除和保护的内部快闪记忆体,请参阅STM8L闪存编程手册(pm0054)。

1 中央处理单元(CPU)。

30。

1.1 引言301.2 CPU的寄存器。

30。

1.2.1 描述CPU寄存器。

..。

301.2.2 STM8 CPU寄存器图。

..。

341.3 全球配置寄存器(cfg_gcr)。

34。

1.3.1 激活水平。

..。

341.3.2 游泳禁用。

..。

351.3.3 描述全局配置寄存器(cfg_gcr)。

..。

351.3.4 全局配置寄存器图及复位值。

..。

352 启动ROM . . . 363程序存储器和数据存储器。

37。

3.1引言373.2术语。

37。

3.3个主要的快闪存储器的特点。

38。

3.4记忆的组织。

39。

3.4.1低密度设备的存储器组织。

393.4.2介质密度的装置记忆的组织。

..。

403.4.3介质+密度装置记忆的组织。

..。

413.4.4高密度存储器组织。

..。

423.4.5专有代码区(译)。

433.4.6用户区(UBC)。

433.4.7数据的EEPROM(数据)。

..。

463.4.8主程序区。

463.4.9选项字节。

..。

463.5内存保护。

47。

3.5.1读出保护。

473.5.2内存访问安全系统(质量)。

473.5.3使写访问选项字节。

493.6内存编程493.6.1同时读写(读写网)。

STM8和STM32之间有些什么差异?STM8和STM32先学谁?

有朋友问:我学习过51,接下来我是先学习STM8,还是STM32呢?

1写在前面

想要明白这个问题,其实就需要明白STM8和STM32之间有些什么差异,包括MCU基本信息、开发难度、以及应用场景等。

站在客观的角度来说,STM8比STM32学起来更容易,C语言功底还不错的朋友,直接上STM32也不是问题。

从大的方向来说,当你对一种MCU掌握的比较透彻,再学其他型号、其他厂商的MCU,相对来说,上手都要容易的多。

针对本文问题,我下面讲述一下相关知识。

2

STM8和STM32内核差异

STM8 CPU 是一种专有架构,它保持了以前的ST7 内核的传统,同时在8 位CPU 效率和代码密度方面实现了突破。

STM32 围绕行业标准ARM® Cortex-M 32 位内核构建,并受益于与ARM 处理器有关的开发工具和软件解决方案的完整生态产业环境。

尽管它们被认为是两种完全不同的处理器,但它们在架构方面实际有许多相似之处。

下面对比STM8S 和STM32F1 (Cortex-M3)这两种内核差异:

两种内核均基于哈佛架构,它们采用 3 级流水线执行,可将执行时间降至最低,对于STM8S,时钟速度高达24 MHz,对于STM32F1系列,时钟速度高达72 MHz。

在代码密度方面,它们均有优异的表现,这归功于STM8S 系列的8 位 CISC 指令集以及STM32F1系列的Cortex 内核引入的16 位 Thumb-2 模式。

3

片上外设差异。