深入了解HCS08的内部时钟源 (ICS)

- 格式:pdf

- 大小:2.23 MB

- 文档页数:12

8位HCS08中央处理单元(CPU)•20-MHz的HCS08 CPU(中央处理单元)•HC08指令集,增加了BGND指令•背景调试系统•断点能力,使单一的断点在电路调试过程中设置(加上两个在片上调试模块断点)•包含两个比较器和九种调试模块触发模式。

八级深度的FIFO存储变化的流地址和事件数据调试模块支持标记和强制断点•支持多达32个中断/复位源内存选项•闪存读取/编程/擦除在整个工作电压和温度•MC9S08QG8 - 8 KB闪存,512字节RAMMC9S08QG4 - 4字节的闪存,256字节RAM省电模式•等待加三站时钟源选项•ICS -含内部时钟源模块锁频环(FLL)控制由内部或外部基准,精密的内部微调引用允许0.2%的分辨率和2%的偏差在温度和电压;支持总线从1 MHz到10 MHz的频率•XOSC -低功耗振荡器模块软件选择晶体或陶瓷谐振器范围,31.25 kHz到38.4 kHz或1 MHz到16 MHz,并支持外部时钟源输入最多20 MHz的系统保护•看门狗计算机运行正常(COP)复位与选项可从专用1-kHz内部运行时钟源或总线时钟•低电压检测复位或中断•非法操作码检测复位•非法地址检测复位•Flash块保护外设•ADC - 8通道,10位模拟至数字转换器,具有自动比较功能,异步时钟源,温度传感器,并内部带隙参考通道; ADC是使用RTI计数器硬件触发的•ACMP -与选项模拟比较器模块要比较的内部参考;输出可可选路由到TPM模块•SCI -串行通信接口模块与选项的13位中断功能•SPI -串行外设接口模块•IIC -内部集成电路总线模块•TPM - 2通道定时器/脉宽调制器; 每个通道可用于输入捕捉,输出比较,缓冲边沿对齐PWM,或缓冲中心对齐PWM•MTIM - 8位模数定时器8位模块预分频器•KBI - 8引脚键盘中断与软件模块边缘或边缘/电平模式可选择极性输入/输出•12个通用输入/输出(I / O)引脚,仅输入引脚和一个只输出引脚,输出每个10毫安60 mA最大的包•作为使用时的端口上通过软件选择上拉输入•软件可选择的转换率控制和驱动作为输出时强度上的端口•RESET和IRQ引脚,以减少内部上拉客户系统成本开发支持•单线背景调试接口•片上,在电路内仿真(ICE)的实时总线捕获封装选项•24引脚四方扁平无引线(QFN)封装•16引脚塑料双列直插式封装(PDIP) - 仅MC9S08QG8•16引脚四方扁平无引线(QFN)封装•16引脚超薄紧缩小型封装(TSSOP)•8脚双列扁平无引线(DFN)封装•8引脚PDIP - 只MC9S08QG4•8引脚窄体小外形集成电路。

freescale hcs08单片机原理及应用单片机作为计算机科学领域重要的嵌入式系统组成部分,广泛应用于各个领域,其中Freescale HCS08单片机以其高性能、低功耗和易于开发等特点备受关注。

本文将介绍Freescale HCS08单片机的原理以及其应用。

一、Freescale HCS08单片机原理Freescale HCS08单片机采用基于哈佛结构的8位微处理器单元,具有高速运算能力和丰富的外设接口,能够满足不同领域的需求。

其核心原理包括指令集、片内存储器、时钟系统和外设接口等。

1. 指令集Freescale HCS08单片机的指令集丰富多样,包括数据传送、算术逻辑、位操作、条件转移和中断等多种类型的指令。

指令执行的速度快,能够满足实时性要求高的应用场景。

2. 片内存储器HCS08单片机内部集成了存储器单元,包括程序存储器ROM和数据存储器RAM。

ROM用于存储程序和常量,RAM用于存储变量和中间结果。

片内存储器的设计使得单片机具有较高的存储容量和读写速度。

3. 时钟系统Freescale HCS08单片机的时钟系统采用晶体振荡器作为基准时钟源,通过分频和锁相环等技术生成系统时钟。

时钟系统的设计能够提供稳定的时钟信号,确保单片机的正常运行。

4. 外设接口HCS08单片机提供了多种外设接口,包括通用输入输出引脚、定时器/计数器、串行通信接口等。

通过这些外设接口,单片机可以与外部设备进行数据交换和通信,实现各种功能。

二、Freescale HCS08单片机应用Freescale HCS08单片机在各个领域都有广泛的应用,如工业控制、汽车电子、家电控制、医疗设备等。

以下将介绍几个常见的应用案例。

1. 工业控制Freescale HCS08单片机在工业控制中扮演重要角色。

它能够实现对温度、压力、流量等参数的监测和控制,实现自动化生产线的稳定运行。

同时,单片机的高可靠性和抗干扰能力,使得它能够适应各种恶劣的工业环境。

Freescale HCS08单片机原理及应用报告实验项目名称 Freescale HCS08单片机IO编程应用姓名章鱼哥一.实验目标:1.理解08系列MCU的I/O模块端口模块的原理;2.了解I/O端口寄存器的功能;3.掌握I/O端口应用设计(硬件设计和软件编程);4.初步认识“对MCU外部管脚/内部模块的控制正是通过Regs的控制来实现”二.实验内容:点亮实验板上4个7段LED数码管:在4个数码管上同时显示0123–把延时缩短为0.1ms、0.01ms现象如何?改大为5ms、10ms、50ms又会出现什么现象?三.实验原理分析:为了在4个数码管同时显示“0123”,需要采用动态显示方式,即瞬间只点亮一个数码管,然后延时一段时间,再瞬间点亮下一个数码管,如此不停的循环显示,利用人眼视觉暂留效应,就如同4个数码管同时显示一样。

每个数码管依次被点亮约1ms,4个数码管点亮一遍约4ms,也就是每个数码管前后两次点亮的时间间隔约为4ms,或者说数码管的刷新频率约为250Hz,也就是4个数码管每秒显示的帧数是250帧,人眼既不会感觉到显示闪烁,也会觉得4个数码管是同时显示。

四.具体代码实现:INCLUDE MC9S08AW60.inc ; 包含头文件ORG $0070SEG DS 1Num DS.b 1Count DS.b 1CNT DS.b 1ORG $1860LED_Table: ; 公阳极LED码表,一定要定位到Flash区DC.B $C0, $F9, $A4, $B0 ; 0-3的字形码DC.B $99, $92, $82, $F8 ; 4-7的字形码;延时模块Re_cycle:MOV #70T,Num ; 4个总线周期DBNZ Num,* ; 7个总线周期RTS ; 6个总线周期; 完成recycle所花费的时间4+7*70+6=500 个总线周期Delay_1ms:MOV #7T, Count ; 4个总线周期循环调用recycle 78次Re_Call: BSR Re_cycle ; 5个总线周期DBNZ Count,Re_Call ; 7个总线周期MOV #07T,Count ; 4个总线周期; 后三条指令花费4+7*7+6=59 个总线周期DBNZ Count,* ; 7个总线周期RTS ; 6个总线周期IO_Init:MOV #$0F, PTCD ; 初始化输出端口的数据寄存器,习惯养成LDA #%00001111STA PTBDDSTA PTDDDSTA PTCDDSTA PTBDSSTA PTDDSSTA PTCDSRTSMain: CLRX ; 00H→XCLRH ; 00H→HCLRA ; 00H→ASTA $1802 ; 00h→SOPT,Disable COPJSR IO_Init ; 对PTA,PTB端口初始化MOV #$FE, SEG ; $70存储单元保存位选信息Again: LDA LED_Table, X ; 查表,读取0~3字形码sta PTBDnsasta PTDD ; 送出字形码MOV SEG, PTCD ; 点亮$70中为0位对应的数码管JSR Delay_1ms ; 持续亮1msMOV #$FF, PTCD; 灭所有数码管,避免余辉且为下一位显示做准备LDA SEGSEC ; C=1ROLASTA SEG ; 位选指向前一个数码管INCXCPX #$4 ; 是否显示完一遍BNE Next_DisCLRXMOV #$FE,SEG ; 显示完一遍则X清零Next_Dis: JMP Again ; 死循环ORG $FFFEDC.W Main ; 复位向量五.实验结果分析:当延时足够小时,因为视觉暂留,0-3同时显示,当增大延时,4个数字开始出现跑马灯的效果。

Nicrosystem NSS08Kit-R1开发板教程-------SCI教程作者bluedream审核bluehacker <QQ: 282074921> /bluehacker版本V 1.0日期2009年12月10日版权说明本教程以Nicrosystem开发的NSS08Kit-R1型低成本飞思卡尔s08单片机开发板为平台,但相关内容应该适用于其他公司开发的飞思卡尔S08开发板,甚至对其他非飞思卡尔MCU也有借鉴作用。

我们通过网络免费提供此教程电子版本,不收取任何费用,您可以自由下载传播,但请您不要更改本教程中的任何文字、图片、表格;更不得以任何形式声称拥有本教程的版权,侵占作者的劳动成果。

本教程可能有描述不当或错误之处,欢迎你指正,但作者和作者所在公司单位不对可能的错误负任何责任。

备注如果你发现本教程的问题,欢迎您通过nicrosystem@与我们联系。

也欢迎你关注我们的产品和在电子论坛上的活动作者的博客:/bluehackerNicrosystem “我们的freescale”专栏:/forum-100-1.htmlNicrosystem 定期在与非网社区开展系列针对飞思卡尔处理器的diy活动和助学活动:Nicrosystem EDN“我们的freescale”小组:/2460/淘宝:一. 串行通信基础串行通信是MCU与外界交换信息的一种基本通信方式。

它是采用一根或很少几根传输线作为通信连接线,把一组二进制数逐位、顺序、分时地进行传输。

串行通信必须遵守严格的硬件规格和软件通信协议才可以用于传输数据。

通信协议约定的内容包括数据格式、同步方式、传输速率、校验方式等。

本教程首先介绍串行通信的一些基本概念和协议。

(一)串行通信基本概念串行通信的概念涉及通信方式、波特率、奇偶校验和传输方式等。

1.串行通信方式依发送与接收设备时钟的配置情况串行通信可以分为异步通信和同步通信。

同步通信通过发送一个时钟信号,使接收器与每位时间同步;异步通信使用开始—停止(start-stop)协议,使接收器与每个字符帧的开始时刻同步。

HCS08系列微控制器参考手册第一册苏州大学飞思卡尔嵌入式系统研发中心翻译 2009年11月目录第一章通用信息与结构框图 (1)1.1HCS08系列微控制器介绍 (1)1.2HCS08CPU编程模型 (2)1.3外设模块 (2)1.4MC9S08GB60的特点 (3)1.4.1 HCS08系列的共性 (3)1.4.2 MC9S08GB60的特点 (3)1.5MC9S08GB60的结构框图 (4)第二章引脚及其连接 (5)2.1简介 (5)2.2推荐的系统连接 (5)2.2.1 电源 (7)2.2.2 MC9S08GB60振荡器 (7)2.2.3 复位 (8)2.2.4 背景/模式选择(BKGD/MS) (8)2.2.5 通用I/O及外设端口 (8)第三章工作模式 (10)3.1简介 (10)3.2特征 (10)3.3运行模式 (10)3.4背景调试模式 (11)3.5等待模式 (12)3.6停止模式 (12)3.6.1 Stop1模式 (13)3.6.2 Stop2模式 (13)3.6.3 Stop3模式 (14)3.6.4 停止模式下激活BDM使能 (14)3.6.5 设置OSCSTEN位 (15)3.6.6 停止模式下LVD使能 (15)3.6.7 停止模式下的片上外设模块 (15)3.6.8 系统选择寄存器(SOPT) (17)3.6.9 系统电源管理状态和控制寄存器1(SPMSC1) (18)3.6.10 系统电源管理状态和控制寄存器2(SPMSC2) (19)第四章片上存储器 (21)4.1简介 (21)4.2HCS08核定义的存储器组织 (21)4.2.1 HCS08存储器组织 (21)4.2.2 MC9S08GB60存储映像 (22)4.2.3 复位和中断向量表 (23)4.3寄存器地址和位分配 (24)4.4RAM (29)4.560K字节的FLASH (29)4.5.1 特征 (30)4.5.2 写入、擦除和空白检测命令 (30)4.5.3 命令时间和突发模式写入 (32)4.5.3.1 行和FLASH的组织结构 (32)4.5.3.2 程序命令时序 (33)4.5.4 访问错误 (34)4.5.5 向量重定向 (34)4.5.6 FLASH块保护(MC9S08GB60) (34)4.6MC9S08GB60的安全性 (35)4.7MC9S08GB60的FLASH寄存器和控制位 (36)4.7.1 FLASH时钟分频寄存器(FCDIV) (36)4.7.2 FLASH选项寄存器(FOPT和NVOPT) (37)4.7.3 FLASH配置寄存器(FCNFG) (38)4.7.4 FLASH保护寄存器(FPROT和NVPROT) (38)4.7.5 FLASH状态寄存器(FSTAT) (39)4.7.6 FLASH命令寄存器(FCMD) (40)4.8FLASH存储器应用实例 (41)4.8.1 FLASH模块时钟的初始化 (41)4.8.2 擦除FLASH的一页(512字节) (42)4.8.3 DoOnStack子程序 (43)4.8.4 SpSub子程序 (45)4.8.5 FLASH的字节编程 (46)第五章复位和中断 (47)5.1简介 (47)5.2MC9S08GB60复位和中断的特征 (47)5.4计算机正常操作监控模块(COP)看门狗 (48)5.5中断 (48)5.5.1 中断堆栈结构 (49)5.5.2 外部中断请求(IRQ)引脚 (50)5.5.2.1 引脚配置选项 (50)5.5.2.2 边沿/电平触发 (50)5.5.3 中断向量、中断源和局部屏蔽 (51)5.6低电压检测系统(LVD) (52)5.6.1 上电复位操作 (52)5.6.2 LVD复位操作 (52)5.6.3 LVD中断操作 (53)5.6.4 低电压警告(LVW) (53)5.7实时中断(RTI) (53)5.8复位、中断以及系统控制寄存器和控制位 (53)5.8.1 中断请求状态和控制寄存器(IRQSC) (54)5.8.2 系统复位状态寄存器(SRS) (55)5.8.3 系统背景调试强制复位寄存器(SBDFR) (56)5.8.4 系统选项寄存器(SOPT) (56)5.8.5 系统设备识别寄存器(SDIDH、SDIDL) (57)5.8.6 系统实时中断状态和控制寄存器(SRTISC) (57)5.8.7 系统电源管理状态控制寄存器1(SPMSC1) (58)5.8.8 系统电源管理状态和控制寄存器2(SPMSC2) (59)第六章中央处理单元 (61)6.1简介 (61)6.2编程结构和CPU寄存器 (61)6.2.1 累加器(A) (62)6.2.2 变址寄存器(H:X) (63)6.2.3 堆栈指针(SP) (64)6.2.4 程序计数器(PC) (66)6.2.5 条件码寄存器(CCR) (66)6.3寻址方式 (70)6.3.1 隐含寻址方式(INH) (71)6.3.2 相对寻址方式(REL) (71)6.3.3 立即寻址方式(IMM) (72)6.3.4 直接寻址方式(DIR) (72)6.3.5 扩展寻址方式(EXT) (72)6.3.6.1 无偏移量变址方式(IX) (73)6.3.6.2 无偏移量变址、变址加1寻址方式(IX+) (73)6.3.6.3 8位偏移量变址方式(IX1) (73)6.3.6.4 8位偏移量变址、变址加1寻址方式(IX1+) (73)6.3.6.5 16位偏移量变址方式(IX2) (73)6.3.6.6 8位偏移量堆栈寻址方式(SP1) (74)6.3.6.7 16位偏移量堆栈寻址方式(SP2) (74)6.4特殊操作 (75)6.4.1 复位序列 (75)6.4.2 中断 (76)6.4.3 等待模式 (76)6.4.4 停止模式 (76)6.4.5 背景模式 (77)6.4.6 总线周期的用户观点 (77)6.5通过指令类别进行指令集描述 (78)6.5.1 数据传送指令 (78)6.5.1.1 加载与存储 (78)6.5.1.2 位的置位与清零 (81)6.5.1.3 存储器到存储器的传送 (82)6.5.1.4 寄存器传输和半字节交换 (82)6.5.2 算术运算指令 (83)6.5.2.1 加、减、乘和除指令 (83)6.5.2.2 加一、减一、清零和求补 (88)6.5.2.3 比较和测试 (88)6.5.2.4 BCD的计算 (88)6.5.3 逻辑操作指令 (89)6.5.3.1 与、或、异或与求补 (90)6.5.3.2 位测试指令 (91)6.5.4 移位类指令 (91)6.5.5 跳转、转移和循环控制指令 (93)6.5.5.1 无条件跳转和转移指令 (94)6.5.5.2 简单转移 (95)6.5.5.3 有符号转移 (95)6.5.5.4 无符号转移 (95)6.5.5.5 位条件转移 (96)6.5.5.6 循环控制 (96)6.5.6 相关堆栈指令 (97)6.6指令简表 (102)6.7汇编语言指南 (114)6.7.1 列表行 (115)6.7.2 汇编指令 (116)6.7.2.1 BASE——设定编译器的缺省数进制 (116)6.7.2.2 INCLUDE——指定附加源文件 (116)6.7.2.3 NOLIST/LIST——关闭或打开程序列表 (116)6.7.2.4 ORG——设置程序的起始位置 (117)6.7.2.5 EQU——把一个标号和一个数值相关联 (118)6.7.2.6 dc.b——定义存储器中字节化常量 (119)6.7.2.7 dc.w——在存储器中定义16位(字)常量 (119)6.7.2.8 ds.b——定义存储(保留)内存变量字节 (120)6.7.3 标号 (121)6.7.4 表达式 (122)6.7.5 通用文件协议 (123)6.7.6 目标代码(S19)文件 (125)第七章开发支持 (129)7.1介绍 (129)7.2特点 (130)7.3背景调试控制器(BDC) (130)7.3.1 BKGD引脚描述 (131)7.3.2 通信细节 (132)7.3.2.1 BDC通信速率考虑事项 (132)7.3.2.2 位时序细节 (133)7.3.3 BDC寄存器和控制位 (135)7.3.3.1 BDC状态和控制寄存器 (135)7.3.3.2 BDC断点匹配寄存器 (137)7.3.4 BDC命令 (137)7.3.4.1 SYNC——要求时序参考脉冲 (138)7.3.4.2 ACK_ENABLE (139)7.3.4.3 ACK_DISABLE (139)7.3.4.4 BACKGROUND (139)7.3.4.5 READ_STATUS (140)7.3.4.6 WRITE_CONTROL (140)7.3.4.7 READ_BYTE (141)7.3.4.8 READ_BYTE_WS (142)7.3.4.10 WRITE_BYTE (143)7.3.4.11 WRITE_BYTE_WS (143)7.3.4.12 READ_BKPT (144)7.3.4.13 WRITE_BKPT (144)7.3.4.14 GO (144)7.3.4.15 TRACE1 (145)7.3.4.16 TAGGO (145)7.3.4.17 READ_A (145)7.3.4.18 READ_CCR (145)7.3.4.19 READ_PC (146)7.3.4.20 READ_HX (146)7.3.4.21 READ_SP (147)7.3.4.22 READ_NEXT (147)7.3.4.23 READ_NEXT_WS (148)7.3.4.24 WRITE_A (148)7.3.4.25 WRITE_CCR (148)7.3.4.26 WRITE_PC (149)7.3.4.27 WRITE_HX (149)7.3.4.28 WRITE_SP (149)7.3.4.29 WRITE_NEXT (149)7.3.4.30 WRITE_ NEXT_WS (150)7.3.5 串行接口硬件握手协议 (150)7.3.6 取消握手协议 (152)7.3.7 BDC硬件断点 (155)7.3.8 与M68HC12BDM的不同之处 (155)7.3.8.1 8位体系结构 (156)7.3.8.2 命令格式 (156)7.3.8.3 状态位的读写 (156)7.3.8.4 BDM与停止和等待模式 (157)7.3.8.5 SYNC指令 (157)7.3.8.6 硬件断点 (157)7.4标识部分和BDC强制复位 (158)7.4.1 系统设备识别寄存器(SDIDH:SDIDL) (158)7.4.2 系统背景调试强制复位寄存器 (158)7.5片上调试系统(DBG) (159)7.5.1 比较器A和B (159)7.5.2总线信息捕捉和FIFO操作 (160)7.5.4 标记与强制断点和触发器 (161)7.5.5 CPU断点请求 (162)7.5.6 触发模式 (162)7.5.6.1 单独A触发模式 (163)7.5.6.2 A或B触发模式 (163)7.5.6.3 A然后B触发模式 (163)7.5.6.4 事件B触发模式(存储数据) (163)7.5.6.5 A然后事件B触发模式(存储数据) (163)7.5.6.6 A和B数据触发(全模式) (164)7.5.6.7 A与非B数据触发(全模式) (164)7.5.6.8 触发范围内:A≤地址≤B (164)7.5.6.9 触发范围外:地址<A 或者地址>B (164)7.5.7 DBG寄存器和控制位 (165)7.5.7.1 调试比较器A的高地址页寄存器(DBGCAH) (165)7.5.7.2 调试比较器A的低位寄存器(DBGCAL) (165)7.5.7.3 调试比较器B的高地址页寄存器(DBGCAH) (165)7.5.7.4 调试比较器B的低位寄存器(DBGCAL) (165)7.5.7.5 调试FIFO高地址页寄存器(DBGFH) (165)7.5.7.6 调试FIFO低位寄存器(DBGFL) (165)7.5.7.7 调试控制寄存器(DBGC) (166)7.5.7.8 调试触发寄存器(DBGT) (167)7.5.7.9 调试状态寄存器(DBGS) (168)7.5.8 应用信息与举例 (169)7.5.8.1 定向的调试器例子 (171)7.5.8.2 例1:终止对地址A的处理 (171)7.5.8.3 例2:终止对地址A指令的处理 (172)7.5.8.4 例3:终止在地址A或B上的指令处理 (172)7.5.8.5 例4:开始跟踪在地址A的指令 (173)7.5.8.6 例5:A到B顺序后停止的尾部跟踪 (173)7.5.8.7 例6:起始跟踪数据B写入地址A (174)7.5.8.8 例7:从地址B中读取被捕获的首八位数据 (174)7.5.8.9 例8:捕获在读地址A后写入到地址B的值 (175)7.5.8.10 例9:在一个例程中触发所有的执行命令 (175)7.5.8.11 例10:通过触发来试图处理外部FLASH (176)7.5.9 硬件断点和ROM修补 (176)附录A 指令集详述 (177)A.2命名规则 (177)A.3规范定义 (180)A.4指令集 (180)ADC Add with Carry(带进位位加) (180)ADD Add without Carry(无进位位加) (181)AIS Add Immediate Value to Stack Pointer(立即数加到SP) (182)AIX Add Immediate Value to Index Register(立即数加到HX) (182)AND Logical AND(逻辑与) (183)ASL Arithmetic Shift Left(算术左移) (184)ASR Arithmetic Shift Right(算术右移) (184)BCC Branch if Carry Bit Clear(C为0则转移) (185)BCLR n Clear Bit n in Memory(内存单元n位清零) (185)BCS Branch if Carry Bit Set(C为1则转移) (186)BEQ Branch if Equal(等于则转移) (187)BGE Branch if Greater Than or Equal To(大于或等于则转移) (187)BGND Background(进入背景调试模式) (188)BGT Branch if Greater Than(大于则转移) (188)BHCC Branch if Half Carry Bit Clear(H为0则转移) (189)BHCS Branch if Half Carry Bit Set(H为1则转移) (189)BHI Branch if Higher(大于则转移) (190)BHS Branch if Higher or Same(大于或等于则转移) (191)BIH Branch if IRQ Pin High(引脚IRQ为1则转移) (191)BIL Branch if IRQ Pin Low(引脚IRQ为0则转移) (192)BIT Bit Test(位测试) (192)BLE Branch if Less Than or Equal To(小于或等于则转移) (193)BLO Branch if Lower(小于则转移) (193)BLS Branch if Lower or Same(小于或等于则转移) (194)BLT Branch if Less Than(小于则转移) (195)BMC Branch if Interrupt Mask Clear(I为0则转移) (195)BMI Branch if Minus(结果为负则转移) (196)BMS Branch if Interrupt Mask Set(I为1则转移) (196)BNE Branch if Not Equal(不等于则转移) (197)BPL Branch if Plus(结果为正则转移) (197)BRA Branch Always(无条件短转移) (198)BRCLR n Branch if Bit n in Memory Clear(M位n为0则转移) (199)BRN Branch Never(三个总线周期的空操作) (200)BRSET n Branch if Bit n in Memory Set(M位n为1则转移) (200)BSET n Set Bit n in Memory(M位n置1) (201)BSR Branch to Subroutine(转移到子程序) (201)CBEQ Compare and Branch if Equal(比较,等于则转移) (202)CLC Clear Carry Bit(进位位C清零) (203)CLI Clear Interrupt Mask Bit(中断屏蔽位I清零) (203)CLR Clear(清零) (204)CMP Compare Accumulator with Memory(A与M比较) (204)COM Complement(按位取反) (205)CPHX Compare Index Register with Memory(HX与M比较) (206)CPX Compare X with Memory(X与M比较) (207)DAA Decimal Adjust Accumulator(A十进制调整) (208)DBNZ Decrement and Branch if Not Zero(减1不为0则转移) (209)DEC Decrement(自减1) (209)DIV Divide(无符号除法) (210)EOR Exclusive-OR Memory with Accumulator(M与A异或) (211)INC Increment(自加1) (211)JMP Jump(无条件跳转) (212)JSR Jump to Subroutine(跳转到子程序) (213)LDA Load Accumulator form Memory(取M内容到A) (213)LDHX Load Index Register form Memory(取M内容到HX) (214)LDX Load X from Memory(取M内容到X) (215)LSL Logical Shift Left(逻辑左移) (215)LSR Logical Shift Right(逻辑右移) (216)MOV Move(M单元间数据传送) (217)MUL Unsigned Multiply(无符号数乘法) (218)NEG Negate(Two’s Complement) (求补) (218)NOP No Operation(空操作) (219)NSA Nibble Swap Accumulator(A的高低4位对调) (219)ORA Inclusive-OR Accumulator and Memory(逻辑或) (220)PSHA Push Accumulator onto Stack(A进栈) (220)PSHH Push H onto Stack(H进栈) (221)PSHX Push X onto Stack(X进栈) (221)PULA Pull Accumulator from Stack(A出栈) (222)PULH Pull H from Stack(H出栈) (222)PULX Pull X from Stack(X出栈) (223)ROL Rotate Left through Carry(带进位位的循环左移) (223)ROR Rotate Right through Carry(带进位位的循环右移) (224)RSP Reset Stack Pointer(堆栈指针置$FF) (224)RTI Return from interrupt(中断返回) (225)RTS Return from Subroutine(子程序返回) (226)SBC Subtract with Carry(带借位减法) (226)SEC Set Carry Bit(进位位置位) (227)SEI Set Interrupt Mask Bit(中断屏蔽位置位) (227)STA Store Accumulator in Memory(A存入M) (228)STHX Store Index Register(HX存入M) (229)STOP Enable IRQ Pin, Stop Processing(停机) (229)STX Store X in Memory(X存入M) (230)SUB Subtract(无借位减法) (231)SWI Software Interrupt(软件中断) (231)TAP Transfer Accumulator to Processor Status Byte(写CCR) (232)TAX Transfer Accumulator to X(A复制到X) (233)TPA Transfer Processor Status Byte to Accumulator(读CCR) (233)TST Test for Negative or Zero(小于或等于0测试) (234)TSX Transfer Stack Pointer to index Register(复制SP到HX) (235)TXA Transfer X to Accumulator(复制X到A) (235)TXS Transfer Index Register Low to Stack Pointer(HX-1写入SP) (235)WAIT Enable Interrupts; Stop Processor(待机) (236)附录B 通用文件规范 (237)B.1引言 (237)B.2存储映射区域划分 (238)B.3中断向量定义 (238)B.4位定义的两种方式 (239)B.5MC9S08GB60完整的通用文件 (240)第一章通用信息与结构框图1.1 HCS08系列微控制器介绍新型的FreescaleHCS08系列微控制器,尽管包含新指令,可以执行快速调试和开发功能,但仍然和旧的M68HC08系列完全兼容。

第2章Freescale HC08/S08/RS08MCU概述Freescale的08系列单片机由于其稳定性高、开发周期短、成本低、型号多种多样、兼容性好而被广泛应用。

本章概要介绍08系列单片机的类型、基本结构,并从总体上阐述其性能特点。

主要内容有:在介绍08系列单片机的命名规则和资源状况的基础上,分别以MC908GP32、MC9S08GB60及MC9RS08KA2为例讲述HC08系列、HCS08系列及RS08系列单片机的基本结构和特点。

了解这些基本知识,不仅可以为实际开发应用中的单片机选型提供参考,也对后续章节的学习有很大的帮助。

本书以GP32为主要芯片阐述嵌入式系统基本硬件与软件原理,2.2节讨论的GP32引脚功能、硬件最小系统及GP32的存储器框图是重点掌握的内容。

硬件最小系统是芯片运行的基本条件,应该对此有清晰的理解。

对于GP32不具备的功能,本书将使用其他芯片进行阐述,但编程语言体系是相同的。

2.108系列单片机简介目前,Freescale的08系列单片机主要有HC08、HCS08和RS08三种类型。

HC08是1999年开始推出的产品,种类也比较多,针对不同场合的应用都可以选到合适的型号。

HCS08是2004年左右推出的8位MCU,资源丰富,功耗低,性价比很高,是08系列单片机的发展趋势。

HC08与HCS08的最大区别是调试方法不同与最高频率的变化。

RS08是HCS08架构的简化版本,于2006年推出,其内核体积比传统的内核小30%,带有精简指令集,满足用户对体积更小、更加经济高效的解决方案的需求。

RAM及Flash 空间大小差异、封装形式不同、温度范围不同、频率不同、I/O资源差异等形成了不同型号,为嵌入式应用产品的开发提供了丰富的选型。

2.1.1Freescale单片机的命名规则Freescale单片机的型号庞大,但同一系列的CPU是相同的,也就是说具有相同的指令系统,多种型号只是为了适用于不同的场合。

AN3041_深入讨论HCS08的内部时钟源模块(ICS)飞思卡尔应用笔记AN3041深入讨论HCS08的内部时钟源模块(ICS)文件编号:AN3041版本:0,10/2005苏州大学飞思卡尔嵌入式教学与应用培训中心译2008年5月目录1 ICS模块的功能描述 (1)1.1 结构框图 (1)1.2 ICS模式:Off (3)1.3 ICS模式:FEI (3)1.4 ICS模式:FEE (4)1.5 ICS模式:FBI 和 FBILP (4)1.6 ICS模式:FBE 和 FBELP (5)1.7 ICS 与ICG (5)1.8 其他应用特点 (6)2 低功耗模式下的ICS (6)2.1 Stop1和Stop2 (6)2.2 Stop3 (7)2.3 Wait (7)3 校准IRC (7)3.1 如何校准- AN2496 (8)3.2 未校准状态 (8)3.3 校准IRC (8)深入讨论HCS08的内部时钟源模块(ICS)Scott PapeFreescale微控制器部系统工程师本文档将更深入地了解内部时钟源模块(Internal Clock Source,ICS),HCS08系列微控制器的一些成员都包含有该模块。

对HCS08 MCU来说,ICS模块是一个非常灵活的时钟源,但使用该系列中更小、更低成本的MCU仍是非常经济的。

ICS包括锁频环、内部时钟参考、外部振荡器和时钟选择子模块。

这些子模块组合可以提供多种时钟模式和频率,以满足任何应用的需要。

本应用笔记详细描述ICS的7种工作模式、ICS模块与其他HCS08 MCU的内部时钟发生器(Internal Clock Generator,ICG)模块作比较、ICS模块从不同低功耗模式下恢复的特性及内部时钟参考的校准方法。

1 ICS模块的功能描述本节将详细介绍内部时钟源的功能操作。

1.1 结构框图图1为ICS的结构框图。

ICS由4个主要的子模块组成:z锁频环(FLL)z内部参考时钟z外部振荡器z时钟选择逻辑ICS的主要输出为ICSOUT,它产生CPU和总线时钟的时钟信号。

第2章FreescaleHC(s)08系列单片机概述是《嵌入式技术基础与实践》这本书的配套课件,帮助大家更好的学习飞思卡尔的住款单片机。

《嵌入式技术基础与实践》嵌入式技术基础与实践》第二章FreescaleHC08/S08系列FreescaleHC0 C08/S08系列单片机概述主要内容 2.1 08系列单片机简介 2.2 HC08系列单片机 2.3 HCS08系列单片机 2.4 RS08系列单片机 2.5 进一步讨论是《嵌入式技术基础与实践》这本书的配套课件,帮助大家更好的学习飞思卡尔的住款单片机。

《嵌入式技术基础与实践》嵌入式技术基础与实践》2.1 08系列单片机简介08系列单片机简介Freescale的08系列单片机主要有HC08, HCS08和RS08三种类型.HC08推出比较早,种类也比较多,针对不同的场合都可以HC08 选到合适的型号. HCS08是最近推出的新型的08 08系列单片机,性价比很高,是HCS08 08 08系列单片机的发展趋势. 08 RS08是HCS08 RS08 HCS08架构的简化版,其内核体积小,带有精简指令HCS08 集,满足用户对体积更小,更加经济高效地解决方案的需求.是《嵌入式技术基础与实践》这本书的配套课件,帮助大家更好的学习飞思卡尔的住款单片机。

《嵌入式技术基础与实践》嵌入式技术基础与实践》Freescale单片机单片机, 2.1.1 Freescale单片机,基本命名规则хх х хх х х хх х хх ① ② ③ ④ ⑤ ⑥ ⑦①指产品状态存储器类型标志. ② 存储器类型标志. 芯片内核. ③ 芯片内核. 型号标志.④ 型号标志. 存储器大小. ⑤ 存储器大小. 工作温度范围标志.⑥ 工作温度范围标志. 封装标志. ⑦ 封装标志.特别说明: HC08芯片以前命名中包含了68HC“部分芯片以前命名中包含了" 部分, 特别说明:Freescale HC08芯片以前命名中包含了"68HC 部分,如: *****32芯片以前的名称是*****08GP32,在很多资料中对于HC08 芯片以前的名称是*****08GP32 HC08芯*****32芯片以前的名称是*****08GP32,在很多资料中对于HC08芯片都沿用了这种方法. 片都沿用了这种方法.是《嵌入式技术基础与实践》这本书的配套课件,帮助大家更好的学习飞思卡尔的住款单片机。

体值,而无需用户自己计算。

由于复位矢量位于Flash空间,并且每个复位/中断矢量占用2字节的Flash空间,因此用DC.W伪指令定义。

注意不能用DS伪指令定义Flash常量。

对于有中断服务子程序的源程序,为了在发生中断时能够响应中断进入相应的中断服务子程序,和填写复位向量类似,只需将中断服务子程序的入口地址填入对应的中断复位向量区即可。

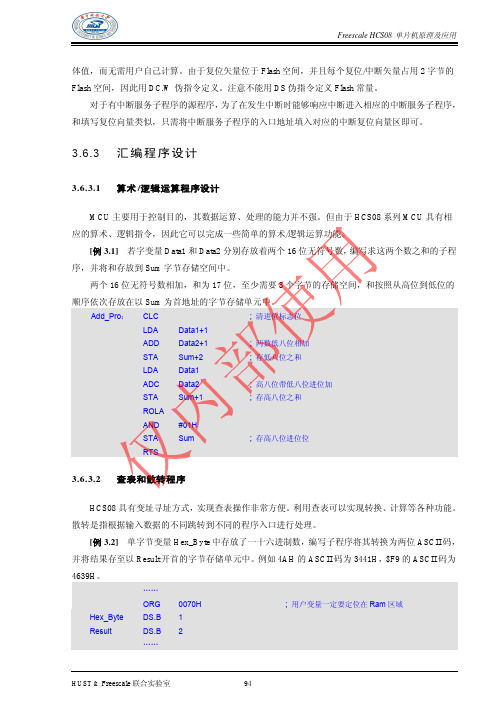

3.6.3汇编程序设计3.6.3.1算术/逻辑运算程序设计MCU主要用于控制目的,其数据运算、处理的能力并不强。

但由于HCS08系列MCU具有相应的算术、逻辑指令,因此它可以完成一些简单的算术/逻辑运算功能。

[例3.1] 若字变量Data1和Data2分别存放着两个16位无符号数,编写求这两个数之和的子程序,并将和存放到Sum字节存储空间中。

两个16位无符号数相加,和为17位,至少需要3个字节的存储空间,和按照从高位到低位的顺序依次存放在以Sum为首地址的字节存储单元中。

Add_Pro:CLC ; 清进位标志位LDA Data1+1ADD Data2+1 ; 两数低八位相加STA Sum+2 ; 存低八位之和LDA Data1ADC Data2 ; 高八位带低八位进位加STA Sum+1 ; 存高八位之和ROLAAND #01HSTA Sum ; 存高八位进位位RTS3.6.3.2查表和散转程序HCS08具有变址寻址方式,实现查表操作非常方便。

利用查表可以实现转换、计算等各种功能。

散转是指根据输入数据的不同跳转到不同的程序入口进行处理。

[例3.2] 单字节变量Hex_Byte中存放了一十六进制数,编写子程序将其转换为两位ASCII码,并将结果存至以Result开首的字节存储单元中。

例如4AH的ASCII码为3441H,$F9的ASCII码为4639H。

……ORG 0070H ; 用户变量一定要定位在Ram区域Hex_Byte DS.B 1Result DS.B 2……ORG 0870HASCII_Table DC.B ‘0123456789ABCDEFG’; 常数表格、代码一定要定位在Flash区域……Hex_To_Ascii:LDA Hex_ByteAND #$F0 ; 取出高4位NSA ; (A[3:0]:A[7:4])→ATAX ; A→XLDA ASCII_Table,X ; 查表,得高4位的ASCII码STA Result ; 存高4位的ASCII码LDA Hex_ByteAND #$0F ; 取出低4位TAX ; A→XLDA ASCII_Table,X ; 查表,得低4位的ASCII码STA Result+1 ; 存低4位的ASCII码RTS[例3.3] 设字节变量Num存放在Ram的0070H单元,取值范围为0T~9T,编写查表子程序,查出变量的立方值,并存入Cube字节变量中。

飞思卡尔半导体 AN3041 应用笔记 第0版, 10/2005深入了解HCS08的内部时钟源(ICS)模块作者:Scott Pape飞思卡尔微控制器部系统工程部在本文中,我们将较为深入地了解一下某些型号的HCS08系列微控制器(MCU)所具有的内部时钟源模块(ICS)。

ICS是HCS08 MCU所采用的一种非常灵活的时钟源,然而它十分的经济高效,适用于HCS08系列中体积较小、成本较低的类型的MCU。

ICS中包含锁频环、内部时钟参考信号、外部振荡器和时钟选择子模块。

这些子模块组合起来能提供各种时钟模式和频率,从而几乎能满足任何应用的需要。

ICS有7种工作模式,后文中将详细讨论。

同时,我们将把ICS模块与用在其他HCS08 MCU中的内部时钟发生器(ICG)模块进行比较。

此外,我们还会介绍ICS模块从HCS08的各种低功耗模式恢复时的工作过程。

在结论部分,我们将介绍内部时钟参考信号的校准。

目录页1 ICS功能介绍 (2)1.1 结构框图 (2)1.2 ICS模式:关断 (4)1.3 ICS模式:FEI (4)1.4 ICS模式:FEE (4)1.5 ICS模式:FBI和FBILP (5)1.6 ICS模式:FBE和FBELP (5)1.7 ICS与ICG (6)1.8 附加应用功能 (6)2 低功耗模式中的ICS (7)2.1 停止1和停止2模式 (7)2.2 停止3模式 (7)2.3 等待模式 (8)3 校准IRC (8)3.1 如何校准— AN2496 (8)3.2 不调整的运行 (8)3.3 校准IRC (9)1 ICS 功能介绍深入了解HCS08的内部时钟源(ICS)模块飞思卡尔半导体 General Business Information 3FLL 的输出频率为参考时钟频率的512倍。

FLL 包括三个主要部分:·参考频率选择·数字控制振荡器(DCO )·用于比较这两个部分输出的滤波器FLL 的工作原理与锁相环(PLL )非常相似。

不同之处在于PLL 是根据参考时钟与DCO时钟的相位差来调节输出的,而FLL 则是通过比较DCO 时钟与参考时钟的频率来工作的。

FLL 对一个参考时钟周期内的DCO 时钟脉冲边沿数进行计数。

因此,对于512倍的倍频器,FLL 应该在参考时钟的每两个上升沿之间得到512个DCO 输出的上升沿。

FLL 的实现大多借助数字逻辑电路,因而不需要PLL 通常必须采用的外部滤波器件。

时钟选择逻辑只是简单地选择FLL 、外部参考时钟或内部参考时钟作为ICS 模块的输出。

此外,还采用了一个时钟分频器电路,可以对输出进行1倍、2倍、4倍或8倍分频,用以降低输出时钟的频率。

内部参考时钟(IRC )是一个可调整的内部参考时钟信号,既可用作FLL 的参考时钟,也可直接用作CPU 和总线时钟的时钟源。

这个内部参考时钟不需要诸如调整电容或电阻等的外部器件。

IRC 由ICS 寄存器中的一个9位数值进行调整,解析度典型值能达到未调整IRC 频率的0.1%。

与许多其他的内部参考时钟不同,这个IRC 可将频率在一定的范围内进行调整,从31.25kHz 变到39.06kHz 。

当用作FLL 的参考时钟时,这将允许用户用0.1%的解析度,把总线频率设定在8MHz 至10MHz 间的任意值。

调整之后,对调整频率的偏差典型值仅为 +0.5% 至 -1%,最大值也只不过是±2%。

外部振荡器参考时钟(OSC )实际上把三个外部时钟源合并在一个里面。

它有一个采用32kHz 至38.4kHz 晶体或谐振器的低频振荡器,还有一个采用1MHz 至16MHz 晶体或谐振器的高频振荡器。

这两个振荡器需要两个引脚即XTAL 和EXTAL 来生成时钟信号。

OSC 还有一种外部时钟模式,该模式简单地把一个外部时钟信号引入MCU 。

在此模式中,只需要EXTAL 脚,而XTAL 脚可用作通用I/O 。

输入频率可以是0Hz 至20MHz 之间的任意值。

由于引脚的限制,有些MCU 可能没有外部振荡器。

ICS 的子模块是否启动取决于采用哪种ICS 时钟模式。

ICS 具有7种工作模式:·关断·FLL 启用、内部参考时钟(FEI )·FLL 启用、外部参考时钟(FEE )·FLL 旁路、内部参考时钟(FBI )·FLL 旁路、内部参考时钟、低功耗(FBILP )·FLL 旁路、外部参考时钟(FBE )·FLL 旁路、外部参考时钟、低功耗(FBELP )1 ICS 功能介绍深入了解HCS08的内部时钟源(ICS)模块表1:FEE 模式下的容许外部频率FEE 中的总线频率可根据等式(2)计算:f bus = (f OSC ÷参考时钟分频器)×512÷(2×总线分频器) 等式(2)1.5 ICS 模式:FBI 和FBILPFLL 旁路、内部参考时钟(FBI )模式与FLL 旁路、内部参考时钟低功耗(FBILP )模式基本上是一样的,只有一点不同。

这两种模式均旁路FLL ,而直接采用IRC 生成ICSOUT 。

不同之处在于FBI 模式让FLL 保持运行,而FBILP 模式则关闭FLL ,从而节省更多的功耗。

FBILP 是通过配置为FBI 并设定ICS 控制寄存器2(ICSC2)中的LP 位来启动的。

采用FBI 而非FBILP 的原因之一,是为了要采用背景调试模式(BDM );之二,当应用要切换到FEI 时可节省FLL 的锁定时间。

FLL 必须处于运行状态才能给BDM 通信提供一个高速时钟源。

如果LP 位在BDM 启动后再置1,FLL 将保持运行状态,不管LP 位是否置1。

同样,如果BDM 在LP 位置1后又启动,FLL 将开启。

FLL 的锁定时间的最大规定值为1ms ,通常需要约500μs 的时间。

关闭FLL 一般可节省大约220~310μA 的电流,具体数值取决于V DD 和FLL 的频率。

1.6 ICS 模式:FBE 和FBELPFLL 旁路、外部参考时钟(FBE )模式和FLL 旁路、外部参考时钟低功耗(FBELP )模式与上述的FBI 和FBILP 模式类似,除了是用OSC 产生时钟源,而不是用IRC 。

FLL 仍被旁路,LP 位则在未启动BDM 时关闭FLL 。

在1.4节中我们看到,当FLL 启用时(FEE ),OSC 的频率会受到限制。

如果不会采用FEE 模式且ICS 被置于FBELP 模式(记住,FLL 在FBE 模式中保持运行),则这些限制都会解除,剩下的只是对OSC 参考时钟本身的限制:低频振荡器从32kHz 到38.4kHz 、高频振荡器从1MHz 到16MHz ,而外部时钟模式从0Hz 到20MHz 。

然而,如果会启用BDM ,则FEE 的振荡器限制在FBILP 模式中 也适用。

飞思卡尔半导体 General Business Information 51 ICS 功能介绍 深入了解HCS08的内部时钟源(ICS)模块6 General Business Information 飞思卡尔半导体同样,对于FBELP ,1.4节中讨论的参考时钟分频器也不起作用。

FEE 模式中的振荡器限制在FBE 模式中也适用。

1.7 ICS 与ICG现在有几款HCS08 MCU 采用了内部时钟发生器(ICG )模块。

为了区分ICS 和ICG ,应弄清几点差异。

尽管ICS 是一种全新的模块,但是就功能而言,它基本上就是ICG 的一个子模块。

ICS 旨在为体积更小、对成本更敏感的HCS08 MCU 提供一种尺寸更小、功耗更低的时钟模块。

首先,对于产生输出频率,ICG 模块中的FLL 具备更多的选择。

ICS 的 FLL 将倍频数固定为512,可输出16MHz 到20MHz 的频率,而ICG 的 FLL 则具有8个软件可选的倍频值,还另有一个预分频器,既可用于高频(>1MHz ),也可用于低频(<100kHz )的参考时钟。

ICG 的FLL 能够输出8MHz 到40MHz 的频率,同时对参考时钟的限制也较少。

ICG 提供了更多的时钟状态位。

ICG 有9个状态位,几乎可监测ICG 运行的所有方面,包括LOCK 状态、当前的ICG 模式、DCO 稳定性和外部参考时钟稳定性(包括各种时钟)。

ICS 只有三个状态位:两个用于监测当前的ICS 模式,另一位用于指示外部振荡器已启动。

ICG 还有一个时钟监控电路,能在FLL 失锁或时钟源失步时产生复位或中断。

失步或失锁不仅能产生复位或中断,ICG 还会切换到内部时钟源,维持CPU 的运行。

ICS 没有监测失步或失锁的功能。

不过,有些HCS08的 MCU 给COP 看门狗定时器提供了一个完全独立的时钟源,能在CPU 和总线时钟出错时使MCU 复位。

有关ICG 的更多细节可参阅任何带ICG 模块的HCS08 MCU ,比如MC9S08GB60的数据手册,或应用笔记AN2494。

1.8 附加应用功能应该提一下的两个附加功能是总线分频器和高增益振荡器。

本文先前已经提到过总线分频器。

总线分频器有4个软件可选的数值用于总线时钟的分频:1、2、4或8,由ICSC2中的BDIV 位选择。

除了关断模式,其他所有的ICS 模式中均可使用。

当不需要较高的总线速度时,它可以降低CPU 和总线时钟,从而降低功耗。

分频器位于FLL 之外,因此其数值的改变不会导致FLL 失锁。

同时,分频器只是简单地从分频器链路的4个输出中选择1个,所以频率的改变只需要很少的几个总线周期。

发生任何复位后,BDIV 设置为二分频。

2 低功耗模式中的ICS 深入了解HCS08的内部时钟源(ICS)模块飞思卡尔半导体 General Business Information 7当驱动晶振或谐振器时,OSC 模块可选择工作在低功耗或高增益模式。

低功耗模式可限制外部器件上的电压振幅,以节省功耗。

高增益模式驱动外部器件达到全电源轨道的幅值,从而使振荡电路不易遭受板级噪声的干扰。

采用高增益选项所导致的功耗上升取决于电源电压和OSC 的频率。

例如,一个运行于低功耗模式的32kHz 晶振通常消耗5μA 的电流,但不会随V DD 发生显著的变化。

当V DD 为3V 时,相同的晶振运行于高增益模式下将消耗约40~50μA 的电流,而且电流会随V DD 发生较大的变化。

2 低功耗模式中的ICS了解低功耗模式如何影响ICS 的运行是很重要的。

2.1 停止1和停止2模式当MCU 进入停止1或停止2模式时,ICS 总是被置于关断模式。

因此,执行STOP 指令时ICS 在所处的模式无关紧要,也不会影响处于停止1和停止2期间的功耗。