基于PCI9054的高速数据处理卡的设计

- 格式:pdf

- 大小:306.90 KB

- 文档页数:4

教你设计PCI总线的高速数据采集卡(基于PCI9054)2007-03-13 21:02眼下有不少场合需要用到PCI总线的数据采集卡,下面我就来谈一下设计PCI数采卡的原理及要点。

首先我要以我的实际经验,纠正存在于很多人心里的几个误区:1.设计PCI采集卡要通读PCI协议。

相信有很多初学者都在这个地方被吓住了,几百页的英文要通读并理解谈何容易!其实PCI协议处理的这部分功能已经被PCI接口芯片完成了,如PLX公司的9054、9056和9052等等,它封装了PCI协议的细节,我们只需要控制这颗接口芯片local端的几个控制线就可以完成PCI总线的数据传输。

PCI协议也有它的用处,我们只需要在某些需要注意的地方查阅一下相关章节即可,比如PRSNT1#和PRSNT2#引脚至少要有一个下拉,才能识别到卡,这就是PCI协议中的规定。

2. PCI卡布线很复杂,一不小心就可能不成功。

其实对于32位33MHz的PCI总线来说,布线相对比较简单,只要稍加注意就不会出问题。

比如:PCI总线的时钟线要做成2500(+/-100)mil,这个是要注意的一点,一般PCI卡上的蛇行弯曲走线就是这条线,因为走直线距离一般都达不到此长度。

其他要求,比如地址和数据线要在1500mil以内,其实你超过一些也没什么问题,不要超太多就好了。

3. PCI卡的驱动程序编写很难。

其实无论是软件还是硬件设计,都有一些相对成熟的资料可以参考。

对驱动程序来说也是这样,对实际项目的开发没有几个是从头到尾自己在编代码,都可以在网上找到一些成熟的代码,然后自己修改一下即可,况且PCI卡的驱动程序又相对比较成熟,可参考的资料也较多。

所以你要从网上找代码,向PCI接口芯片的供应商要代码,等收集到足够多的代码,再配以适当的教材(比如对于windows2000/XP系统下的WDM驱动程序,可以参考武安河老师的教材就足够),就可以进行你自己的驱动设计了。

下面我再针对具体应用谈谈PCI采集卡的设计:一般数采卡的情况是将A/D转换后的数据通过PCI总线上传到PCI机,然后利用上层的软件进行分析处理。

基于PCI9054的高速数据处理卡的设计

林若波;陈旭文

【期刊名称】《测控技术》

【年(卷),期】2011(030)005

【摘要】详细介绍了一种基于PCI9054的高速数据处理卡的系统结构以及主要功能模块,并基于PCI9054桥片和EPM1270,介绍了该数据处理卡的硬件和软件的实现方案,讨论了数据处理卡的测试结果.

【总页数】4页(P57-60)

【作者】林若波;陈旭文

【作者单位】广东揭阳职业技术学院,广东,揭阳,522051;广东揭阳职业技术学院,广东,揭阳,522051

【正文语种】中文

【中图分类】TP274

【相关文献】

1.基于PCI Express总线的数据处理与传输卡的设计与实现 [J], 王大磊;王斌

2.基于PCI9054的数据通信接口卡设计 [J], 张丹红;张孝勇;刘文

3.基于PCI9054的LVDS高速数据通信卡设计 [J], 黄华;刘亚军

4.基于PCI9054与FPGA的高速低电压差分信号接收器设计 [J], 赵巨兴;王民钢;樊英平

5.基于PCI9054的通信卡设计 [J], 陈嫣然;张会新;郑燕露

因版权原因,仅展示原文概要,查看原文内容请购买。

收稿日期:2008-05-20基金项目:铁道部资助项目(99j34-A )作者简介:纪淑波(1977-),男,山东海阳人,讲师,主要研究方向为光电工程、图像产生、获取与处理技术.文章编号:1673-1255(2008)04-0046-03PCI9054接口芯片的应用设计纪淑波,曲北北(鲁东大学,山东 烟台 264025)摘 要:PCI9054是美国PL X 公司生产的PCI 总线通用接口芯片.介绍了PCI 总线接口的一般设计方法及PCI9054的内部结构、以及其工作原理,并以一种基于PCI 总线的数据传输系统的设计为例,给出其工作原理,并讨论接口的硬件实现方法以及采用软件包Windriver 开发设备驱动程序的方法.关键词:PCI 总线;FPG A ;驱动程序;Windriver ;PCI9054中图分类号:T N911.7 文献标识码:AApplication and Design of PCI 9054Interface ChipJ I Shu 2bo ,QU Bei 2bei(L udong U niversity ,Yantai 264025,China )Abstract :PCI9054is a general interface chip made by the PL X Company of USA.G eneral design method of PCI bus interface ,inter instruction and the work principle of PCI9054are introduced.The design of a data transmis 2sion system based on PCI bus as a example ,its working principle is given ,and the implementation method of hard 2ware design for PCI interface and the ways to develop the driver program by using Windriver are discussed.K ey w ords :PCI bus ;F GPA ;driver ;Windriver ;PCI9054 PCI9054是美国PL X 公司生产的PCI 总线通用接口芯片.使用该芯片桥接PCI 总线和本地总线(local bus ),开发者可以省去考虑太多复杂的PCI 总线规范,而集中精力开发硬件和驱动程序.PCI9054具有较强的性能.它符合PCI V2.1和V2.2规范;提供了2个独立的可编程DMA 控制器,每个通道均支持块和分散/集中的DMA 方式;在PCI 总线端支持32位/33MHz ;本地端(local bus )可以编程8、16、32位的数据宽度,传输速率最高可达132MB/s.本地总线端时钟最高可达50MHz ,支持复用/非复用的32位地址/数据[1,2].PCI9054内部有6种可编程的FIFO 存储器,以实现零等待突发传输以及本地总线和PCI 总线之间的异步操作(见表1).总之,该芯片为用户提供了较宽松灵活的设计空间.PCI 总线是Intel 公司推出的一种高性能局部表1 PCI9054内部FIFOFIFO 长度/(dB )PCI 启动I/O 读PCI 启动I/O 写PCI 目标读PCI 目标写DMA 读DMA 写163216323232总线[3],其数据总线为32位,且可扩展为64位,最大数据传输速率为132~264MB/s ,是目前使用非常普遍的一种总线.因PCI 协议比较复杂,较难掌握,故PCI 总线扩展卡的开发比ISA 总线等其他扩展卡难度大.PCI 9054芯片是一种能满足PCI V2.2协议,特别适用于PCI 总线外设产品开发的PCI →本地总线I/O 加速器芯片.结合PCI9054介绍PCI第23卷第4期2008年8月 光电技术应用EL ECTRO -OPTIC TECHNOLO GY APPL ICA TION Vol.23,No.4August.2008总线技术的设计方法.1 系统工作原理系统应用于光电信号转换系统中,主要解决主机与光电装备之间的数据传输问题,其工作流程是:主机运行应用程序,产生数据源,在外部控制信号的控制下,通过PCI 总线与光电装备进行数据通信,主要解决的问题是:PCI 接口硬件设计和PCI 设备驱动程序开发.2 PCI 接口硬件设计目前实现PCI 接口的有效方案有使用可编程逻辑器件和使用专用芯片2种[4].由于PCI 总线协议较复杂,采用可编程逻辑器件设计PCI 控制接口难度大,对于产品不大又有时限的工程项目来说,成本较高,采用专用接口器件虽然没有采用可编程逻辑器件那么灵活,但其优越性相当明显:能够有效地降低接口设计的难度,缩短开发时间.数据传输系统采用PL X 公司的PCI9054作为PCI 接口芯片,以FP G A 来完成逻辑控制以及与光电装备的连接,整个系统的框图如图1所示,其中,FP G A 选用的是AL TREA 公司的EPF1030AQC240-3.图1 数据传输系统硬件设计框图2.1 数据传输及控制原理PCI 9054可工作在M ,C ,J 3种模式,其中,C模式时序较为简单,系统采用PCI9054的C 模式传送,先由计算机主机通过PCI 总线向系统发出命令字,PCI9054将数据或命令字存入声纳设备中,数据传送时,局部总线控制逻辑FP G A 应驱动地址总线、数据总线、读写信号线及地址选通信号,控制PCI 局部总线的数据传输.PCI9054会直接将数据存入其内部FIFO ,随后PCI9054会向PCI 系统申请PCI 总线控制权,在得到总线控制权后,根据映射地址自行完成本次数据传输操作.局部总线控制器只需将数据写入PCI9054内部FIFO ,其后的操作不需要FP G A 的参与.FP G A 的局部总线逻辑的状态机框图如图2所示.图2 局部总线逻辑状态机框图状态0为空闲状态,当ADS #为0时如经本地总线译码后表明需要访问本地空间时,转到状态1,否则留在状态0;状态1为访问开始状态,当处于此状态下,如BLAST #为0时,转到状态2,如BLAST #为1时,则转到状态4;状态2为单周期等待状态,在此状态下,数据在本地总线上保持稳定,当处于此状态下直接转到状态3;状态3单周期数据结束状态,在此状态下数据从本地总线上取走,当ADS #为0时,经本地总线译码后,表明还需要访问本地空间时,则转到状态1,否则转到状态0,完成数据传送;状态4为突发等待状态,在此状态下数据在本地总线上保持稳定,当处于此状态下直接转到状态5;状态5为突发重复状态,在此状态下,如BLAST #为0时,转到状态6,否则重复此状态;状态6为最后数据突发传输完成状态,在此状态下当ADS #为0时,如经本地总线译码后,表明还需要访问本地空间时,转到状态1,否则转到状态0,将以上状态机用V HDL 语言在可编程逻辑器件中实现,即可实现访问本地总线的控制.2.2 EEPROM 的配置与烧写与ISA 总线相比,PCI 总线支持3个物理空间:存储器地址空间、I/O 空间和配置空间.串行EEP 2ROM 存储了PCI9054重要的信息,如设备号DID 、制造商号V ID 、子设备号SDID 、子制造商号SV ID 、中断号、设备类型号、局部空间基地址以及局部空间描述符等信号,EEPROM 的内容非常重要,它直接关系到整个板卡能否正常工作.系统加电时,通过PCI 的RST 复位以后,PCI9054首先检测EEPROM 是否存在.如果检测到EEPROM 首字不是FFFFH ,PCI9054将依次读取74第4期 纪淑波等:PCI9054接口芯片的应用设计 EEPROM的内容来初始化内部寄存器.PCIB I-OS 根据配置寄存器的内容进行系统资源分配,这样,整个PCI设备的资源才不会发生冲突.配置寄存器的内容编写完以后,可以用编程器写入EEPROM中.另外,也可以通过主机在线烧写,但由于各种原理,成功率很低.对于PCI9054芯片,可选用的串行EEPROM有STM公司的93CS56等.3 实例分析以下为一段使用Windriver开发的PCI9054 DMA的驱动代码[5],为了节省篇幅,省略了变量说明部分.程序中出现的变量大都由其名称可以反映含义,具体可以参见Windriver的设计文档中的说明.#include“windrvr.h”#include“plx lib.h”#define PCI9054DEFAUL T V ENDOR ID0x10b5 //PL X公司制造商号#define PCI9054DEFAUL T DEV ICE ID0x9054// PCI9054的设备号#define IS MASTER TRU EhDev=PL X DIA G DeviceFindAndOpen(PCI9054 DEFAUL T V ENDOR ID,PCI9054DEFAUL T DEV ICE ID,IS MASTER);//打开Windriver设备,锁定并返回该设备的资源,该设备的资源均包括在hHandle中;PCI9054DMAOpen(hDev,3pDMA,dwBytes);//初始化并锁定用于DMA传输的内存资源;PCI9054Int Enable(hDev,funcInt Handler);//设定中断,funcInt Handler为中断处理函数PCI9054DMAStart(hDev,3pDMA,f Read,fBlocking, dwBytes,dwoffset);//根据给定参数开始DMA传输PCI9054DMAClose(hDev,3pDMA);//解除DMA传输资源PCI9054intDisable(hDev);//禁止中断;PCI9054Close(hDev);//关闭Windriver设备4 结 束 语从以上分析可以看出,PCI9054是一种性价比很高的PCI桥路芯片,PCI9054提供了PCI总线的一种直接数据传输路径,降低了PCI总线的复杂性.对本地总线与设备进行数据传输进行了详细的讨论,给出了实用的本地总线数据传输的接口逻辑设计,根据这一设计,就可以很好地在本地总线和外部设备之间进行数据传输和控制,具有较高的应用价值.参考文献[1] 陈露晨.PCI9054性能分析及外部FIFO的扩充[J].电子产品世界,2000(11):50-51.[2] PCI9054Data Book Version2.1[Z],2002.[3] 尹勇,李宇.PCI总线设备开发宝典[M].北京:北京航空航天大学出版社,2004:153-160.[4] 彭佛才.基于PCI的高速媒体网关系统及其驱动程序设计[J].电子技术应用,2006(6):19-21.[5] 武安河.Windows2000/XP WDM设备驱动程序开发[M].北京:电子工业出版社,2005:132-136.简讯分布式孔径半主动激光导引头的发展 2008年6月2日,英国BAE系统公司的“先进精确杀伤武器系统”(APKWS)II半主动激光制导70mm火箭弹,进行了系统的发展与演示验证.APKWS II火箭弹采用了分布式孔径导引头.布置在弹体中部的分布式孔径半主动激光导引头(DASAL S)和制导控制装置可免遭沙尘、振动、冰雪和其他实战中可能遇到的恶劣环境的危害.APKWS II火箭弹是一种低成本的轻型制导武器,能有效对付轻型装甲目标,以弥补70mm火箭弹和“海尔法”导弹之间的火力空缺,其系统将应用于所有目前使用70mm 火箭弹的陆军飞机上.英国BAE系统公司和美国雷声公司不约而同地选择了半主动激光制导技术,将制导组件安装到“九头蛇”-70火箭弹上,双方的设计思路可谓大相径庭.雷声公司主张将激光导引头安排在火箭弹的头部,其好处是在火箭弹发射前导引头就能锁定目标.由于“九头蛇”-70火箭弹的战斗部及引信均位于头部,因此这种设计将改变战斗部及引信的原有位置,进而需要重新鉴定、测试和确认火箭弹的杀伤力.BAE系统公司设计的制导组件称为“分布式孔径半主动激光导引(下转第65页)84 光 电 技 术 应 用 第23卷。

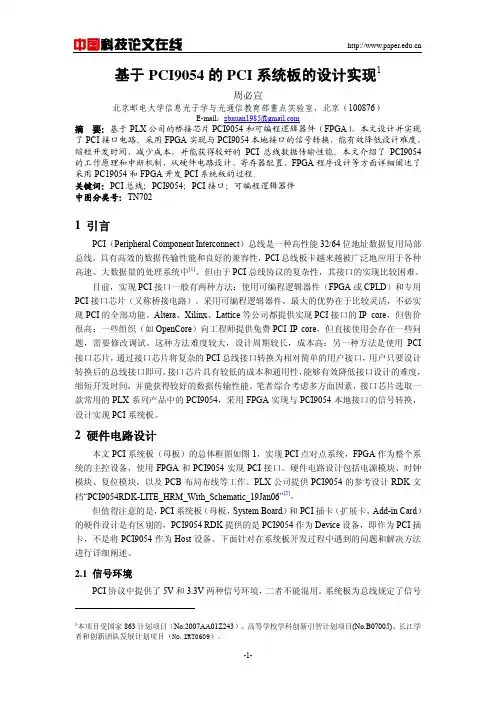

基于PCI9054的PCI系统板的设计实现1周必宣北京邮电大学信息光子学与光通信教育部重点实验室,北京(100876)E-mail:zbxuan1985@摘要:基于PLX公司的桥接芯片PCI9054和可编程逻辑器件(FPGA),本文设计并实现了PCI接口电路。

采用FPGA实现与PCI9054本地接口的信号转换,能有效降低设计难度,缩短开发时间,减少成本,并能获得较好的PCI总线数据传输性能。

本文介绍了PCI9054的工作原理和中断机制,从硬件电路设计、寄存器配置、FPGA程序设计等方面详细阐述了采用PC19054和FPGA开发PCI系统板的过程。

关键词:PCI总线;PCI9054;PCI接口;可编程逻辑器件中图分类号:TN7021 引言PCI(Peripheral Component Interconnect)总线是一种高性能32/64位地址数据复用局部总线,具有高效的数据传输性能和良好的兼容性,PCI总线板卡越来越被广泛地应用于各种高速、大数据量的处理系统中[1]。

但由于PCI总线协议的复杂性,其接口的实现比较困难。

目前,实现PCI接口一般有两种方法:使用可编程逻辑器件(FPGA或CPLD)和专用PCI接口芯片(又称桥接电路)。

采用可编程逻辑器件,最大的优势在于比较灵活,不必实现PCI的全部功能。

Altera、Xilinx、Lattice等公司都提供实现PCI接口的IP core,但售价很高;一些组织(如OpenCore)向工程师提供免费PCI IP core,但直接使用会存在一些问题,需要修改调试。

这种方法难度较大,设计周期较长,成本高;另一种方法是使用PCI 接口芯片,通过接口芯片将复杂的PCI总线接口转换为相对简单的用户接口,用户只要设计转换后的总线接口即可。

接口芯片具有较低的成本和通用性,能够有效降低接口设计的难度,缩短开发时间,并能获得较好的数据传输性能。

笔者综合考虑多方面因素,接口芯片选取一款常用的PLX系列产品中的PCI9054,采用FPGA实现与PCI9054本地接口的信号转换,设计实现PCI系统板。

基于PCI9054的接口卡PCI 总线支持突发传送,多处理器和并发工作,广泛应用于各种平台设计。

基于PCI9054 的接口板也广泛地应用于各种高速、大数据量的处理系统。

由于PCI9054 桥接有PCI 总线和本地总线,开发者不必过多考虑复杂的PCI 总线规范,从而能有更多精力开发硬件和驱动程序设计。

这里以PCI9054 为例,给出了接口板的硬件和软件设计,详细论述了该系统设计的原理图和用VHDL 语言编写的部分逻辑源程序,以供相关开发人员参考。

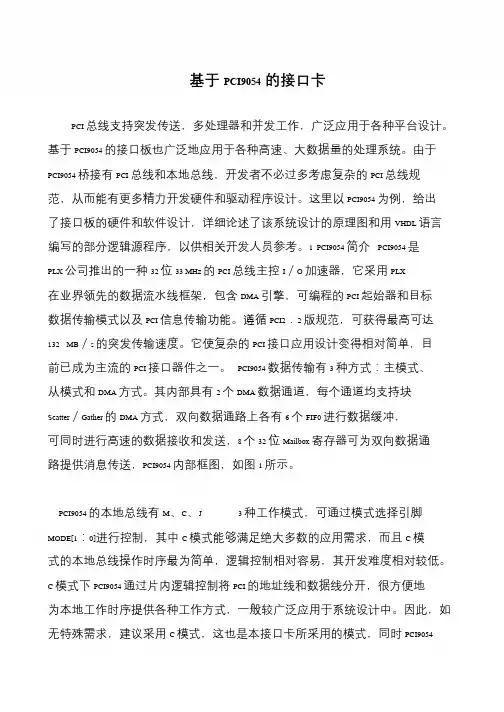

1 PCI9054 简介PCI9054 是PLX 公司推出的一种32 位33 MHz 的PCI 总线主控I/O 加速器,它采用PLX 在业界领先的数据流水线框架,包含DMA 引擎,可编程的PCI 起始器和目标数据传输模式以及PCI 信息传输功能。

遵循PCI2.2 版规范,可获得最高可达132 MB/s 的突发传输速度。

它使复杂的PCI 接口应用设计变得相对简单,目前已成为主流的PCI 接口器件之一。

PCI9054 数据传输有3 种方式:主模式、从模式和DMA 方式。

其内部具有2 个DMA 数据通道,每个通道均支持块Scatter/Gather 的DMA 方式,双向数据通路上各有6 个FIF0 进行数据缓冲,可同时进行高速的数据接收和发送,8 个32 位Mailbox 寄存器可为双向数据通路提供消息传送,PCI9054 内部框图,如图1 所示。

PCI9054 的本地总线有M、C、J 3 种工作模式,可通过模式选择引脚MODE[1:0]进行控制,其中C 模式能够满足绝大多数的应用需求,而且C 模式的本地总线操作时序最为简单,逻辑控制相对容易,其开发难度相对较低。

C 模式下PCI9054 通过片内逻辑控制将PCI 的地址线和数据线分开,很方便地为本地工作时序提供各种工作方式,一般较广泛应用于系统设计中。

因此,如无特殊需求,建议采用C 模式,这也是本接口卡所采用的模式,同时PCI9054。

基于PCI9054的PCI接口板设计,电子商务- 基于PCI9054的PCI接口板设计简介谢冲,中国人民解放军驻六三一所代表室工程师,硕士。

主要从事计算机硬件设计。

董鹏举,西安邮电学院助理工程师。

主要从事自动化。

摘要:用PCI接口芯片实现的PCI总线接口板具有成本低,通用,设计难度低,开发周期短的优点,使用这种设计方法能够减少许多相应的外围器件,可用于开发各种高速数据采集系统、图象处理系统等PCI总线扩展板。

关键词:PCI总线;PCI接口芯片;PCI接口板《中国电子商务》杂志征稿详情点击:http://引言PCI总线是一种高性能局部总线,是为了满足外设间以及外设与主机间高速数据传输而提出来的。

采用PCI总线进行数据传输,可以解决原有的标准总线数据传输率低带来的瓶颈问题。

因此,基于PCI总线的扩展板越来越多地被应用于各种高速、大数据量的处理系统中。

PCI总线接口板的设计必须符合PCI总线规范定义的电气特性和时序要求。

目前,PCI总线接口开发一般采用两种方式:一是采用CPLD来实现接口电路。

这种设计方法的优点是使用比较灵活,设计人员可以根据自己的需要设计适合于特定功能的接口电路,而不必实现PCI总线的全部功能。

但由于PCI总线协议复杂,设计PCI控制接口难度较大,对于产品不大又有时限的工程项目来说,耗时长、成本高。

二是采用通用PCI接口芯片,例如PLX公司的PCI9054、PCI9050、PCI9080等,它们均实现了PCI 总线规范要求的所有硬件接口信号和配置空间寄存器。

相比于CPLD设计控制接口的设计方法,PCI接口芯片的成本较低,具有通用性,能够有效降低接口设计的难度,缩短开发时间。

1PCI接口芯片对于实现功能比较简单,成本要求较低的PCI总线扩展板,使用专用接口芯片是最优选择。

PCI9054是使用较为普遍的一种PCI接口芯片。

PCI9054是由美国PLX公司生产的先进的PCII/O加速器,它采用了先进的PLX数据管道结构技术,具有比较高的性价比,相比于PCI9080、PCI9050性能更优越。

基于P C I9054的多总线通信板卡的研制郑永龙\白煊2,穆蓉2,聂敏2,周勇军\彭虎1(1.中国人民解放军第5720工厂安徽省航空设备测控与逆向工程实验室,安徽芜湖241007;2.南京航空航天大学自动化学院,江苏南京211106)摘要:为掌握PCI板卡设计及其通信原理、开发基于PCI接口的多总线通信卡,针对目前PC I总线通信接口模块的研制现状,在对PCI9054及其PCI卡开发流程进行系统诠释的基础上,以PCI9054为PCI总线协议芯片,以Cyclone皿系列FPGA(EP3C5E144C8)为本地总线控制器,采用“FPGA +PCI9054”架构,设计一种基于PCI接口的具有1路RS232、3路RS422收发的多总线通信卡,给出该模块的硬件设计与软件开发(包括基于VC ++的板卡测试软件与基于Verilog的板卡功能代码),并对其通信功能进行试验验证,仿真与实验结果表明其有效性。

关键词:PCI9054; FPGA; PCI总线;板卡中图分类号:V243. 1文献标识码:A 文章编号:000 -8829(2018)03-0123 -06Design of Multi-Bus Communication Board Based on PCI9054ZHENG Yong-long1,BAI Xuan2,MU Rong2,NIE M in2,ZHOU Yong-ju n1,PENG H u1(1. A n h u i A e r o n a u tic a l E q u ip m e n t M e a su r e m e n t a n d R e v e r se E n g in e e r in g L a b o r a to r y,T h e 5720 F a c to r y o f t h e C h in e se P e o p le’s L ib e r a tio n A rm y, W u h u 241007, C h in a;2. C o lle g e o f A u to m a tio n E n g in e e r in g, N a n jin g U n iv e r s ity of A e ro n a u tic s a n d A stro n a u tic s, N a n jin g 211106, C h in a)A b stra ct:In order to master the PCI board design and its communication principle and to develop the multibus communication card based on PCI interface,according to the current development situation,based on the systematic interpretation of PCI9054 and its PCI card development process,a multi-bus communication card with one RS232 and three RS422 transceivers based on PCI interface is designed,which adopting the“FPGA + PCI9054”architecture and taking PCI9054 as PCI interface protocol chip,Cyclone M series FPGA (EP3C5E144C8) as local bus controller.The software and hardware of this module(including board testing software based on VC ++ and board function code based on Verilog)have been developed,and their communication functions are verified.Simulation and test results demonstrate their effectiveness.K ey words: PCI9054;FPGA;PCI bus;boardP C I总线由IS A总线发展而来,具有传输能力强、多总线共存、独立于C PU以及可自动识别配置外设等 特点,目前被广泛应用于工控测试系统中。

总线接口芯片PCI9054及其在高速数据采集系统中的应用装备指挥技术学院邵胜利侯孝民摘要:本文介绍了PCI总线接口芯片PCI9054的性能、总线操作及其DMA 数据传输方式,并且通过它在高速数据采集系统中的应用实例,阐述了PCI9054在PCI接口电路设计中的简便性和实用性。

关键词:PCI总线接口PCI9054 DMA Windriver引言PCI(Peripheral Component Interconnect)总线即外围部件互连总线,是一种先进的高性能32/64位地址数据复用局部总线,可同时支持多组外围设备,并且不受制于处理器,为中央处理器与高速外围设备提供一座沟通的桥梁,提高了数据吞吐量(32位时最大可达132MB/s),是当今PC领域中流行的总线。

PCI总线具有严格的总线规范,这就保证了它具有良好的兼容性,符合PCI总线规范的扩展卡可以插入任何PCI系统可靠地工作。

一个PCI接口包括一系列的寄存器,这些寄存器中的信息允许计算机自动配置PCI卡。

目前实现PCI接口一般采用专用器件,有效方案分为两种:使用可编程逻辑器件和使用专用总线接口器件。

采用可编程逻辑器件实现PCI接口比较灵活,可以利用的器件也比较多,但由于PCI总线协议的复杂性,其接口的实现比ISA 等总线要困难得多,这种方法难度较大,设计周期较长。

采用专用接口器件不仅对PCI协议有良好的支持,而且提供给设计者良好的接口,这些都大大减少了设计者的工作量。

PCI9054的结构和性能PCI9054是美国PLX公司继PCI9052之后推出的又一低成本PCI总线接口芯片,低功耗,PQFP 172pins封装,它采用了先进的PLX数据管道结构技术,可以使局部总线快速转换到PCI总线上。

PCI9054主要特性PCI9054的主要特性如下:* 符合PCI V2.1,V2.2 规范,包含PCI电源管理特性。

* 支持VPD(Vital Product Data)的PCI扩展。

基于PCI9054的PCI接口板设计,电子商务- 基于PCI9054的PCI接口板设计简介谢冲,中国人民解放军驻六三一所代表室工程师,硕士。

主要从事计算机硬件设计。

董鹏举,西安邮电学院助理工程师。

主要从事自动化。

摘要:用PCI接口芯片实现的PCI总线接口板具有成本低,通用,设计难度低,开发周期短的优点,使用这种设计方法能够减少许多相应的外围器件,可用于开发各种高速数据采集系统、图象处理系统等PCI总线扩展板。

关键词:PCI总线;PCI接口芯片;PCI接口板《中国电子商务》杂志征稿详情点击:http://引言PCI总线是一种高性能局部总线,是为了满足外设间以及外设与主机间高速数据传输而提出来的。

采用PCI总线进行数据传输,可以解决原有的标准总线数据传输率低带来的瓶颈问题。

因此,基于PCI总线的扩展板越来越多地被应用于各种高速、大数据量的处理系统中。

PCI总线接口板的设计必须符合PCI总线规范定义的电气特性和时序要求。

目前,PCI总线接口开发一般采用两种方式:一是采用CPLD来实现接口电路。

这种设计方法的优点是使用比较灵活,设计人员可以根据自己的需要设计适合于特定功能的接口电路,而不必实现PCI总线的全部功能。

但由于PCI总线协议复杂,设计PCI控制接口难度较大,对于产品不大又有时限的工程项目来说,耗时长、成本高。

二是采用通用PCI接口芯片,例如PLX公司的PCI9054、PCI9050、PCI9080等,它们均实现了PCI 总线规范要求的所有硬件接口信号和配置空间寄存器。

相比于CPLD设计控制接口的设计方法,PCI接口芯片的成本较低,具有通用性,能够有效降低接口设计的难度,缩短开发时间。

1PCI接口芯片对于实现功能比较简单,成本要求较低的PCI总线扩展板,使用专用接口芯片是最优选择。

PCI9054是使用较为普遍的一种PCI接口芯片。

PCI9054是由美国PLX公司生产的先进的PCII/O加速器,它采用了先进的PLX数据管道结构技术,具有比较高的性价比,相比于PCI9080、PCI9050性能更优越。

基于PCI9054的PCI高速通信接口实现图2 PCI9054硬件衔接3) PCI9054与PCI插槽信号衔接PCI9054与PCI插槽间的衔接信号线,这些信号线包括地址数据复用信号AD[31:0],总线指令信号C/BE[3:0]和PCI协议控制信号PAR,FRAME,IRDY,TRDY,STOP,IDSEL,DEVSEL等,电路衔接中将彼此对应的信号线衔接在一起即可。

在PCI总线信号中.除了RST。

INTA-INTD之外,其他全部的信号都在始终升高沿被采样。

每个信号都有相对于时钟前沿建立和保持时光。

在此期间,不允许有信号的跳跃。

该时光一过,信号的变幻就无关紧要了。

这种建立和保持时光对于不同的信号其情形是不同的。

对于AD[31:0],PAR和IDSEL来说,惟独在一定的十种边沿上才有上述时光的要求。

对于LOCK,IRDY,TRDY.FRAME,DEVSEL,STOP,ⅢeQ,GNT,SERR和PERR这些信号在每个时钟前沿都有建立和保持时光。

对于C/BE[3:0]在传输总线指令是,要在FRAME 第一次建立时对应的时钟边沿上遵守建立和保持时光的关系。

若传输字节使能信号时,要在完成一个地址期或数据期之后的每一个时钟边沿保证相应的建立和保持时光。

4) PCI9054与EEPROM接口各种接口芯片都需要外接串行EEPROM芯片来加载配置数据.对于串行EEPROM芯片,需要按照接口芯片数据手册中给出的生产厂家及型号挑选。

这里挑选FM93LC56。

PCI9054提供4个管脚与串行EEPROM相衔接,他们分离是EEDI,EEDO,EESK,EECS,对应于FM93LC56的DI,DO,SkCS这四个管脚,这4对管脚挺直相连就可以,另外93Lc56的VCC 管脚需要接+5V电源,GND接地。

由于需要对串行EEPROM举行写操作,串行EEPROM应处于可编程而且非庇护状态,所以PE接高电平而PRE 接低电平。

FM93LC56的技术手册规定两个管脚上拉和下拉的应为10K 左右。