思考题与习题7-答案

- 格式:doc

- 大小:339.00 KB

- 文档页数:4

第1章思考题与习题1-1动力系统、电力系统和电力网的基本组成形式如何?1-2电力系统的接线方式有几种?何谓开式网络?何谓闭式网络?1-3简述电力系统运行特点和要求。

1-4如何评价电能质量,电能质量的三个指标是什么?各有怎样要求?1-5为什么要规定电力系统的电压等级?简述主要电压等级。

1-6电力系统的各个元件(设备)的额定电压如何确定?举例说明。

1-7电力系统的负荷曲线有几种?什么是年持续负荷曲线和最大负荷利用小时数?T。

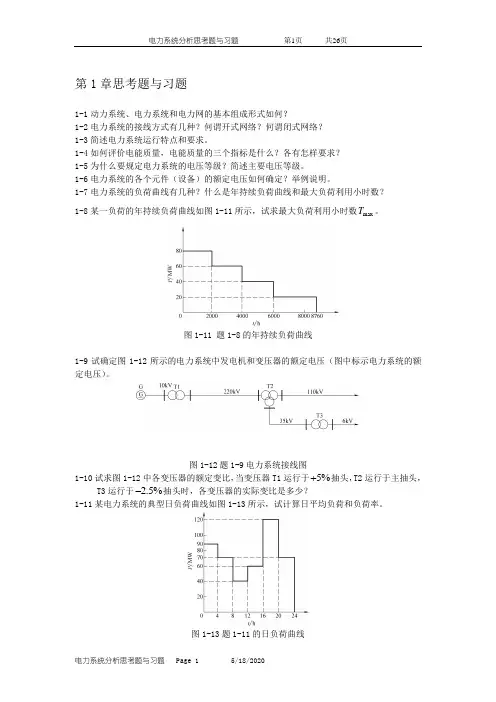

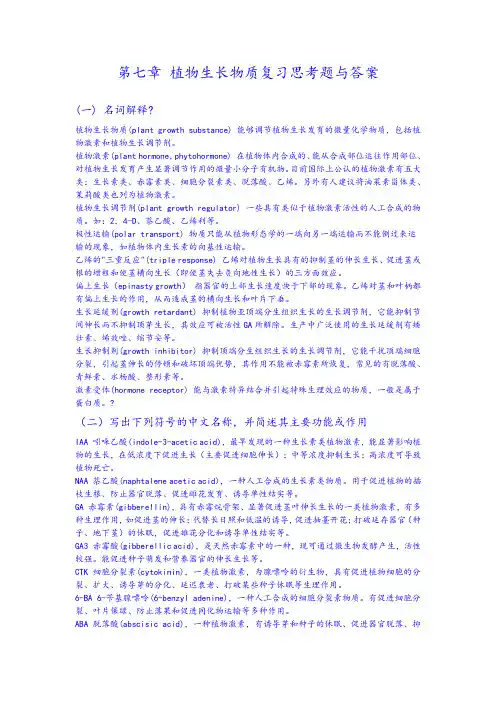

1-8某一负荷的年持续负荷曲线如图1-11所示,试求最大负荷利用小时数max图1-11 题1-8的年持续负荷曲线1-9试确定图1-12所示的电力系统中发电机和变压器的额定电压(图中标示电力系统的额定电压)。

图1-12题1-9电力系统接线图+抽头,T2运行于主抽头,1-10试求图1-12中各变压器的额定变比,当变压器T1运行于5%-抽头时,各变压器的实际变比是多少?T3运行于 2.5%1-11某电力系统的典型日负荷曲线如图1-13所示,试计算日平均负荷和负荷率。

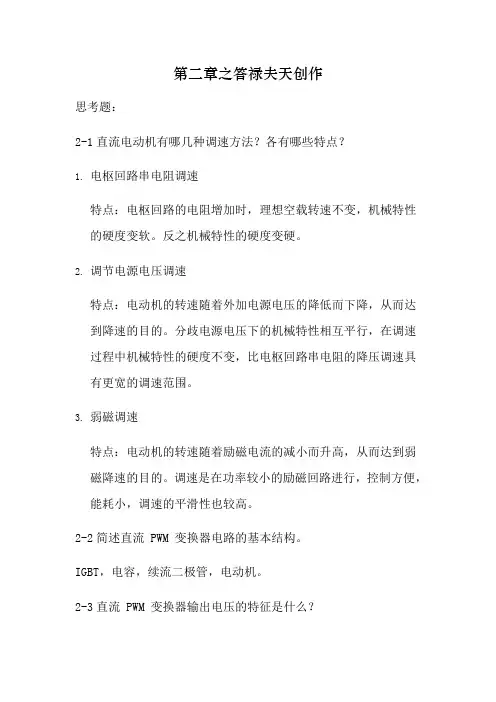

图1-13题1-11的日负荷曲线第2章思考题与习题2-1 架空输电线路的电阻、电抗、电纳和电导是如何计算的,影响电抗的参数的主要因素是什么?2-1 架空线路采用分裂导线有哪些优点?电力线路一般采用什么样的等效电路表示? 2-3 何谓自然功率?2-4 双绕组和三绕组变压器一般以什么样等值电路表示?2-5 对于升压型和降压型的变压器,如果所给出的其他原始数据均相同,它们的参数相同吗?为什么?2-7 什么称为变压器的额定变比、实际变比、平均额定电压变比,在归算中如何应用? 2-8 何谓有名值?何谓标幺制?标幺制有什么优缺点?基准值如何选取? 2-9 电力系统等值电路的元件参数计算时,何谓精确计算法?何谓近似计算法?它们分别用在怎样的场合?2-10 试推导由负荷功率求取恒定负荷阻抗或导纳的方法。

2-11 一条长度为600km 的500kV 架空线路,使用4×LGJ-400分裂导线,611110.01870.275 4.05100r x km b S km g -=Ω=Ω=⨯=、、、。

第七章植物生长物质复习思考题与答案(一) 名词解释?植物生长物质(plant growth substance) 能够调节植物生长发育的微量化学物质,包括植物激素和植物生长调节剂。

植物激素(plant hormone,phytohormone) 在植物体内合成的、能从合成部位运往作用部位、对植物生长发育产生显著调节作用的微量小分子有机物。

目前国际上公认的植物激素有五大类:生长素类、赤霉素类、细胞分裂素类、脱落酸、乙烯。

另外有人建议将油菜素甾体类、茉莉酸类也列为植物激素。

植物生长调节剂(plant growth regulator) 一些具有类似于植物激素活性的人工合成的物质。

如:2,4-D、萘乙酸、乙烯利等。

极性运输(polar transport) 物质只能从植物形态学的一端向另一端运输而不能倒过来运输的现象,如植物体内生长素的向基性运输。

乙烯的"三重反应"(triple response) 乙烯对植物生长具有的抑制茎的伸长生长、促进茎或根的增粗和使茎横向生长(即使茎失去负向地性生长)的三方面效应。

偏上生长(epinasty growth)指器官的上部生长速度快于下部的现象。

乙烯对茎和叶柄都有偏上生长的作用,从而造成茎的横向生长和叶片下垂。

生长延缓剂(growth retardant) 抑制植物亚顶端分生组织生长的生长调节剂,它能抑制节间伸长而不抑制顶芽生长,其效应可被活性GA所解除。

生产中广泛使用的生长延缓剂有矮壮素、烯效唑、缩节安等。

生长抑制剂(growth inhibitor) 抑制顶端分生组织生长的生长调节剂,它能干扰顶端细胞分裂,引起茎伸长的停顿和破坏顶端优势,其作用不能被赤霉素所恢复,常见的有脱落酸、青鲜素、水杨酸、整形素等。

激素受体(hormone receptor) 能与激素特异结合并引起特殊生理效应的物质,一般是属于蛋白质。

?(二)写出下列符号的中文名称,并简述其主要功能或作用IAA 吲哚乙酸(indole-3-acetic acid),最早发现的一种生长素类植物激素,能显著影响植物的生长,在低浓度下促进生长(主要促进细胞伸长);中等浓度抑制生长;高浓度可导致植物死亡。

第二章之答禄夫天创作思考题:2-1直流电动机有哪几种调速方法?各有哪些特点?1.电枢回路串电阻调速特点:电枢回路的电阻增加时,理想空载转速不变,机械特性的硬度变软。

反之机械特性的硬度变硬。

2.调节电源电压调速特点:电动机的转速随着外加电源电压的降低而下降,从而达到降速的目的。

分歧电源电压下的机械特性相互平行,在调速过程中机械特性的硬度不变,比电枢回路串电阻的降压调速具有更宽的调速范围。

3.弱磁调速特点:电动机的转速随着励磁电流的减小而升高,从而达到弱磁降速的目的。

调速是在功率较小的励磁回路进行,控制方便,能耗小,调速的平滑性也较高。

2-2简述直流 PWM 变换器电路的基本结构。

IGBT,电容,续流二极管,电动机。

2-3直流 PWM 变换器输出电压的特征是什么?直流电压2-4为什么直流PWM变换器-电动机系统比V-M系统能够获得更好的动态性能?直流PWM变换器-电动机系统比V-M系统开关频率高,电流容易连续,谐波少,电动机损耗及发热都较小;低速性能好,稳速精度高,调速范围宽;若与快速响应的电动机配合,则系统频带宽,动态响应快,动态抗扰能力强;电力电子开关器件工作在开关状态,导通损耗小,当开关频率适中时,开关损耗也不大,因而装置效率较高;直流电源采取不控整流时,电网功率因数比相控整流器高。

2-5在直流脉宽调速系统中,当电动机停止不动时,电枢两端是否还有电压?电路中是否还有电流?为什么?电枢两端还有电压,因为在直流脉宽调速系统中,电动机电枢两端电压仅取决于直流。

电路中无电流,因为电动机处已断开,构不成通路。

2-6直流PWM变换器主电路中反并联二极管有何作用?如果二极管断路会发生什么后果?反并联二极管是续流作用。

若没有反并联二极管,则IGBT的门极控制电压为负时,无法完成续流,导致电动机电枢电压不近似为零。

2-7直流 PWM 变换器的开关频率是否越高越好?为什么?不是越高越好,因为太高的话可能出现电容还没充完电就IGBT关断了,达不到需要的输出电压。

思考题与习题解马西芹第一章、思考题与习题1、检测系统由哪几部分组成?说明各部分的作用。

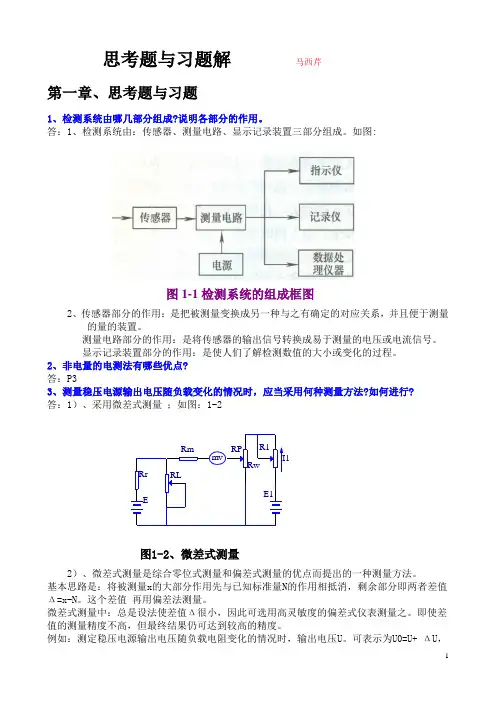

答:1、检测系统由:传感器、测量电路、显示记录装置三部分组成。

如图:图1-1检测系统的组成框图2、传感器部分的作用:是把被测量变换成另一种与之有确定的对应关系,并且便于测量的量的装置。

测量电路部分的作用:是将传感器的输出信号转换成易于测量的电压或电流信号。

显示记录装置部分的作用:是使人们了解检测数值的大小或变化的过程。

2、非电量的电测法有哪些优点?答:P33、测量稳压电源输出电压随负载变化的情况时,应当采用何种测量方法?如何进行?答:1)、采用微差式测量;如图:1-2图1-2、微差式测量2)、微差式测量是综合零位式测量和偏差式测量的优点而提出的一种测量方法。

基本思路是:将被测量x的大部分作用先与已知标准量N的作用相抵消,剩余部分即两者差值Δ=x-N。

这个差值再用偏差法测量。

微差式测量中:总是设法使差值Δ很小,因此可选用高灵敏度的偏差式仪表测量之。

即使差值的测量精度不高,但最终结果仍可达到较高的精度。

例如:测定稳压电源输出电压随负载电阻变化的情况时,输出电压U。

可表示为U0=U+ ΔU,其中ΔU 是负载电阻变化所引起的输出电压变化量,相对U 来讲为一小量。

如果采用偏差法测 量,仪表必须有较大量程以满足U 。

的要求,因此对ΔU 这个小量造成的U0的变化就很难测准。

当然,可以改用零位式测量,但最好的方法是采用如图1-3所示的微差式测量。

微差式测量:⑴、微差式测量电路图中;①、使用了高灵敏度电压表:毫伏表和电位差计; ②、Rr 和E 分别表示稳压电源的内阻和电动势; ③、RL 表示稳压电源的负载;④、E1、R1和Rw 表示电位差计的参数。

⑵、微差式测量过程①、在测量前调整R1,使电位差计工作电流I1为标准值。

②、然后使稳压电压负载电阻RL 为额定值,调整RP 的活动触点,使毫伏表指示为零,这相当于事先用零位式测量出额定输出电压U 。

模拟电路课后习题答案 Final approval draft on November 22, 2020第七章 习题与思考题◆◆ 习题 7-1 在图P7-1所示的放大电路中,已知R 1=R 2=R 5=R 7=R 8=10k Ω,R 6=R 9=R 10=20k Ω:① 试问R 3和R 4分别应选用多大的电阻; ② 列出u o1、u o2和u o 的表达式;③ 设u I1=3V ,u I2=1V ,则输出电压u o =解:① Ω=Ω==k k R R R 5)10//10(//213,Ω≈Ω==k k R R R 67.6)20//10(//654 ② 1111211010I I I o u u u R R u -=-=-=,2226525.1)20101()1(I I I o u u u R R u =+=+=, ③ V V u u u I I o 9)1332(3221=⨯+⨯=+=本题的意图是掌握反相输入、同相输入、差分输入比例运算电路的工作原理,估算三种比例电路的输入输出关系。

◆◆ 习题 7-2 在图P7-2所示电路中,写出其输出电压u O 的表达式。

解:本题的意图是掌握反相输入和同相输入比例 电路的输入、输出关系。

◆◆ 习题 7-3 试证明图P7-3中,)(11221I I o u u R R u -=)+(解:◆◆ 解:◆◆ 解:◆◆ 习题 7-6 试设计一个比例运算放大器,实现以下运算关系:u O =。

请要求画出电路原理图,并估算各电阻的阻值。

希望所用电阻的阻抗在20k Ω至200k Ω的范围内。

解:上图为实现本题目要求的一种设计方案,使5.0)1()5.0(21=-⨯-=⋅=uf uf uf A A A ,即I O u u 5.0=。

本题的意图是在深入掌握各种比例运算电路性能的基础上,采用适当电路实现给定的运算关系。

以上只是设计方案之一。

◆◆ 习题 7-71为阻值在1k Ω~10k Ω之间可调的电位器,R 2=R 3=20k Ω,R 4=R 5=33k Ω,R 6=R 7=100k Ω,试估算电路的输出电压与输入电压之间的比例系数的可调范围。

第7章 多组定量资料的比较思考与练习参考答案一、最佳选择题1. 完全随机设计资料的方差分析中,必然有( C )。

A. 组间SS >组内SSB. 组内组间总MS MS MS +=C. 总ss=组间SS +组内SSD. 组内组间MS MS >E. 组间组内νν> 2. 定量资料两样本均数的比较,可采用( D )。

A. t 检验B.F 检验C. Bonferroni 检验D. t 检验与F 检验均可E. LSD 检验3. 当组数等于2时,对于同一资料,方差分析结果与t 检验结果相比,( C )。

A. t 检验结果更为准确B. 方差分析结果更为准确C. 完全等价且F t =D. 完全等价且t F =E. 两者结果可能出现矛盾4. 若单因素方差分析结果为),(01.021ννF F >,则统计推断是( D )。

A. 各样本均数都不相等B. 各样本均数不全相等C. 各总体均数都不相等D. 各总体均数不全相等E. 各总体均数全相等 5. 完全随机设计资料的方差分析中,组间均方表示( C )。

A. 抽样误差的大小B. 处理效应的大小C. 处理效应和抽样误差综合结果D. N 个数据的离散程度E. 随机因素的效应大小 6. 多样本定量资料比较,当分布类型不清时应选择( D )。

A. 方差分析B. t 检验C. Z 检验D. Kruskal-Wallis 检验E. Wilcoxon 检验 7. 多组样本比较的Kruskal-Wallis 检验中,当相同秩次较多时,如果用H 值而不用校正后的c H 值,则会( C )。

A . 提高检验的灵敏度B .把一些无差别的总体推断成有差别 C. 把一些有差别的总体推断成无差别D.Ⅰ、Ⅱ类错误概率不变E. 以上说法均不对二、思考题1. 方差分析的基本思想和应用条件是什么?答:方差分析的基本思想是,对于不同设计的方差分析,其思想都一样,即均将处理间平均变异与误差平均变异比较。

《单片机原理及接口技术》(第2版)人民邮电出版社第7章 AT89S51单片机的串行口思考题及习题71.帧格式为1个起始位,8个数据位和1个停止位的异步串行通信方式是方式。

答:方式1。

2.在串行通信中,收发双方对波特率的设定应该是的。

答:相等的。

3.下列选项中,是正确的。

A.串行口通信的第9数据位的功能可由用户定义。

对B.发送数据的第9数据位的内容是在SCON寄存器的TB8位中预先准备好的。

对C.串行通信帧发送时,指令把TB8位的状态送入发送SBUF中。

错D.串行通信接收到的第9位数据送SCON寄存器的RB8中保存。

对E.串行口方式1的波特率是可变的,通过定时器/计数器T1的溢出率设定。

对4.通过串行口发送或接收数据时,在程序中应使用。

A.MOVC指令B.MOVX指令 C.MOV指令 D.XCHD指令答:C5.串行口工作方式1的波特率是。

A.固定的,为f osc/32 B.固定的,为f osc/16C.可变的,通过定时器/计数器T1的溢出率设定D.固定的,为f osc/64答:C6.在异步串行通信中,接收方是如何知道发送方开始发送数据的?答:当接收方检测到RXD端从1到0的跳变时就启动检测器,接收的值是3次连续采样,取其中2次相同的值,以确认是否是真正的起始位的开始,这样能较好地消除干扰引起的影响,以保证可靠无误的开始接受数据。

7.AT89S51单片机的串行口有几种工作方式?有几种帧格式?各种工作方式的波特率如何确定?答:串行口有4种工作方式:方式0、方式1、方式2、方式3;有3种帧格式,方式2和3具有相同的帧格式;方式0的发送和接收都以fosc/12为固定波特率,方式1的波特率=2SMOD /32×定时器T1的溢出率方式2的波特率=2SMOD /64×fosc方式3的波特率=2SMOD /32×定时器T1的溢出率8.假定串行口串行发送的字符格式为1个起始位、8个数据位、1个奇校验位、1个停止位,请画出传送字符“B ”的帧格式。

思考题与习题绪论一、填空1 同一台设备的设计可能有多种方案,通常要用()来确定最终的方案.2 单元操作中常用的五个基本概念包括( )、()、()、( )和()。

3 奶粉的生产主要包括()、()、()、( )、()等单元操作.二、简答1 什么是单元操作?食品加工中常用的单元操作有哪些?2 “三传理论”是指什么?与单元操作有什么关系?3 如何理解单元操作中常用的五个基本概念?4 举例说明三传理论在实际工作中的应用。

5 简述食品工程原理在食品工业中的作用、地位.三、计算1 将5kg得蔗糖溶解在20kg的水中,试计算溶液的浓度,分别用质量分数、摩尔分数、摩尔浓度表示。

已知20%蔗糖溶液的密度为1070kg/m3。

2 在含盐黄油生产过程中,将60%(质量分数)的食盐溶液添加到黄油中。

最终产品的水分含量为15。

8%,含盐量1.4%,试计算原料黄油中含水量.3 将固形物含量为7。

08%的鲜橘汁引入真空蒸发器进行浓缩,得固形物含量为58%得浓橘汁。

若鲜橘汁进料流量为1000kg/h,计算生产浓橘汁和蒸出水的量。

4 在空气预热器中用蒸气将流量1000kg/h,30℃的空气预热至66℃,所用加热蒸气温度143。

4℃,离开预热器的温度为138。

8℃。

求蒸气消耗量。

5 在碳酸饮料的生产过程中,已知在0℃和1atm下,1体积的水可以溶解3体积的二氧化碳。

试计算该饮料中CO2的(1)质量分数;(2)摩尔分数。

忽略CO2和水以外的任何组分。

6 采用发酵罐连续发酵生产酵母。

20m3发酵灌内发酵液流体发酵时间为16h。

初始接种物中含有1.2%的酵母细胞,将其稀释成2%菌悬液接种到发酵灌中。

在发酵罐内,酵母以每2.9h 增长一倍的生长速度稳定增长。

从发酵罐中流出的发酵液进入连续离心分离器中,生产出来的酵母悬浮液含有7%的酵母,占发酵液中总酵母的97%。

试计算从离心机中分离出来的酵母悬浮液的流量F以及残留发酵液的流量W(假设发酵液的密度为1000kg/m3)。

《马克思主义与社会科学方法论》1-7章思考题答案《马克思主义与社会科学方法论》1-7章思考题答案导论1.如何理解社会认识与社会科学方法论的演变逻辑?社会认识即人类认识社会的主要方式,社会科学方法论即研究社会历史的方法论。

一、总体来说,社会认识与社会科学方法论的演变逻辑为:马克思主义产生之前的各种社会认识和社会理论,在总体是唯心主义的,陷入了唯心史观,即用社会意识去解释社会存在。

原因在于生产规模的狭小、阶级立场的局限。

马克思主义主张,研究社会历史必须研究社会赖以生存的物质条件,并根据这种物质生活条件说明政治、法律、美学、哲学、宗教等观点,即用社会存在去解释社会意识,而不是相反。

这样,马克思主义的唯物史观创立了。

唯物史观为研究社会历史指明了方向,提供了科学的方法论指导,在社会历史研究中实现了革命性的革命。

二、社会认识的演变逻辑为:唯心主义——唯物主义——辩证唯物主义(即马克思主义社会认识论);自发——自觉,具体来说,神话传说(原始社会自发认识)——非理性方式(第一种自觉形式)——理性求知(批判性的)、实证方式(发展性的)、非理性方式。

三、社会科学方法论的演变逻辑为:形而上学——辩证法——唯物辩证法(即马克思主义社会科学方法论,包括:实践的、辩证的历史唯物主义哲学,剩余价值论,创立了科学社会主义学说,阶级和阶级斗争学说。

)2.如何理解社会科学方法论的性质和特点?方法是主体依据对客体发展规律的认识而为自己规定的活动方式和行为准则,是人们实现特定目的的手段或途径,是主体接近、把握以至改造客体的工具或桥梁。

方法论是关于方法的理论,它以多种多样的方法为研究对象,探讨方法的基本原理和基本原则,为人们正确认识事物、评价事物和改造事物指明方向。

方法论具有不同的层次,如哲学方法论、科学方法论、技术方法论等。

社会科学方法论是从事科学研究的方法论,它是对各门具体社会科学研究方法的概括和总结,因而对各门社会科学研究具有普遍的指导意义。

河海⼤学_⼟⼒学_课后习题思考题答案河海⼟⼒学课后习题与答案第⼀章思考题11-1 什么叫⼟?⼟是怎样形成的?粗粒⼟和细粒⼟的组成有何不同?1-2 什么叫残积⼟?什么叫运积⼟?他们各有什么特征?1-3 何谓⼟的级配?⼟的粒径分布曲线是怎样绘制的?为什么粒径分布曲线⽤半对数坐标?1-4 何谓⼟的结构?⼟的结构有哪⼏种类型?它们各有什么特征?1-5 ⼟的粒径分布曲线的特征可以⽤哪两个系数来表⽰?它们定义⼜如何?1-6 如何利⽤⼟的粒径分布曲线来判断⼟的级配的好坏?1-7 什么是吸着⽔?具有哪些特征?1-8 什么叫⾃由⽔?⾃由⽔可以分为哪两种?1-9 什么叫重⼒⽔?它有哪些特征?1-10 ⼟中的⽓体以哪⼏种形式存在?它们对⼟的⼯程性质有何影响?1-11 什么叫的物理性质指标是怎样定义的?其中哪三个是基本指标?1-12 什么叫砂⼟的相对密实度?有何⽤途?1-13 何谓粘性⼟的稠度?粘性⼟随着含⽔率的不同可分为⼏种状态?各有何特性?1-14 何谓塑性指数和液性指数?有何⽤途?1-15 何谓⼟的压实性?⼟压实的⽬的是什么?1-16 ⼟的压实性与哪些因素有关?何谓⼟的最⼤⼲密度和最优含⽔率?1-17 ⼟的⼯程分类的⽬的是什么?1-18 什么是粗粒⼟?什么叫细粒⼟?习题11-1有A、B两个图样,通过室内实验测得其粒径与⼩于该粒径的⼟粒质量如下表所⽰,试绘出它们的粒径分布曲线并求出C和c C值。

uA⼟样实验资料(总质量500g)得其质量为15.3g,烘⼲后质量为10.6g,⼟粒⽐重为2.70,求试样的含⽔率、孔隙⽐、孔隙率、饱和密度、浮密度、⼲密度及其相应的重度。

1-3 某⼟样的含⽔率为6.0%密度为1.60 3g/cm,⼟粒⽐重为2.70,若设孔隙⽐不变,为使⼟样完全饱和,问100 3cm⼟样中应该加多少⽔?1-4 有⼟料1000g,它的含⽔率为6.0%,若使它的含⽔率增加到16.0%,问需要加多少⽔?1-5 有⼀砂⼟层,测得其天然密度为1.773g/cm ,天然含⽔率为9.8%,⼟的⽐重为2.70,烘⼲后测得最⼩孔隙⽐为0.46,最⼤孔隙⽐为0.94,试求天然孔隙⽐e 、饱和含⽔率和相对密实度D ,并判别该砂⼟层处于何种密实状态。

思考题与习题参考答案绪论一、填空1、经济核算2、物料衡算、经济核算、能量核算、物系的平衡关系、传递速率3、液体输送、离心沉降、混合、热交换、蒸发、喷雾干燥二、简答1、在食品工程原理中,将这些用于食品生产工艺过程所共有的基本物理操作过程成为单元操作。

例如,奶粉的加工从原料乳的验收开始,需要经过预热杀菌、调配、真空浓缩、过滤、喷雾干燥等过程;再如,酱油的加工,也包含大豆的浸泡、加热、杀菌、过滤等工序,这两种产品的原料、产品形式、加工工艺都有较大的不同,但却包含了流体的输送、物质的分离、加热等相同的物理操作过程。

2、“三传理论”即动量传递、热量传递和质量传递。

(1)动量传递理论。

随着对单元操作的不断深入研究,人们认识到流体流动是一种动量传递现象,也就是流体在流动过程中,其内部发生动量传递。

所以凡是遵循流体流动基本规律的单元操作都可以用动量传递理论去研究。

(2)热量传递理论。

物体在加热或者冷却的过程中都伴随着热量的传递。

凡是遵循传热基本规律的单元操作都可以用热量传递的理论去研究。

(3)质量传递理论。

两相间物质的传递过程即为质量传递。

凡是遵循传质基本规律的单元操作都可以用质量传递的理论去研究。

例如,啤酒的灭菌(热量传递),麦芽的制备(动量传递,热量传递,质量传递)等。

三传理论是单元操作的理论基础,单元操作是三传理论具体应用。

3、单元操作中常用的基本概念有物料衡算、能量衡算、物系的平衡关系、传递速率和经济核算。

物料衡算遵循质量守恒定律,是指对于一个生产加工过程,输入的物料总量必定等于输出的物料总质量与积累物料质量之和。

能量衡算的依据是能量守恒定律,进入过程的热量等于离开的热量和热量损失之和。

平衡状态是自然界中广泛存在的现象。

平衡关系可用来判断过程能否进行,以及进行的方向和能达到的限度。

过程的传递速率是决定化工设备的重要因素,传递速率增大时,设备尺寸可以减小。

为生产定量的某种产品所需要的设备,根据设备的型式和材料的不同,可以有若干设计方案。

第一章 习题参考答案 1-1 略 1-2C O H H H C C OH H (1)(2)H(3)sp 3sp 3 sp 2C NH H H H C C H H H ⋯⋯N (4)(5)C C HHH ⋯⋯N O sp 3 sp 3sp sp 3 sp1-3 C 18H 11NO 21-4 (A): c < b < a; (B): c < b < a; (C): b < a < c1-5有机化合物氧原子具有未共享电子对,表现为碱,与质子结合,从而溶于冷的浓硫酸。

加水稀释后,释放出硫酸,又得到原来的化合物。

以乙醚为例:O+ H 2SO 4O + HSO 4H+ HSO 4HH OO+ H 2SO 41-6 (1) CH 3CH 2OH (2) CH 3CH 2O - (3) CH 3CH 2S - (4) HCOO -(5)H 2PO 4-(6) I -(7) (CH 3)2N -(8) HO -(9) H 2O (10) NH 31-7 写出下列碱的共轭酸。

(1) O H(2) HF (3) C 2H 5OH (4) H 3O + (5) (CH 3)2NH 2+1-8 Lewis 酸BF 3,ZnCl 2,AlCl 3; Lewis 碱CH 3CH 2OH ,CH 3CH 2OCH 2CH 3,NH 3,H-C ≡C -,C 2H 5O -,CH 3SCH 3,H 2C =CH 2 1-9 A: CHCl 3 > CH 2Cl 2 > CH 3Cl > CCl 4HCl H HHCl Cl H HCl HCl B:<<1-10N ON OS S ON OON OON OO第二章 习题参考答案 2-1(1)3-甲基-4-乙基庚烷;(2)2-甲基-4-异丙基己烷;(3)新壬烷;(4)2-甲基-5-乙基庚烷 (5)2-甲基-3-丙基己烷;(6)4-叔丁基辛烷;2-2 (1)(2)CH 3CHCHCH 3H 3CCH 3C CH 2CH 3CH 3CH 3H 3C (3)CH 3CHCH2CH 2CH 3CH32-3(1)庚烷(2)2-甲基己烷(3)(4)(5)(6)(7)(8)(9)3-甲基己烷2, 2-二甲基戊烷3, 3-二甲基戊烷2, 3-二甲基戊烷2, 4-二甲基戊烷3-乙基戊烷2, 2, 3-三甲基丁烷2-4CH 3—C —CH 2—CH —CH 2—CH 3CH 3CH 3CH 31°2°3°2°4°1°1°1°1°2-5 该化合物分子式为C 8H 18,结构式 命名为:2,2,3,3-四甲基丁烷 2-6 化合物沸点依次降低顺序:(4)>(2)>(3)>(5)>(1)H 3CH 3CC C CH 3CH 3H3CCH 3(7) (CH 3)2CHCH 2CH 3(8) (CH 3)2CHCHCH 2CH 2 CCH 2CH 3CH 2CH 3CH 3CH 2CH 3(9)(10)2-7 熔点:(1)>(2);沸点:(1)<(2) 2-8 稳定性大小:(1)>(3)>(2)>(4)2-9 1,2-二溴乙烷的四种典型构象式(从左到右稳定性依次降低)H HBr H H BrH H H HBrH H H HHHBr HBrH BrBr对位交叉式邻位交叉式 部分重叠式 全重叠式3, 4-二甲基己烷的优势构象为:2-10链引发:Cl 22Cl •链增长:Cl •+Cl•+ HCl•+ Cl 2Cl •+链终止:Cl •Cl •+Cl 2•Cl •+Cl•+•2-11 主要的原因是:甲基环己烷分子结构中有1个3º H ,10个2º H ,3个1º H ,进行溴代CH 3Br25反应时,不同类型氢原子的反应活性大小是3º H ∶2º H ∶1º H = 1600∶82∶1,可以初步计算出3º H 被溴取代后的产物所占百分比例大约是66%,因此反应主要得到 2-13 该化合物为: Cl 2++ HClC C H 3C H 3C H 3C CH 3CH 3CH 3C C H 3C H 3C H 3C CH 3CH 3CH 2Cl第三章 习题参考答案 3-1(1)甲基环戊烷 (2)1-甲基-4-乙基环己烷 (3)2-甲基-3-环丙基-6-环丁基辛烷 (4)反-1-甲基-2-异丙基环丁烷 (5)1-甲基-3-环戊基环己烷 (6)2-甲基-8-乙基螺[4.5]癸烷 (7)2, 7, 7-三甲基二环[4.1.0]庚烷 (8)二环[3.3.3]十一烷(9)1-甲基二环[2.2.2]辛烷(10) (11) (12) (13)3-2 该烃分子可能为下列化合物之一:甲基环己烷 乙基环戊烷 丙基环丁烷 丁基环丙烷 3-3(1)2) H 2OBrBr CH 2BrOHC C H 3C H 3C H 3C CH 3CH 3CH 3(2)HBrBr3-4顺-1-甲基-4-丙基环己烷的椅式构象式 反-1-甲基-4-丙基环己烷的椅式构象式CH 3C(CH 3)3H 3CC(CH 3)3CH 3C(CH 3)3C(CH 3)3CH 3最优势构象 3-5(1)CH 3H 3CC(CH 3)3(2) CH 3C 2H 5CH 3(3)CH 3(4) C(CH 3)3C 2H 5(5)C 2H 5C 2H 5H 5C 23-6 3, 4-二溴-1-叔丁基环己烷可能的构象异构体如下:C(CH 3)3C(CH 3)3Br BrC(CH 3)3BrBr C(CH 3)3BrBrC(CH 3)3Br BrBrBr C(CH 3)3BrBrC(CH 3)3BrBrC(CH 3)3BrBr3-7 化合物A 是: 化合物B 是: Br反应式:溴水褪色BrCH2BrBr3-8溴 水褪 色褪 色无变化无变化褪 色3-9 反-1,2-二甲基环己烷采用ee 构象时,亚甲基和甲基是处在对位交叉式,分子内能较小;而在aa 构象中,亚甲基和甲基是处在邻位交叉式,分子扭转张力相对比较大,同时由于1,3-竖键作用,空间张力大。

资料范本本资料为word版本,可以直接编辑和打印,感谢您的下载有机化学第7、8章习题答案地点:__________________时间:__________________说明:本资料适用于约定双方经过谈判,协商而共同承认,共同遵守的责任与义务,仅供参考,文档可直接下载或修改,不需要的部分可直接删除,使用时请详细阅读内容第7章芳烃及非苯芳烃思考题答案思考题7-1 苯具有什么结构特征? 它与早期的有机化学理论有什么矛盾?答案:苯分子具有高度的不饱和性,其碳氢比相当于同分子量的炔烃,根据早期的有机化学理论,它应具有容易发生加成反应、氧化反应等特性。

但事实上,苯是一种高度不饱和却具异常稳定性的化合物。

因此,要能够很好地解释这一矛盾是当时有机化学家所面临的重大挑战。

[知识点:苯的结构特征]思考题7-2早期的有机化学家对苯的芳香性认识与现代有机化学家对苯的芳香性认识有什么不同?答案:早期的有机化学把那些高度不饱和的苯环类结构并具有芳香气味的化合物称为芳香化合物,这些化合物所具有的特性具称为芳香性。

随着对事物认识的不断深入,人们已经意识到,除了苯环以外还有一些其他类型的分子结构也具有如苯一样的特别性质。

现在仍然迫用芳香性概念,但其内涵已超出了原来的定义范围。

现在对芳香性的定义为:化学结构上环状封闭的共轭大π键,不易被氧化,也不易发生加成反应,但是容易起亲电反应的性质。

[知识点:苯的芳香性]思考题7-3 关于苯分子的近代结构理论有哪些?其中,由Pauling提出的共振结构理论是如何解释苯分子结构?答案:现代价键理论:苯分子中的六个碳原子都以sp2杂化轨道和相邻的碳和氢原子形成σ键,此sp2杂化轨道为平面其对称轴夹角为120°,此外每个碳原子还有一个和平面垂直的p轨道,六个p轨道相互平行重叠形成了一个闭合共轭体系。

分子轨道理论:基态时,苯分子的六个π电子都处在成建轨道上,具有闭壳层电子结构。

离域的π电子使得所有的C-C键都相同,具有大π键的特殊性质因此相比孤立π键要稳定得多。

第七章直流斩波电路习题与思考题解7-1.DC/DC变换电路的主要形式和工作特点是什么?解:.DC/DC变换器有两种主要的形式,一种是逆变整流型,另一种是斩波电路控制型。

逆变整流型是将直流电压逆变成一个固定的高频交流电压,将这个交流电压经变压器变为要求的交流电压,再整流成所需要的直流电压。

逆变电路一般采用恒压恒频控制,它适用于小功率的电源变换和变压比较大的变换中。

斩波电路控制型可选用多种脉冲调制方式做为控制输入,适用于不需要隔离的场合和升压、降压比不大的场合。

7-2.试述斩波电路的主要功能。

解:直流斩波电路是一种直流/直流(DC/DC)变换电路,其主要功能是通过控制直流电源的通和断,来实现对负载上的平均电压和功率进行控制,即所谓调压调功功能。

7-3.斩波电路常用的三种控制方式是什么?解:斩波电路常用的三种控制方式是:(1)时间比控制方式;(2)瞬时值控制方式;(3)时间比和瞬时值结合的控制方式。

7-4.试述斩波电路时间比控制方式中的三种控制模式。

解:斩波电路时间比控制方式中的三种控制模式为:(1)定频调宽控制模式定频就是指开关元件的开、关频率固定不变,也就是开、关周期T固定不变,调宽是指通过改变斩波电路的开关元件导通的时间T on来改变导通比K t值,从而改变输出电压的平均值。

(2)定宽调频控制模式定宽就是斩波电路的开关元件的导通时间T on固定不变,调频是指用改变开关元件的开关周期T来改变导通比K t。

(3)调频调宽混合控制模式这种方式是前两种控制方式的综合,是指在控制驱动的过程中,即改变开关周期T,又改变斩波电路导通时间T on的控制方式。

通常用于需要大幅度改变输出电压数值的场合.7-5.试述降压型斩波电路的工作原理,如果电路中U d =100V ,K t =0.5,求输出电压值? 解:降压型斩波电路的输出平均直流电压低于电源输入的直流电压,电路原理结构及工作波形参阅教材P117中的图7-8。

第七章 思考题1. 什么情况下必须采用多级压缩?多级活塞式压缩机为什么必须采用级间冷却? 答:为进一步提高终压和限制终温,必须采用多级压缩。

和绝热压缩及多变压缩相比,定温压缩过程,压气机的耗功最小,压缩终了的气体温度最低,所以趋近定温压缩是改善压缩过程的主要方向,而采用分级压缩、中间冷却是其中一种有效的措施。

采用此方法,同样的压缩比,耗功量比单级压缩少,且压缩终温低,温度过高会使气缸里面的润滑油升温过高而碳化变质。

理论上,分级越多,就越趋向于定温压缩,但是无限分级会使系统太复杂,实际上通常采用2-4级。

同时至于使气缸里面的润滑油升温过高而碳化变质,必须采用级间冷却。

2. 从示功图上看,单纯的定温压缩过程比多变或绝热压缩过程要多消耗功,为什么还说压气机采用定温压缩最省功?答:这里说的功是技术功,而不是体积功,因为压缩过程是可看作稳定流动过程,不是闭口系统,在p-v 图上要看吸气、压缩和排气过程和p 轴围成的面积,不是和v 轴围成的面积。

3. 既然余隙不增加压气机的耗功量,为什么还要设法减小它呢?答:有余隙容积时,虽然理论压气功不变,但是进气量减少,气缸容积不能充分利用,当压缩同量的气体时,必须采用气缸较大的机器,而且这一有害的余隙影响还随着增压比的增大而增加,所以应该尽量减小余隙容积。

4. 空气压缩制冷循环能否用节流阀代替膨胀机,为什么?答:蒸汽制冷循环所以采用节流阀代替膨胀机,是因为液体的膨胀功很小,也就是说液体的节流损失是很小的,而采用节流阀代替膨胀机,成本节省很多,但是对于空气来说,膨胀功比液体大的多,同时用节流阀使空气的熵值增加很大,从T-s 图上可以看出,这样使吸热量减少,制冷系数减少。

5. 绝热节流过程有什么特点?答:缩口附近流动情况复杂且不稳定,但在缩口前后一定距离的截面处,流体的流态保持不变,两个截面的焓相等。

对于理想气体,绝热节流前后温度不变。

6. 如图7-15(b)所示,若蒸汽压缩制冷循环按351212' 运行,循环耗功量没有变化,仍为h 2-h 1,而制冷量则由h 1-h 4增大为h 1-h 5,这显然是有利的,但为什么没有被采用? 答:如果按351212'运行,很难控制工质状态,因此采用节流阀,经济实用。

加行第7课课后思考题参考答案全部1、古往今来,很多人竭尽所能、不惜一切,去追求长生不老。

你对这种现象如何看待?请说明理由。

答:即使是天王,最终也逃一死。

世人追求的道教之长生不老、仙人之永恒不死,也只不过是时间长短而已,实际上都不能不死。

《功德藏》亦云:?梵帝自在转轮王,无法摆脱死主魔。

?我们也可以想一想,再过一百年,自己还有多少会留在人间?其实,死亡对我们来说并不遥远,尽管每个人都贪生怕死,但也没有办法,因为无常的本性即是如此。

2、我们观修无常方面,跟古大德比起来有何差距?你认为这主要是什么原因导致的?答:象一些古大德,他们一辈子想的都是佛法,不图名也不求利,毕生中一直认真修行。

可我们现在不是这样,很多人对世间的执著特别强,口头上说要修行佛法,实则无法摆脱各种诱惑。

在我们汉地有一位xx大师(即清凉国师),他曾在生前发了十大愿:一、长期依止一丈四方之室,除了三衣一钵,不留任何财物;二、对名利犹如鼻涕般抛弃;三、目不视女人;四、不到在家人的家里走动;五、长期诵《法华经》;六、长期读诵大乘经典,普济群生;七、常宣讲《华严经》;八、一生昼夜不卧;九、不为虚名而欺惑众生;十、不退失慈悲菩提心。

对照一下自己,我们能做到几条?跟前辈的高僧大德比起来,我们心力特别差,实在是值得羞愧,但说到底,无常观还是不象古大德那样能深深地刻在心里。

3、在本课中,怎样思维各种喻义而修无常?请大致说明。

答:xx尊者在《道歌集》中,就用了八种比喻形容无常:一、绘画的金色佛像终会褪色;二、美丽的鲜花到秋天会被寒霜冻死;三、高谷奔腾咆哮的瀑布,流至平原会缓缓无力;四、绿绿的稻田终会镰刀砍割;五、精美的绸缎也会被利剪裁截;六、精勤积累的珍贵财宝,人死时终会被舍弃;七、初三的新月清丽动人,但不久就会变得形态臃肿;八、初生的孩子极可爱,突然遭受违缘也会夭折。

通过这八种比喻来文明万法的无常迁变。

另外,本课中还用秋云的比喻来说明无常的道理,比如引用的《方广庄严经》云:在界皆无常,如秋日浮云。

7.已知待处理废水的流量为400m3/h,总碱度为0.5×10-3n-1mol/L。

经试验,宜采用精制硫酸铝为混凝剂,剂量为25mg/L,以生石灰为pH调整剂,其活性CaO含量为60%。

试估算每天的硫酸铝和生石灰实物用量各为多少?第五章浮力浮上法1.按照水中悬浮物的性质,浮力浮上法有哪几种具体的处理方法?试述它们各自的特点和适用对象。

2.试比较压力溶气气浮三种供气方式的优缺点和适用场合?3.什么是微气泡与微絮粒的共聚粘附?如何实现共聚粘附?4.今拟用平流式隔油池处理流量为60 m3/h的某含油废水。

已知废水在池内的流速为12mm/s,要求除去废水内粒径大于60μm的可浮油,浮油密度为0.87g/cm3。

试确定该隔油池上浮区的结构尺寸。

5.试将图5-8改为部分进水加压和部分回流水加压流程示意图。

6.今用部分回流水加压溶气气浮流程处理某厂纸浆白水。

已知废水流量为160m3/h,原水中纸浆纤维SS为160mg/L,处理后要求不大于10mg/L。

经技术经济比较,确定采用空压机供气和折流板空罐溶气,溶气罐过流密度为60m3/m2·h,溶气压力为294kPa(表压)。

气固比A/S=20L/kgSS,水温为20℃。

试计算:(1)空压机额定供气量;(2)溶气罐结构尺寸;(3)气浮池结构尺寸。

第六章不溶态污染物的其它分离方法1.格栅和筛网的功能各是什么?它们各适用于什么场合?2.用离心分离法进行固-液或液-液分离的基本原理是什么?其分离效果与哪些因素有关?3.磁力分离的原理如何?怎样提高其分离效率?4.已知某种工业废水的流量为160m3/h,水温为30℃。

现选用直径为500mm的压力式水力旋流器进行预处理。

如被分离砂质颗粒的密度为2.25g/cm3。

试计算此旋流器的各部结构尺寸、单台处理能力、所需台数和被分离颗粒的极限尺寸。

第七章活性污泥法1.活性污泥降解有机污染物的规律包括哪几种主要关系,试从理论予以推导和说明。

思考题与习题7

7–1基本概念题:

(1)填空题

① 一个EPROM有18条地址输入线,其内部存储单元有( )个。

② 某SRAM芯片有13条地址线和8条数据线,其存储容量为( )。

③ RAM根据所采用的存储单元工作原理的不同,可分为( )存储器和

( )存储器;一个12位地址码、4位输出的ROM,若需将该ROM容量扩展为4K×8,

则需对其进行( )扩展;为构成8K×8的RAM,需要( )片1024×1的RAM,

并且需要有( )位地址译码以完成寻址操作。

④ 半导体存储器是一种能存储( )的半导体器件。用1024×4位的RAM芯

片2114构成8K×8位RAM,需要( )片2114和一个( )译码器。

⑤ 半导体存储器按存取功能分为( )存储器和( ) 存储器。

(2)选择题

① 下列哪些存储器具有非易失性( )。

(a)PROM (b)SRAM (c)DRAM (d)FPGA

② 以下哪种记忆体不是( )半导体器件?

(a)U盘 (b)硬盘 (c)内存 (d)缓存

(3)判断题

① 具有8根地址线的ROM其存储容量为256。 ( )

② 静态随机存储器的基本特点是可随时快速读写,断电后数据易丢失,因而工作时

必须不断刷新。 ( )

【解】

(1)填空题

① 218;② 213×8bits;

③ 静态随机/SRAM,动态随机/DRAM,位,64,13;

④ 大量二值信息,16,3线-8线;⑤ 只读,读写。

(2)选择题:

① a;② b。

(3)判断题:

① ×;② ×。

7–2已知SRAM2112组成的存储器电路如题7–2图所示,其中2线-4线译码器功能表如

题7–2表所示,分析该存储器电路的容量及地址范围。

【解】该存储器电路的容量为:28×8位=2K位。

内存地址的范围为:10 0000 0000~10 1111 1111,即200H~2FFH。

2112-12112-2

8

A

8

A

9

I/O1 I/O

4

I/O1 I/O

4

D

7

D

0

CSCS

0

Y

2

Y

2线-4线译

码器

1

B

0

B

A7A0A7A0A

7

A

0

7–3 试用两片1024×4的RAM组成1K×8位的存储器。

【解】见题7–3图解。

D0…D3A0A9…1024×4RAMCS……D

0

…

D

3

A0A

9

…

1024×4

RAM

CS

…

…

A

9

A

0

…

CS

D

0

D

3

…

D

4

D

7

…

8

位

数

据

输

出

题7–3图解

7–4 比较PROM、PLA、PAL、GAL等4种SPLD的编程特性。

【解】PROM、PLA、PAL、GAL等4种SPLD的编程特性见题7–4表解。

题7–4表解 SPLD的编程特性

器件类型 与阵列 或阵列 实现函数 输出电路

PROM

固定 可编程 标准与或式 固定

PLA

可编程 可编程 最简与或式 固定

PAL

可编程 固定 最简与或式 固定

GAL

可编程 固定 最简与或式 可编程

题7–2表

1

B

0

B

0Y1Y2Y3

Y

000 1 1 1

011 0 1 1

101 1 0 1

111 1 1 0

题7–2图

7–5 用1片16×4位的ROM设计一个将两个2位二进制数相乘的乘法器电路,列出

ROM的数据表,并画出ROM存储矩阵的电路图。

【解】设被乘数和乘数分别为A3A2和A1A0,乘积用D3D2D1D0表示,则ROM数据表见

题7–5表解。将A3A2A1A0作为ROM的地址输入端A3A2A1A0,实现电路图如题7–5图解。

题7–5表解

被乘数 乘数 乘积 被乘数 乘数 乘积

A3 A2 A1 A0 D3 D2 D1 D0 A3 A2 A1 A0 D3 D2 D1 D0

0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0

0 0 0 1 0 0 0 0 1 0 0 1 0 0 1 0

0 0 1 0 0 0 0 0 1 0 1 0 0 1 0 0

0 0 1 1 0 0 0 0 1 0 1 1 0 1 1 0

0 1 0 0 0 0 0 0 1 1 0 0 0 0 0 0

0 1 0 1 0 0 0 1 1 1 0 1 0 0 1 1

0 1 1 0 0 0 1 0 1 1 1 0 0 1 1 0

0 1 1 1 0 0 1 1 1 1 1 1 1 0 0 1

7–6 试将题7–6图中PLA的各输出函数写成∑m的形式。

YZFF56WXFF34FF

12

【解】 1F(W,X,Y,Z)WXYWXZm(5,7,10,11)

2

F(W,X,Y,Z)WXZWXYm(5,7,14,15)

3

F(W,X,Y,Z)WXY0m(14,15)

4

F(W,X,Y,Z)WXZm(0,2)

5

F(W,X,Y,Z)WXZXYZm(0,2,5,13)

6

F(W,X,Y,Z)XYZWYZm(5,10,13,14)

ROM

16×4

A

0

A

1

A

2

A

3

D

0

D

1

D

2

D

3

被

乘

数

乘

数

乘

积

题7–5图解

题7–6图

图2-71

7–7 CPLD和FPGA有哪些特点?

【解】CPLD和FPGA主要有以下五个优点:

① 芯片规模越来越大。随着超大规模集成电路(Very Large Scale IC,VLSI)工艺的不

断提高,单一芯片内部可以容纳上百万个晶体管,CPLD和FPGA芯片的规模越来越大。芯

片的规模越大,所能实现的功能就越强,同时更适用于实现片上系统(SOC)。

② 芯片投资小。CPLD和FPGA芯片在出厂前都已做过100%的测试,而且CPLD/FPGA

设计灵活,发现错误时可以直接更改设计,降低了设计人员投片的风险,节省了许多潜在的

开销,因此,CPLD和FPGA芯片的投资小。

③ 芯片可以反复编程、擦除、使用。在不改变外围电路的情况下,设计不同的片内逻

辑就可实现不同的电路功能,当电路有少量改动时,更能显示出CPLD/FPGA的优势。

④ 芯片运算速度高于单片机。CPLD和FPGA的工作方式与单片机相比,单片机的指

令有固定的执行方式,至少需要4个时钟周期且时钟频率较低,而CPLD和FPGA的运算

执行方式会根据实现该运算的硬件电路方式不同而改变,因此,CPLD和FPGA的运算速度

会高于单片机。

⑤ 规模大、集成度高、可靠性高、灵活性好。

7–8 CPLD和FPGA之间有什么区别?

【解】CPLD和FPGA的不同之处如下:

① FPGA的集成度比CPLD高,具有更复杂的布线结构和逻辑实现。

② CPLD逻辑寄存器少,更适合完成各种算法和组合逻辑;FPGA 逻辑弱而寄存器多,

更适合完成时序逻辑。换句话说,CPLD更适合于触发器有限而乘积项丰富的结构;FPGA

更适合于触发器丰富的结构。

③ CPLD的速度比FPGA快,并且具有较大的时间可预测性。这是由于CPLD的逻辑

块之间的互联是集总式的,而FPGA的互连则是分布式的。

④ CPLD比FPGA使用起来更方便。CPLD的编程采用E2PROM或FASTFLASH技术,

无需外部存储器芯片,使用简单。而FPGA的编程信息需存放在外部存储器上,使用方法

复杂。

⑤ 在编程方式上,CPLD主要是基于E2PROM或Flash存储器编程,编程次数可达1

万次,优点是系统断电时编程信息也不丢失。CPLD又可分为在编程器上编程和在系统编程

两类。FPGA大部分是基于SRAM编程,编程信息在系统断电时丢失,每次上电时,需从

器件外部将编程数据重新写入SRAM中。其优点是可以编程任意次,可在工作中快速编程,

从而实现板级和系统级的动态配置。

⑥ 在编程上FPGA比CPLD具有更大的灵活性。CPLD通过修改具有固定内连电路的

逻辑功能来编程,FPGA主要通过改变内部连线的布线来编程;FPGA可在逻辑门下编程,

而CPLD是在逻辑块下编程。