R1210N512C中文资料

- 格式:pdf

- 大小:28.32 KB

- 文档页数:1

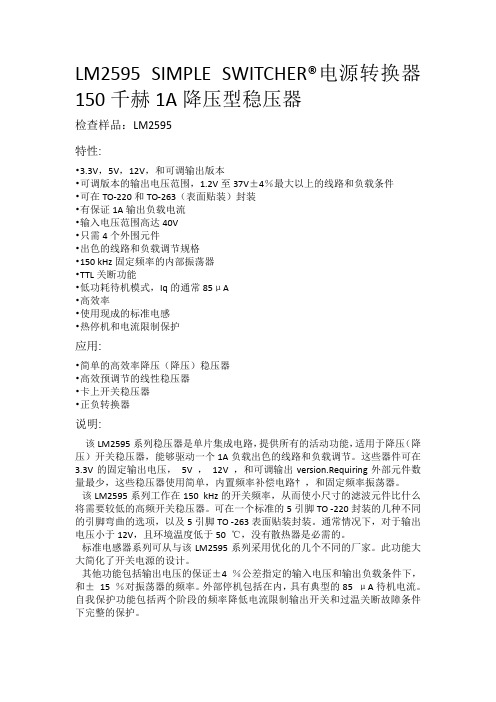

资料来源:整理:Tansuozg·cn512C中文说明书单相控制器512C型产品型号HA389196目录目录 (1)概述 (2)机械安装尺寸…………………………………………………………………………电气规格 (3)环境条件 (4)基本接线 (5)接线端说明 (5)系统框图………………………………………………………………………………安装须知 (8)基本设定程序 (9)故障处理 (11)概述SSD512控制器适用于永磁和并磁直流电机的转速和力矩控制。

装置有四种型号:512C/04 4A DC512C/08 8A DC512C/16 16A DC512C/32 32A DC控制器计设在110-415VAC 50/60Hg 单相电流上运行,简单改变控制器上的变换抽头即可使装置使用于供电电压。

控制器采用全波半控可控硅/二极管功率桥块,封装在两块分开的模块中,以便使两模块及控制板可靠接地。

直流电动机的转速采用线性闭环控制,由电枢电压或测速发电机取得反馈讯号使电机转速能在负载波动情况下保持不变。

速度环内的电流环使受控制的电流电平适应于电动机,实际电平值用户可通过电流控制电位器和开关来调节。

由于过大的负载,电机可能堵转,约15秒后控制器会跳闸,由感应引起的严重过电流可以被瞬间过流脱机装置检测到。

磁场及控制电路还提供快熔丝及过电压保护。

警告不先断开系统的所有电流决不能在控制器上工作电气规格环境条件外壳:框架安装运行温度:0 - 40℃(40℃以上每度降低%额定值)温度:40℃时相对温度85%(无结露)海拔温度:1000mm以上,每增加100m额定值降低1% 重量:1.5Kg — 512C/041.5Kg — 512C/081.6Kg — 512C/162.9Kg — 512C/32转速控制转矩控制基本接线①用于非标电压②信号接地,推荐接保护接地。

如有多台控制器同时使用,应采用一点接地。

③用于电流控制。

接线端说明控制端1.速机反馈:与电动机转速成比例的正向电压(350V最大)。

TYP 212--->TYP 2012April 1995SCR FOR OVERVOLTAGE PROTECTIONSymbol ParameterValue Unit I T(RMS)RMS on-state current(180°conduction angle,single phase circuit)Tc =110°C 12A I T(AV)Average on-state current(180°conduction angle,single phase circuit)Tc =110°C 8A I TSMNon repetitive surge peak on-state current (Tj initial =25°C )tp =8.3ms 315Atp =10ms 300I 2t I 2t valuetp =10ms 450A 2s I TMNon repetitive surge peak on-state current (Tj initial =25°C )Exponential pulse wave formtp =1ms750A dI/dt Critical rate of rise of on-state currentGate supply :I G =100mA di G /dt =1A/µs 100A/µs Tstg Tj Storage and operating junction temperature range-40to +150-40to +125°C °C TlMaximum lead temperature for soldering during 10s at 4.5mm from case260°CTO220AB (Plastic)KA G.HIGH SURGE CURRENT CAPABILITY .HIGH dI/dt RATING.HIGH STABILITY AND RELIABILITYDESCRIPTIONSymbol ParameterTYPUnit21251210122012V DRM V RRM Repetitive peak off-state voltage Tj =125°C2550100200VABSOLUTE RATINGS (limiting values)FEATURESThe TYP 212--->1012Family uses high perform-ance glass passivated chips technology.These Silicon Controlled Rectifiers are designed for overvoltage protection in crowbar circuits applica-tion.1/5GATE CHARACTERISTICS (maximum values)Symbol ParameterValue Unit Rth (j-a)Junction to ambient60°C/W Rth (j-c)DC Junction to case for DC1.3°C/WSymbol Test ConditionsValue Unit I GT V D =12V (DC)R L =33ΩTj=25°C MAX 30mA V GT V D =12V(DC)R L =33ΩTj=25°C MAX 1.5V V GD V D =V DRM R L =3.3k ΩTj=125°C MIN 0.2V tgt V D =V DRM I G =200mA dI G /dt =1.5A/µs Tj=25°C TYP 1µs I L I G =1.2I GT Tj=25°CTYP 60mA I H I T =500mAgate openTj=25°C MAX 50mA V TM ITM=50A tp=380µs Tj=25°C MAX 1.5V I DRM I RRM V DRM Rated V RRMRatedTj=25°C MAX0.01mATj=125°C 2dV/dt Linear slope up to V D =67%V DRM gate openTj=125°C MIN 200V/µs tqV D =67%V DRM I TM =50A V R =25V dI TM /dt=30A/µs dV D /dt=50V/µsTj=125°CTYP 100µs P G (AV)=1WP GM =10W (tp =20µs)I FGM =4A (tp =20µs)V RGM =5V.ELECTRICAL CHARACTERISTICSTHERMAL RESISTANCESTYP 212--->TYP 20122/5Fig.1:Maximum average power dissipation versus average on-state current.Fig.2:Correlation between maximum average power dissipation and maximum allowable temperatures (T amb and T case )for different thermal resistances heatsink +contact.Fig.5:Relative variation of gate trigger current versus junction temperature.Fig.6:Non repetitive surge peak on-state current versus number of cycles.Fig.3:Average on-state current versus casetemperature.1E-31E-21E-11E+01E+11E+25E+20.010.11Zth/Rth Zth(j-c)Zth(j-a)tp(s)Fig.4:Relative variation of thermal impedance versus pulse duration.TYP 212--->TYP 20123/5Fig.7:Non repetitive surge peak on-state current for asinusoidal pulse with width:t≤10ms,andcorresponding value of I2t.Fig.8:On-state characteristics(maximum values).Fig.9:Peak capacitor discharge current versus pulse width.Fig.10:Allowable peak capacitor discharge current versus initial junction temparature.TYP212--->TYP2012 4/5PACKAGE MECHANICAL DATA TO220AB PlasticCooling method :CMarking :type number Weight :2.3gRecommended torque value :0.8m.N.Maximum torque value :1m.N.AGJHDBCMLFOP=N =IREF.DIMENSIONSMillimeters Inches Min.Max.Min.Max.A 10.0010.400.3930.409B 15.2015.900.5980.625C 13.0014.000.5110.551D 6.20 6.600.2440.259F 3.50 4.200.1370.165G 2.65 2.950.1040.116H 4.40 4.600.1730.181I 3.75 3.850.1470.151J 1.23 1.320.0480.051L 0.490.700.0190.027M 2.40 2.720.0940.107N 4.80 5.400.1880.212O 1.14 1.700.0440.066P0.610.880.0240.034Information furnished is believed to be accurate and reliable.However,SGS-THOMSON Microelectronics assumes no responsability for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use.No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics.Specifications mentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.©1995SGS-THOMSON Microelectronics -Printed in Italy -All rights reserved.SGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia -Brazil -France -Germany -Hong Kong -Italy -Japan -Korea -Malaysia -Malta -Morocco -The Nether-lands Singapore -Spain -Sweden -Switzerland -Taiwan -Thailand -United Kingdom -U.S.A.TYP 212--->TYP 20125/5。

MX25L512512K-BIT [x 1] CMOS SERIAL FLASH FEATURESGENERAL• Serial Peripheral Interface (SPI) compatible -- Mode 0 and Mode 3• 524,288 x 1 bit structure• 16 Equal Sectors with 4K byte each- Any Sector can be erased individually• S ingle Power Supply Operation- 2.7 to 3.6 volt for read, erase, and program operations• L atch-up protected to 100mA from -1V to Vcc +1VPERFORMANCE• H igh Performance- Fast access time: 85MHz serial clock (15pF + 1TTL Load) and 66MHz serial clock (30pF + 1TTL Load)- Fast program time: 1.4ms(typ.) and 5ms(max.)/page (256-byte per page)- Fast erase time: 60ms(typ.) and 120ms(max.)/sector (4K-byte per sector) ; 1s(typ.) and 2s(max.)/chip(512Kb)• L ow Power Consumption- Low active read current: 12mA(max.) at 85MHz, 8mA(max.) at 66MHz and 4mA(max.) at 33MHz- Low active programming current: 15mA (max.)- Low active erase current: 15mA (max.)- Low standby current: 10uA (max.)- Deep power-down mode 1uA (typical)• M inimum 100,000 erase/program cyclesSOFTWARE FEATURES• Input Data Format- 1-byte Command code• Block Lock protection- The BP0~BP1 status bit defines the size of the area to be software protected against Program and Erase in-structions.• Auto Erase and Auto Program Algorithm- Automatically erases and verifies data at selected sector- Automatically programs and verifies data at selected page by an internal algorithm that automatically times the program pulse widths (Any page to be programed should have page in the erased state first)• Status Register Feature• Electronic Identification- JEDEC 2-byte Device ID- RES command, 1-byte Device IDHARDWARE FEATURES• SCLK Input- Serial clock input• SI Input- Serial Data Input• SO Output- Serial Data Output• WP# pin- Hardware write protection• HOLD# pin- pause the chip without diselecting the chip• PACKAGE- 8-pin SOP (150mil)- 8-USON (2x3mm)- All Pb-free devices are RoHS CompliantGENERAL DESCRIPTIONMX25L512 is a CMOS 524,288 bit serial Flash memory, which is configured as 65,536 x 8 internally. MX25L512 features a serial peripheral interface and software protocol allowing operation on a simple 3-wire bus. The three bus signals are a clock input (SCLK), a serial data input (SI), and a serial data output (SO). SPI access to the device is enabled by CS# input.MX25L512 provide sequential read operation on whole chip.After program/erase command is issued, auto program/ erase algorithms which program/ erase and verify the spec-ified page or sector/block locations will be executed. Program command is executed on page (256 bytes) basis, and erase command is executes on chip or sector (4K-bytes).To provide user with ease of interface, a status register is included to indicate the status of the chip. The status read command can be issued to detect completion status of a program or erase operation via WIP bit.When the device is not in operation and CS# is high, it is put in standby mode and draws less than 10uA DC cur-rent.The MX25L512 utilize MXIC's proprietary memory cell, which reliably stores memory contents even after 100,000 program and erase cycles.PIN CONFIGURATIONSSYMBOL DESCRIPTION CS#Chip SelectSI Serial Data Input SO Serial Data Output SCLK Clock InputHOLD#Hold, to pause the device without deselecting the device WP#Write ProtectionVCC + 3.3V Power Supply GNDGroundPIN DESCRIPTION8-PIN SOP (150mil)CS#SO WP#GND VCC HOLD#SCLK SI8-LAND USON (2x3mm)CS#SO WP#GND VCC HOLD#SCLK SIBLOCK DIAGRAMDATA PROTECTIONMX25L512 is designed to offer protection against accidental erasure or programming caused by spurious system level signals that may exist during power transition. During power up the device automatically resets the state ma-chine in the standby mode. In addition, with its control register architecture, alteration of the memory contents only occurs after successful completion of specific command sequences. The device also incorporates several features to prevent inadvertent write cycles resulting from VCC power-up and power-down transition or system noise.• Valid command length checking: The command length will be checked whether it is at byte base and completed on byte boundary.• Write Enable (WREN) command: WREN command is required to set the Write Enable Latch bit (WEL) before other command to change data. The WEL bit will return to reset stage under following situation:- Power-up- Write Disable (WRDI) command completion- Write Status Register (WRSR) command completion- Page Program (PP) command completion- Sector Erase (SE) command completion- Block Erase (BE) command completion- Chip Erase (CE) command completion• Software Protection Mode (SPM): by using BP0-BP1 bits to set the part of Flash protected from data change.• Hardware Protection Mode (HPM): by using WP# going low to protect the BP0-BP1 bits and SRWD bit from data change.• Deep Power Down Mode: By entering deep power down mode, the flash device also is under protected from writing all commands except Release from deep power down mode command (RDP) and Read Electronic Sig-nature command (RES).Table 1. Protected Area SizesStatus bitProtect level 512b BP1 BP00 0 0 (none) None 0 1 1 (All)All 1 0 2 (All)All 113 (All)AllHOLD FEATUREHOLD# pin signal goes low to hold any serial communications with the device. The HOLD feature will not stop the operation of write status register, programming, or erasing in progress.The operation of HOLD requires Chip Select(CS#) keeping low and starts on falling edge of HOLD# pin signal while Serial Clock (SCLK) signal is being low (if Serial Clock signal is not being low, HOLD operation will not start until Serial Clock signal being low). The HOLD condition ends on the rising edge of HOLD# pin signal while Se-rial Clock(SCLK) signal is being low( if Serial Clock signal is not being low, HOLD operation will not end until Serial Clock being low), see Figure 1.The Serial Data Output (SO) is high impedance, both Serial Data Input (SI) and Serial Clock (SCLK) are don't care during the HOLD operation. If Chip Select (CS#) drives high during HOLD operation, it will reset the internal logic of the device. To re-start communication with chip, the HOLD# must be at high and CS# must be at low.Figure 1. Hold Condition OperationTable 2. COMMAND DEFINITION(1) ADD=00H will output the manufacturer's ID first and ADD=01H will output device ID first.(2) BE command may erase whole 512Kb chip.(3) It is not recommended to adopt any other code which is not in the above command definition table.COMMAND (byte)WREN (write enable)WRDI (write disable)RDID (readidentification)RDSR (read status register)WRSR (write status register)READ(read data)Fast Read(fast readdata)1st 06 (hex)04 (hex)9F (hex)05 (hex)01 (hex)03 (hex)0B (hex)2nd AD1AD13rd AD2AD24th AD3AD35th xActionsets the (WEL) write enable latch bit resets the (WEL) write enable latchbit outputs manufacturer ID and 2-byte device IDto read out the status register to write new values to the status register n bytes read out until CS# goes highCOMMAND (byte)SE(Sector Erase)BE (2)(Block Erase)CE (Chip Erase)PP(Page Program)DP(Deep Power Down) RDP(Release from Deep Power-down) RES (ReadElectronicID)REMS (ReadElectronicManufacturer& Device ID)1st 20 (hex)52 or D8 (hex)60 or C7 (hex)02 (hex) B9 (hex)AB (hex)AB (hex)90 (hex)2nd AD1AD1AD1x x 3rd AD2AD2AD2x x 4th AD3AD3AD3xADD(1)5th ActionOutput the manufacturer ID and deviceIDDEVICE OPERATION1. Before a command is issued, status register should be checked to ensure device is ready for the intended op-eration.2. When incorrect command is inputted to this LSI, this LSI becomes standby mode and keeps the standby modeuntil next CS# falling edge. In standby mode, SO pin of this LSI should be High-Z.3. When correct command is inputted to this LSI, this LSI becomes active mode and keeps the active mode until next CS# rising edge.4. Input data is latched on the rising edge of Serial Clock(SCLK) and data shifts out on the falling edge of SCLK. The difference of SPI mode 0 and mode 3 is shown as Figure 2.Figure 2. SPI Modes SupportedSCLKMSBCPHA shift inshift outSI 01CPOL(Serial mode 0)(Serial mode 3)1SO SCLKMSB5. For the following instructions: RDID, RDSR, READ, FAST_READ, RES and REMS the shifted-in instruction se-quence is followed by a data-out sequence. After any bit of data being shifted out, the CS# can be high. For the following instructions: WREN, WRDI, WRSR, SE, BE, CE, PP , RDP and DP the CS# must go high exactly at the byte boundary; otherwise, the instruction will be rejected and not executed.6. During the progress of Write Status Register, Program, Erase operation, to access the memory array is neglect-ed and not affect the current operation of Write Status Register, Program, Erase. Table 3. Memory OrganizationNote:CPOL indicates clock polarity of SPI master, CPOL=1 for SCLK high while idle, CPOL=0 for SCLK low while not transmitting. CPHA indicates clock phase. The combination of CPOL bit and CPHA bit decides which SPI mode is supported.Sector Address Range1500F000h 00FFFFh:::3003000h 003FFFh 2002000h 002FFFh 1001000h 001FFFh 0000000h 000FFFhCOMMAND DESCRIPTION(1) Write Enable (WREN)The Write Enable (WREN) instruction is for setting Write Enable Latch (WEL) bit. For those instructions like PP, SE, BE, CE, and WRSR, which are intended to change the device content, should be set every time after the WREN in-struction setting the WEL bit.The sequence of issuing WREN instruction is: CS# goes low-> sending WREN instruction code-> CS# goes high. (see Figure 11)(2) Write Disable (WRDI)The Write Disable (WRDI) instruction is for resetting Write Enable Latch (WEL) bit.The sequence of issuing WRDI instruction is: CS# goes low-> sending WRDI instruction code-> CS# goes high. (see Figure 12)The WEL bit is reset by following situations:- Power-up- Write Disable (WRDI) instruction completion- Write Status Register (WRSR) instruction completion- Page Program (PP) instruction completion- Sector Erase (SE) instruction completion- Block Erase (BE) instruction completion- Chip Erase (CE) instruction completion(3) Read Identification (RDID)RDID instruction is for reading the manufacturer ID of 1-byte and followed by Device ID of 2-byte. The MXIC Manu-facturer ID is C2(hex), the memory type ID is 20(hex) as the first-byte device ID, and the individual device ID of second-byte ID is as followings: 10(hex) for MX25L512.The sequence of issuing RDID instruction is: CS# goes low→sending RDID instruction code→24-bits ID data out on SO→to end RDID operation can use CS# to high at any time during data out. (see Figure. 13)While Program/Erase operation is in progress, it will not decode the RDID instruction, so there's no effect on the cy-cle of program/erase operation which is currently in progress. When CS# goes high, the device is at standby stage.(4) Read Status Register (RDSR)The RDSR instruction is for reading Status Register Bits. The Read Status Register can be read at any time (even in program/erase/write status register condition) and continuously. It is recommended to check the Write in Progress (WIP) bit before sending a new instruction when a program, erase, or write status register operation is in progress. The sequence of issuing RDSR instruction is: CS# goes low→sending RDSR instruction code→Status Register data out on SO (see Figure. 14)The definition of the status register bits is as below:WIP bit. The Write in Progress (WIP) bit, a volatile bit, indicates whether the device is busy in program/erase/write status register progress. When WIP bit sets to 1, which means the device is busy in program/erase/write status register progress. When WIP bit sets to 0, which means the device is not in progress of program/erase/write status register cycle.WEL bit. The Write Enable Latch (WEL) bit, a volatile bit, indicates whether the device is set to internal write enable latch. When WEL bit sets to 1, which means the internal write enable latch is set, the device can accept program/erase/write status register instruction. When WEL bit sets to 0, which means no internal write enable latch; the de-vice will not accept program/erase/write status register instruction.BP1, BP0 bits. The Block Protect (BP1, BP0) bits, non-volatile bits, indicate the protected area(as defined in table 1) of the device to against the program/erase instruction without hardware protection mode being set. To write the Block Protect (BP1, BP0) bits requires the Write Status Register (WRSR) instruction to be executed. Those bits define the protected area of the memory to against Page Program (PP), Sector Erase (SE), Block Erase (BE) and Chip Erase(CE) instructions (only if all Block Protect bits set to 0, the CE instruction can be executed)SRWD bit. The Status Register Write Disable (SRWD) bit, non-volatile bit, is operated together with Write Protec-tion (WP#) pin for providing hardware protection mode. The hardware protection mode requires SRWD sets to 1 and WP# pin signal is low stage. In the hardware protection mode, the Write Status Register (WRSR) instruction is no longer accepted for execution and the SRWD bit and Block Protect bits (BP1, BP0) are read only.Note: 1. See the table "Protected Area Sizes".2. The endurance cycles of protect bits are 100,000 cycles; however, the tW time out spec of protect bits isrelaxed as tW = N x 15ms (N is a multiple of 10,000 cycles, ex. N = 2 for 20,000 cycles) after 10,000 cycles on those bits.bit7bit6bit5bit4bit3bit2bit1bit0SRWD (status register write protect)0BP1 (level of protected block)BP0 (level of protected block)WEL (write enable latch)WIP (write inprogress bit)1=status register write disable(note 1)(note 1)1=write enable 0=not write enable 1=write operation 0=not in write operation(5) Write Status Register (WRSR)The WRSR instruction is for changing the values of Status Register Bits. Before sending WRSR instruction, the Write Enable (WREN) instruction must be decoded and executed to set the Write Enable Latch (WEL) bit in ad-vance. The WRSR instruction can change the value of Block Protect (BP1, BP0) bits to define the protected area of memory (as shown in table 1). The WRSR also can set or reset the Status Register Write Disable (SRWD) bit in accordance with Write Protection (WP#) pin signal. The WRSR instruction cannot be executed once the Hardware Protected Mode (HPM) is entered.The sequence of issuing WRSR instruction is: CS# goes low-> sending WRSR instruction code-> Status Register data on SI-> CS# goes high. (see Figure 15)The WRSR instruction has no effect on b6, b5, b4, b1, b0 of the status register.The CS# must go high exactly at the byte boundary; otherwise, the instruction will be rejected and not executed. The self-timed Write Status Register cycle time (tW) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Write Status Register cycle is in progress. The WIP sets 1 during the tW timing, and sets 0 when Write Status Register Cycle is completed, and the Write Enable Latch (WEL) bit is reset.Table 4. Protection ModesNote:1. As defined by the values in the Block Protect (BP1, BP0) bits of the Status Register, as shown in Table 1.As the table above showing, the summary of the Software Protected Mode (SPM) and Hardware Protected Mode (HPM). Software Protected Mode (SPM):- When SRWD bit=0, no matter WP# is low or high, the WREN instruction may set the WEL bit and can changethe values of SRWD, BP1, BP0. The protected area, which is defined by BP1, BP0, is at software protected mode (SPM).- When SRWD bit=1 and WP# is high, the WREN instruction may set the WEL bit can change the values ofSRWD, BP1, BP0. The protected area, which is defined by BP1, BP0, is at software protected mode (SPM)ModeStatus register condition WP# and SRWD bit status Memory Software protectionmode (SPM)Status register can be written in (WEL bit is set to "1") andthe SRWD, BP0-BP1bits can be changed WP#=1 and SRWD bit=0, or WP#=0 and SRWD bit=0, or WP#=1 and SRWD=1The protected areacannotbe program or erase.Hardware protectionmode (HPM)The SRWD, BP0-BP1 of status register bits cannot bechangedWP#=0, SRWD bit=1The protected areacannotbe program or erase.Note: If SRWD bit=1 but WP# is low, it is impossible to write the Status Register even if the WEL bit has previously been set. It is rejected to write the Status Register and not be executed.Hardware Protected Mode (HPM):- When SRWD bit=1, and then WP# is low (or WP# is low before SRWD bit=1), it enters the hardware protected mode (HPM). The data of the protected area is protected by software protected mode by BP1, BP0 and hard-ware protected mode by the WP# to against data modification.Note: to exit the hardware protected mode requires WP# driving high once the hardware protected mode is entered. If the WP# pin is permanently connected to high, the hardware protected mode can never be entered; only can use software protected mode via BP1, BP0.(6) Read Data Bytes (READ)The read instruction is for reading data out. The address is latched on rising edge of SCLK, and data shifts out on the falling edge of SCLK at a maximum frequency fR. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single READ instruction. The address counter rolls over to 0 when the highest address has been reached.The sequence of issuing READ instruction is: CS# goes low→ sending READ instruction code→ 3-byte address on SI→ data out on SO→ to end READ operation can use CS# to high at any time during data out. (see Figure. 16) (7) Read Data Bytes at Higher Speed (FAST_READ)The FAST_READ instruction is for quickly reading data out. The address is latched on rising edge of SCLK, and data of each bit shifts out on the falling edge of SCLK at a maximum frequency fC. The first address byte can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single FAST_READ instruction. The address counter rolls over to 0 when the highest address has been reached.The sequence of issuing FAST_READ instruction is: CS# goes low→ sending FAST_READ instruction code→ 3-byte address on SI→ 1-dummy byte address on SI→data out on SO→ to end FAST_READ operation can use CS# to high at any time during data out. (see Figure. 17)While Program/Erase/Write Status Register cycle is in progress, FAST_READ instruction is rejected without any im-pact on the Program/Erase/Write Status Register current cycle.(8) Sector Erase (SE)The Sector Erase (SE) instruction is for erasing the data of the chosen sector to be "1". A Write Enable (WREN) in-struction must execute to set the Write Enable Latch (WEL) bit before sending the Sector Erase (SE). Any address of the sector (see table 3) is a valid address for Sector Erase (SE) instruction. The CS# must go high exactly at the byte boundary (the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.Address bits [Am-A12] (Am is the most significant address) select the sector address.The sequence of issuing SE instruction is: CS# goes low → sending SE instruction code→ 3-byte address on SI → CS# goes high. (see Figure 19)The self-timed Sector Erase Cycle time (tSE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tSE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP1, BP0 bits, the Sector Erase (SE) instruction will not be executed on the page.(9) Block Erase (BE)The Block Erase (BE) instruction is for erasing the data of the chosen block to be "1". A Write Enable (WREN) in-struction must execute to set the Write Enable Latch (WEL) bit before sending the Block Erase (BE). Any address of the block (see table 3) is a valid address for Block Erase (BE) instruction. The CS# must go high exactly at the byte boundary (the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed.The sequence of issuing BE instruction is: CS# goes low → sending BE instruction code→ 3-byte address on SI → CS# goes high. (see Figure 20)The self-timed Block Erase Cycle time (tBE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tBE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP1, BP0 bits, the Block Erase (BE) instruction will not be executed on the page.(10) Chip Erase (CE)The Chip Erase (CE) instruction is for erasing the data of the whole chip to be "1". A Write Enable (WREN) instruc-tion must execute to set the Write Enable Latch (WEL) bit before sending the Chip Erase (CE). Any address of the sector (see table 3) is a valid address for Chip Erase (CE) instruction. The CS# must go high exactly at the byte boundary( the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not ex-ecuted.The sequence of issuing CE instruction is: CS# goes low→ sending CE instruction code→ CS# goes high. (see Figure 20)The self-timed Chip Erase Cycle time (tCE) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Chip Erase cycle is in progress. The WIP sets 1 during the tCE timing, and sets 0 when Chip Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the chip is protected by BP1, BP0 bits, the Chip Erase (CE) instruction will not be executed. It will be only executed when BP1, BP0 all set to "0".(11) Page Program (PP)The Page Program (PP) instruction is for programming the memory to be "0". A Write Enable (WREN) instruction must execute to set the Write Enable Latch (WEL) bit before sending the Page Program (PP). If the eight least sig-nificant address bits (A7-A0) are not all 0, all transmitted data which goes beyond the end of the current page are programmed from the start address if the same page (from the address whose 8 least significant address bits (A7-A0) are all 0). The CS# must keep during the whole Page Program cycle. The CS# must go high exactly at the byte boundary( the latest eighth of address byte been latched-in); otherwise, the instruction will be rejected and not executed. If more than 256 bytes are sent to the device, the data of the last 256-byte is programmed at the request page and previous data will be disregarded. If less than 256 bytes are sent to the device, the data is programmed at the request address of the page without effect on other address of the same page.The sequence of issuing PP instruction is: CS# goes low→ sending PP instruction code→ 3-byte address on SI→at least 1-byte on data on SI→ CS# goes high. (see Figure 18)The self-timed Page Program Cycle time (tPP) is initiated as soon as Chip Select (CS#) goes high. The Write in Progress (WIP) bit still can be check out during the Page Program cycle is in progress. The WIP sets 1 during the tPP timing, and sets 0 when Page Program Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the page is protected by BP1, BP0 bits, the Page Program (PP) instruction will not be executed.(12) Deep Power-down (DP)The Deep Power-down (DP) instruction is for setting the device on the minimizing the power consumption (to enter-ing the Deep Power-down mode), the standby current is reduced from ISB1 to ISB2). The Deep Power-down mode requires the Deep Power-down (DP) instruction to enter, during the Deep Power-down mode, the device is not ac-tive and all Write/Program/Erase instruction are ignored. When CS# goes high, it's only in standby mode not deep power-down mode. It's different from Standby mode.The sequence of issuing DP instruction is: CS# goes low→ sending DP instruction code→ CS# goes high. (see Fig-ure 22)Once the DP instruction is set, all instruction will be ignored except the Release from Deep Power-down mode (RDP) and Read Electronic Signature (RES) instruction. (RES instruction to allow the ID been read out). When Power-down, the deep power-down mode automatically stops, and when power-up, the device automatically is in standby mode. For RDP instruction the CS# must go high exactly at the byte boundary (the latest eighth bit of instruction code been latched-in); otherwise, the instruction will not executed. As soon as Chip Select (CS#) goes high, a delay of tDP is required before entering the Deep Power-down mode and reducing the current to ISB2.(13) Release from Deep Power-down (RDP), Read Electronic Signature (RES)The Release from Deep Power-down (RDP) instruction is terminated by driving Chip Select (CS#) High. When Chip Select (CS#) is driven High, the device is put in the Stand-by Power mode. If the device was not previously in the Deep Power-down mode, the transition to the Stand-by Power mode is immediate. If the device was previously in the Deep Power-down mode, though, the transition to the Stand-by Power mode is delayed by tRES2, and Chip Select (CS#) must remain High for at least tRES2(max), as specified in Table 6. Once in the Stand-by Power mode, the device waits to be selected, so that it can receive, decode and execute instructions.RES instruction is for reading out the old style of 8-bit Electronic Signature, whose values are shown as table of ID Definitions. This is not the same as RDID instruction. It is not recommended to use for new design. For new deisng, please use RDID instruction. Even in Deep power-down mode, the RDP and RES are also allowed to be executed, only except the device is in progress of program/erase/write cycle; there's no effect on the current program/erase/ write cycle in progress.The sequence is shown as Figure 23,24.The RES instruction is ended by CS# goes high after the ID been read out at least once. The ID outputs repeat-edly if continuously send the additional clock cycles on SCLK while CS# is at low. If the device was not previously in Deep Power-down mode, the device transition to standby mode is immediate. If the device was previously in Deep Power-down mode, there's a delay of tRES2 to transit to standby mode, and CS# must remain to high at least tRES2(max). Once in the standby mode, the device waits to be selected, so it can be receive, decode, and execute instruction.The RDP instruction is for releasing from Deep Power Down Mode.(14) Read Electronic Manufacturer ID & Device ID (REMS)The REMS instruction is an alternative to the Release from Power-down/Device ID instruction that provides both the JEDEC assigned manufacturer ID and the specific device ID.The REMS instruction is very similar to the Release from Power-down/Device ID instruction. The instruction is initi-ated by driving the CS# pin low and shift the instruction code "90h" followed by two dummy bytes and one bytes address (A7~A0). After which, the Manufacturer ID for MXIC (C2h) and the Device ID are shifted out on the falling edge of SCLK with most significant bit (MSB) first as shown in figure 25. The Device ID values are listed in Table of ID Definitions on page 16. If the one-byte address is initially set to 01h, then the device ID will be read first and then followed by the Manufacturer ID. The Manufacturer and Device IDs can be read continuously, alternating from one to the other. The instruction is completed by driving CS# high.Table of ID Definitions:RDID Command manufacturer ID memory type memory density C22010RES Command electronic ID05REMS Command manufacturer ID device ID C205。

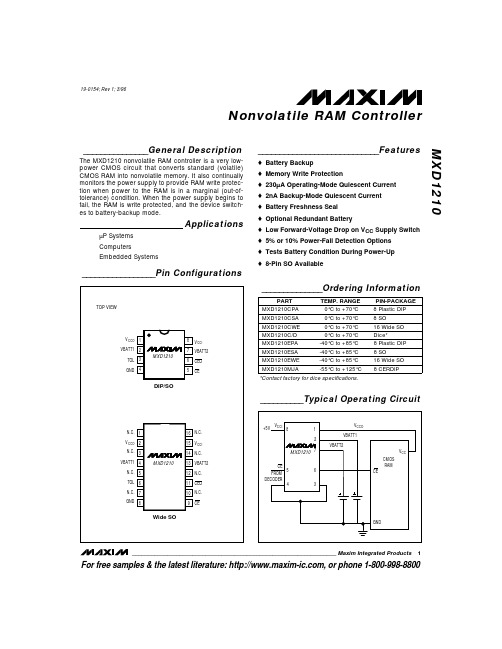

For free samples & the latest literature: , or phone 1-800-998-8800_______________General DescriptionThe MXD1210 nonvolatile RAM controller is a very low-power CMOS circuit that converts standard (volatile)CMOS RAM into nonvolatile memory. It also continually monitors the power supply to provide RAM write protec-tion when power to the RAM is in a marginal (out-of-tolerance) condition. When the power supply begins to fail, the RAM is write protected, and the device switch-es to battery-backup mode.ApplicationsµP Systems ComputersEmbedded Systems____________________________Featureso Battery Backupo Memory Write Protectiono 230µA Operating-Mode Quiescent Current o 2nA Backup-Mode Quiescent Current o Battery Freshness Seal o Optional Redundant Batteryo Low Forward-Voltage Drop on V CC Supply Switch o 5% or 10% Power-Fail Detection Options o Tests Battery Condition During Power-Up o 8-Pin SO Available______________Ordering Information*Contact factory for dice specifications.MXD1210Nonvolatile RAM Controller________________________________________________________________Maxim Integrated Products 1__________Typical Operating Circuit19-0154; Rev 1; 3/96PARTTEMP. RANGE PIN-PACKAGE MXD1210CPA 8 Plastic DIP MXD1210CSA 8 SOMXD1210CWE 0°C to +70°C 16 Wide SO 0°C to +70°C 0°C to +70°C MXD1210C/D Dice*MXD1210ESA -40°C to +85°C 8 SOMXD1210EPA -40°C to +85°C 8 Plastic DIP MXD1210EWE -40°C to +85°C 16 Wide SO MXD1210MJA-55°C to +125°C8 CERDIP0°C to +70°C _________________Pin ConfigurationsM X D 1210Nonvolatile RAM ControllerABSOLUTE MAXIMUM RATINGSELECTRICAL CHARACTERISTICS(T A = T MIN to T MAX , unless otherwise noted.)Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.ELECTRICAL CHARACTERISTICS(V CCI = +4.75V to +5.5V, TOL = GND; or V CCI = +4.5V to +5.5V, TOL = V CCO ; T A = T MIN to T MAX ; unless otherwise noted.)V CCI to GND ................................................................-0.3V, +7V VBATT1 to GND..........................................................-0.3V, +7V VBATT2 to GND.......................................................... -0.3V, +7V V CCO to GND..................................................... -0.3V, V S + 0.3V(V S = greater of V CCI , VBATT1, VBATT2)Digital Input and Output Voltages to GND............. 0.3V, V CCI + 0.3VContinuous Power Dissipation (T A = +70°C)8-Pin Plastic DIP (derate 9.09mW/°C above +70°C)....727mW 8-Pin SO (derate 5.88mW/°C above +70°C).................471mW 16-Pin Wide SO (derate 9.52mW/°C above +70°C)......762mW 8-Pin CERDIP (derate 8.00mW/°C above +70°C).........640mW Operating Temperature RangesMXD1210C_ _..................................................... 0°C to +70°C MXD1210E_ _.................................................. -40°C to +85°C MXD1210MJA................................................ -55°C to +125°C Storage Temperature Range ........................... -65°C to +150°C Lead Temperature (soldering, 10sec)............................ +300°CNonvolatile RAM ControllerELECTRICAL CHARACTERISTICS(V CCI < VBATT; positive edge rate at VBATT1, VBATT2 > 0.1V/µs, T A = T MIN to T MAX ; unless otherwise noted.)MXD1210ELECTRICAL CHARACTERISTICS(T A = T MIN to T MAX , unless otherwise noted.)_______________________________________________________________________________________3V CC POWER TIMING CHARACTERISTICS(V= +4.75V to +5.5V, TOL = GND; or V = +4.5V to +5.5V, TOL = V ; T = T to T ; unless otherwise noted.)TIMING CHARACTERISTICS(V CCI < +4.75V to +5.5V, TOL = GND; or V CCI < +4.5V , TOL = V CCO ; T A = T MIN to T MAX ; unless otherwise noted.)Note 1:Only one battery input is required. Unused battery inputs must be grounded.Note 2:I CCO1is the maximum average load current the MXD1210 can supply to the memories.Note 3:I CCO2is the maximum average load current the MXD1210 can supply to the memories in battery-backup mode.Note 4:CEO can sustain leakage current only in battery-backup mode.Note 5:Guaranteed by design.Note 6:t CE max must be met to ensure data integrity on power loss.M X D 1210Nonvolatile RAM Controller 4_____________________________________________________________________________________________________________________________________________________Pin DescriptionFigure 1. Block Diagram______________Detailed DescriptionMain FunctionsThe MXD1210 executes five main functions to perform reliable RAM operation and battery backup (see Typical Operating Circuit and Figure 1):1. RAM Power-Supply Switch: The switch directs power to the RAM from the incoming supply or from the selected battery, whichever is at thegreater voltage. The switch control uses the same criterion to direct power to MXD1210 internal circuitry.2. Power-Failure Detection: The write-protection func-tion is enabled when a power failure is detected.The power-failure detection range depends on the state of the TOL pin as follows:Power-failure detection is independent of the battery-backup function and precedes it sequentially as the power-supply voltage drops during a typical power failure.3. Write Protection: This holds the chip-enable output (CEO ) to within 0.2V of V CCI or of the selected bat-tery, whichever is greater. If the chip-enable input (CE )is low (active) when power failure is detected,then CEO is held low until CE is brought high, at which time CEO is gated high for the duration of the power failure. The preceding sequence com-pletes the current RD/WR cycle, preventing data corruption if the RAM access is a WR cycle.4. Battery Redundancy: A second battery is optional.When two batteries are connected, the stronger battery is selected to provide RAM backup and to power the MXD1210. The battery-selection circuitry remains active while in the battery-backup mode,selecting the stronger battery and isolating the weaker one. The battery-selection activity is trans-parent to the user and the system. If only one bat-tery is connected, the second battery input should be grounded.5. Battery-Status Warning: This notifies the system when the stronger of the two batteries measures ≤2.0V. Each time the MXD1210 is repowered(V CCI > V CCTP ) after detecting a power failure, the battery voltage is measured. If the battery in use is low, following the MXD1210 recovery period, the device issues a warning to the system by inhibit-ing the second memory cycle. The sequence is as follows:First access: read memory location n, loc(n) = x Second access: write memory location n,loc (n) = complement (x)Third access: read memory location n, loc (n) = ?If the third access (read) is complement (x), then the battery is good; otherwise, the battery is not good.Return to loc(n) = x following the test sequence.Freshness-Seal ModeThe freshness-seal mode relates to battery longevity during storage rather than directly to battery backup.This mode is activated when the first battery is connect-ed, and is defeated when the voltage at V CCI first exceeds V CCTP . In the freshness-seal mode, both bat-teries are isolated from the system; that is, no current is drained from either battery, and the RAM is not pow-ered by either battery. This means that batteries can be installed and the system can be held in inventory with-out battery discharge. The positive edge rate at VBATT1 and VBATT2 should exceed 0.1V/µs. The bat-teries will maintain their full shelf-life while installed in the system.Battery BackupThe Typical Operating Circuit shows the MXD1210 con-nected in order to write protect the RAM when V CC is less than 4.75V, and to provide battery backup to the supply.MXD1210Nonvolatile RAM Controller_______________________________________________________________________________________5CONDITION V CCTP RANGE (V)TOL = GND 4.75 to 4.50TOL = V CCO4.50 to 4.25M X D 1210Nonvolatile RAM Controller 6_______________________________________________________________________________________Figure 2. Power-Up Timing Diagram Figure 3. Power-Down Timing DiagramMXD1210Nonvolatile RAM Controller_______________________________________________________________________________________7__________________Chip TopographyTRANSISTOR COUNT: 1436;LEAVE SUBSTRATE UNCONNECTED.VBATT2CECEO V CCO VBATT1TOLV CCIGND0.121" (3.073mm)0.080" (2.032mm)Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.8____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600©1996 Maxim Integrated ProductsPrinted USAis a registered trademark of Maxim Integrated Products.M X D 1210Nonvolatile RAM Controller ________________________________________________________Package Information。

Vectron International· v.2005-08-05-05 · page 1 of 4 SEMVectron International Frequency Range1 to 800 MHz (ACMOS and TTL outputs available up to 125 MHz. LVPECL and LVDS output frequencies above 220 MHz are achieved through the use of a PLL multiplier.)Standard Frequencies 19.44, 32.768, 44.736, 51.84, 77.76, 155.52, 622.08 MHzFrequency Stabilities 1ParameterMin TypMax Units Condition Ordering Code5Operating temperature range -100 +100 ppm 0 +70°C C104 (referenced to +25°C)-50 +50 ppm 0 +70°C C505 -25 +25 ppm 0 +70°C C255 -15 +15 ppm 0 +70°C C155 -100 +100 ppm -40 +85°C F104 -50 +50 ppm -40 +85°C F505 -25 +25 ppm -40 +85°C F255 -100 +100 ppm -55 +125°C M104 -65 +65 ppm -55 +125°C M655 Initial accuracy (do not use with -15 +15 ppm @ 25°C T155 overall tolerance code below)-25 +25 ppm @ 25°C T255 -50 +50 ppm @ 25°C T505 -100 +100 ppm @ 25°C T104ParameterMin TypMax Units Condition Ordering Code5Overall tolerance (includes operating -100 +100 ppm 0 +70°C TC104 temperature and initial accuracy)7-50 +50 ppm 0 +70°C TC505-25 +25 ppm 0 +70°C TC255 -100 +100 ppm -40 +85°C TF104 -50 +50 ppm -40 +85°C TF505 -100 +100 ppm -55 +125°C TM104 -80+80 ppm -55 +125°C TM805Additional stability parameters: vs. Supply voltage change vs. Load change vs. Aging / 1st yearvs. Aging / year (following years)-2 -1 -3 -1+2 +1 +3 +1ppm ppm ppm ppmV S ± 5% Load ± 5%Supply Voltage (Vs)ParameterMin Typ Max Units ConditionOrdering Code5Supply voltage4.755.05.25 VDC SV050Current consumption 15 mA ACMOS or TTL 1.0 to 23.9 MHZ (+5 VDC)20 mA ACMOS or TTL 24 to 49.9 MHz 40 mA ACMOS or TTL 50 to 125.00 MHzSupply voltage 3.135 3.3 3.465 VDC SV033 Supply voltage2.375 2.52.625 VDC SV025Current consumption 6 mA ACMOS 1.0 to 14.90 MHZ (+3.3 VDC or +2.5 VDC)8 mA ACMOS 15.0 to 39.9 MHz 12 mA ACMOS 40.0 to 59.9 MHz 16 mA ACMOS 60.0 to 84.9 MHz 40 mA ACMOS 85.0 to 125.0 MHz75 mA LVPECL or LVDS No load <200 MHz 100mALVPECL or LVDS No load >200 MHzTypical ApplicationsFeaturesMilitary Systems5X7 Surface Mount Package Avionics and Instrumentation Reflow Process CompatibleTest Equipment ACMOS, TTL, LVPECL and LVDSMedical EquipmentMIL-PRF-55310 Class B Screening (optional) Military Operating Temperature Range (optional)Vectron International· v.2005-08-05-05 · page 2 of 4 SEMVectron International RF OutputParameterMinTyp MaxUnits ConditionOrdering Code5Signal ACMOSRFALoad1550 pF Signal Level (Vol) 0.5 VDC Vs= 5.0V and 15pF load 0.3 VDC Vs=3.3V and 15pF load 0.25VDC Vs=2.5V and 15pF load Signal Level (Voh)4.5 VDC Vs=5.0V and 15pF load 3.0 VDC Vs=3.3V and 15pF load 2.25VDC Vs=2.5V and 15pF loadRise and fall times for ACMOS (measured 10% to 90%) 10 6 3 ns ns ns 1.0 to 23.9 MHz 24.0 to 79.9 MHz 80.0 to 125.0MHz Duty cycle 45 4055 60% %@ 50% Vs< 15 MHz @ 50% Vs > 15 MHzSignal TTLRFT Load10 Signal Level (Vol) 0.5VDC Vs= 5.0V and 15pF load Signal Level (Voh)4.5VDC Vs= 5.0V and 15pF loadRise and fall times for TTL (measured 0.8V to 2.0V) 5 3 ns ns 1.0 to 23.9 MHz 24 to 125 MHz Duty Cycle45 4055 60% % @ 1.4V < 15 MHz @ 1.4V > 15 MHzSignal LVPECLRFPLoad50 Into Vcc-2V or Thevenin Equivalent Signal Level (Vol) Vs -1.62VDC -40 +85°C operating temp Signal Level (Voh)Vs- 1.025VDC -40 +85°C operating tempRise and fall times (measured @ 20% to 80%)1000 600 ps ps <100 MHz > 100 MHz Duty cycle LVPECL 4555 % @ 50% VddJitter (rms) 10 0.5 ps ps BW = 10Hz to 20 MHz BW = 12 kHz to 20 MHz Period Jitter (pk-pk) 40ps10,000 Samples - Rising edgeSignal LVDSRFLLoad60100 140Between outputsSignal Level (Vol)1.2 VDC Signal Level (Voh)1.4 VDC Differential Voltage (Vod)240 330 460 mVpeakCommon Mode (Offset) Voltage (Vos) 1.1251.2 1.375 V Start-up Time10 mS Rise and fall times 6001000 ps measured @ 20% to 80% of VodDuty cycle 4555 % @ 50% of Vod Jitter (rms) 5 1 ps ps BW = 10Hz to 20 MHz BW = 12 kHz to 20 MHz Period Jitter (pk-pk)40ps 10,000 Samples - Rising edgeAdditional ParametersScreening Vectron Verification9V Screening Class B, MIL-PRF-55310, Rev.D BOutput Enable6Logic "0" input = Outputs disabled (Tri-state)Logic "1" or floating input = Outputs enabled ) Standard (All outputs)Logic "0" or floating input = Outputs enabledLogic "1" input = Outputs disabled (Tri-state )Custom (Contact factory for availability)Weight< 2 gramsProcessing & PackingHandling & processing noteVectron International· v.2005-08-05-05 · page 3 of 4 SEMVectron International Standard EnvironmentalsParameterTest ConditionVibration MIL-STD-202, Method 204, Condition G (30 G, 10Hz-2000Hz) ShockMIL-STD-202, Method 213, Condition I (100 G, 6ms, Sawtooth) AccelerationMIL-STD-883, Method 2001, Condition A (5000 G, Y1 Plane)Temperature Cycling MIL-STD-883, Method 1010, Condition B Thermal Shock MIL-STD-883, Method 107, Condition BSolderabilityMIL-STD-202, Method 208Leak Test (Fine and Gross)MIL-STD-883, Method 1014, Condition A1 and C1Absolute Maximum RatingsParameterMinTypMax Units Condition Supply voltage (Vs) 7.0 V Vs=5.0VDC 7.0 V Vs=3.3VDCOperable temperature range -55 +125 °C Storage temperature range-62+125°CEnclosuresType A ACMOS or TTLType B LVPECL or LVDSPackage Codes:CodesHeight CodesHeight A1 = 4 leads0.074 ± 0.007 B1 = 6 leads0.074 ± 0.007 E1 = Enable/Disable pin 1 (1.88 ± 0.178) E1 = Enable/Disable pin 1 (1.88 ± 0.178)X = N/C pin 1 E2 = Enable/Disable pin 2 X = N/C pin 1 and pin 2 T = Tinned J leads 8T = Tinned J leads 8X = No TinningX = No TinningPin ConnectionsPin Connections1 Enable/Disable or N/C 3 RF Output 1 Enable/Disable or N/C4 RF Output2 Ground (case) 4 Supply Voltage2 N/C5 Complementary Output 3 Ground (Case)6 Supply VoltageVectron International· v.2005-08-05-05 · page 4 of 4 SEMVectron InternationalHow to Order this Product: 10Step 1Use this worksheet to forward the following information to your factory representative (example follows):ModelStabilityCodeInitial AccuracyCode(if required)Supply Voltage Code RF Output Code Screening Code Package Code Enable/DisableCodeTinning CodeC1250 C505 T505SV033RFAVA1E1TStep 2The factory representative will then respond with a Vectron Part Number in the following configuration: Model Package CodeDash Dash NumberC1250[Customer Specified Package Code]-[Factory Generated 4 digit number]Typical P/N C1250A1-0001Notes:1Contact factory for improved stabilities or additional product options. Not all options and codes are available at all frequencies, RF outputs and supply voltages.2Unless otherwise stated all values are valid after warm-up time and refer to typical conditions for supply voltage, frequency control voltage, load, temperature (25°C).3Phase noise degrades with increasing output frequency. 4Subject to technical modification. 5Contact factory for availability. 6Contact factory for other options.7Overall stabilities do not require an initial accuracy code.8Leads tinned IAW Vectron International standard procedure (GR-37409). 9Vectron Verification IAW Vectron International standard process (HK-69314). 10Please be sure to specify nominal frequency.。

物料编号CL10C151JB8NNNC参数_易容网

MLCC即是多层陶瓷电容片式,是电子信息产品不可或缺的基本组件之一。

我国MLCC的生产起步在80年代初,行业早期主要是在外资企业的带动下发展起来的,近年来国内企业在技术上实现突破,行业国产化成效显著,并推动了MLCC产量迅速增长。

目前,MLCC的应用领域已从手机、电脑、电视机等消费电子领域,逐步拓展到新能源发电、新能源汽车、节能灯具、轨道交通、直流输变电、三网融合、高清电视、机顶盒、手机电视等多个行业。

对于这个悄悄活跃在人们生活中的元件你又知道多少呢.

本次易容网为大家推荐比较常用的MLCC三星 | Samsung品牌的料号CL10C151JB8NNNC相关参数

易容网是深圳市易容信息技术有限公司独自研发的全球最大的MLCC搜索采购服务网站,2014年创立于深圳市南山区,全国首家电子元器件行业电容元件的搜索引擎及o2o商务服务平台。

易容网()现已建成全球最大的MLCC电容搜索引擎数据库,包含全球25家电容生产厂商超过28万组MLCC产品数据,用户可根据行业应用、物料编号、规格参数等信息快速的找到所有相关的MLCC电容数据。

易容网在搜索服务的前提下还提供村田、TDK、国巨、太阳诱电、风华高科等常见品牌产品的o2o商务服务,让企业客户实现询价、报价、在线订单、出库、实时物流、签收、账期服务等在线一站式商务服务体验。

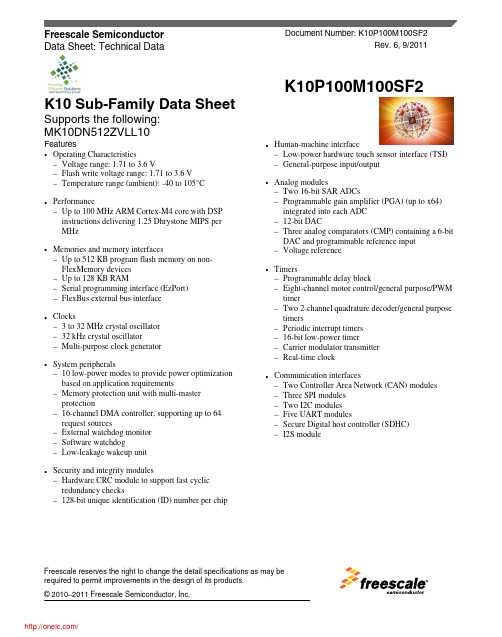

K10P100M100SF2K10 Sub-Family Data SheetSupports the following:MK10DN512ZVLL10Features•Operating Characteristics–Voltage range: 1.71 to 3.6 V–Flash write voltage range: 1.71 to 3.6 V –Temperature range (ambient): -40 to 105°C •Performance–Up to 100 MHz ARM Cortex-M4 core with DSP instructions delivering 1.25 Dhrystone MIPS per MHz •Memories and memory interfaces–Up to 512 KB program flash memory on non-FlexMemory devices –Up to 128 KB RAM–Serial programming interface (EzPort)–FlexBus external bus interface •Clocks– 3 to 32 MHz crystal oscillator –32 kHz crystal oscillator–Multi-purpose clock generator•System peripherals–10 low-power modes to provide power optimization based on application requirements–Memory protection unit with multi-master protection–16-channel DMA controller, supporting up to 64request sources–External watchdog monitor –Software watchdog–Low-leakage wakeup unit •Security and integrity modules–Hardware CRC module to support fast cyclic redundancy checks–128-bit unique identification (ID) number per chip•Human-machine interface–Low-power hardware touch sensor interface (TSI)–General-purpose input/output •Analog modules–Two 16-bit SAR ADCs–Programmable gain amplifier (PGA) (up to x64)integrated into each ADC –12-bit DAC–Three analog comparators (CMP) containing a 6-bit DAC and programmable reference input –Voltage reference •Timers–Programmable delay block–Eight-channel motor control/general purpose/PWM timer–Two 2-channel quadrature decoder/general purpose timers–Periodic interrupt timers –16-bit low-power timer–Carrier modulator transmitter –Real-time clock •Communication interfaces–Two Controller Area Network (CAN) modules –Three SPI modules –Two I2C modules –Five UART modules–Secure Digital host controller (SDHC)–I2S moduleFreescale Semiconductor Document Number: K10P100M100SF2Data Sheet: Technical DataRev. 6, 9/2011Freescale reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.© 2010–2011 Freescale Semiconductor, Inc.Table of Contents1Ordering parts (3)1.1Determining valid orderable parts (3)2Part identification (3)2.1Description (3)2.2Format (3)2.3Fields (3)2.4Example (4)3Terminology and guidelines (4)3.1Definition: Operating requirement (4)3.2Definition: Operating behavior (5)3.3Definition: Attribute (5)3.4Definition: Rating (6)3.5Result of exceeding a rating (6)3.6Relationship between ratings and operatingrequirements (6)3.7Guidelines for ratings and operating requirements (7)3.8Definition: Typical value (7)3.9Typical value conditions (8)4Ratings (8)4.1Thermal handling ratings (9)4.2Moisture handling ratings (9)4.3ESD handling ratings (9)4.4Voltage and current operating ratings (9)5General (10)5.1AC electrical characteristics (10)5.2Nonswitching electrical specifications (10)5.2.1Voltage and current operating requirements (10)5.2.2LVD and POR operating requirements (12)5.2.3Voltage and current operating behaviors (12)5.2.4Power mode transition operating behaviors (13)5.2.5Power consumption operating behaviors (14)5.2.6EMC radiated emissions operating behaviors (17)5.2.7Designing with radiated emissions in mind (18)5.2.8Capacitance attributes (18)5.3Switching specifications (18)5.3.1Device clock specifications (18)5.3.2General switching specifications (18)5.4Thermal specifications (19)5.4.1Thermal operating requirements (19)5.4.2Thermal attributes (20)6Peripheral operating requirements and behaviors (20)6.1Core modules (20)6.1.1Debug trace timing specifications (21)6.1.2JTAG electricals (21)6.2System modules (24)6.3Clock modules (24)6.3.1MCG specifications (24)6.3.2Oscillator electrical specifications (27)6.3.332kHz Oscillator Electrical Characteristics (29)6.4Memories and memory interfaces (30)6.4.1Flash (FTFL) electrical specifications (30)6.4.2EzPort Switching Specifications (32)6.4.3Flexbus Switching Specifications (32)6.5Security and integrity modules (35)6.6Analog (35)6.6.1ADC electrical specifications (35)6.6.2CMP and 6-bit DAC electrical specifications (43)6.6.312-bit DAC electrical characteristics (46)6.6.4Voltage reference electrical specifications (49)6.7Timers (50)6.8Communication interfaces (50)6.8.1CAN switching specifications (50)6.8.2DSPI switching specifications (limited voltagerange) (51)6.8.3DSPI switching specifications (full voltage range).526.8.4I2C switching specifications (54)6.8.5UART switching specifications (54)6.8.6SDHC specifications (54)6.8.7I2S switching specifications (55)6.9Human-machine interfaces (HMI) (57)6.9.1TSI electrical specifications (57)7Dimensions (58)7.1Obtaining package dimensions (58)8Pinout (59)8.1K10 Signal Multiplexing and Pin Assignments (59)8.2K10 Pinouts (63)9Revision History (64)1Ordering parts1.1Determining valid orderable partsValid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to and perform a part number search for the following device numbers: PK10 and MK10.2Part identification2.1DescriptionPart numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.2.2FormatPart numbers for this device have the following format:Q K## A M FFF R T PP CC N2.3FieldsThis table lists the possible values for each field in the part number (not all combinations are valid):2.4ExampleThis is an example part number:MK10DN512ZVMD103Terminology and guidelines3.1Definition: Operating requirementAn operating requirement is a specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip.3.1.1ExampleThis is an example of an operating requirement, which you must meet for the accompanying operating behaviors to be guaranteed:3.2Definition: Operating behaviorAn operating behavior is a specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions.3.2.1ExampleThis is an example of an operating behavior, which is guaranteed if you meet the accompanying operating requirements:3.3Definition: AttributeAn attribute is a specified value or range of values for a technical characteristic that are guaranteed, regardless of whether you meet the operating requirements.3.3.1ExampleThis is an example of an attribute:3.4Definition: RatingA rating is a minimum or maximum value of a technical characteristic that, if exceeded,may cause permanent chip failure:•Operating ratings apply during operation of the chip.•Handling ratings apply when the chip is not powered.3.4.1ExampleThis is an example of an operating rating:3.5Result of exceeding a rating40302010Measured characteristicOperating ratingF a i l u r e s i n t i m e (p p m )The likelihood of permanent chip failure increases rapidly assoon as a characteristic begins to exceed one of its operating ratings.3.6Relationship between ratings and operating requirements–∞∞pe r at i ng o r h a n d l i n g r at i n g (m a x .)pe r a ti n g re q ui r e m e n t (m a x .)per a ti n g re q u i r em en t (mi n .)p e r a t i n g o r h a n d l in g r a t i n g (mi n .)3.7Guidelines for ratings and operating requirementsFollow these guidelines for ratings and operating requirements:•Never exceed any of the chip’s ratings.•During normal operation, don’t exceed any of the chip’s operating requirements.•If you must exceed an operating requirement at times other than during normal operation (for example, during power sequencing), limit the duration as much as possible.3.8Definition: Typical valueA typical value is a specified value for a technical characteristic that:•Lies within the range of values specified by the operating behavior•Given the typical manufacturing process, is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions Typical values are provided as design guidelines and are neither tested nor guaranteed.3.8.1Example 1This is an example of an operating behavior that includes a typical value:3.8.2Example 2This is an example of a chart that shows typical values for various voltage and temperature conditions:0.900.951.001.051.10500100015002000250030003500400045005000150 °C 105 °C 25 °C –40 °CV DD (V)I (μA )D D _S T O P T J 3.9Typical value conditionsTypical values assume you meet the following conditions (or other conditions asspecified):4Ratings4.1Thermal handling ratings2.Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for NonhermeticSolid State Surface Mount Devices.4.2Moisture handling ratingsSolid State Surface Mount Devices.4.3ESD handling ratingsModel (HBM).2.Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method forElectrostatic-Discharge-Withstand Thresholds of Microelectronic Components.4.4Voltage and current operating ratings5General5.1AC electrical characteristicsUnless otherwise specified, propagation delays are measured from the 50% to the 50%point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.Figure 1. Input signal measurement referenceAll digital I/O switching characteristics assume:1.output pins•have C L =30pF loads,•are configured for fast slew rate (PORTx_PCRn[SRE]=0), and •are configured for high drive strength (PORTx_PCRn[DSE]=1)2.input pins•have their passive filter disabled (PORTx_PCRn[PFE]=0)5.2Nonswitching electrical specifications分销商库存信息: FREESCALEMK10DN512ZVLL10。