AFL2824DY-CH中文资料

- 格式:pdf

- 大小:128.09 KB

- 文档页数:11

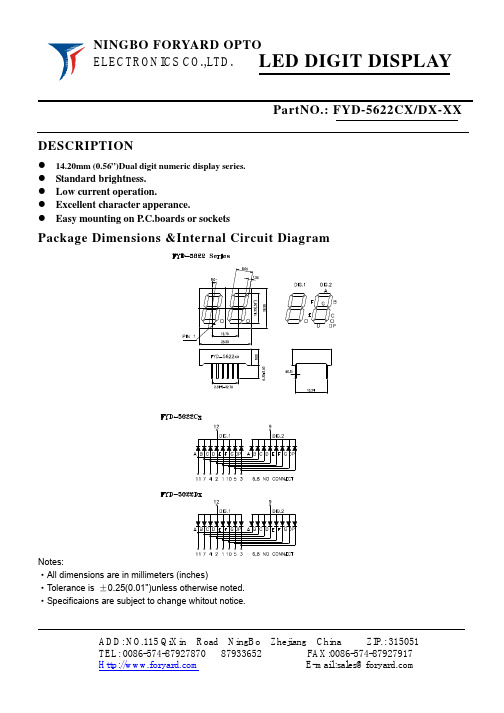

PartNO.:FYD-5622CX/DX-XXADD:NO.115QiXin Road NingBo Zhejiang China ZIP.:315051DESCRIPTION●14.20mm (0.56”)Dual digit numeric display series.●Standard brightness.●Low current operation.●Excellent character apperance.●Easy mounting on P.C.boards or socketsPackage Dimensions &Internal Circuit DiagramNotes:·All dimensions are in millimeters (inches)·Tolerance is ±0.25(0.01")unless otherwise noted.·Specificaions are subject to change whitoutnotice.PartNO.:FYD-5622CX/DX-XXADD:NO.115QiXin Road NingBo Zhejiang China ZIP.:315051:Absolute maximum ratings (Ta=25℃)ValueParameterSymbolTest ConditionMinMaxUnitReverse V oltage VR IR=30μA 5-----V ForwardCurrentIF -----------30mA Power Dissipation Pd -----------100mW Pulse Current Ipeak Duty=0.1mS,1KHz ------150mA Operating Temperature Topr ------40+85°C Storage TemperatureTstr------40+85°C■Description:·Color Code &Chip characteristics:(Test Condition:IF=20mA)ForwardVoltage(VF)Unit:V Emitting Color Dice Material PeakWaveLength (λP )Spectral Line halfwidth(△λ1/2)Typ Max Luminous Intensity (Iv)Unit:ucd H Red GaP/GaP 700nm 90nm 2.25 2.50500S Hi Red GaAlAs/GaAs,SH 660nm 20nm 1.85 2.203500D Super Red GaAlAs/GaAs,DH 660nm 20nm 1.85 2.206000UR Ultra Red GaAlAs/GaAs,DD H660nm 20nm1.852.2012000E Orange GaAsP/GaP 635nm 35nm 2.10 2.502500Y Yellow GaAsP/GaP 585nm 35nm 2.10 2.502000G Green GaP/GaP 570nm 30nm 2.20 2.502500B Blue InGaN 460nm 30nm 2.83.507000·-XX:Surface /Lens color :Number12345Ref Surface Color White Black Gray Red Green Epoxy ColorWater clearWhite diffusedRed DiffusedGreen DiffusedYellow DiffusedPartNO.:FYD-5622CX/DX-XXADD:NO.115QiXin Road NingBo Zhejiang China ZIP.:3150511.00.53504004505005506006507007508008509009501000(A)(B)(C)(D)(2)(3)(8)(4)(1)(6)(5)(9)(10)Wavelength(nm)RELATIVE INTENSITY Vs WAVELENGTH()λp (1)-GaAsP/GaAs 655nm/Red (2)-GaP 570nm/Yellow Green (3)-GaAsP/GaP 585nm/Yellow(4)-GaAsp/GaP 635nm/Orange &Hi-Eff Red (5)-GaP 700nm/Bright Red(6)-GaAlAs/GaAs 660nm/Super Red (8)-GaAsP/GaP 610nm/Super Red(9)-GaAlAs 880nm(10)-GaAs/GaAs &GaAlAs/GaAs 940nm (A)-GaN/SiC 430nm/Blue (B)-InGaN/SiC 470nm/Blue(C)-(D)-InGaN/SiC 505nm/Ultra Green InGaAl/SiC 525nm/Ultra Green504030201001.21.62.0 2.4 2.63.016345285040302010020406080100162,4,8,A 353210.50.20.1-30-20-10102030405060701542310987654321110100100010,00010KHz 3KHz1KHz 300KHz 100KHz F-REFRESH RATE100KHz 30KHz10KHz 3KHz 1KHz 300Hz 100Hz 10987654321110100100010,000FORWARD VOLT AGE (Vf)FORWARD CURRENT VS.FORWARD VOLTAGERELATIVE LUMINOUSINTENSITY VS.FORWARD CURRENTAMBIENT TEMPERATURE T a()℃FORWARD CURRENT VS.AMBIENT TEMPERATUREtp-PULSE DURATION uS (1,2,3,4,6,8,B.D.J.K)NOTE:25free air temperature unless otherwise specified℃tp-PULSE DURATION uSFORWARD CURRENT(mA)FORWARD CURRENT (mA)RELA TIVE LUMINOUS INTENSITYFORWARD CURRENT(mA)RELATIVE LUMINOUS INTENSITYAMBIENT TEMPERATURE T a()℃(5)Ipeak MAX.IDC MAX.Ipeak MAX.IDC MAX.PartNO.:FYD-5622CX/DX-XXADD:NO.115QiXin Road NingBo Zhejiang China ZIP.:315051tapy QTY/foam(pcs)QTY /Bundle (pcs)QTY /CARTONDimensionFYD-5622CDx-xx 5*13=6565*16=10401040*4=4160。

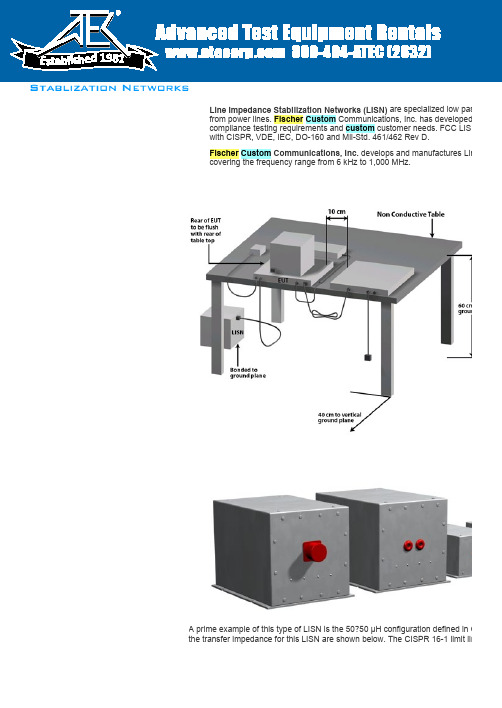

1981Line Impedance Stabilization Networks (LISN) are specialized low pasfrom power lines. Fischer Custom Communications, Inc. has developedcompliance testing requirements and custom customer needs. FCC LISwith CISPR, VDE, IEC, DO-160 and Mil-Std. 461/462 Rev D.Fischer Custom Communications, Inc. develops and manufactures Lincovering the frequency range from 6 kHz to 1,000 MHz.A prime example of this type of LISN is the 50?50 µH configuration defined in Cthe transfer impedance for this LISN are shown below. The CISPR 16-1 limit linThe model FCC-LISN-50-25-2 is produced in accord with the required schem requirements. The impedance versus frequency curve of this LISN is superim configuration. The 50Ω50Ω µH configuration is often used for Mil Std conduct specific details refer to Mil Std 461/462 D.In addition to this LISN there are 50Ωversions used to test both to lower and require conducted emission measurements on electronic devices from 9 kHz a 250 µH inductor and additional resistor and capacitance networks are added defines this LISN as 50Ω50Ω µH + 5 W. This type of LISN is often used when In contrast the aerospace, automotive and aircraft industries require conducte MHz. To achieve the higher bandwidth a 5 µH inductor is used.Voltage and current rating of the LISN are the second characteristic. It is impo to operate as intended. Fischer Custom Communications, Inc. offers LISN's line and current ratings from 16 A to 200 A..The third parameter is the number of power conductors or lines. EMI specifica leads to be tested for conducted emissions. Any neutral or ground wires not c tested. DC and AC single phase power circuits must be tested using LISN mo power network requires tests to be conducted with a LISN's containing three p system must be tested with LISN modules having four lines. To maximize flex LISN modules containing one, two and four power conductors.Fischer Custom Communications Inc. offers over twenty connectors. The ke in compliance with IEC 1010, not cause the impedance of the LISN to vary an Fischer Custom Communications Inc. LISN's come with transfer impedance We strongly recommend that IEC 320 or NEMA connectors be used to elimina All of Fischer Custom Communications, Inc. LISN's are easily mounted to th Additional grounding is available.LISN Selection Guide CodesConnector Code01020304050607080910111213 Multi-Contact Satety SocketSuperior Plug and Jack Safety SocketIEC 320, 10 A / 16A PowerIEC 320, 10 A / 16A PowerFrench /Belgium 16 A PowerBS 1363 13 A British PowerCEE 7/7 16A Schuko Berman PowerNema 5-15, 15 A US PowerNema 5-15, 15 A US PowerIEC 309, 16 A 3-Wire PowerIEC 309, 16 A 3-Wire PowerHubbel 330P6W, 30 A 3-Wire US PowerHubbel 330P6W, 30 A 3-Wire US PowerT010203040506070809CFFMMDSTV141516171819 Hubbel 330P6W, 30 A 3-Wire US Power Hubbel 330P6W, 30 A 3-Wire US Power IEC 309, 32 A 5-Wire PowerIEC 309, 32 A 5-Wire PowerIEC 309, 32 A 5-Wire PowerLC Coaxial for TempestFiltered LISN's remotely switched LISN's and low profile LISN's for under turn GHz are now available.Remotely switched LISN's may be controlled by the remote control or via a pe output 0-5 volt DC logic levels. The remote control and 50 foot cable are supp remote connector is filtered to prevent external noise from entering the LISN e LISN Selection GuideModel MaximumFrequencyNetworkInductanceMaximumCurrent*StandardMaximumVoltageFCC-LISN-5-50-10.1-100MHz50Ω/5µH50 A240FCC-LISN-5-50-1-DO-1600.1-400MHz50Ω/5µH50 A240FCC-LISN-5-50-1-T 0.1-1,000MHz50Ω/5µH50 A240FCC-LISN-5-100-10.1-65 MHz50Ω/5µH100 A240FCC-LISN-50-50-10.15-100MHz50Ω/50µH50 A240FCC-LISN-50-100-10.15-30MHz50Ω/50µH100 A240FCC-LISN-50-200-10.15-30MHz50Ω/50µH200 A240FCC-LISN-57-50-10.01-10MHz50Ω/57µH50 A240FCC-LISN-50-25-20.15-100MHz50Ω/50µH25 A240FCC-LISN-50-32-20.15-100MHz50Ω/50µH32 A240FCC-LISN-50-50-20.15-100MHz50Ω/50µH50 A240FCC-LISN-50-32-40.15-100MHz50Ω/50µH32 A240FCC-LISN-50-50-40.15-100MHz50Ω/50µH50 A240FCC-LISN-50-100-40.15-30MHz50Ω/50µH100 A240FCC-LISN-50/250-25-20.009-100MHz50Ω/50µH +5Ω50/250 µH25 A240FCC-LISN-50/250-32-20.009-100MHz50Ω/50µH +5Ω50/250 µH32 A240FCC-LISN-50/250-32-40.009-100MHz50Ω/50µH +5Ω50/250 µH32 A240FCC-LISN-50/250-50-20.009-100MHz50Ω/50µH +5Ω50/250 µH50 A240FCC-LISN-50/250-50-40.009-100MHz50Ω/50µH +5Ω50/250 µH50 A240FCC-LISN-50/250-100-20.009-30MHz50Ω/50µH +5Ω50/250 µH100 A240。

厦华P24机芯介绍厦华P24机芯是采用菲利莆片的一款性能的价格比较高的机芯,该机芯调试简单,工艺性好,现就其电源、解码芯片、枕校电路做个技术性介绍(以厦华XT-2560/2980)机划为例)一、开关电源本机芯采用自激式脉冲调宽开关电源,具体电路见图<l>。

1.低通滤波电路AC220V经电源线勾焊在A1、A2焊片上,经保险丝FU501,进入由C509、R503、L501、C508组成的低通滤波器,通过插头X503到电源开关,然后回到插头X502分三路输出:一路送到由RT501、X501组成的消磁电路;另一路送到桥式整流电路,第三路径T501降压、整流、稳压后,产生+5V的待机电压,送CPU及遥控电路。

该低通滤波器用于防止高频干扰信号通过电源线进入电视机而产生的干扰,同时防止机内的高频脉冲进入交流电网造成污染。

2.待机电压产生电路该电路由降压变压器T501、桥式整流二极管VD505~VD 508,高频滤波电容c510~C513。

滤波电容C514,降压电阻RT504以及由R505、C 515、VD 509、V501、C 517、C 516 组成的稳压电路组成。

用于为N801提供+5V工作电压,红外接收头工作电压,电源指示灯电压。

3.自动消磁电路自动消磁电路由正温度系数热敏电阻RT501,消磁线圈X501组成,刚接通电源时RT501电阻值很小,X501中有很大电流流过,该电流在通过RT501时,使其温度上升,电阻值迅速增加,流过X501的电流急剧衰减,在消磁线圈X501周围产生一个由强到弱变化的交变磁场,以消除由显象管荫罩板上的杂散磁场造成的光栅色纯不良。

4.整流和滤波电路整流由VD501-VD504组成的桥式整流电路,高频滤波电容C501-C504,限流电阻R501组成。

滤波由C505、C506组成。

用于将AC20V电压转DC300V电压。

5.开关稳压电路(1)电源的启动和开关电源的自激振荡过程整流和滤波电路输出的+300V电压,一路经开关变压器T502的初级绕组6 ~ 9加到开关调整管V504 C极,另一路经由R509、R511、R517组成的启动电路,为V504提供1b,使V504导通,产生IC,流过T502的初级绕组,产生6正9负的自感电。

®345Power Quality Clamp Meter用户手册(Simplified Chinese)October 2006© 2006 Fluke Corporation. All rights reserved.Product names are trademarks of their respective companies.有限担保和有限责任Fluke担保在正常使用和保养的情况下,其产品没有材料和工艺上的缺陷。

担保期为从购买产之日起的一年内。

部件、产品修理和服务的担保期限为90天。

本担保仅限于Fluke授权零商的原购买人或最终用户,并且不适用于一次性电池、电缆接头、电缆绝缘接头或Fluke认为于误用、改装、疏忽、污染及意外或异常操作或处理引起的任何产品损坏。

Fluke担保软件依照功能规格正常运行90天,并且软件是记录在无缺陷的媒介上。

Fluke并不担保软件无错或在运行中不会中断。

Fluke授权的零售商应仅对最终用户就新的和未使用的产品提供本担保,但无权代表Fluke公司提供额外或不同的担保。

只有通过Fluke 授权的销售店购买的产品或买方已经按适的国际格付款才能享受Fluke的担保支持。

在一国购买的产品需在他国修理时,Fluke有权向买方求负担重大修理/零件更换费用。

Fluke的担保为有限责任,由Fluke决定是否退还购买金额、免费修理或更换在担保期间退还Fluke授权服务中心的故障产品。

如需要保修服务,请与您就近的Fluke授权服务中心联系,获得退还授权信息;然后将产品寄至务中心并附上产品问题描述,同时预付运费和保险费(目的地离岸价格)。

Fluke不承担运途中发生的损坏。

在保修之后,产品将被寄回给买方并提前支付运输费(目的地交货)。

如果Fluke认定产品故障是由于疏忽、误用、污染、修改、意外或不当操作或处理状况而产生包括未在产品规定的额定值下使用引起的过压故障;或是由于机件日常使用损耗,则Fluke会估算修理费用,在获得买方同意后再进行修理。

FOXBORO ®The FBM214 HART ® Communication Input Interface Module provides eight input channels, each accepting a 4 to 20mA analog signal or a digital HART signal superimposed on a 4 to 20 mA analog input signal.FEATURESKey features of the FBM214 module are:Eight analog input channels, each accepting oneof the following inputs:•Standard 4 to 20 mA analog sensor signal •Digital HART Frequency Shift Keying (FSK) signal superimposed on a 4 to 20 mA analog input signal.FSK modem dedicated to each input channel forbi-directional digital communications with a HART field deviceAnalog to digital conversion of each of the 4to20mA input signals from the HART devicesSupport for the HART universal commandsnecessary to interface the field device with the I/A Series ® system databaseGalvanic isolation of the group of 8 inputchannels from ground and module logicCompact, rugged design suitable for enclosure inClass G3 (harsh) environmentsHigh accuracy achieved by sigma-delta dataconversions for each channelTermination Assemblies (TAs) for locally orremotely connecting field wiring to the FBM214Termination Assemblies for per channel internallyand/or externally loop powered transmitters.PSS 21H-2Z14 B4 Page 2OVERVIEWThe FBM214 HART Communication Input Interface Module contains eight 4to20mA group isolated analog input channels. The FBM214 supports any mix of standard 4to20mA devices and HART devices.The FBM214 serves as a HART communications field device host, enabling the I/A Series system to request and receive two digital messages per second from the field device. The message pass-through capability can be used to support HART universal, common practice, and device-specific commands, but not the burst communication mode. These commands are implemented using the Intelligent Field Device Configurator (IFDC — refer toPSS 21S-8A3 B3 for details).The FBM214 provides a common isolated power supply to power all eight channels. Optionally, the channels can be powered by an external power supply. However, when a common external power supply is used with two or more channels, a Cable Balun module is required to prevent channel cross talk.COMPACT DESIGNThe FBM214 has a compact design, with a rugged extruded aluminum exterior for physical protection of the circuits. Enclosures specially designed for mounting the FBMs provide various levels of environmental protection, up to harsh environments per ISA Standard S71.04.HIGH ACCURACYFor high accuracy, the module incorporates a Sigma-Delta converter which can provide new analog input values for each channel every 100 milliseconds.VISUAL INDICATORSLight-emitting diodes (LEDs) incorporated into the front of the module provide visual indication of the module’s operational status, and communication activity on the channels.EASY REMOVAL/REPLACEMENTThe module can be removed/replaced without removing field device termination cabling, power, or communications cabling.FIELDBUS COMMUNICATIONA Fieldbus Communication Module or a Control Processor interfaces the redundant 2 Mbps module Fieldbus used by the FBMs. The FBM214 module accepts communication from either path (A or B) of the redundant 2 Mbps fieldbus – should one path fail or be switched at the system level, the module continues communication over the active path.The use of an external power supply common to two or more loops requires a Cable Balun Module to maintain communication signal line balance.MODULAR BASEPLATE MOUNTINGThe module mounts on a modular baseplate which accommodates up to four or eight FBMs. The modular baseplate is either DIN rail mounted or rack mounted, and includes signal connectors for redundant fieldbus, redundant independent dc power, and termination cables.TERMINATION ASSEMBLIESField input signals connect to the FBM subsystem via DIN rail mounted TAs. The TAs used with theFBM214 are described in “TERMINATION ASSEMBLIES AND CABLES” on page8.PSS 21H-2Z14 B4Page 3CABLE BALUN MODULEThe Cable Balun module is used to maintain digital communication line balance for HART Transmitter to FBM loops that are powered from a common external power supply. This powering effectively connects one line of each loop together. Without the Baluns, in each loop so powered, the common connection at the external power supply, would cause near end crosstalk at the system end of the loop wiring cable. Loops using FBM internal power source do not require Baluns.The Cable Balun module contains multiple Baluns. One Balun segment is interconnected in each loop powered from an external power supply per the diagram above. There is one Cable Balun module.Figure 1. Cable Balun Module Cable Balun ModuleModule Model ModulePart No.No. of Balunsin the ModuleCBM-4P0903SV4PSS 21H-2Z14 B4Page 4FUNCTIONAL SPECIFICATIONSField Device ChannelsVERSION SUPPORTEDHART Protocol v6INTERFACE8 group-isolated channelsCOMMUNICATION TO THE DEVICEPoint-to-point, master/slave, asynchronous, half-duplex, at 1200 baud.ERROR CHECKINGParity on each byte, and one CRC check byte.SPEED2 messages per secondFASTEST ALLOWED ECB BLOCK PERIOD500 msecMAXIMUM DISTANCE (FBM214 TO FIELDDEVICE)Meets HART FSK physical layer specificationHCF_SPEC-54, Revision 8.1 [up to 3030 m(10000ft)](1).COMPLIANCE VOLTAGE18 V dc minimum at 20.5 mACURRENT INPUTSSense Resistor61.9 Ω nominalTotal Input Resistance280 Ω minimumAccuracy (Includes Nonlinearity)±0.03% of full scaleTemperature Coefficient50 ppm/ºCResolution15 bitsUpdate Rate100 msIntegration Time500 msCommon Mode Rejection>100 db at 50 or 60 HzNormal Mode Rejection>35 db at 50 or 60 HzMAXIMUM LOOP RESISTANCE280 Ω (not including the field device)(2)LOOP POWER SUPPLY PROTECTIONEach channel is galvanically group isolated,current limited and voltage regulated. All inputsare limited by their design to less than 30 mA. Ifthe current limit circuit shorts out, the current islimited to about 85 mA.FBM INPUT IMPEDANCE280 Ω minimumFBM INTERNAL POWER FOR FIELD DEVICE24 V dc ±10% common power supply for allchannels. Loop load limited to one device perchannel.ISOLATIONThe channels are not galvanically isolated fromeach other, but are galvanically isolated (bothoptical and transformer isolation) as a group from ground and module logic. Inputs use an internal FBM isolated power supply for field power. Themodule withstands, without damage, a potential of 600 V ac applied for one minute between the group-isolated channels and earth (ground).CAUTIONThis does not imply that these channels areintended for permanent connection tovoltages of these levels. Exceeding the limitsfor input voltages, as stated elsewhere in thisspecification, violates electrical safety codesand may expose users to electric shock. Fieldbus CommunicationCommunicates with its associated FCM or FCP via the redundant 2 Mbps module FieldbusHEAT DISSIPATION4 W (maximum)(1)The maximum allowable distance decreases when the loop is operated through an intrinsic safety barrier. The maximum distance ofthe field device from the FBM is a function of compliance voltage, wire gauge and voltage drop at the device.(2)In an intrinsic safety application, if a zener barrier is used between the FBM and the field device, the power supply must be set at24V dc +5%, -1%. There are no specific constraints with the use of galvanic barriers.PSS 21H-2Z14 B4Page 5 FUNCTIONAL SPECIFICATIONS (CONTINUED)Power RequirementsINPUT VOLTAGE RANGE (REDUNDANT)24V dc ±5%CONSUMPTION7 W (maximum)Regulatory ComplianceELECTROMAGNETIC COMPATIBILITY (EMC) European EMC Directive 89/336/EECMeets:EN 50081-2 Emission standardEN 50082-2 Immunity standardEN 61326 Annex A (Industrial Levels) CISPR 11, Industrial Scientific and Medical(ISM) Radio-frequency Equipment -Electromagnetic Disturbance Characteristics- Limits and Methods of MeasurementMeets Class A LimitsIEC 61000-4-2 ESD ImmunityContact 4 kV, air 8 kVIEC 61000-4-3 Radiated Field Immunity10 V/m at 80 to 1000 MHzIEC 61000-4-4 Electrical FastTransient/Burst Immunity2 kV on I/O, dc power and communicationlinesIEC 61000-4-5 Surge Immunity2kV on ac and dc power lines; 1kV on I/Oand communications linesIEC 61000-4-6 Immunity to ConductedDisturbances Induced by Radio frequencyFields10 V (rms) at 150 kHz to 80 MHz on I/O,dc power and communication linesIEC 61000-4-8 Power Frequency MagneticField Immunity30 A/m at 50 and 60 HzPRODUCT SAFETY (FBM AND CABLE BALUN) Underwriters Laboratories (UL) for U.S. andCanadaUL/UL-C listed as suitable for use inUL/UL-C listed Class I, Groups A-D;Division 2; temperature code T4 enclosurebased systems. These modules are also ULand UL-C listed as associated apparatus forsupplying non-incendive communicationcircuits for Class I, Groups A-D hazardouslocations when connected to specifiedI/A Series® processor modules as describedin the I/A Series DIN Rail MountedSubsystem User’s Guide (B0400FA). Wherepower is supplied by the FBM,communications circuits also meet therequirements for Class2 as defined inArticle725 of the National Electrical Code(NFPA No.70) and Section 16 of theCanadian Electrical Code (CSA C22.1).Conditions for use are as specified in theI/A Series DIN Rail Mounted SubsystemUser’s Guide (B0400FA).European Low Voltage Directive 73/23/EECand Explosive Atmospheres (ATEX) directive94/9/ECCENELEC (DEMKO) certified as EEx nA IICT4 for use in CENELEC certified Zone 2enclosure certified as associated apparatusfor supplying non-incendive field circuits forZone 2, Group IIC, potentially explosiveatmospheres when connected to specifiedI/A Series processor modules as describedin the I/A Series DIN Rail MountedSubsystem User’s Guide (B0400FA). Also,see Table1 on page9.Calibration RequirementsCalibration of the module or termination assembly is not required.PSS 21H-2Z14 B4Page 6ENVIRONMENTAL SPECIFICATIONS(3)OperatingTEMPERATUREModule-20 to +70°C (-4 to +158°F)Termination AssemblyPVC-20 to +50°C (-4 to +122°F)PA-20 to +70°C (-4 to +158°F) RELATIVE HUMIDITY5 to 95% (noncondensing)ALTITUDE-300 to +3,000m (-1,000 to +10,000ft)StorageTEMPERATURE-40 to +70°C (-40 to +158°F)RELATIVE HUMIDITY5 to 95% (noncondensing)ALTITUDE-300 to +12,000m (-1,000 to +40,000ft) ContaminationSuitable for use in Class G3 (Harsh) environments as defined in ISA Standard S71.04, based on exposure testing according to EIA Standard 364-65, Class III. Vibration7.5 m/S2 (0.75 g) from 5 to 500 Hz(3)The environmental limits of this module may be enhanced by the type of enclosure containing the module. Refer to the applicableProduct Specification Sheet (PSS) which describes the specific type of enclosure that is to be used.PSS 21H-2Z14 B4Page 7 PHYSICAL SPECIFICATIONSMountingMODULEFBM214 mounts on a modular baseplate. Thebaseplate can be mounted on a DIN rail(horizontally or vertically), or horizontally on a19-inch rack using a mounting kit. Refer toPSS21H-2W6B4 for details.TERMINATION ASSEMBLYThe TA mounts on a DIN rail and accommodates multiple DIN rail styles including 32mm (1.26in) and 35mm 1.38in).MassMODULE284 g (10 oz) approximateTERMINATION ASSEMBLYCompression181 g (0.40 lb) approximateRing Lug249 g (0.55 lb) approximateDimensions – ModuleHEIGHT102 mm (4 in)114 mm (4.5 in) including mounting lugsWIDTH45 mm (1.75 in)DEPTH104 mm (4.11 in)Dimensions – Termination AssemblySee page10.Part NumbersFBM214 MODULEP0922VTTERMINATION ASSEMBLIESSee “FUNCTIONAL SPECIFICATIONS –TERMINATION ASSEMBLIES” on page8. Termination CablesCABLE LENGTHSUp to 30 m (98 ft)CABLE MATERIALSPolyurethane or Hypalon®/XLPTERMINATION CABLE TYPEType 1 – See Table2 on page9.CABLE CONNECTION – TA25-pin male D-subminiatureConstruction – Termination AssemblyMATERIALPolyvinyl Chloride (PVC), compressionPolyamide (PA), compressionPVC, ring lugFAMILY GROUP COLORGreen – communicationTERMINAL BLOCKS3 tiers, 8 positionsField Termination ConnectionsCOMPRESSION-TYPE ACCEPTED WIRINGSIZESSolid/Stranded/AWG0.2 to 4 mm2/0.2 to 2.5 mm2/24 to 12 AWGStranded with Ferrules0.2 to 2.5 mm2 with or without plastic collarRING-LUG TYPE ACCEPTED WIRING SIZES#6 size connectors (0.375 in (9.5 mm))0.5 to 4 mm2/22 AWG to 12 AWGPSS 21H-2Z14 B4Page 8TERMINATION ASSEMBLIES AND CABLESField input signals connect to the FBM subsystem via DIN rail mounted Termination Assemblies, which are electrically passive.TAs for the FBM214 are available in the following forms: Compression screw type using Polyvinyl Chloride(PVC) materialCompression screw type using Polyamide (PA) material Ring lug type using PVC material.See the following “FUNCTIONAL SPECIFICATIONS –TERMINATION ASSEMBLIES” for a list of TAs used with the FBM214.The FBM214 provides sufficient loop resistance to allow use of the HART Hand-Held Terminal, or PC20 Intelligent Field Device Configurator (PSS 2A-1Z3 E).A removable termination cable connects the DIN railmounted TA to the FBM via a field connector on the baseplate in which the FBM is installed. Termination cables are available in the following materials: PolyurethaneHypalon XLP .Termination cables are available in a variety of lengths, up to 30 meters (98feet), allowing the Termination Assembly to be mounted in either theenclosure or in an adjacent enclosure. See Table 2 for a list of termination cables used with the TAs forthe FBM214.FUNCTIONAL SPECIFICATIONS – TERMINATION ASSEMBLIESFBM Type Input SignalTA Part NumberTermination TA Cable TACertification PVC (a)(a)PVC is polyvinyl chloride rated from -20 to +50°C (-4 to +122°F).PA is Polyamide rated from -20 to +70°C (-4 to +158°F).PA (a)Type (b)(b) C = TA with compression terminals; RL = TA with ring lug terminals.Type (c)(c)See Table 2 for cable part numbers and specifications.Type (d)(d)See Table 1 for Termination Assembly certification definitions.FBM2148 input channels, 4 to 20mA analog signal, alone or with HART signal superimposedP0916BX P0926EA P0926TD CRL11, 2PSS 21H-2Z14 B4Page 9Table 1. Certification for Termination AssembliesType Certification (a)(a)All TAs are UL/UL-C listed to comply with applicable ordinary location safety standards for fire and shock hazards. Hazardous locationtypes comply with ATEX directive for II 3 G use. They also comply with the requirements of the European Low Voltage Directive. All listings/certifications require installation and use within the constraints specified in DIN Rail Mounted Subsystem User’s Guide (B0400FA) and the conditions stated in UL and DEMKO reports.Type 1TAs are UL/UL-C listed as suitable for use in Class I; Groups A-D; Division 2 temperature code T4 hazardous locations. They are CENELEC (DEMKO) certified EEx nA IIC T4 for use in Zone 2 potentially explosive atmospheres.Type 2TAs are UL/UL-C listed as associated apparatus for supplying non-incendive field circuits Class I; Groups A-D; Division 2 hazardous locations when connected to specified DIN rail mounted FBMs and field circuits meeting entity parameter constraints specified in DIN Rail Mounted Subsystem User’s Guide (B0400FA). They are also CENELEC (DEMKO) certified as associated apparatus for supplying field circuits for Group IIC, Zone 2 potentially explosive atmospheres. Field circuits are also Class 2 limited energy (60 V dc, 30 V ac, 100 VA or less) if customer-supplied equipment meets Class 2 limits.Table 2. Cables Types and Part NumbersCable Lengthm (ft) Type 1P/PVC (a)Type 1H/XLPE (b)Cable Lengthm (ft) Type 1P/PVC (a)Type 1H/XLPE (b)0.5 (1.6)P0916DA P0916VA 10.0 (32.8) P0916DE P0916VE 1.0 (3.2) P0916DB P0916VB 15.0 (49.2) P0916DF P0916VF 2.0 (6.6)P0931RM P0931RR 20.0 (65.6) P0916DG P0916VG 3.0 (9.8) P0916DC P0916VC 25.0 (82.0) P0916DH P0916VH 5.0 (16.4)P0916DDP0916VD30.0 (98.4)P0916DJP0916VJ(a)P/PVC is polyurethane outer jacket and semi-rigid PVC primary conductor insulation.(b)H/XLPE is Hypalon outer jacket and XLPE (cross-linked polyethylene) primary conductor insulation.PSS 21H-2Z14 B4Page 10DIMENSIONS – NOMINALRELATED PRODUCT SPECIFICATION SHEETSCompression Termination AssemblyRing Lug Termination Assembly(a) Overall width – for determining DIN rail loading.(b) Height above DIN rail (add to DIN rail height for total).PSS NumberDescriptionPSS 21H-2W1 B3DIN Rail Mounted FBM Subsystem OverviewPSS 21H-2W2 B3DIN Rail Mounted FBM Equipment, Agency CertificationsPSS 21H-2Z14 B4Page 11PSS 21H-2Z14 B4 Page 12IPS Corporate Headquarters 5601 Granite Parkway Suite 1000 Plano, TX 75024United States of AmericaFoxboro Global Client Support Inside U.S.: 1-866-746-6477 Outside U.S.: 1-508-549-2424 or contact your local Foxboro representative.Facsimile: 1-508-549-4999Invensys, Foxboro, I/A Series and the IPS Logo are trademarks of Invensys plc, its subsidiaries, and affiliates. All other brand names may be trademarks of their respective owners.Copyright 2002-2010 Invensys Systems, Inc.All rights reservedMB 21A Printed in U.S.A. 0210。

•ISO 7816 compliant contact locations•Single supply with operation down to 2.5V -Maximum write current 3 mA at 6.0V -Maximum read current 150 µ A at 6.0V -Standby current 1 µ A max at 2.5V•T wo wire serial interface bus, I 2 C ™ compatible •100 kHz (2.5V) and 400 kHz (5V) compatibility •Self-timed ERASE and WRITE cycles •Power on/off data protection circuitry•1,000,000 ERASE/WRITE cycles guaranteed •32 byte page or byte write modes available •Schmitt trigger inputs for noise suppression•Output slope control to eliminate ground bounce • 2 ms typical write cycle time, byte or page •Electrostatic discharge protection > 4000V •Data retention > 200 years•8-pin PDIP and SOIC packages •T emperature ranges:DESCRIPTIONThe Microchip T echnology Inc. 24LC32A is a 4K x 8(32K bit) Serial Electrically Erasable PROM in an ISO micromodule for use in smart card applications. The device has a page-write capability of up to 32 bytes.-Commercial: 0˚C to +70˚C2元器件交易网24LC32A MODULE1.0ELECTRICAL CHARACTERISTICS1.1Maximum Ratings*V CC ........................................................................7.0V All inputs and outputs w.r.t. V SS ......-0.6V to VCC +1.0V Storage temperature ..........................-65˚C to +150˚C Ambient temp. with power applied......-65˚C to +125˚C Soldering temperature of leads (10 seconds)..+300˚C ESD protection on all pins .....................................≥ 4 kV*Notice: Stresses above those listed under “Maximum Ratings”may cause permanent damage to the device. This is a stress rat-ing only and functional operation of the device at those or anyother conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.TABLE 1-1:PIN FUNCTIONSName Function V SS Ground SDA Serial Data SCL Serial ClockV CC+2.5V to 6.0V Power SupplyTABLE 1-2:DC CHARACTERISTICSVcc = +2.5V to 6.0VCommercial (C):T amb = 0˚C to +70 ° CParameterSymbolMinTypMaxUnitsConditionsSCL and SDA pins:High level input voltage V IH .7 V CC —V Low level input voltage V IL —.3 Vcc V Hysteresis of Schmitt T rigger inputsV HYS .05 V CC—V Note 1Low level output voltage V OL —.40V I OL = 3.0 mA @ V CC = 4.5V I OL = 2.1 mA @ V CC = 2.5V Input leakage current I LI -1010 µ A V IN = .1V to V CC Output leakage current I LO -1010 µ A V OUT = .1V to V CC Pin capacitance (all inputs/outputs)C IN ,C OUT —10pF V CC = 5.0V (Note 1)T amb = 25˚C, f c = 1 MHz Operating current I CC Write —3mA V CC = 6.0VI CC Read —400 µ A V CC = 6.0V , SCL = 400Khz Standby currentI CCS —1 µ A5 µ A SCL = SDA = V CC = 5.0VI CCS1µ AVCC = 2.5V (Note 1)Note 1:This parameter is periodically sampled and not 100% tested.元器件交易网24LC32A MODULETABLE 1-3:AC CHARACTERISTICSParameterSymbolVcc = 2.5 - 6.0V STD. MODE Vcc = 4.5 - 6.0V FAST MODE UnitsRemarksMinMaxMinMaxClock frequency F CLK —100—400kHz Clock high time T HIGH 4000—600—ns Clock low timeT LOW 4700—1300—ns SDA and SCL rise time T R —1000—300ns Note 1SDA and SCL fall time T F —300—300ns Note 1START condition hold timeT HD : STA 4000—600—ns After this period the first clock pulse is generatedST ART condition setup timeT SU : STA 4700—600—ns Only relevant for repeated ST ART conditionData input hold time T HD : DAT 0—0—ns Data input setup time T SU : DAT 250—100—ns STOP condition setup timeT SU : STO 4000—600—ns Output valid from clock T AA —3500—900ns Note 2Bus free timeT BUF 4700—1300—ns Time the bus must be free before a new transmission can start Output fall time from V IH min to V IL maxT OF —25020 +0.1C B 250ns Note 1, CB ≤ 100 pF Input filter spike sup-pression (SDA and SCL pins)T SP—50—50nsNote 3Write cycle timeTWR —5—5ms Byte or Page modeNote 1: Not 100% tested. CB = total capacitance of one bus line in pF .2: As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region (minimum 300 ns) of the falling edge of SCL to avoid unintended generation of ST ART or STOP conditions. 3: The combined T SP and VHYSspecifications are due to Schmitt trigger inputs which provide improved noise and spike suppression. This eliminates the need for a Ti specification for standard operation.元器件交易网24LC32A MODULE2.0PIN DESCRIPTIONS2.1SDA (Serial Data)This is a bidirectional pin used to transfer addresses and data into and data out of the device. It is an open drain terminal, therefore the SDA bus requires a pullup resistor to V CC (typical 10K Ω for 100 kHz, 1K Ω for 400kHz)For normal data transfer SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the ST ART and STOP condi-tions.2.2SCL (Serial Clock)This input is used to synchronize the data transfer from and to the device.3.0FUNCTIONAL DESCRIPTIONThe 24LC32A supports a bidirectional two-wire bus and data transmission protocol. A device that sends data onto the bus is defined as transmitter, and a device receiving data as receiver. The bus must be con-trolled by a master device which generates the serial clock (SCL), controls the bus access, and generates the ST ART and STOP conditions, while the 24LC32A works as slave. Both master and slave can operate as transmitter or receiver but the master device deter-mines which mode is activated.元器件交易网24LC32A MODULE4.0BUS CHARACTERISTICSThe following bus protocol has been defined:•Data transfer may be initiated only when the bus is not busy.•During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a ST ART or STOP condition.Accordingly, the following bus conditions have been defined (See Figure 4-1).4.1Bus not Busy (A)Both data and clock lines remain HIGH.4.2Start Data Transfer (B)A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a ST ART condition.All commands must be preceded by a START condi-tion.4.3Stop Data Transfer (C)A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.4.4Data Valid (D)The state of the data line represents valid data when,after a ST ART condition, the data line is stable for the duration of the HIGH period of the clock signal.The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.Each data transfer is initiated with a ST ART condition and terminated with a STOP condition. The number of the data bytes transferred between the ST ART and STOP conditions is determined by the master device.4.5AcknowledgeEach receiving device, when addressed, is obliged to generate an acknowledge signal after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit.A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course,setup and hold times must be taken into account. Dur-ing reads, a master must signal an end of data to the slave by NOT generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave (24LC32A) will leave the data line HIGH to enable the master to generate the STOP condition.(See Figure 4-2)元器件交易网24LC32A MODULE5.0DEVICE ADDRESSINGA control byte is the first byte received following the start condition from the master device. (See Figure 5-1) The control byte consists of a four bit control code;for the 24LC32A this is set as 1010 binary for read and write operations. The next three bits are device select bits on standard devices, however, for micromodules,these must be zeros. The last bit of the control byte defines the operation to be performed. When set to a one a read operation is selected, and when set to a zero a write operation is selected. The next two bytesreceived define the address of the first data byte (see Figure 5-2). Because only A11...A0 are used, the upper four address bits must be zeros. The most signif-icant bit of the most significant byte of the address is transferred first.Following the start condition, the 24LC32A monitors the SDA bus checking the device type identifier being transmitted. Upon receiving a valid control byte, the slave device outputs an acknowledge signal on the SDA line. Depending on the state of the R/W bit, the 24LC32A will select a read or write operation元器件交易网24LC32A MODULE6.0WRITE OPERATIONS6.1Byte WriteFollowing the start condition from the master, the con-trol code (four bits), the device select (three bits), and the R/W bit which is a logic low are clocked onto the bus by the master transmitter. This indicates to the addressed slave receiver that a byte with a word address will follow after it has generated an acknowl-edge bit during the ninth clock cycle. Therefore the next byte transmitted by the master is the high-order byte of the word address and will be written into the address pointer of the 24LC32A MODULE. The next byte is the least significant address byte. After receiving another acknowledge signal from the 24LC32A the master device will transmit the data word to be written into the addressed memory location.The 24LC32A acknowledges again and the master generates a stop condition. This initiates the internal write cycle, and during this time the 24LC32A will not generate acknowledge signals (see Figure 6-1).6.2Page WriteThe write control byte, word address and the first data byte are transmitted to the 24LC32A in the same way as in a byte write. But instead of generating a stop con-dition, the master transmits up to 32 bytes which are temporarily stored in the on-chip page buffer and will be written into memory after the master has transmitted a stop condition. After receipt of each word, the five lower address pointer bits are internally incremented by one.If the master should transmit more than 32 bytes prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received, an internal write cycle will begin. (see Figure 6-2).元器件交易网24LC32A MODULE7.0ACKNOWLEDGE POLLINGSince the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write com-mand has been issued from the master, the device ini-tiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master send-ing a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If the cycle is complete, then the device will return the ACK and the master can then proceed with the next read or write command. See Figure 7-1 for flow diagram.FIGURE 7-1:ACKNOWLEDGE POLLING8.0READ OPERATIONRead operations are initiated in the same way as write operations with the exception that the R/W bit of the slave address is set to one. There are three basic types of read operations: current address read, random read,and sequential read.8.1Current Address ReadThe 24LC32A contains an address counter that main-tains the address of the last word accessed, internally incremented by one. Therefore, if the previous access (either a read or write operation) was to address n (n is any legal address), the next current address read oper-ation would access data from address n + 1. Upon receipt of the slave address with R/W bit set to one, the 24LC32A issues an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the 24LC32A discontinues transmission (see Figure 8-1).8.2Random ReadRandom read operations allow the master to access any memory location in a random manner. T o perform this type of read operation, first the word address must be set. This is done by sending the word address to the 24LC32A as part of a write operation (R/W bit set to 0).After the word address is sent, the master generates a start condition following the acknowledge. This termi-nates the write operation, but not before the internal address pointer is set. Then the master issues the con-trol byte again but with the R/W bit set to a one. The 24LC32A will then issue an acknowledge and transmit the eight bit data word. The master will not acknowl-edge the transfer but does generate a stop condition which causes the 24LC32A to discontinue transmis-sion (see Figure 8-2).元器件交易网24LC32A MODULE8.3Sequential ReadSequential reads are initiated in the same way as a ran-dom read except that after the 24LC32A transmits the first data byte, the master issues an acknowledge as opposed to the stop condition used in a random read.This acknowledge directs the 24LC32A to transmit the next sequentially addressed 8 bit word (see Figure 8-3). Following the final byte transmitted to the master,the master will NOT generate an acknowledge but will generate a stop condition.To provide sequential reads the 24LC32A contains an internal address pointer which is incremented by one at the completion of each operation. This address pointer allows the entire memory contents to be serially read during one operation. The internal address pointer will automatically roll over from address 0FFF to address 000 if the master acknowledges the byte received from the array address 0FFF .元器件交易网24LC32A MODULE9.0SHIPPING METHODThe micromodules will be shipped to customers in clear plastic trays. Each tray holds 150 modules, and the trays can be stacked in a manner similar to shipping die in waffle packs. A tray drawing with dimensions is shown in Figure 9-1.元器件交易网24LC32A MODULE元器件交易网24LC32A MODULENOTES:元器件交易网24LC32A MODULENOTES:元器件交易网24LC32A MODULENOTES:元器件交易网24LC32A MODULE24LC32A MODULE PRODUCT IDENTIFICATION SYSTEMT o order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.Sales and SupportData SheetsProducts supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recom-mended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:1.Y our local Microchip sales office.2.The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277.3.The Microchip’s Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.元器件交易网MAll rights reserved. © 1997, Microchip T echnology Incorporated, USA. 9/97 Printed on recycled paper.元器件交易网。

®724qÉãéÉê~íìêÉ=`~äáÄê~íçê用户手册cÉÄêì~êó=OMMM=oÉîK=NI=ULMP=EpáãéäáÑáÉÇ=`ÜáåÉëÉF«=OMMMJOMMP=cäìâÉ=`çêéçê~íáçåI=^ää=êáÖÜíë=êÉëÉêîÉÇK^ää=éêçÇìÅí=å~ãÉë=~êÉ=íê~ÇÉã~êâë=çÑ=íÜÉáê=êÉëéÉÅíáîÉ=Åçãé~åáÉëK公司简介福州福光电子有限公司是一家集研发、生产和销售的高新科技企业,专业为通信运营商、电力和专网提供电源、传输、数据、无线等测试领域的系统集成服务。

V 12-2Detecting objectson conveyor belts using VS/VE 12-2through-beam photo-electric switches.▼VL 12-2 photoelectric reflex switches canalso be used for the reliable detection of reflective surfaces, for example film-wrapped cardboard boxes.VT 12-2 photo-electric proximity switches used to ensure that waste is rolled up correctly when paper and film strips are cut.Is an objectpresent or not? The VT 12-2 photo-electric proximity switch provides the answer.▼▲▲VT 12T-2, Scanning distance 115 mm/340 mm115 mm Scanning distance340 mm Scanning distance 0 (mm)204060801001207025501152100210 (mm)501001502002503003502180200034023002112Scanning distance on white, 90 % remission Scanning distance on grey, 18 % remissionOperating distance Scanning distance, max. typical(mm)50100150200250300100101O p e r a t i n g r e s e r v eScanning distance max. typical Operating distanceVT 12(T)-2300 mm12(mm)10060802040100110O p e r a t i n g r e s e r v eOperating distance 21Scanning distance max. typical VT 12(T)-2100 mmScanning distance, max. typical 1)0... 115 mm 0 ... 340 mm Operating distance 1)2... 100 mm 2 ... 300 mmSensitivity setting Manual, per Teach-in buttonElectronic, per control input C (0 V)2)Light source 3), light type LED, infrared lightLight spot diameterApprox. 20 mm at 100 mm Approx. 28 mm at 300 mm Angle of dispersion of senderApprox. 11.4°(SD = max.), Approx. 22.6°(SD = 1/2 max.)Approx. 5.3°(SD = max.),Approx. 11.2°(SD = 1/2 max.)Supply voltage V S 10 ... 30 V DC 4)Ripple 5)≤10%Current consumption 6)≤20 mA Switching outputs Q: PNP Q: NPN Output current l A max.≤100 mASwitching mode Light-/Dark-switching selectable 2)Response time 7)≤1.25 ms Switching frequency max.8)400/sConnection typesCable 9)PVC, 2 m, 4 x 0.14 mm 2, Ø 3.75 mm PlugM12, 4-pinVDE protection class 10)VCircuit protection 11)A, B, C, D Enclosure ratingIP 67Ambient temperature T A Operation –25 °C ... +70 °C Storage –25 °C ... +70 °C WeightWith cable Approx. 54 g With plug Approx. 18 gHousing materialHousing:Nickel-coated brass/PA Optics:PC1)Object to be detected with 90%remission (relating to standard white in acc. with DIN 5033); 100 x 100 mm2)Controll input C – L.ON/D.ON and – external Teach-inC = open: light-switching L.ON C = + V S : dark-switching D.ONC = 0 V: Sensitivity setting per “externalTeach-in” active3)Average service life 100,000 h at T A = +25°C 4)Limit values5)May not exceed or fall short of V S tolerances 6)Without load7)Signal transit time with resistive load8)With light/dark ratio 1:19)Do not bend below 0°C 10)Reference voltage 50 V DC11)A =V Sconnections reverse-polarityprotectedB =Inputs and output reverse-polarityprotectedC =Interference pulse suppressionD =Outputs overload and short-circuitprotectedTechnical dataVT 12T-2P 112P 410N 112N 410P 132P 430N 132N 430TypeOrder no.VT 12T -2P 112 6 026 211VT 12T -2P 410 6 026 212VT 12T -2N 112 6 026 209VT 12T -2N 410 6 026 210VT 12T -2P 132 6 026 215VT 12T -2P 430 6 026 216VT 12T -2N 132 6 026 213VT 12T -2N 4306 026 214Order information0 (m)0.5 1.0 1.5 2.0 2.5 3.0Operating range Scanning range, max. typical0 2.50.03 2.00 2.30.03 1.80.90.10.7 2.80.03 2.323410.1 ... 0.7 mReflective tape Diamond GradePL 50 A/PL 40 A/P 25040.03 ... 1.8 m 3 C 1100.03 ... 2.0 m 2PL 80 A 0.03 ... 2.3 m1Reflector type Operating range VL 12-210001001011.01.52.02.50.5(m)O p e r a t i n g r a n g eOperating rangeReflectorC 110Scanning range, max. typical V L 12-22Scanning range, max.typ./reflector 0.03... 2.8 m/PL 80 A Operating range 0.03... 2.3 m/PL 80 A Sensitivity settingNot availableLight source 1), light type LED, red light, with polarization filter Light spot diameterApprox. 80 mm at 2 m Angle of dispersion of sender Approx. 2.3°(SR = max.), Approx. 6.3°(SR = 1/2 max.)Supply voltage V S 10 … 30 V DC 2)Ripple 3)≤10%Current consumption 4)≤20 mASwitching outputsQ: PNP Q: NPN Output current l A max.≤100 mASwitching mode Light-/Dark-switching selectable 5)Response time 6)≤1.25 ms Switching frequency max.7)400/sConnection types Cable 8)PVC, 2 m, 4 x 0.14 mm 2, Ø 3.75 mm PlugM12, 4-pinVDE protection class 9)VCircuit protection 10)A, B, C, D Enclosure ratingIP 67Ambient temperature T A Operation –25 °C ... +70 °C Storage –25 °C ... +70 °CWeightWith cable Approx. 54 g With plug Approx. 18 gHousing materialHousing: Nickel-coated brass/PA Optics: PC1)Average service life 100,000 h at T A = +25°C 2)Limit values3)May not exceed or fall short of V S tolerances 4)Without load5)L/D switching type control line L/D =open (not assigned)dark-switching D.ONL/D =+ V S : light-switching L.ON L/D =0 V: dark-switching D.ON6)Signal transit time with resistive load 7)With light/dark ratio 1:18)Do not bend below 0°C 9)Reference voltage 50 V DC10)A =V S connections reverse-polarityprotectedB =Inputs and output reverse-polarityprotectedC =Interference pulse suppressionD =Outputs overload and short-circuitprotectedTechnical dataVL 12-2P 132P 430N 132N 430Scanning range and operating reserveType Order no.VL 12-2P 132 6 026 219VL 12-2P 430 6 026 220VL 12-2N 132 6 026 217VL 12-2N 4306 026 218Order informationVS/VE 12-2100010010123451(m)O p e r a t i n g r e s e r v eOperating rangeScanning range, max. typical V S/V E 12-20 (m) 1.0 2.0 3.0 4.0 5.0 6.0Operating range Scanning range, max. typical5.04.0Scanning range, m a x .t yp .0... 5.0 m O p e r at in g r a n ge 0... 4.0 m Se n s i t ivi t y sett in gN ot a v a il a bl e Light source 1), light type L ED, infr a r e d li g h tLi g h t s p ot di a m ete rAppr o x . 100 mm at 4 m An g l e o f di s p e r s i o n o f se nd e r Appr o x . 1.4°(S R = m a x .), An g l e o f di s p e r s i o n o f r ece iv e r Appr o x . 4.5°(S R = 1/2 m a x .)Supply voltage V S 10 … 30 V DC 2)Rippl e 3)≤10%C urr e n t co n s ump t i o n 4)≤20 mASwitching outputs Q : PNP Q : NPN O u t pu t c urr e n t l A m a x .≤100 mAS wi tc hin g m o d e Li g h t-/Da rk -s wi tc hin g se l ecta bl e 5)R es p o n se t im e 6)≤2.0 m s S wi tc hin g fr e qu e n c y m a x .7)250/sConnection typesCa bl e 8) se nd e r V S 12-2 PV C, 2 m , 2 x 0.14 mm 2, Ø 3.75 mm Ca bl e 8) r ece iv e r V E 12-2 PV C, 2 m , 4 x 0.14 mm 2, Ø 3.75 mm Plu gM12, 4-pinVDE protection class 9)VCircuit protection 10)A , B, C, D Enclosure ratingIP 67Ambient temperature T A O p e r at i o n –25 °C ... +70 °C Sto r age –25 °C ... +70 °C WeightWi t h ca bl e V S a nd V E eac h a ppr o x . 54 g Wi t h plu g V S a nd V E eac h a ppr o x . 18 g Housing materialH o u s in g : Ni c k e l -coate d br ass /PA O p t i cs :P C1)Av e r age se rvi ce lif e 100,000 h at T A = +25°C 2)Limi t v a lu es3)M a y n ot e x cee d o r f a ll s h o r t o f V S to l e r a n ces 4)Wi t h o u t l oa d5)L/D s wi tc hin g t yp e co n t r o l lin e L/D =o p e n (n ot ass i g n e d)d a rk -s wi tc hin g D.O NL/D =+ V S : li g h t-s wi tc hin g L .O N L/D =0 V: d a rk -s wi tc hin g D.O N6)S i g n a l t r a n s i t t im e wi t h r es i st iv e l oa d 7)Wi t h li g h t /d a rk r at i o 1:18)Do n ot b e nd b e l o w 0°C 9)R e f e r e n ce v o l tage 50 V DC10)A =V S co nn ect i o n s r e v e r se-p o l a ri t ypr otecte dB =Inpu ts a nd o u t pu t r e v e r se-p o l a ri t ypr otecte dC =In te rf e r e n ce pul se s uppr ess i o nD =O u t pu ts o v e rl oa d a nd s h o r t-c ir c ui tpr otecte d11)Th e o rd e r n o. co n ta in s t r a n s mi tte r a nd r ece iv e r (= p a ir).Technical dataV S /V E 12-2P 132P 430N 132N 430Scanning range and operating reserveType 11)Order no.11)V S /V E 12-2P 132 6 026 223V S /V E 12-2P 430 6 026 224V S /V E 12-2N 132 6 026 221V S /V E 12-2N 4306 026 222Order information。

June 2013 (Simplified Chinese) Rev. 1, 5/16© 2013 -2016 Fluke Corporation. All rights reserved. Specifications are subject to change without notice. All product names are trademarks of their respective companies. 2638AHYDRA Series III Data Acquisition Unit用户手册有限担保及责任范围Fluke 公司保证其每一个Fluke的产品在正常使用及维护情形下,其用料和做工都是毫无瑕疵的。

保证期限是一年并从产品寄运日起开始计算。

零件、产品修理及服务的保证期是 90 天。

本保证只提供给从Fluke 授权经销商处购买的原购买者或最终用户, 且不包括保险丝、电池以及因误用、改变、疏忽、或非正常情况下的使用或搬运而损坏(根据 Fluke 的意见而定)的产品。

Fluke 保证在 90 天之内,软件会根据其功能指标运行,同时软件已经正确地被记录在没有损坏的媒介上。

Fluke 不能保证其软件没有错误或者在运行时不会中断。

Fluke 仅授权经销商将本保证提供给购买新的、未曾使用过的产品的最终用户。

经销商无权以 Fluke 的名义来给予其它任何担保。

保修服务仅限于从 Fluke 授权销售处所购买的产品,或购买者已付出适当的Fluke国际价格。

在某一国家购买而需要在另一国家维修的产品,Fluke 保留向购买者征收维修/更换零件进口费用的权利。

Fluke 的保证是有限的,在保用期间退回 Fluke 授权服务中心的损坏产品,Fluke有权决定采用退款、免费维修或把产品更换的方式处理。

欲取得保证服务,请和您附近的Fluke服务中心联系,或把产品寄到最靠近您的Fluke服务中心(请说明故障所在,预付邮资和保险费用,并以 FOB 目的地方式寄送)。

81系列电源V1.4用户手册青岛仪迪电子有限公司QINGDAO IDI ELECTRONICS CO.,LTD.目录第一章简介1.1 安全须知 (1)1.2 安装准备 (1)1.3 储存和运输 (1)1.4 电源接线 (2)第二章如何选择变频电源2.1 输出电压和电流的对应关系 (11)2.2 负载的功率因数对输出功率的影响 (11)2.3 电机、压缩机负载对输出功率的影响 (11)第三章面板说明3.1 前面板操作说明 (12)3.2 面板说明 (12)第四章操作说明4.1 操作说明 (18)4.2 参数设定 (18)4.3 显示器讯息 (18)第五章应用说明5.1 遥控接口 (23)第六章仪表校正6.1 校正步骤 (25)第七章维护和保养7.1 维护和保养 (26)第八章附录8.1 工作原理及方块图 (27)请在使用本仪器前仔细阅读用户手册符合标准符合GB/T 15290-1994、 GB/T 8554-1998和IEC 61007-1994 测试标准;校验及校正声明青岛仪迪电子有限公司特别声明,本手册所列的仪器设备完全符合本公司一般型号上所标称的规范和特征。

本仪器在出厂前已经通过本公司厂内校验。

校验程序和步骤是符合电子校验中心的规范和标准。

产品品质保证青岛仪迪电子有限公司保证所生产制造的新品仪器均经过严格的品质确认,同时保证在出厂一年内,如果发现产品的施工瑕疵或零件故障,本公司负责免费给予修复。

但如果使用者有自行更改电路、功能、或进行修理仪器及零件或外箱损坏等情况,本公司恕不提供免费保修服务。

如果本仪器在非正常的使用、或人为疏忽、或不可抗力下发生故障,例如地震、水灾、火灾或暴动等非人力可控制的因素,本公司不予免费保修服务。

·本保证不包含仪器的附件。

·手册内容若有改变,恕不另行通知。

·本手册若有不详尽之处,请直接与本公司总部联系。

版本号:V1.40。

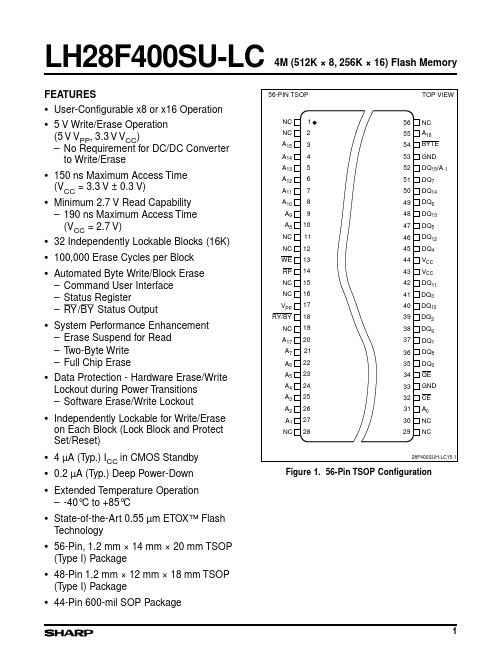

LH28F400SU-LC4M (512K × 8, 256K × 16) Flash MemoryFigure 1. 56-Pin TSOP ConfigurationFEATURES•User-Configurable x8 or x16 Operation• 5 V Write/Erase Operation(5 V V PP , 3.3 V V CC )–No Requirement for DC/DC Converter to Write/Erase•150 ns Maximum Access Time(V CC = 3.3 V ± 0.3 V)•Minimum 2.7 V Read Capability–190 ns Maximum Access Time(V CC = 2.7 V)•32 Independently Lockable Blocks (16K)•100,000 Erase Cycles per Block •Automated Byte Write/Block Erase–Command User Interface –Status Register –RY /BY Status Output•System Performance Enhancement–Erase Suspend for Read –T wo-Byte Write –Full Chip Erase•Data Protection - Hardware Erase/WriteLockout during Power T ransitions –Software Erase/Write Lockout•Independently Lockable for Write/Eraseon Each Block (Lock Block and Protect Set/Reset)• 4 µA (T yp.) I CC in CMOS Standby •0.2 µA (T yp.) Deep Power-Down •Extended T emperature Operation–-40°C to +85°C•State-of-the-Art 0.55 µm ETOX™ FlashT echnology•56-Pin, 1.2 mm × 14 mm × 20 mm TSOP(T ype I) Package•48-Pin 1.2 mm × 12 mm × 18 mm TSOP(T ype I) Package•44-Pin 600-mil SOP Package元器件交易网Figure 3. 44-Pin SOP ConfigurationFigure 2. 48-PIn TSOP ConfigurationFigure 4. LH28F004SU-LC Block DiagramPIN DESCRIPTIONSYMBOL TYPE NAME AND FUNCTIONDQ15 - A1INPUT BYTE-SELECT ADDRESSES: Selects between high and low byte when device is in x8 mode. This address is latched in x8 Data Writes. Not used in x16 mode (i.e., the DQ15/A1 input buffer is turned off when BYTE is high).A0 - A12INPUT WORD-SELECT ADDRESSES: Select a word within one 16K block. These addresses are latched during Data Writes.A13 - A17INPUT BLOCK-SELECT ADDRESSES: Select 1 of 32 Erase blocks. These addresses are latched during Data Writes, Erase and Lock-Block operations.DQ0 - DQ7INPUT/OUTPUT LOW-BYTE DATA BUS: Inputs data and commands during CUI write cycles. Outputs array, buffer, identifier or status data in the appropriate Read mode. Floated when the chip is de-selected or the outputs are disabled.DQ8- DQ15INPUT/OUTPUTHIGH-BYTE DATA BUS: Inputs data during x16 Data Write operations. Outputsarray, buffer or identifier data in the appropriate Read mode; not used for Statusregister reads. Floated when the chip is de-selected or the outputs are disabled.DQ15/A1 is address.CE INPUT CHIP ENABLE INPUT: Activate the device’s control logic, input buffers, decoders and sense amplifiers. CE must be low to select the device.RP INPUT RESET/POWER-DOWN: RP low places the device in a Deep Power-Down state. All circuits that burn static power, even those circuits enabled in standby mode, are turned off. When returning from Deep Power-Down, a recovery time of 750 ns is required to allow these circuits to power-up. When RP goes low, any current or pending WSM operation(s) are terminated, and the device is reset. All Status registers return to ready (with all status flags cleared).OE INPUT OUTPUT ENABLE: Gates device data through the output buffers when low. The outputs float to tri-state off when OE is high.WE INPUT WRITE ENABLE: Controls access to the CUI, Data Queue Registers and Address Queue Latches. WE is active low, and latches both address and data (command or array) on its rising edge.RY/BY OPEN DRAINOUTPUTREADY/BUSY: Indicates status of the internal WSM. When low, it indicates that theWSM is busy performing an operation. When the WSM is ready for new operation orErase is Suspended, or the device is in deep power-down mode RY/BY pin is floated.BYTE INPUT BYTE ENABLE: BYTE low places device in x8 mode. All data is then input or output on DQ0 - DQ7, and DQ8 - DQ15 float. Address A1 selects between the high and low byte. BYTE high places the device in x16 mode, and turns off the A1 input buffer. Address A0, then becomes the lowest order address.V PP SUPPLY ERASE/WRITE POWER SUPPLY (5.0 V ±0.5 V): For erasing memory array blocks or writing words/bytes into the flash array.V CC SUPPLY DEVICE POWER SUPPLY (3.0 V ±0.3 V): Do not leave any power pins floating. GND SUPPLY GROUND FOR ALL INTERNAL CIRCUITRY: Do not leave any ground pins floating. NC NO CONNECT: No internal connection to die, lead may be driven or left floating.INTRODUCTIONSharp’s LH28F400SU-LC 4M Flash Memory is a revolutionary architecture which enables the design of truly mobile, high performance, personal computing and communication products. With innovative capabilities, 3.3 V low power operation and very high read/write per-formance, the LH28F400SU-LC is also the ideal choice for designing embedded mass storage flash memory systems.The LH28F400SU-LC’s independently lockable 32 symmetrical blocked architecture (16K each) extended cycling, low power operation, very fast write and read performance and selective block locking provide a highly flexible memory component suitable for cellular phone, facsimile, game, PC, printer and handy terminal. The LH28F400SU-LC’s 5.0 V/3.3 V power supply operation enables the design of memory cards which can be read in 3.3 V system and written in 5.0 V/3.3 V systems. Its x8/x16 architecture allows the optimization of memory to processor interface. The flexible block locking option enables bundling of executable application software in a Resident Flash Array or memory card. Manufactured on Sharp’s 0.55 µm ETOX™ process technology, the LH28F400SU-LC is the most cost-effective, high-density 3.3 V flash memory.DESCRIPTIONThe LH28F400SU-LC is a high performance 4M (4,194,304 bit) block erasable non-volatile random access memory organized as either 256K × 16 or 512K × 8. The LH28F400SU-LC includes thirty-two 16K (16,384) blocks. A chip memory map is shown in Figure 5.The implementation of a new architecture, with many enhanced features, will improve the device operating characteristics and results in greater product reliability and ease of use.Among the significant enhancements of the LH28F400SU-LC:• 3 V Read, 5 V Write/Erase Operation(5 V V PP, 3 V V CC)•Low Power Capability (2.7 V V CC Read)•Improved Write Performance•Dedicated Block Write/Erase Protection •Command-Controlled Memory Protection Set/Reset CapabilityA Command User Interface (CUI) serves as the sys-tem interface between the microprocessor or microcontroller and the internal memory operation.Internal Algorithm Automation allows Byte W rites and Block Erase operations to be executed using a T wo-Write command sequence to the CUI in the same way as the LH28F008SA 8M Flash memory.A Superset of commands have been added to the basic LH28F008SA command-set to achieve higher write performance and provide additional capabilities. These new commands and features include:•Software Locking of Memory Blocks•Memory Protection Set/Reset Capability•T wo-Byte Serial Writes in 8-bit Systems•Erase All Unlocked BlocksWriting of memory data is performed typically within 20 µs per byte. Writing of memory data is performed typically within 30 µs per word. A Block Erase operation erases one of the 32 blocks in typically 0.8 seconds, independent of the other blocks.LH28F400SU-LC allows to erase all unlocked blocks. It is desirable in case of which you have to implement Erase operation maximum 32 times.LH28F400SU-LC enable T wo-Byte serial W rite which is operated by three times command imput. Writing of memory data is performed typically within 30 µs per two-byte. This feature can improve 8-bit system write performance by up to typically 15 µs per byte.All operations are started by a sequence of Write commands to the device. Status Register (described in detail later) and a RY/BY output pin provide informa-tion on the progress of the requested operation.Same as the LH28F008SA, LH28F400SU-LC requires an operation to complete before the next operation can be requested, also it allows to suspend block erase to read data from any other block, and allow to resume erase operation.The LH28F400SU-LC provides user-selectable block locking to protect code or data such as Device Drivers, PCMCIA card information, ROM-Executable OS or Application Code. Each block has an associated non-volatile lock-bit which determines the lock status of the block. In addition, the LH28F400SU-LC has a software controlled master Write Protect circuit which prevents any modifications to memory blocks whose lock-bits are set.MEMORY MAP When the device power-up or RP turns High, WriteProtect Set/Confirm command must be written. Other-wise, all lock bits in the device remain being locked,can’t perform the Write to each block and single BlockErase. Write Protect Set/Confirm command must bewritten to reflect the actual lock status. However, whenthe device power-on or RP turns High, Erase AllUnlocked Blocks can be used. If used, Erase is per-formed with reflecting actual lock status, and after thatWrite and Block Erase can be used.The LH28F400SU-LC contains a Compatible StatusRegister (CSR) which is 100% compatible with theLH28F008SA Flash memory’s Status Register. This reg-ister, when used alone, provides a straightforwardupgrade capability to the LH28F400SU-LC from aLH28F008SA-based design.The LH28F400SU-LC incorporates an open drainRY/BY output pin. This feature allows the user to OR-tie many RY/BY pins together in a multiple memory con-figuration such as a Resident Flash Array.The LH28F400SU-LC is specified for a maximumaccess time of 150 ns (t ACC) at 3.3 V operation (3.0 to3.6 V) over the commercial temperature range. A corre-sponding maximum access time of 190 ns (t ACC) at 2.7 V (0 to +70°C) is achieved for reduced power con-sumption applications.The LH28F400SU-LC incorporates an Automatic Power Saving (APS) feature which substantially reduces the active current when the device is in static mode of operation (addresses not switching).In APS mode, the typical I CC current is 1 mA at 3.3 V.A Deep Power-Down mode of operation is invoked when the RP(called PWD on the LH28F008SA) pin transitions low. This mode brings the device power con-sumption to less than 8 µA, and provides additional write protection by acting as a device reset pin during power transitions. A reset time of 750 ns is required from RP switching high until outputs are again valid. In the Deep Power-Down state, the WSM is reset (any current operation will abort) and the CSR register is cleared.A CMOS Standby mode of operation is enabled when CE transitions high and RP stays high with all input control pins as CMOS levels. In this mode, the device draws an I CC standby current of 15 µA.157C000H7FFFFH7BFFFH78000H77FFFH74000H73FFFH70000H6FFFFH6C000H6BFFFH68000H67FFFH64000H63FFFH60000H5FFFFH5C000H5BFFFH58000H57FFFH54000H53FFFH50000H4FFFFH4C000H4BFFFH48000H47FFFH44000H43FFFH40000H3FFFFH3C000H3BFFFH38000H37FFFH34000H33FFFH30000H2FFFFH2C000H2BFFFH28000H27FFFH24000H23FFFH20000H1FFFFH1C000H1BFFFH18000H17FFFH14000H13FFFH10000H0FFFFH0C000H0BFFFH08000H07FFFH04000H03FFFH00000H14131211109876543216KB BLOCK1616KB BLOCK1716KB BLOCK1816KB BLOCK1916KB BLOCK2016KB BLOCK2116KB BLOCK2216KB BLOCK2316KB BLOCK2416KB BLOCK2516KB BLOCK2616KB BLOCK2716KB BLOCK2816KB BLOCK2916KB BLOCK3016KB BLOCK3116KB BLOCK16KB BLOCK16KB BLOCK16KB BLOCK16KB BLOCK16KB BLOCK16KB BLOCK16KB BLOCK16KB BLOCK16KB BLOCK16KB BLOCK16KB BLOCK16KB BLOCK16KB BLOCK116KB BLOCK16KB BLOCK28F400SUH-LC15-3Figure 5. Memory MapBUS OPERATIONS, COMMANDS AND STATUS REGISTER DEFINITIONS Bus Operations for Word-Wide Mode (BY T E= V IH)MODE RP CE OE WE A0DQ0-15RY/BY NOTE Read V IH V IL V IL V IH X D OUT X1, 2, 7 Output Disable V IH V IL V IH V IH X High-Z X1, 6, 7 Standby V IH V IH X X X High-Z X1, 6, 7 Deep Power-Down V IL X X X X High-Z V OH1, 3 Manufacturer ID V IH V IL V IL V IH V IL00B0H V OH4Device ID V IH V IL V IL V IH V IH ID V OH4Write V IH V IL V IH V IL X D IN X1, 5, 6 Bus Operations for Word-Wide Mode (BY T E= V IH)MODE RP CE OE WE A0DQ0-7RY/BY NOTE Read V IH V IL V IL V IH X D OUT X1,2,7 Output Disable V IH V IL V IH V IH X High-Z X1, 6, 7 Standby V IH V IH X X X High-Z X1, 6, 7 Deep Power-Down V IL X X X X High-Z V OH1, 3 Manufacturer ID V IH V IL V IL V IH V IL B0H V OH4Device ID V IH V IL V IL V IH V IH ID V OH4Write V IH V IL V IH V IL X D IN X1,5,6 NOTES:1.X can be V IH or V IL for address or control pins except for RY/BY, which is either V OL or V OH.2.RY/BY output is open drain. When the WSM is ready, Erase is suspended or the device is in deeppower-down mode, RY/BY will be at V OH if it is tied to V CC through a resistor. When the RY/BYat V OL is independent of OE while a WSM operation is in progress.3.RP at GND ±0.2 V ensures the lowest deep power-down current.4.A0 at V IL provide manufacturer ID codes. A0 at V IH provide device ID codes. Device ID code = 23H (x8).Device ID Code = 6623H (x16). All other addresses are set to zero.mands for different Erase operations, Data Write Operations, and Lock-Block operations can onlybe successfully completed when V PP = V PPH.6.While the WSM is running, RY/BY in Level-Mode (default) stays at V OL until all operations are complete.RY/BY goes to V OH when the WSM is not busy or in erase suspend mode.7.RY/BY may be at V OL while the WSM is busy performing various operations. For example, a statusregister read during a write operation.COMMANDFIRST BUS CYCLE SECOND BUS CYCLE NOTEOPER.ADDRESSDATAOPER.ADDRESSDATARead Array Write X FFH Read AA AD Intelligent IdentifierWrite X 90H Read IA ID 1Read Compatible Status Register Write X 70H ReadXCSRD2Clear Status Register Write X 50H 3Word WriteWrite X 40H Write WA WD Alternate Word Write Write X 10H Write WA WD Block Erase/Confirm Write X 20H Write BA D0H 4Erase Suspend/ResumeWriteXB0HWriteXD0H4LH28F008SA-Compatible Mode Command Bus DefinitionsADDRESSDATAAA = Array Address AD = Array Data BA = Block Address CSRD = CSR Data IA = Identifier Address ID = Identifier Data WA = Write Address WD = Write DataX = Don’t CareNOTES:1.Following the intelligent identifier command, two Read operations access the manufacturer and device signature codes.2.The CSR is automatically available after device enters Data Write, Erase or Suspend operations.3.Clears CSR.3, CSR.4, and CSR.5. See Status register definitions.4.While device performs Block Erase, if you issue Erase Suspend command (B0H), be sure to confirm ESS (Erase-Suspend-Status) is set to 1 on compatible status register. In the case, ESS bit was not set to 1, also completed the Erase (ESS = 0, WSMS = 1), be sure to issue Resume command (D0H) after completed next Erase command. Beside, when the Erase Suspend command is issued, while the device is not in Erase, be sure to issue Resume command (D0H) after the next erase completed.LH28F400SU-LC Performance Enhancement Command Bus DefinitionsADDRESSDATABA = Block Address AD = Array DataWA = Write Address WD (L, H) = Write Data (Low, High)X = Don’t CareWD (H, L) = Write Data (High, Low)NOTES:1.After initial device power-up, or return from deep power-down mode, the block lock status bits default to the locked state independent of the data in the corresponding lock bits. In order to upload the lock bit status, it requires to write Protect Set/Confirm command.2.To reflect the actual lock-bit status, the Protect Set/Confirm command must be written after Lock Block/Confirm command.3.When Protect Reset/Confirm command is written, all blocks can be written and erased regardless of the state of the lock-bits.4.The Lock Block/Confirm command must be written after Protect Reset/Confirm command was written.5.A 1 is automatically complemented to load second byte of data A 1 value determines which WD is supplied first: A 1 = 0 looks at the WDL, A 1 = 1 looks at the WDH. In word-wide (x16) mode A 1 don't care.6.Second bus cycle address of Protect Set/Confirm and Protect Reset/Confirm command is 0FFH. Specifically A 9 - A 8 = 0, A 7 - A 0 = 1,others are don’t care.COMMANDMODEFIRST BUS CYCLESECOND BUS CYCLETHIRD BUS CYCLE NOTEOPER.ADD.DATA OPER.ADD.DATAOPER.ADD.DATAProtect Set/Confirm Write X 57H Write 0FFH D0H 1, 2Protect Reset/Confirm Write X 47H Write 0FFH D0H 3Lock Block/Confirm Write X 77H Write BA D0H 1, 2, 4Erase All Unlocked Blocks Write X A7H Write X D0H 1, 2Two-Byte Writex8WriteXFBHWriteA1WD (L, H)WriteWAWD (H, L)1, 2, 5WSMS ESS ES DWS VPPS R R R 76543210 Compatible Status RegisterCSR.7=WRITE STA TE MACHINE STA TUS (WSMS)1 = Ready0 = BusyCSR.6=ERASE-SUSPEND STA TUS (ESS)1 = Erase Suspended0 = Erase in Progress/CompletedCSR.5=ERASE STA TUS (ES)1 = Error in Block Erasure0 = Successful Block EraseCSR.4=DA TA-WRITE ST A TUS (DWS)1 = Error in Data Write0 = Data Write SuccessfulCSR.3=V PP ST A TUS (VPPS)1 = V PP Low Detect, Operation Abort0 = V PP OK NOTES:1.RY/BY output or WSMS bit must be checked to determinecompletion of an operation (Erase Suspend, Erase or Data Write) before the appropriate Status bit (ESS, ES or DWS) is checked for success.2.If DWS and ES are set to ‘1’ during an erase attempt, animproper command sequence was entered. Clear the CSR and attempt the operation again.3.The VPPS bit, unlike an A/D converter, does not providecontinuous indication of V PP level. The WSM interrogates V PP’s level only after the Data-Write or Erase commandsequences have been entered, and informs the system if V PP has not been switched on. VPPS is not guaranteed to report accurate feedback between V PPL and V PPH.4.CSR.2 - CSR.0 = Reserved for further enhancements.These bits are reserved for future use and should bemasked out when polling the CSR.4M FLASH MEMORYSOFTWARE ALGORITHMSOVERVIEWWith the advanced Command User Interface, its Per-formance Enhancement commands and Status Regis-ters, the software code required to perform a given operation may become more intensive but it will result in much higher write/erase performance compared with current flash memory architectures.The software flowcharts describing how a given operation proceeds are shown here. Figures 6 through 8 depict flowcharts using the 2nd generation flash device in the LH28F008SA-compatible mode. Figures 9 through 15 depict flowcharts using the 2nd genera-tion flash device’s performance enhancement com-mands mode.When the device power-up or the device is reset by RP pin, all blocks come up locked. Therefore, Word/ Byte Write, T wo Byte Serial Write and Block Erase can not be performed in each block. However, at that time, Erase All Unlocked Block is performed normally, if used, and reflect actual lock status, also the unlocked block data is erased. When the device power-up or the device is reset by RP pin, Set Write Protect command must be written to reflect actual block lock status.Reset Write Protect command must be written be-fore Write Block Lock command. T o reflect actual block lock status, Set Write Protect command is succeeded.The Compatible Status Register (CSR) is used to determine which blocks are locked. In order to see Lock Status of a certain block, a Word/Byte Write command (WA = Block Address, WD = FFH) is written to the CUI, after issuing Set Write Protect command. If CSR.7, CSR.5 and CSR.4 (WSMS, ES and DWS) are set to ‘1’s, the block is locked. If CSR.7 is set to ‘1’, the block is not locked.Reset Write Protect command enables Write/Erase operation to each block.In the case of Block Erase is performed, the block lock information is also erased. Block Lock command and Set Write Protect command must be written to pro-hibit Write/Erase operation to each block.There are unassigned commands. It is not recom-mended that the customer use any command other than the valid commands specified in “Command Bus Defi-nitions”. Sharp reserved the right to redefine these codes for future functions.Figure 6. Word/Byte Writes with Compatible Status RegisterFigure 7. Block Erase with Compatible Status RegisterFigure 8. Erase Suspend to Read Array with Compatible Status RegisterFigure 9. Block Locking SchemeFigure 10. Updating Data in a Locked BlockFigure 11. Two-Byte SerialWrites with Compatible Status Registers (40-pin TSOP)Figure 12. Two-Byte Serial Writes with Compatible Status Registers (56-pin TSOP, 44-pin SOP)Figure 13. Erase All Unlocked Blocks with Compatible Status RegistersFigure 14. Set Write ProtectFigure 15. Reset Write Protect*WARNING: Stressing the device beyond the “Abso-lute Maximum Ratings” may cause permanent dam-age. These are stress ratings only. Operation beyondthe “Operating Conditions” is not recommended and extended exposure beyond the “Operating Conditions”may affect device reliability.ELECTRICAL SPECIFICATIONS Absolute Maximum Ratings*T emperature under bias .........................0°C to +70°C Storage temperature .........................-65°C to +125°CV CC = 3.3 V ± 0.3 V SystemsSYMBOLPARAMETERMIN.MAX.UNITSTEST CONDITIONSNOTET A Operating Temperature, Commercial 070°C Ambient Temperature 1V CC V CC with Respect to GND-0.27.0V 2V PP V PP Supply Voltage with Respect to GND -0.27.0V 2V Voltage on any Pin (Except V CC , V PP )with Respect to GND-0.5V CC + 0.5V 2I Current into any Non-Supply Pin ±30mA I OUTOutput Short Circuit Current100.0mA3NOTES:1.Operating temperature is for commercial product defined by this specification.2.Minimum DC voltage is -0.5 V on input/output pins. During transitions, this level may undershoot to -2.0 V for periods < 20 ns.Maximum DC voltage on input/output pins is V CC + 0.5 V which, during transitions, may overshoot to V CC + 2.0 V for periods < 20 ns.3.Output shorted for no more than one second. No more than one output shorted at a time.Capacitance For a 3.3 V SystemsSYMBOLPARAMETERTYP.MAX.UNITSTEST CONDITIONSNOTEC INCapacitance Looking into an Address/Control Pin 710pF T A = 25°C, f = 1.0 MHz 1Capacitance Looking into an Address/Control Pin A 1912pF T A = 25°C, f = 1.0 MHz 1C OUT Capacitance Looking into an Output Pin 912pF T A = 25°C, f = 1.0 MHz 1C LOADLoad Capacitance Driven by Outputs for Timing Specifications50pF For V CC = 3.3 V ±0.3 V 1Equivalent Testing Load Circuit V CC ± 10%2.5ns50 Ω transmission line delayNOTE:1.Sampled, not 100% tested.Timing NomenclatureFor 3.3 V systems use 1.5 V cross point definitions.Each timing parameter consists of 5 characters. Some common examples are defined below:t CE t ELQV time (t) from CE (E) going low (L) to the outputs (Q) becoming valid (V)t OE t GLQVtime (t) from OE (G) going low (L) to the outputs (Q) becoming valid (V)t ACC t AVQVtime (t) from address (A) valid (V) to the outputs (Q) becoming valid (V)t AS t AVWH time (t) from address (A) valid (V) to WE (W) going high (H)t DHt WHDX time (t) from WE (W) going high (H) to when the data (D) can become undefined (X)Figure 16. Transient Input/Output Reference Waveform (V CC = 3.3 V)Figure 17. Transient Equivalent TestingLoad Circuit (V CC = 3.3 V)PIN CHARACTERSPIN STATESA Address Inputs H High D Data Inputs L Low Q Data Outputs V ValidE CE(Chip Enable)X Driven, but not necessarily valid G OE(Output Enable)ZHigh ImpedanceW WE (Write Enable)P RP(Deep Power-Down Pin)R RY/BY(Ready/Busy)V Any Voltage Level 3 VV CC at 3.0 V Min.2.5 ns OF 50 Ω TRANSMISSION LINETOTAL CAPACITANCE = 50 pFFROM OUTPUT UNDER TESTTEST POINT28F400SUH-LC15-15DC CharacteristicsV CC = 3.3 V ± 0.3 V, T A = 0°C to +70°CSYMBOL PARAMETER TYP.MIN.MAX.UNITS TEST CONDITIONS NOTEI IL Input Load Current±1µA V CC = V CC MAX., V IN = V CC or GND1I LO Output Leakage Current±10µA V CC = V CC MAX., V IN = V CC or GND1I CCS V CC Standby Current415µAV CC = V CC MAX.,CE, RP= V CC ±0.2 VBYTE = V CC ±0.2 V or GND ±0.2 V1,4 0.34mAV CC = V CC MAX.,CE, RP= V IHBYTE = V IH or V ILI CCD V CC Deep Power-DownCurrent0.28µA RP= GND ±0.2 V1I CCR1V CC Read Current35mA V CC = V CC MAX.,CMOS: CE= GND ±0.2 VBYTE = GND ±0.2 V or V CC ±0.2 VInputs = GND ±0.2 V or V CC ±0.2 V,TTL: CE= V IL,BYTE = V IL or V IHInputs = V IL or V IH,f = 8 MHz, I OUT = 0 mA1, 3, 4I CCR2V CC Read Current1020mA V CC = V CC MAX.,CMOS: CE= GND ±0.2 VBYTE = GND ±0.2 V or V CC ±0.2 VInputs = GND ±0.2 V or V CC ±0.2 V,TTL: CE= V IL,BYTE = V IH or V ILInputs = V IL or V IH,f = 4 MHz, I OUT = 0 mA1, 3, 4I CCW V CC Write Current816mA Word/Byte Write in Progress1 I CCE V CC Block Erase Current612mA Block Erase in Progress1I CCES V CC Erase SuspendCurrent36mACE= V IHBlock Erase Suspended1, 2I PPS V PP Standby Current±1±10µA V PP≤ V CC1I PPD V PP Deep Power-DownCurrent0.28µA RP= GND ±0.2 V1DC Characteristics (Continued)V CC = 3.3 V ± 0.3 V , T A = 0°C to +70°CNOTES:1.All currents are in RMS unless otherwise noted. T ypical values at V CC = 3.3 V , V PP = 5.0 V , T = 25°C. These currents are valid for all product versions (package and speeds).2.I CCES is specified with the device de-selected. If the device is read while in erase suspend mode, current draw is the sum of I CCES and I CCR .3.Automatic Power Saving (APS) reduces I CCR to less than 2 mA in Static operation.4.CMOS inputs are either V CC ± 0.2 V or GND ± 0.2 V . TTL Inputs are either V IL or V IH .5.In 2.7 V < V CC < 3.0 V operation, TTL-lelvel input of RP is V IL (MAX.) = 0.6 V .6.V PPL in read is V CC - 0.2 V < V PPL < 5.5 V or GND < V PPL < GND + 0.2 V .SYMBOLPARAMETERTYPEMIN.MAX.UNITSTEST CONDITIONS NOTEI PPR V PP Read Current 200µA V PP > V CC1I PPW V PP Write Current 1535mA V PP = V PPH , Word/Byte Write in Progress 1I PPE V PP Erase Current 2040mA V PP = V PPH ,Block Erase in Progress 1I PPES V PP Erase SuspendCurrent200µA V PP = V PPH ,Block Erase Suspended1V IL Input Low Voltage -0.30.8V 5V IH Input High Voltage 2.0V CC + 0.3V V OL Output Low Voltage0.4V V CC = V CC MIN. and I OL = 4 mA V OH 1Output High Voltage2.4V I OL = -2 mA V CC = V CC MIN.V OH 2 V CC - 0.2VI OL = 100 µA V CC = V CC MIN.V PPL V PP during Normal Operations0.0 5.5V 6V PPH V PP during Write/Erase Operations 5.04.55.5V V LKOV CC Erase/Write Lock Voltage1.4V。

卓有成效地排查具有挑战性的问题配备丰富的功能,适用于高压和低压应用场景更安全、更智慧地工作红外成像功能使您能够快速扫描过热的系统部件,然后使用数字万用表测试功能排查和诊断故障• 借助于18种数字万用表功能,包括VFD 模式、 真有效值、LoZ (低阻抗输入)、非接触式 试电笔(NCV )、内置照明灯和激光 指示器,解决具有挑战性的问题• 可用于测量电压、电流、频率、电阻、 导通性、二极管、电容和温度• 具有直观的菜单系统,操作便捷• 借助于非接触式温度测量功能,在安全 距离处识别带电设备和存在故障的设备• 以无线的方式连接至FLIR InSite 专业 工作流管理工具,从而简化检测 流程和数据收集、分享与报告*• 使用内置数据存储器保存电气 参数数据和热图像*设计和功能一款经久耐用、集多种功能于一体的工具• 仪表通过抗跌落测试,可靠耐用,适用于任何工作环境• 电池盒采用‘免工具’设计,可快速 轻松地更换电池*• 具有宽广的视场角,可清晰地 查看TFT 显示屏上的读数**仅限于DM285。

世界第六感技术参数如有变更,恕不另行通知。

最新技术参数,请访问技术参数红外成像参数DM284DM285红外分辨率160 x 120 (19,200像素)160 x 120 (19,200像素)红外探测器FLIR Lepton ®微测辐射热计FLIR Lepton ®微测辐射热计温度灵敏度≤ 150 mK≤ 150 mK发射率设置带自定义调整的4个预设值带自定义调整的4个预设值温度精度3°C 或3.5%3°C 或3.5%温度范围-10°C 至150°C -10°C 至150°C 视场角46° x 35°50° x 38°激光指示器支持支持调焦固定固定红外成像调色板铁红色、彩虹色、灰度铁红色、彩虹色、灰度电平与跨度自动自动测量参数-两种型号真有效值支持量程基本精度交流/直流电压(V )1000 V ±1.0% / 0.09%交流/直流电压(mV )600.0 mV ±1.0% / 0.5%变频交流电压(V )1000 V ±1.0%交流/直流低阻抗 输入(V )1000 V ±2.0%交流/直流电流(A )10.00 A ±1.5% / 1.0%交流/直流电流(mA )400.0 mA ±1.5% / 1.0%交流/直流电流(μA )4,000 μA ±1.0%电阻 6.000 MΩ50.00 MΩ±0.9%±3.0%电容10.00 mF ±1.9%二极管测试 1.500 V±0.9%柔性电流钳范围3000 A 交流(可选TA72/74)± 3.0% + 5位数频率计数器100.00 kHz ±0.1%温度,K 型热电偶-40°C 至400°C±1.0% + 3°C其它测量参数DM284DM285导通性检查600 Ω20 Ω和200 Ω测量速率每秒3个样本每秒3个样本最小值/最大值/平均值支持支持一般信息连接性–蓝牙®数据记录与存储–10 组40k 标量测量值, 100张图像自动关机支持支持照明灯支持支持显示屏尺寸 2.8英寸TFT 屏 2.8英寸TFT 屏电池4节AAA 电池;可选TA04锂聚合物可充电电池3节AA 电池;可选TA04锂聚合物可充电电池抗跌落测试3 m 3 m IP 等级IP54IP40安全等级CAT III-1000V, CAT IV-600V CAT III-1000V, CAT IV-600V 尺寸(长×宽×高)200 x 95 x 49 mm 200 x 95 x 49 mm 重量537 g537 g质保10年整机和探测器保修10年整机和探测器保修标配数字万用表、L91 锂电池、硅测试引线、测试引线存储/三脚架配件、K 型热电偶、鳄鱼夹探头、软质便携箱订购信息订单编号FLIR DM285工业级红外成像数字万用表 (带数据记录、连接功能,采用IGM 技术)793950372876FLIR DM284工业级红外成像真有效值数字万用表 (采用IGM 技术)793950372845如需获取可选配件的完整列表,敬请访问:/store/instruments/testaccessories。