LC89975MTER中文资料

- 格式:pdf

- 大小:287.94 KB

- 文档页数:7

1、引言UCC3895是美国德州仪器公司生产的移相谐振全桥软开关控制器,该系列控制器采用了先进的BCDM OS技术。

UCC3895在基本功能上与UC3875系列和UC3879系列控制器完全相同,同时增加了一些新的功能。

下面对其特点、引脚功能、电气参数、工作原理分别进行介绍。

2、特点和引脚说明2.1 特点(1)输出导通延迟时间编程可控;(2)自适应延迟时间设置功能;(3)双向振荡器同步功能;(4)电压模式控制或电流模式控制;(5)软启动/软关机和控制器片选功能编程可控,单引脚控制;(6)占空比控制范围0%~100%;(7)内置7MHz误差放大器;(8)最高工作频率达到1MHz;(9)工作电流低,500KHz下的工作电流仅为5mA;(10)欠压锁定状态下的电流仅为150μA。

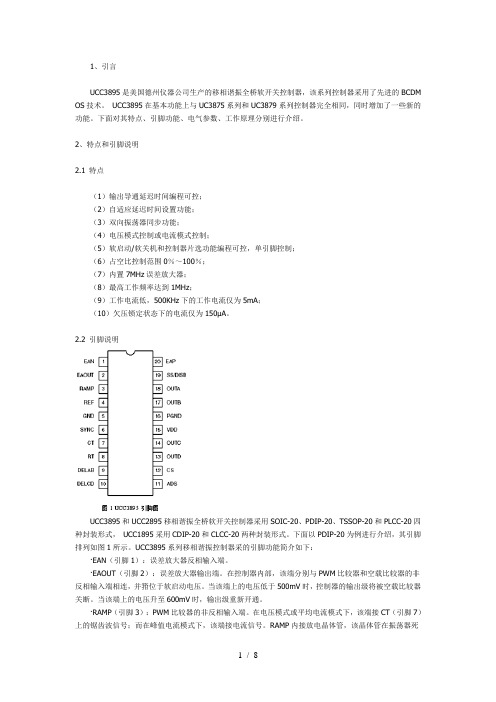

2.2 引脚说明UCC3895和UCC2895移相谐振全桥软开关控制器采用SOIC-20、PDIP-20、TSSOP-20和PLCC-20四种封装形式,UCC1895采用CDIP-20和CLCC-20两种封装形式。

下面以PDIP-20为例进行介绍,其引脚排列如图1所示。

UCC3895系列移相谐振控制器采的引脚功能简介如下:·EAN(引脚1):误差放大器反相输入端。

·EAOUT(引脚2):误差放大器输出端。

在控制器内部,该端分别与PWM比较器和空载比较器的非反相输入端相连,并箝位于软启动电压。

当该端上的电压低于500mV时,控制器的输出级将被空载比较器关断。

当该端上的电压升至600mV时,输出级重新开通。

·RAMP(引脚3):PWM比较器的非反相输入端。

在电压模式或平均电流模式下,该端接CT(引脚7)上的锯齿波信号;而在峰值电流模式下,该端接电流信号。

RAMP内接放电晶体管,该晶体管在振荡器死区时间内触发。

·REF(引脚4):精密5V基准电压输出端。

控制器内部的基准电源一方面为控制器内部的电路供电,另一方面还能够向外接负载提供5mA的偏置电流。

LM2578A/LM3578A Switching RegulatorGeneral DescriptionThe LM2578A is a switching regulator which can easily be set up for such DC-to-DC voltage conversion circuits as the buck,boost,and inverting configurations.The LM2578A fea-tures a unique comparator input stage which not only has separate pins for both the inverting and non-inverting inputs, but also provides an internal1.0V reference to each input, thereby simplifying circuit design and p.c.board layout.The output can switch up to750mA and has output pins for its collector and emitter to promote design flexibility.An external current limit terminal may be referenced to either the ground or the V in terminal,depending upon the application.In addi-tion,the LM2578A has an on board oscillator,which sets the switching frequency with a single external capacitor from<1 Hz to100kHz(typical).The LM2578A is an improved version of the LM2578,offer-ing higher maximum ratings for the total supply voltage and output transistor emitter and collector voltages.Featuresn Inverting and non-inverting feedback inputsn 1.0V reference at inputsn Operates from supply voltages of2V to40Vn Output current up to750mA,saturation less than0.9V n Current limit and thermal shut downn Duty cycle up to90%Applicationsn Switching regulators in buck,boost,inverting,and single-ended transformer configurationsn Motor speed controln Lamp flasherConnection Diagram and Ordering InformationDual-In-Line Package00871129Order Number LM3578AM,LM2578AN or LM3578ANSee NS Package Number M08A or N08E February2005LM2578A/LM3578A Switching Regulator©2005National Semiconductor Corporation Functional Diagram00871101L M 2578A /L M 3578A 2Absolute Maximum Ratings(Note1) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Total Supply Voltage50V Collector Output to Ground−0.3V to+50V Emitter Output to Ground(Note2)−1V to+50V Power Dissipation(Note3)Internally limited Output Current750mA Storage Temperature−65˚C to+150˚C Lead Temperature(soldering,10seconds)260˚C Maximum Junction Temperature150˚CESD Tolerance(Note4)2kVOperating RatingsAmbient Temperature RangeLM2578A−40˚C≤T A≤+85˚C LM3578A0˚C≤T A≤+70˚C Junction Temperature RangeLM2578A−40˚C≤T J≤+125˚C LM3578A0˚C≤T J≤+125˚CElectrical CharacteristicsThese specifications apply for2V≤V IN≤40V(2.2V≤V IN≤40V for T J≤−25˚C),timing capacitor C T=3900pF,and25%≤duty cycle≤75%,unless otherwise specified.Values in standard typeface are for T J=25˚C;values in boldface type apply for operation over the specified operating junction temperature range.LM2578A/Symbol Parameter Conditions Typical LM3578A Units(Note5)Limit(Note6) OSCILLATORf OSC Frequency20kHz24kHz(max)16kHz(min)∆f OSC/∆T Frequency Drift with Temperature−0.13%/˚C Amplitude550mV p-p REFERENCE/COMPARATOR(Note7)V R Input Reference I1=I2=0mA and 1.0V Voltage I1=I2=1mA±1%(Note8) 1.050/1.070V(max)0.950/0.930V(min)∆V R/∆V IN Input Reference Voltage LineRegulationI1=I2=0mA and0.003%/VI1=I2=1mA±1%(Note8)0.01/0.02%/V(max) I INV Inverting Input Current I1=I2=0mA,duty cycle=25%0.5µALevel Shift Accuracy Level Shift Current=1mA 1.0%10/13%(max)∆V R/∆t Input Reference Voltage Long TermStability100ppm/1000h OUTPUTV C(sat)Collector Saturation Voltage I C=750mA pulsed,Emittergrounded 0.7V0.90/1.2V(max)V E(sat)Emitter Saturation Voltage I O=80mA pulsed, 1.4VV IN=V C=40V 1.7/2.0V(max)I CES Collector Leakage Current V IN=V CE=40V,Emitter grounded,Output OFF 0.1µA200/250µA(max)BV CEO(SUS)Collector-Emitter Sustaining Voltage I SUST=0.2A(pulsed),V IN=060V50V(min) CURRENT LIMITV CL Sense Voltage Shutdown Level Referred to V IN or Ground110mV(Note9)80mV(min)160mV(max)LM2578A/LM3578A3Electrical Characteristics(Continued)These specifications apply for 2V ≤V IN ≤40V (2.2V ≤V IN ≤40V for T J ≤−25˚C),timing capacitor C T =3900pF,and 25%≤duty cycle ≤75%,unless otherwise specified.Values in standard typeface are for T J =25˚C;values in boldface type apply for operation over the specified operating junction temperature range.LM2578A/Symbol ParameterConditionsTypical LM3578A Units(Note 5)Limit (Note 6)CURRENT LIMIT ∆V CL /∆T Sense Voltage Temperature Drift 0.3%/˚C I CLSense Bias CurrentReferred to V IN 4.0µA Referred to ground0.4µA DEVICE POWER CONSUMPTION I SSupply CurrentOutput OFF,V E =0V2.0mA3.5/4.0mA (max)Output ON,I C =750mA pulsed,14mAV E =0VNote 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.DC and AC electrical specifications do not apply when operating the device beyond its rated operating conditions.Note 2:For T J ≥100˚C,the Emitter pin voltage should not be driven more than 0.6V below ground (see Application Information).Note 3:At elevated temperatures,devices must be derated based on package thermal resistance.The device in the 8-pin DIP must be derated at 95˚C/W,junction to ambient.The device in the surface-mount package must be derated at 150˚C/W,junction-to-ambient.Note 4:Human body model,1.5k Ωin series with 100pF.Note 5:Typical values are for T J =25˚C and represent the most likely parametric norm.Note 6:All limits guaranteed at room temperature (standard type face)and at temperature extremes (bold type face).Room temperature limits are 100%production tested.Limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC)methods.All limits are used to calculate AOQL.Note 7:Input terminals are protected from accidental shorts to ground but if external voltages higher than the reference voltage are applied,excessive current will flow and should be limited to less than 5mA.Note 8:I 1and I 2are the external sink currents at the inputs (refer to Test Circuit).Note 9:Connection of a 10k Ωresistor from pin 1to pin 4will drive the duty cycle to its maximum,typically 90%.Applying the minimum Current Limit Sense Voltage to pin 7will not reduce the duty cycle to less than 50%.Applying the maximum Current Limit Sense Voltage to pin 7is certain to reduce the duty cycle below 50%.Increasing this voltage by 15mV may be required to reduce the duty cycle to 0%,when the Collector output swing is 40V or greater (see Ground-Referred Current Limit Sense Voltage typical curve).Typical Performance CharacteristicsOscillator Frequency Changewith TemperatureOscillator Voltage Swing0087113200871133L M 2578A /L M 3578A 4Typical Performance Characteristics(Continued)Input Reference Voltage Drift with TemperatureCollector Saturation Voltage(Sinking Current,Emitter Grounded)0087113400871135Emitter Saturation Voltage(Sourcing Current,Collector at V in )Ground ReferredCurrent Limit Sense Voltage0087113600871137Current Limit Sense Voltage Drift with Temperature Current Limit Response Time for Various Over Drives0087113800871139LM2578A/LM3578A5Typical Performance Characteristics(Continued)Current Limit Sense Voltagevs Supply VoltageSupply Current0087114000871141Supply CurrentCollector Current with Emitter Output Below Ground0087114200871143Test Circuit*Parameter tests can be made using the test circuit shown.Select the desired V in ,collector voltage and duty cycle with adjustable power supplies.A digital volt meter with an input resistance greater than 100M Ωshould be used to measure the following:Input Reference Voltage to Ground;S1in either position.Level Shift Accuracy (%)=(T P3(V)/1V)x 100%;S1at I 1=I 2=1mAInput Current (mA)=(1V −T p3(V))/1M Ω:S1at I 1=I 2=0mA.Oscillator parameters can be measured at T p4using a fre-quency counter or an oscilloscope.The Current Limit Sense Voltage is measured by connecting an adjustable 0-to-1V floating power supply in series with the current limit terminal and referring it to either the ground or the V in terminal.Set the duty cycle to 90%and monitor test point T P5while adjusting the floating power supply voltage until the LM2578A’s duty cycle just reaches 0%.This voltage is the Current Limit Sense Voltage.The Supply Current should be measured with the duty cycle at 0%and S1in the I 1=I 2=0mA position.*LM2578A specifications are measured using automated test equipment.This circuit is provided for the customer’s convenience when checking parameters.Due to possible variations in testing conditions,the measured values from these testing procedures may not match those of the factory.L M 2578A /L M 3578A 6Test Circuit*(Continued)00871103 Op amp supplies are±15VDVM input resistance>100MΩ*LM2578max duty cycle is90%Definition of TermsInput Reference Voltage:The voltage(referred to ground) that must be applied to either the inverting or non-inverting input to cause the regulator switch to change state(ON or OFF).Input Reference Current:The current that must be drawn from either the inverting or non-inverting input to cause the regulator switch to change state(ON or OFF).Input Level Shift Accuracy:This specification determines the output voltage tolerance of a regulator whose output control depends on drawing equal currents from the inverting and non-inverting inputs(see the Inverting Regulator of Fig-ure21,and the RS-232Line Driver Power Supply of Figure 23).Level Shift Accuracy is tested by using two equal-value resistors to draw current from the inverting and non-inverting input terminals,then measuring the percentage difference in the voltages across the resistors that produces a controlled duty cycle at the switch output.Collector Saturation Voltage:With the inverting input ter-minal grounded thru a10kΩresistor and the output transis-tor’s emitter connected to ground,the Collector Saturation-Voltage is the collector-to-emitter voltage for a given collector current.Emitter Saturation Voltage:With the inverting input termi-nal grounded thru a10kΩresistor and the output transistor’s collector connected to V in,the Emitter Saturation Voltage is the collector-to-emitter voltage for a given emitter current. Collector Emitter Sustaining Voltage:The collector-emitter breakdown voltage of the output transistor,mea-sured at a specified current.Current Limit Sense Voltage:The voltage at the CurrentLimit pin,referred to either the supply or the ground terminal,which(via logic circuitry)will cause the output transistor toturn OFF and resets cycle-by-cycle at the oscillator fre-quency.Current Limit Sense Current:The bias current for theCurrent Limit terminal with the applied voltage equal to theCurrent Limit Sense Voltage.Supply Current:The IC power supply current,excluding thecurrent drawn through the output transistor,with the oscilla-tor operating.Functional DescriptionThe LM2578A is a pulse-width modulator designed for useas a switching regulator controller.It may also be used inother applications which require controlled pulse-width volt-age drive.A control signal,usually representing output voltage,fed intothe LM2578A’s comparator is compared with an internally-generated reference.The resulting error signal and the os-cillator’s output are fed to a logic network which determineswhen the output transistor will be turned ON or OFF.Thefollowing is a brief description of the subsections of theLM2578A.COMPARATOR INPUT STAGEThe LM2578A’s comparator input stage is unique in that boththe inverting and non-inverting inputs are available to theuser,and both contain a1.0V reference.This is accom-plished as follows:A1.0V reference is fed into a modifiedvoltage follower circuit(see FUNCTIONAL DIAGRAM).When both input pins are open,no current flows through R1LM2578A/LM3578A7Functional Description(Continued)and R2.Thus,both inputs to the comparator will have the potential of the 1.0V reference,V A .When one input,for example the non-inverting input,is pulled ∆V away from V A ,a current of ∆V/R1will flow through R1.This same current flows through R2,and the comparator sees a total voltage of 2∆V between its inputs.The high gain of the system,through feedback,will correct for this imbalance and return both inputs to the 1.0V level.This unusual comparator input stage increases circuit flex-ibility,while minimizing the total number of external compo-nents required for a voltage regulator system.The inverting switching regulator configuration,for example,can be set up without having to use an external op amp for feedback polarity reversal (see TYPICAL APPLICATIONS).OSCILLATORThe LM2578A provides an on-board oscillator which can be adjusted up to 100kHz.Its frequency is set by a single external capacitor,C 1,as shown in Figure 1,and follows the equationf OSC =8x10−5/C 1The oscillator provides a blanking pulse to limit maximum duty cycle to 90%,and a reset pulse to the internal circuitry.OUTPUT TRANSISTORThe output transistor is capable of delivering up to 750mA with a saturation voltage of less than 0.9V.(see Collector Saturation Voltage and Emitter Saturation Voltage curves).The emitter must not be pulled more than 1V below ground (this limit is 0.6V for T J ≥100˚C).Because of this limit,an external transistor must be used to develop negative output voltages (see the Inverting Regulator Typical Application).Other configurations may need protection against violation of this limit (see the Emitter Output section of the Applica-tions Information).CURRENT LIMITThe LM2578A’s current limit may be referenced to either the ground or the V in pins,and operates on a cycle-by-cycle basis.The current limit section consists of two comparators:one with its non-inverting input referenced to a voltage 110mV below V in ,the other with its inverting input referenced110mV above ground (see FUNCTIONAL DIAGRAM).The current limit is activated whenever the current limit terminal is pulled 110mV away from either V in or ground.Applications InformationCURRENT LIMITAs mentioned in the functional description,the current limit terminal may be referenced to either the V in or the ground terminal.Resistor R3converts the current to be sensed into a voltage for current limit detection.CURRENT LIMIT TRANSIENT SUPPRESSIONWhen noise spikes and switching transients interfere with proper current limit operation,R1and C1act together as a low pass filter to control the current limit circuitry’s response time.Because the sense current of the current limit terminal varies according to where it is referenced,R1should be less than 2k Ωwhen referenced to ground,and less than 100Ωwhen referenced to V in .00871104FIGURE 1.Value of Timing Capacitor vsOscillator Frequency00871115FIGURE 2.Current Limit,Ground Referred00871116FIGURE 3.Current Limit,V in ReferredL M 2578A /L M 3578A 8Applications Information(Continued)C.L.SENSE VOLTAGE MULTIPLICATIONWhen a larger sense resistor value is desired,the voltage divider network,consisting of R1and R2,may be used.This effectively multiplies the sense voltage by(1+R1/R2).Also, R1can be replaced by a diode to increase current limit sense voltage to about800mV(diode V f+110mV).UNDER-VOLTAGE LOCKOUTUnder-voltage lockout is accomplished with few external components.When V in becomes lower than the zener breakdown voltage,the output transistor is turned off.This occurs because diode D1will then become forward biased, allowing resistor R3to sink a greater current from the non-inverting input than is sunk by the parallel combination of R1 and R2at the inverting terminal.R3should be one-fifth of the value of R1and R2in parallel.MAXIMUM DUTY CYCLE LIMITINGThe maximum duty cycle can be externally limited by adjust-ing the charge to discharge ratio of the oscillator capacitor with a single external resistor.Typical values are50µA for the charge current,450µA for the discharge current,and a voltage swing from200mV to750mV.Therefore,R1is selected for the desired charging and discharging slopes and C1is readjusted to set the oscillator frequency.00871117 FIGURE4.Current Limit Transient Suppressor,Ground Referred00871118 FIGURE5.Current Limit Transient Suppressor,V in Referred00871119 FIGURE6.Current Limit Sense Voltage Multiplication,Ground Referred00871120FIGURE7.Current Limit Sense Voltage Multiplication,V in Referred00871122FIGURE8.Under-Voltage LockoutLM2578A/LM3578A9Applications Information(Continued)DUTY CYCLE ADJUSTMENTWhen manual or mechanical selection of the output transis-tor’s duty cycle is needed,the cirucit shown below may be used.The output will turn on with the beginning of each oscillator cycle and turn off when the current sunk by R2and R3from the non-inverting terminal becomes greater than the current sunk from the inverting terminal.With the resistor values as shown,R3can be used to adjust the duty cycle from 0%to 90%.When the sum of R2and R3is twice the value of R1,the duty cycle will be about 50%.C1may be a large electrolytic capacitor to lower the oscillator frequency below 1Hz.REMOTE SHUTDOWNThe LM2578A may be remotely shutdown by sinking a greater current from the non-inverting input than from the inverting input.This may be accomplished by selecting re-sistor R3to be approximately one-half the value of R1and R2in parallel.EMITTER OUTPUTWhen the LM2578A output transistor is in the OFF state,if the Emitter output swings below the ground pin voltage,the output transistor will turn ON because its base is clamped near ground.The Collector Current with Emitter Output Be-low Ground curve shows the amount of Collector current drawn in this mode,vs temperature and Emitter voltage.When the Collector-Emitter voltage is high,this current will cause high power dissipation in the output transistor and should be avoided.This situation can occur in the high-current high-voltage buck application if the Emitter output is used and the catch diode’s forward voltage drop is greater than 0.6V.A fast-recovery diode can be added in series with the Emitter output to counter the forward voltage drop of the catch diode (see Figure 2).For better efficiency of a high output current buck regulator,an external PNP transistor should be used as shown in Figure 16.SYNCHRONIZING DEVICESWhen several devices are to be operated at once,their oscillators may be synchronized by the application of an external signal.This drive signal should be a pulse waveform with a minimum pulse width of 2µs.and an amplitude from00871121FIGURE 9.Maximum Duty Cycle Limiting00871123FIGURE 10.Duty Cycle Adjustment00871124FIGURE 11.Shutdown Occurs when V L is High00871130FIGURE 12.D1Prevents Output Transistor from Improperly Turning ON due to D2’s Forward Voltage L M 2578A /L M 3578A 10Applications Information(Continued)1.5V to2.0V.The signal source must be capable of 1.)driving capacitive loads and 2.)delivering up to 500µA for each LM2578A.Capacitors C1thru CN are to be selected for a 20%slower frequency than the synchronization frequency.Typical ApplicationsThe LM2578A may be operated in either the continuous or the discontinuous conduction mode.The following applica-tions (except for the Buck-Boost Regulator)are designed for continuous conduction operation.That is,the inductor cur-rent is not allowed to fall to zero.This mode of operation has higher efficiency and lower EMI characteristics than the dis-continuous mode.BUCK REGULATORThe buck configuration is used to step an input voltage down to a lower level.Transistor Q1in Figure 14chops the input DC voltage into a squarewave.This squarewave is then converted back into a DC voltage of lower magnitude by the low pass filter consisting of L1and C1.The duty cycle,D,of the squarewave relates the output voltage to the input volt-age by the following equation:V out =D x V in =V in x (t on )/(t on +t off ).Figure 15is a 15V to 5V buck regulator with an output current,I o ,of 350mA.The circuit becomes discontinuous at 20%of I o(max),has 10mV of output voltage ripple,an effi-ciency of 75%,a load regulation of 30mV (70mA to 350mA)and a line regulation of 10mV (12≤V in ≤18V).Component values are selected as follows:R1=(V o −1)x R2where R2=10k ΩR3=V/I sw(max)R3=0.15Ωwhere:V is the current limit sense voltage,0.11VI sw(max)is the maximum allowable current thru the output transistor.L1is the inductor and may be found from the inductance calculation chart (Figure 16)as follows:Given V in =15VV o =5VI o(max)=350mA f OSC =50kHzDiscontinuous at 20%of I o(max).Note that since the circuit will become discontinuous at 20%of I o(max),the load current must not be allowed to fall below 70mA.00871125FIGURE 13.Synchronizing Devices00871105FIGURE 14.Basic Buck RegulatorLM2578A/LM3578A11Typical Applications(Continued)00871106V in =15V R3=0.15ΩV o =5V C1=1820pF V ripple =10mV C2=220µF I o =350mA C3=20pF f osc =50kHz L1=470µH R1=40k ΩD1=1N5818R2=10k ΩFIGURE 15.Buck or Step-Down RegulatorL M 2578A /L M 3578A 12LM2578A/LM3578A Typical Applications(Continued)00871131FIGURE16.DC/DC Inductance Calculator13Typical Applications(Continued)Step 1:Calculate the maximum DC current through the inductor,I L(max).The necessary equations are indicated at the top of the chart and show that I L(max)=I o(max)for the buck configuration.Thus,I L(max)=350mA.Step 2:Calculate the inductor Volts-sec product,E-T op ,according to the equations given from the chart.For the Buck:E-T op =(V in −V o )(V o /V in )(1000/f osc )=(15−5)(5/15)(1000/50)=66V-µs.with the oscillator frequency,f osc ,expressed in kHz.Step 3:Using the graph with axis labeled “Discontinuous At %I OUT ”and “I L(max,DC)”find the point where the desired maximum inductor current,I L(max,DC)intercepts the desired discontinuity percentage.In this example,the point of interest is where the 0.35A line intersects with the 20%line.This is nearly the midpoint of the horizontal axis.Step 4:This last step is merely the translation of the point found in Step 3to the graph directly below it.This is accom-plished by moving straight down the page to the point which intercepts the desired E-T op .For this example,E-T op is 66V-µs and the desired inductor value is 470µH.Since this example was for 20%discontinuity,the bottom chart could have been used directly,as noted in step 3of the chart instructions.For a full line of standard inductor values,contact Pulse Engineering (San Diego,Calif.)regarding their PE526XX series,or A.I.E.Magnetics (Nashville,Tenn.).A more precise inductance value may be calculated for the Buck,Boost and Inverting Regulators as follows:BUCKL =V o (V in −V o )/(∆I L V in f osc )BOOSTL =V in (V o −V in )/(∆I L f osc V o )INVERTL =V in |V o |/[∆I L (V in +|V o |)f osc ]where ∆I L is the current ripple through the inductor.∆I L is usually chosen based on the minimum load current expected of the circuit.For the buck regulator,since the inductor current I L equals the load current I O ,∆I L =2•I O(min)∆I L =140mA for this circuit.∆I L can also be interpreted as ∆I L =2•(Discontinuity Factor)•I Lwhere the Discontinuity Factor is the ratio of the minimum load current to the maximum load current.For this example,the Discontinuity Factor is 0.2.The remainder of the components of Figure 15are chosen as follows:C1is the timing capacitor found in Figure 1.C2≥V o (V in −V o )/(8f osc 2V in V ripple L1)where V ripple is the peak-to-peak output voltage ripple.C3is necessary for continuous operation and is generally in the 10pF to 30pF range.D1should be a Schottky type diode,such as the 1N5818or 1N5819.BUCK WITH BOOSTED OUTPUT CURRENTFor applications requiring a large output current,an external transistor may be used as shown in Figure 17.This circuit steps a 15V supply down to 5V with 1.5A of output current.The output ripple is 50mV,with an efficiency of 80%,a load regulation of 40mV (150mA to 1.5A),and a line regulation of 20mV (12V ≤V in ≤18V).Component values are selected as outlined for the buck regulator with a discontinuity factor of 10%,with the addition of R4and R5:R4=10V BE1B f /I pR5=(V in −V −V BE1−V sat )B f /(I L(max,DC)+I R4)where:V BE1is the V BE of transistor Q1.V sat is the saturation voltage of the LM2578A output transis-tor.V is the current limit sense voltage.B f is the forced current gain of transistor Q1(B f =30for Figure 17).I R4=V BE1/R4I p =I L(max,DC)+0.5∆I LL M 2578A /L M 3578A 14Typical Applications(Continued)BOOST REGULATORThe boost regulator converts a low input voltage into a higher output voltage.The basic configuration is shown in Figure 18.Energy is stored in the inductor while the transis-tor is on and then transferred with the input voltage to the output capacitor for filtering when the transistor is off.Thus,V o =V in +V in (t on /t off ).The circuit of Figure 19converts a 5V supply into a 15V supply with 150mA of output current,a load regulation of 14mV (30mA to 140mA),and a line regulation of 35mV (4.5V ≤V in ≤8.5V).R1=(V o −1)R2where R2=10k Ω.R3=V/(I L(max,DC)+0.5∆I L )where:∆I L =2(I LOAD(min))(V o /V in )∆I L is 200mA in this example.R4,C3and C4are necessary for continuous operation and are typically 220k Ω,20pF,and 0.0022µF respectively.C1is the timing capacitor found in Figure 1.C2≥I o (V o −V in )/(f osc V o V ripple ).00871108V in =15V R4=200ΩV o =5V R5=330ΩV ripple =50mV C1=1820pF I o =1.5AC2=330µFf osc =50kHz C3=20pF R1=40k ΩL1=220µH R2=10k ΩD1=1N5819R3=0.05ΩQ1=D45FIGURE 17.Buck Converter with Boosted Output Current00871109FIGURE 18.Basic Boost Regulator00871111V in =5V R4=200k ΩV o =15V C1=1820pF V ripple =10mV C2=470µF I o =140mA C3=20pF f osc =50kHz C4=0.0022µF R1=140k ΩL1=330µH R2=10k ΩD1=1N5818R3=0.15ΩFIGURE 19.Boost or Step-Up RegulatorLM2578A/LM3578A15Typical Applications(Continued)D1is a Schottky type diode such as a 1N5818or 1N5819.L1is found as described in the buck converter section,using the inductance chart for Figure 16for the boost configuration and 20%discontinuity.INVERTING REGULATORFigure 20shows the basic configuration for an inverting regulator.The input voltage is of a positive polarity,but the output is negative.The output may be less than,equal to,or greater in magnitude than the input.The relationship be-tween the magnitude of the input voltage and the output voltage is V o =V in x (t on /t off ).Figure 21shows an LM2578A configured as a 5V to −15V polarity inverter with an output current of 300mA,a load regulation of 44mV (60mA to 300mA)and a line regulation of 50mV (4.5V ≤V in ≤8.5V).R1=(|V o |+1)R2where R2=10k Ω.R3=V/(I L(max,DC)+0.5∆I L ).R4=10V BE1B f /(I L (max,DC)+0.5∆I L )where:V,V BE1,V sat ,and B f are defined in the “Buck Converter with Boosted Output Current”section.∆I L =2(I LOAD(min))(V in +|V o |)/V INR5is defined in the “Buck with Boosted Output Current”section.R6serves the same purpose as R4in the Boost Regulator circuit and is typically 220k Ω.C1,C3and C4are defined in the “Boost Regulator”section.C2≥I o |V o |/[f osc (|V o |+V in )V ripple ]L1is found as outlined in the section on buck converters,using the inductance chart of Figure 16for the invert con-figuration and 20%discontinuity.BUCK-BOOST REGULATORThe Buck-Boost Regulator,shown in Figure 22,may step a voltage up or down,depending upon whether or not the desired output voltage is greater or less than the input voltage.In this case,the output voltage is 12V with an input voltage from 9V to 15V.The circuit exhibits an efficiency of 75%,with a load regulation of 60mV (10mA to 100mA)and a line regulation of 52mV.R1=(V o −1)R2where R2=10k ΩR3=V/0.75AR4,C1,C3and C4are defined in the “Boost Regulator”section.D1and D2are Schottky type diodes such as the 1N5818or 1N5819.where:V d is the forward voltage drop of the diodes.V sat is the saturation voltage of the LM2578A output transis-tor.V sat1is the saturation voltage of transistor Q1.L1≥(V in −V sat −V sat1)(t on /I p )00871110FIGURE 20.Basic Inverting Regulator00871112V in =5V R4=190ΩV o =−15V R5=82ΩV ripple =5mV R6=220k ΩI o =300mA C1=1820pF I min =60mAC2=1000µFf osc =50kHz C3=20pF R1=160k ΩC4=0.0022µF R2=10k ΩL1=150µH R3=0.01ΩD1=1N5818FIGURE 21.Inverting RegulatorL M 2578A /L M 3578A16。

AT89C52 中文资料

AT89S52 低功耗高性能CMOS 8 位单片机,片内8k Bytes ISP(In-system

programmable)的可反复擦写1000 次的FLASH 只读程序存储器,器件采用ATMEL 公司之高密度、非易失性存储技术制造,兼容标准MCS-51 指令系统及80C51 引脚结构,片上Flash 允许程序存储器在系统可编程,亦适于常规编程器。

单芯片上,拥有8 位CPU 及在系统可编程FLASH,使AT89S52 为众多嵌入式控制应用系统提供高灵活、超有效之解决方案。

AT89S52 之特点:40 个引脚,8k Bytes Flash 片内程序存储器,256 bytes

的随机存取数据存储器(RAM),32 个外部双向输入/输出(I/O)口,5 个中断优先级2 层中断嵌套中断,2 个16 位可编程定时计数器,2 个全双工串行通信口,看门狗(WDT)电路,片内时钟振荡器。

AT89C52 低电压高性能CMOS 8 位单片机,片内8k bytes 的可反复擦写的FLASH 只读程序存储器及256 bytes 的随机存取数据存储器(RAM),器件采用ATMEL 公司的高密度、非易失性存储技术生产,兼容标准MCS-51 指令

系统,片内置通用8 位中央处理器及FLASH 存储单元,功能强大之

AT89C52 单片机可为您提供许多较复杂系统控制之应用场合。

AT89C52 有40 个引脚,32 个外部双向输入/输出(I/O)端口,同时内含2 个。

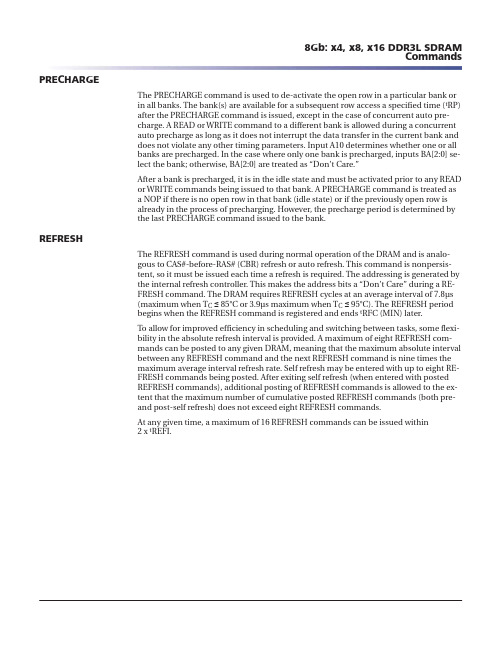

PRECHARGEThe PRECHARGE command is used to de-activate the open row in a particular bank orin all banks. The bank(s) are available for a subsequent row access a specified time (t RP)after the PRECHARGE command is issued, except in the case of concurrent auto pre-charge. A READ or WRITE command to a different bank is allowed during a concurrentauto precharge as long as it does not interrupt the data transfer in the current bank anddoes not violate any other timing parameters. Input A10 determines whether one or allbanks are precharged. In the case where only one bank is precharged, inputs BA[2:0] se-lect the bank; otherwise, BA[2:0] are treated as “Don’t Care.”After a bank is precharged, it is in the idle state and must be activated prior to any READor WRITE commands being issued to that bank. A PRECHARGE command is treated asa NOP if there is no open row in that bank (idle state) or if the previously open row isalready in the process of precharging. However, the precharge period is determined bythe last PRECHARGE command issued to the bank.REFRESHThe REFRESH command is used during normal operation of the DRAM and is analo-gous to CAS#-before-RAS# (CBR) refresh or auto refresh. This command is nonpersis-tent, so it must be issued each time a refresh is required. The addressing is generated bythe internal refresh controller. This makes the address bits a “Don’t Care” during a RE-FRESH command. The DRAM requires REFRESH cycles at an average interval of 7.8μs(maximum when T Cื 85°C or 3.9μs maximum when T Cื 95°C). The REFRESH periodbegins when the REFRESH command is registered and ends t RFC (MIN) later.To allow for improved efficiency in scheduling and switching between tasks, some flexi-bility in the absolute refresh interval is provided. A maximum of eight REFRESH com-mands can be posted to any given DRAM, meaning that the maximum absolute intervalbetween any REFRESH command and the next REFRESH command is nine times themaximum average interval refresh rate. Self refresh may be entered with up to eight RE-FRESH commands being posted. After exiting self refresh (when entered with postedREFRESH commands), additional posting of REFRESH commands is allowed to the ex-tent that the maximum number of cumulative posted REFRESH commands (both pre-and post-self refresh) does not exceed eight REFRESH commands.At any given time, a maximum of 16 REFRESH commands can be issued within2 x t REFI.Figure 38: Refresh ModeDon’t CareIndicates breakin time scale CK CK#Command CKE AddressA10BA[2:0]DQ 4DM 4DQS, DQS#4Notes: 1.NOP commands are shown for ease of illustration; other valid commands may be possi-ble at these times. CKE must be active during the PRECHARGE, ACTIVATE, and REFRESH commands, but may be inactive at other times (see Power-Down Mode (page 174)).2.The second REFRESH is not required, but two back-to-back REFRESH commands are shown.3.“Don’t Care” if A10 is HIGH at this point; however, A10 must be HIGH if more than one bank is active (must precharge all active banks).4.For operations shown, DM, DQ, and DQS signals are all “Don’t Care”/High-Z.5.Only NOP and DES commands are allowed after a REFRESH command and until t RFC (MIN) is satisfied.SELF REFRESHThe SELF REFRESH command is used to retain data in the DRAM, even if the rest of the system is powered down. When in self refresh mode, the DRAM retains data without ex-ternal clocking. Self refresh mode is also a convenient method used to enable/disable the DLL as well as to change the clock frequency within the allowed synchronous oper-ating range (see Input Clock Frequency Change (page 117)). All power supply inputs (including V REFCA and V REFDQ ) must be maintained at valid levels upon entry/exit and during self refresh mode operation. V REFDQ may float or not drive V DDQ /2 while in self refresh mode under the following conditions:•V SS < V REFDQ < V DD is maintained •V REFDQ is valid and stable prior to CKE going back HIGH •The first WRITE operation may not occur earlier than 512 clocks after V REFDQ is valid •All other self refresh mode exit timing requirements are met。

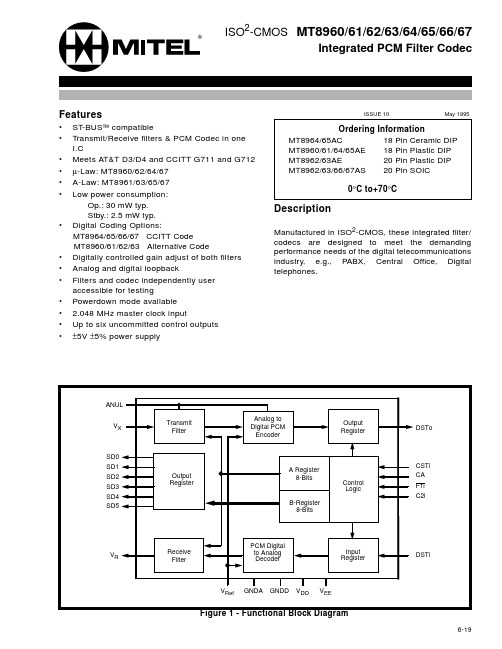

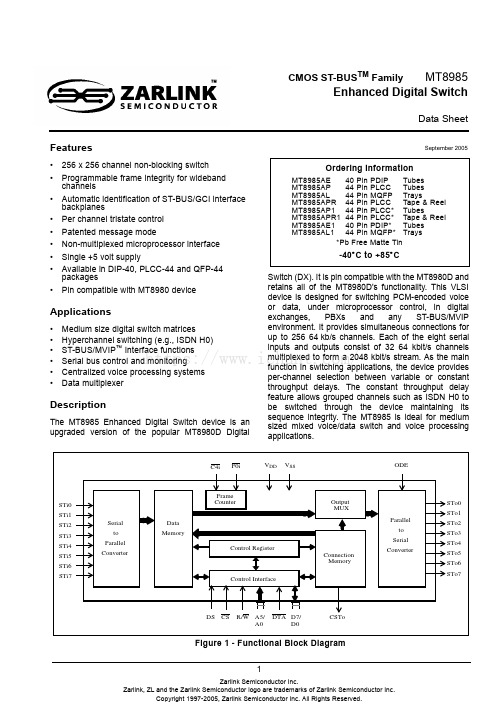

1Features•256 x 256 channel non-blocking switch •Programmable frame integrity for wideband channels•Automatic identification of ST-BUS/GCI interface backplanes•Per channel tristate control •Patented message mode•Non-multiplexed microprocessor interface •Single +5 volt supply•Available in DIP-40, PLCC-44 and QFP-44 packages•Pin compatible with MT8980 deviceApplications•Medium size digital switch matrices•Hyperchannel switching (e.g., ISDN H0)•ST-BUS/MVIP ™ interface functions •Serial bus control and monitoring•Centralized voice processing systems •Data multiplexerDescriptionThe MT8985 Enhanced Digital Switch device is an upgraded version of the popular MT8980D DigitalSwitch (DX). It is pin compatible with the MT8980D and retains all of the MT8980D's functionality. This VLSI device is designed for switching PCM-encoded voice or data, under microprocessor control, in digital exchanges, PBXs and any ST-BUS/MVIP environment. It provides simultaneous connections for up to 256 64kb/s channels. Each of the eight serial inputs and outputs consist of 32 64 kbit/s channels multiplexed to form a 2048 kbit/s stream. As the main function in switching applications, the device provides per-channel selection between variable or constant throughput delays. The constant throughput delay feature allows grouped channels such as ISDN H0 to be switched through the device maintaining its sequence integrity. The MT8985 is ideal for medium sized mixed voice/data switch and voice processing applications.September 2005Ordering InformationMT8985AE 40 Pin PDIP Tubes MT8985AP 44 Pin PLCC Tubes MT8985AL 44 Pin MQFP Trays MT8985APR 44 Pin PLCC Tape & Reel MT8985AP144 Pin PLCC*TubesMT8985APR144 Pin PLCC*Tape & Reel MT8985AE140 Pin PDIP*Tubes MT8985AL144 Pin MQFP*Trays*Pb Free Matte Tin-40°C to +85°CCMOS ST-BUS TM FamilyMT8985Enhanced Digital SwitchData SheetFigure 1 - Functional Block Diagramhttps:///MT8985Data SheetChanges SummaryThe following table captures the changes from the May 2005 issue.Figure 2 - Pin ConnectionsPage ItemChange7Figure 3 - “Address Memory Map“•corrected Address Memory MapDTA STi0STi1STi2STi3STi4STi5STi6STi7VDD F0i C4i A0A1A2A3A4A5DS CSTo ODE STo0STo1STo2STo3STo4STo5STo6STo7VSS D0D1D2D3D4D5D6D7CS1654324443424140789101112131415163938373635343332313023181920212224252627281729STi3STi4STi5STi6STi7VDD F0i C4i A0A1A2STo3STo4STo5STo6STo7VSS D0D1D2D3D4N C S T i 1D T A O D E S T o 1N CS T i 2S T i 0C S T o S T o 0S T o 2N C A 4D S C S D 6N CA 3A 5R /W D 740 PIN PLASTIC DIP44 PIN PLCC2345678910111213141516171819201R/W4039383736353433323130292827262524232221D 5394443424140383736353412345678910333231302928272625241712131415161819202122112344 PIN QFPSTi3STi4STi5STi6STi7VDD F0i C4i A0A1A2N C A 4D S C S D 6N CA 3A 5R /W D 7D 5STo3STo4STo5STo6STo7VSS D0D1D2D3D4N C S T i 1D T A O D E S T o 1N CS T i 2S T i 0C S T o S T o 0S T o 2https:///MT8985Data SheetPin DescriptionPin #Name Description40 DIP44PLCC 44QFP1240DTAData Acknowledgement (Open Drain Output). This active low output indicates that a data bus transfer is complete. A pull-up resistor is required at this output.2-93-57-1141-431-5STi0-STi7ST-BUS Input 0 to 7 (Inputs). Serial data input streams. These streams have 32 channels at data rates of 2.048 Mbit/s.10126V DD +5 Volt Power Supply rail.11137F0iFrame Pulse (Input): This input accepts and automatically identifies framesynchronization signals formatted according to different backplane specifications such as ST-BUS and GCI.12148C4iClock (Input). 4.096 MHz serial clock for shifting data in and out of the data streams.13-1815-1719-219-1113-15A0-A5Address 0 to 5 (Inputs). These lines provide the address to MT8985 internalregisters.192216DSData Strobe (Input). This is the input for the active high data strobe on themicroprocessor interface. This input operates with CS to enable the internal read and write generation.202317R/W Read/Write (Input). This input controls the direction of the data bus lines (D0-D7) during a microprocessor access. 212418CSChip Select (Input). Active low input enabling a microprocessor read or write ofcontrol register or internal memories.22-2925-2729-3319-2123-27D7-D0Data Bus 7 to 0 (Bidirectional). These pins provide microprocessor access to datain the internal control register, connect memory high, connect memory low and datamemory.303428V SSGround Rail.31-3835-3941-4329-3335-37STo7-STo0ST-BUS Outputs 7 to 0 (Three-state Outputs). Serial data output streams. Thesestreams are composed of 32 channels at data rates of 2.048 Mbit/s.394438ODE Output Drive Enable (Input). This is an output enable for the STo0 to STo7 serialoutputs. If this input is low STo0-7 are high impedance. If this input is high each channel may still be put into high impedance by software control.40139CSTo Control ST-BUS Output (Output). This output is a 2.048 Mb/s line which contains256 bits per frame. The level of each bit is controlled by the contents of the CSTo bit in the Connect Memory high locations.6, 18,28, 4012,2234,44NCNo Connection.https:///MT8985Data SheetFunctional DescriptionWith the integration of voice, video and data services into the same network, there has been an increasing demand for systems which ensure that data at N x 64 Kbit/s rates maintain frame sequence integrity while being transported through time slot interchange circuits. Existing requirements demand time slot interchange devices performing switching with constant throughput delay while guaranteeing minimum delay for voice channels.The MT8985 device provides both functions and allows existing systems based on the MT8980D to be easily upgraded to maintain the data integrity while multiple channel data are transported. The device is designed to switch 64 kbit/s PCM or N x 64 kbit/s data. The MT8985 can provide both frame integrity for data applications and minimum throughput switching delay for voice applications on a per channel basis.By using Zarlink Message mode capability, the microprocessor can access input and output time slots on a per channel basis to control devices such as the Zarlink MT8972, ISDN Transceivers and T1/CEPT trunk interfaces through the ST-BUS interface. Different digital backplanes can be accepted by the MT8985 device without user's intervention. The MT8985 device provides an internal circuit that automatically identifies the polarity and format of frame synchronization input signals compatible to ST-BUS and GCI interfaces.Device OperationA functional block diagram of the MT8985 device is shown in Figure 1. The serial ST-BUS streams operate continuously at 2.048 Mb/s and are arranged in 125 µs wide frames each containing 32 8-bit channels. Eight input (STi0-7) and eight output (STo0-7) serial streams are provided in the MT8985 device allowing a complete 256 x 256 channel non-blocking switch matrix to be constructed. The serial interface clock for the device is 4.096 MHz, as required in ST-BUS and GCI specifications.https:///Data MemoryThe received serial data is converted to parallel format by the on-chip serial to parallel converters and stored sequentially in a 256-position Data Memory. The sequential addressing of the Data Memory is generated by an internal counter that is reset by the input 8 kHz frame pulse (F0i) marking the frame boundaries of the incoming serial data streams.Depending on the type of information to be switched, the MT8985 device can be programmed to perform time slot interchange functions with different throughput delay capabilities on a per-channel basis. For voice applications, the variable delay mode can be selected ensuring minimum throughput delay between input and output data. In multiple or grouped channel data applications, the constant delay mode can be selected maintaining the integrity of the information through the switch.Data to be output on the serial streams may come from two sources: Data Memory or Connect Memory. Locations in the Connect Memory, which is split into HIGH and LOW parts, are associated with particular ST-BUS output streams. When a channel is due to be transmitted on an ST-BUS output, the data for the channel can either be switched from an ST-BUS input (connection mode) or it can be originated from the microprocessor (message mode). If a channel is configured in connection mode, the source of the output data is the Data Memory. If a channel is configured in message mode, the source of the output data is the Connect Memory Low. Data destined for a particular channel on the serial output stream is read from the Data or Connect Memory Low during the previous channel time slot. This allows enough time for memory access and internal parallel to serial conversion.Connection and Message ModesIn connection mode, the addresses of input source for all output channels are stored in the Connect memory Low. The Connect Memory Low locations are mapped to each location corresponding to an output 64 kb/s channel. The contents of the Data memory at the selected address are then transferred to the parallel to serial converters. By having the output channel to specify the input channel through the connect memory, the user can route the same input channel to several output channels, allowing broadcasting facility in the switch.MT8985Data SheetIn message mode the CPU writes data to the Connect Memory Low locations which correspond to the output link and channel number. The contents of the Connect Memory Low are transferred to the parallel to serial converter one channel before it is to be output. The Connect Memory Low data is transmitted each frame to the output until it is changed by the CPU.The per-channel functions available in the MT8985 are controlled by the Connect Memory High bits, which determine whether individual output channels are selected into specific conditions such as: message or connection mode, variable or constant throughput delay modes, output drivers enabled or in three-state condition. In addition, the Connect Memory High provides one bit to allow the user to control the state of the CSTo output pin.If an output channel is set to three-state condition, the TDM serial stream output will be placed in high impedance during that channel time. In addition to the per-channel three-state control, all channels on the TDM outputs can be placed in high impedance at one time by pulling the ODE input pin in LOW. This overrides the individual per-channel programming on the Connect Memory High bits.The Connect Memory data is received via the Microprocessor Interface at D0-D7 lines. The addressing of the MT8985 internal registers, Data and Connect memories is performed through address input pins and some bits of the device's Control register. The higher order address bits come from the Control register, which may be written or read through the microprocessor interface. The lower order address bits come directly from the external address line inputs. For details on the device addressing, see Software Control and Control register description.Serial Interface TimingThe MT8985 master clock (C4i) is a 4.096 MHz allowing serial data link configuration at 2.048 Mb/s to be implemented. The MT8985 frame synchronization pulse can be formatted according to ST-BUS or GCI interface specifications; i.e., the frame pulse can be active in HIGH (GCI) or LOW (ST-BUS). The MT8985 device https:///automatically detects the presence of an input frame pulse and identifies the type of backplane present on the serial interface. Upon determining the correct interface connected to the serial port, the internal timing unit establishes the appropriate serial data bit transmit and sampling edges. In ST-BUS mode, every second falling edge of the 4.096 MHz clock marks a bit boundary and the input data is clocked in by the rising edge, three quarters of the way into the bit cell. In GCI mode, every second rising edge of the 4.096 MHz clock marks the bit boundary while data sampling is performed during the falling edge, at three quarters of the bit boundaries.Delay through the MT8985The transfer of information from the input serial streams to the output serial streams results in a delay through the MT8985 device. The delay through the MT8985 device varies according to the mode selected in the V/C bit of the connect memory high.Variable Delay ModeThe delay in this mode is dependent only on the combination of source and destination channels and it is not dependent on the input and output streams. The minimum delay achievable in the MT8985 device is 3 time slots. In the MT8985 device, the information that is to be output in the same channel position as the information is input (position n), relative to frame pulse, will be output in the following frame (channel n, frame n+1). The same occurs if the input channel has to be output in the two channels succeeding (n+1 and n+2) the channel position as the information is input.The information switched to the third timeslot after the input has entered the device (for instance, input channel 0 to output channel 3 or input channel 30 to output channel 1), is always output three channels later.Any switching configuration that provides three or more timeslots between input and output channels, will have a throughput delay equal to the difference between the output and input channels; i.e., the throughput delay will be less than one frame. Table 1 shows the possible delays for the MT8985 device in Variable Delay mode:MT8985Data SheetConstant Delay ModeIn this mode frame integrity is maintained in all switching configurations by making use of a multiple Data-Memory buffer technique where input channels written in any of the buffers during frame N will be read out during frame N+2. In the MT8985, the minimum throughput delay achievable in Constant Delay mode will be 32 time slots; for example, when input time slot 32 (channel 31) is switched to output time slot 1 (channel 0). Likewise, the maximum delay is achieved when the first time slot in a frame (channel 0) is switched to the last time slot in the frame (channel 31), resulting in 94 time slots of delay.To summarize, any input time slot from input frame N will be always switched to the destination time slot on output frame N+2. In Constant Delay mode, the device throughput delay is calculated according to the following formula:DELAY = [32 + (32 - IN) + (OUT - 1)]; (expressed in number of time slots)Where:IN is the number of the input time slot (from 1 to 32).OUT is the number of the output time slot (from 1 to 32).Microprocessor PortThe MT8985 microprocessor port has pin compatibility with Zarlink MT8980 Digital Switch device providing a non-multiplexed bus architecture. The parallel port consists of an 8 bit parallel data bus (D0-D7), six address input lines (A0-A5) and four control lines (CS, DS, R/W and DTA). This parallel microport allows the access to the Control registers, Connection Memory High, Connection Memory Low and the Data Memory. All locations are read/written except for the data memory which can be read only.Accesses from the microport to the connection memory and the data memory are multiplexed with accesses from the input and output TDM ports. This can cause variable Data Acknowledge delays (DTA). In the MT8985 device,the DTA output provides a maximum acknowledgement delay of 800 ns for read/write operations in the Connection Memory. However, for operations in the Data Memory (Message Mode), the maximum acknowledgement delay can be 1220 ns.Input ChannelOutput Channel Throughput Delay n m=n, n+1 or n+2m-n + 32 timeslotsnm>n+2m-n time slotsn m<n 32-(n-m) time slotshttps:///MT8985Data SheetFigure 3 - Address Memory MapNote: "x" Don’t careSoftware ControlThe address lines on the microprocessor interface give access to the MT8985 internal registers and memories. If the A5,A1,A0 address line inputs are LOW, then the MT8985 Internal Control Register is addressed (see Figure 3).If A5 input line is HIGH, then the remaining address input lines are used to select Memory subsections of 32locations corresponding to the number of channels per input or output stream. As explained in the Control register description, the address input lines and the Stream Address bits (STA) of the Control register give the user the capability of selecting all positions of the MT8985 Data and Connect memories.The data in the Control register consists of Split memory and Message mode bits, Memory select and Stream Address bits (see Figure 4). The memory select bits allow the Connect Memory HIGH or LOW or the Data Memory to be chosen, and the Stream Address bits define an internal memory subsections corresponding to input or output ST-BUS streams. Bit 7 (Split Memory) of the Control register allows split memory operation whereby reads are from the Data memory and writes are to the Connect Memory LOW.The Message Enable bit (bit 6) places every output channel on every output stream in message mode; i.e., the contents of the Connect Memory LOW (CML) are output on the ST-BUS output streams once every frame unless the ODE input pin is LOW. If ME bit is HIGH, then the MT8985 behaves as if bits 2 (Message Channel) and 0(Output Enable) of every Connect Memory HIGH (CMH) locations were set to HIGH, regardless of the actual value.If ME bit is LOW, then bit 2 and 0 of each Connect Memory HIGH location operates normally. In this case, if bit 2 of the CMH is HIGH, the associated ST-BUS output channel is in Message mode. If bit 2 of the CMH is LOW, then the contents of the CML define the source information (stream and channel) of the time slot that is to be switched to an output.If the ODE input pin is LOW, then all serial outputs are high-impedance. If ODE is HIGH, then bit 0 (Output Enable)of the CMH location enables (if HIGH) or disables (if LOW) the output drivers for the corresponding individual ST-BUS output stream and channel.The contents of bit 1 (CSTo) of each Connection Memory High location (see Figure 5) is output on CSTo pin once every frame. The CSTo pin is a 2048 Mbit/s output which carries 256 bits. If CSTo bit is set HIGH, the corresponding bit on CSTo output is transmitted in HIGH. If CSTo bit is LOW, the corresponding bit on the CSTo output is transmitted in LOW. The contents of the 256 CSTo bits of the CMH are transmitted sequentially on to the CSTo output pin and are synchronous to the ST-BUS streams. To allow for delay in any external control circuitry the contents of the CSTo bit is output one channel before the corresponding channel on the ST-BUS streams. For example, the contents of CSTo bit in position 0 (ST0, CH0) of the CMH, is transmitted synchronously with ST-BUS channel 31, bit 7. The contents of CSTo bit in position 32 (ST1, CH0) of the CMH is transmitted during ST-BUS channel 31 bit 6. Bit V/C (Variable/Constant Delay) on the Connect Memory High locations allow per-channel selection between Variable and Constant throughput delay capabilities.A5A4A3A2A1A0LOCATION 011111111000•••••1000•••••1000•••••1000•••••1001•••••1Control Register Channel 0Channel 1•••••Channel 31https:///MT8985Data SheetFigure 4 - Control Register Bitsx = Don’t careInitialization of the MT8985On initialization or power up, the contents of the Connection Memory High can be in any state. This is a potentially hazardous condition when multiple MT8985 ST-BUS outputs are tied together to form matrices, as these outputs may conflict. The ODE pin should be held low on power up to keep all outputs in the high impedance condition.BIT NAME DESCRIPTION7SM Split Memory. When 1, all subsequent reads are from the Data Memory and writes are to theConnection Memory Low, except when the Control Register is accessed again. The Memory Select bits need to be set to specify the memory for the operations. When 0, the Memory Select bits specify the memory for subsequent operations. In either case, the Stream Address Bits select the subsection of the memory which is made available.6MEMessage Enable. When 1, the contents of the Connection Memory Low are output on the Serial Output streams except when in High Impedance. When 0, the Connection Memory bits for each channel determine what is output.4-3MS1-MS0Memory Select Bits. The memory select bits operate as follows:0-0 - Not to be used0-1 - Data Memory (read only from the CPU)1-0 - Connection Memory Low 1-1 - Connection Memory High2-0STA2-0Stream Address Bits 2-0. The number expressed in binary notation on these bits refers to the input or output ST-BUS stream which corresponds to the subsection of memory made accessible for subsequent operations.SMMEXMS1MS0STA2STA1STA076543210https:///MT8985Data SheetFigure 5 - Connection Memory High Bitsx = Don’t careFigure 6 - Connection Memory Low BitsDuring the microprocessor initialization routine, the microprocessor should program the desired active paths through the matrices, and put all other channels into the high impedance state. Care should be taken that no two connected ST-BUS outputs drive the bus simultaneously. When this process is complete, the microprocessor controlling the matrices can bring the ODE signal high to relinquish high impedance state control to the CMH b 0s.BIT NAME DESCRIPTION6V/C Variable/Constant Throughput Delay Mode. This bit is used to select between Variable (LOW) and Constant Delay (HIGH) modes on a per-channel basis.2MCMessage Channel. When 1, the contents of the corresponding location in Connection Memory Low are output on the corresponding channel and stream. When 0, the contents of the programmed location in Connection Memory Low act as an address for the Data Memory and so determine the source of the connection to the location’s channel and stream.1CSTo CSTo Bit. This bit drives a bit time on the CSTo output pin.OEOutput Enable. This bit enables the output drivers on a per-channel basis. This allows individual channels on individual streams to be made high-impedance, allowing switch matrices to be constructed. A HIGH enables the driver and a LOW disables it.BIT NAME DESCRIPTION7-5SAB2-0*Source Stream Address bits. These three bits are used to select eight source streams for the connection. Bit 7 of each word is the most significant bit.4-0*CAB4-0*Source Channel Address bits 0-4. These five bits are used to select 32 different source channels for the connection (The ST-BUS stream where the channel is present is defined by bits SAB2-0). Bit 4 is the most significant bit.*If bit 2 of the corresponding Connection High location is 1 or if bit 6 of the Control Register is 1, then these entire 8 bits are output on the channel and stream associated with this location. Otherwise, the bits are used as indicated to define the source of the connection which is output on the channel and stream associated with this location.XV/CXXXMCCSToOE76543210SAB2SAB1SAB0CAB4CAB3CAB2CAB1CAB07654321https:///MT8985Data Sheet ApplicationsTypical Exchange, PBX or MultiplexerFigure 7 shows a typical implementation of line cards being interconnected through a central routing matrix that can scale up in channel capacity to accommodate different number of ports depending on the application. In a configuration where the switched services utilize concatenated or grouped time slots to carry voice, data and video (channels of 128, 256 Kb/s, ISDN H0 and others), the central routing matrix has to guarantee constant throughput delay to maintain the sequence integrity between input and output channels. Figure 7 shows an example where the MT8985 device guarantees data integrity when data flows from the T1/E1 to the S/U interface links and vice-versa. Modern technologies available today such as Frame Relay network using dedicated fractional T1 are one of the key applications for the MT8985 device.Figure 7 - Typical Exchange, PBX or Multiplexer ConfigurationMT8985Data SheetLow Latency Isochronous NetworkIn today's local working group environment, there is an increasing demand for solutions on interconnection of desktop and telephone systems so that mixed voice, data and video services can be grouped together in a reliable https:///network allowing the deployment of multimedia services. Existing multimedia applications require a network with predictable data transfer delays that can be implemented at a reasonable cost. The Low Latency Isochronous Network is one of the alternatives that system designers have chosen to accommodate this requirement (see Figure 8a). This network can be implemented using existing TDM transmission media devices such as ISDN Basic (S or U) and Primary rates trunks (T1 and CEPT) to transport mixed voice and data signals in grouped time slots; for example, 2B channels in case of ISDN S or U interfaces or up to 32 channels in case of a CEPT link.Figure 8b shows a more detailed configuration whereby several PCs are connected to form an Isochronous network. Several services can be interconnected within a single PC chassis through the standardized Multi Vendor Integration Protocol (MVIP). Such an interface allows the distribution and interconnection of services like voice mail, integrated voice response, voice recognition, LAN gateways, key systems, fax servers, video cards, etc.The information being exchanged between cards through the MVIP interface on every computer as well as between computers through T1 or CEPT links is, in general, of mixed type where 64Kb/s and N*64Kb/s channels are grouped together. When such a mixed type of data is transferred between cards within one chassis or from one computer to another, the sequence integrity of the concatenated channels has to be maintained. The MT8985 device suits this application and can be used to form a complete non-blocking switch matrix of 512 channels (see Figure 9). This allows 8 pairs of ST-BUS streams to be dedicated to the MVIP side whereas the remaining 8 pairs are used for local ancillary functions in typical dual T1/E1 interface applications (Figure 10).Another application of the MT8985 in an MVIP environment is to build an ISDN S-interface card (Figure 11). In this card, 7 pairs of ST-BUS streams are connected to the MVIP interface while the remaining pair is reserved for the interconnection of Zarlink MT8930 (SNIC), MT8992 (H-PHONE) and the MVIP interface.MT8985Data Sheet To Video, Data,MT8985Data SheetFigure 9 - 512-Channel Switch Array8 Input Streams From MVIP8 Input On-Board ST-BUS Streams8 Output Streams to MVIP8 Output On-Board ST-BUS StreamsMVIP DirectionMVIP EnableMT8985 #1CSToMT8985 #2CSToMT8985#3MT8985#4https:///MT8985Data SheetFigure 10 - Dual T1/E1 Card Functional Block DiagramFDL HDLC MT8952B T1/E1MH89760Bor MH89790B HDLC MT8952BANALOG D-PHONE MT8992/93SWITCH MT8985SWITCH MT8985SWITCH MT8985SWITCH MT8985DPLL MT8941PC INTERFACEMVIP HEADERMVIP STo0-7MVIP STi0-7FDL HDLC MT8952BT1/E1MH89760Bor MH89790B HDLC MT8952B512 Channel Switch Matrixhttps:///MT8985Data SheetFigure 11 - S-Access Card Functional Block DiagramMVIP HEADERSWITCH MATRIX SINTERFACEHDLCDIGITAL PHONEDPLL DTMF RECEIVER PC INTERFACEHDLCSTi7-1STo7-1STi0STo0MT8930BMT8941MT8992/93MT8870MVIP STi1-7MVIP STo1-7MT8985https:///。

AT89S51概述1 一般概述该AT89S51是一个低功耗,高性能CMOS 8位微控制器,可在4K字节的系统内编程的闪存存储器。

该设备是采用Atmel的高密度非易失性存储器技术和符合工业标准的80C51指令集和引脚。

芯片上的Flash程序存储器可重新编程的系统或常规非易失性内存编程。

通过结合通用8位中央处理器的系统内可编程闪存的单芯片,AT89S51是一个功能强大的微控制器提供了高度灵活的和具有成本效益的解决办法,可在许多嵌入式控制中应用。

在AT89S51提供以下标准功能:4K字节的Flash闪存,128字节的RAM ,32个I / O线,看门狗定时器,两个数据指针,两个16位定时器/计数器,5向量两级中断结构,全双工串行端口,片上振荡器和时钟电路。

此外,AT89S51设计的静态逻辑操作到零频率和支持两种软件可选节电模式。

空闲模式停止的CPU ,同时允许的RAM ,定时器/计数器,串行接口和中断系统继续运作。

在掉电模式保存RAM内容,可停止振荡器,停用所有其他芯片的功能,直到下一个外部中断或硬件复位。

2 端口端口0是一个8位漏极开路双向I / O端口。

作为一个输出端口,每个引脚可汇8的TTL 输入。

当1写入端口0引脚,该引脚可作为高阻抗输入。

端口0也可以配置为复低阶地址/数据总线,在访问外部程序和数据存储器。

在这种模式下,P0了内部无上拉。

端口还收到0字节的代码在Flash编程和产出代码波特率的核查。

外部上拉需要在使用。

端口1是一个8位双向I / O端口内部上拉。

端口1输出缓冲器可以驱动四个TTL。

当1写入端口1引脚,他们的退出高足态上拉,可作为输入。

作为输入,端口1引脚的外部被拉低将电源电流(IIL )由于内部上拉。

端口1还收到低字节为了解决在Flash编程和核查。

端口2是一个8位双向I / O端口内部上拉。

端口2输出缓冲器可以驱动四的TTL输入。

当1写入端口2,他们的退出高阻态上拉,可作为输入。