MEMORY存储芯片PTVS3V3S1UTR中文规格书

- 格式:pdf

- 大小:140.93 KB

- 文档页数:4

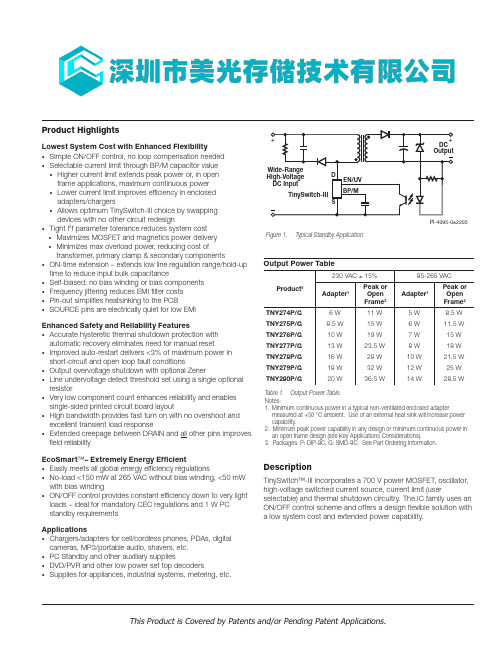

This Product is Covered by Patents and/or Pending Patent Applications.Output Power TableProduct 3230 VAC ± 15%85-265 VAC Adapter 1Peak or Open Frame 2Adapter 1Peak or Open Frame 2TNY274P/G 6 W 11 W 5 W 8.5 W TNY275P/G 8.5 W 15 W 6 W 11.5 W TNY276P/G 10 W 19 W 7 W 15 W TNY277P/G 13 W 23.5 W 8 W 18 W TNY278P/G 16 W 28 W 10 W 21.5 W TNY279P/G 18 W 32 W 12 W 25 W TNY280P/G20 W36.5 W14 W28.5 WTable 1. Output Power Table. Notes:1.Minimum continuous power in a typical non-ventilated enclosed adaptermeasured at +50 °C ambient. Use of an external heat sink will increase power capability.2.Minimum peak power capability in any design or minimum continuous power in an open frame design (see Key Applications Considerations).3.Packages: P: DIP-8C, G: SMD-8C. See Part Ordering Information.Product HighlightsLowest System Cost with Enhanced Flexibility•Simple ON/OFF control, no loop compensation needed •Selectable current limit through BP/M capacitor value • Higher current limit extends peak power or, in open frame applications, maximum continuous power •Lower current limit improves efficiency in enclosed adapters/chargers•Allows optimum TinySwitch-III choice by swapping devices with no other circuit redesign•Tight I 2f parameter tolerance reduces system cost •Maximizes MOSFET and magnetics power delivery •Minimizes max overload power, reducing cost oftransformer, primary clamp & secondary components•ON-time extension – extends low line regulation range/hold-up time to reduce input bulk capacitance•Self-biased: no bias winding or bias components •Frequency jittering reduces EMI filter costs •Pin-out simplifies heatsinking to the PCB•SOURCE pins are electrically quiet for low EMIEnhanced Safety and Reliability Features•Accurate hysteretic thermal shutdown protection with automatic recovery eliminates need for manual reset•Improved auto-restart delivers <3% of maximum power in short-circuit and open loop fault conditions•Output overvoltage shutdown with optional Zener•Line undervoltage detect threshold set using a single optional resistor•Very low component count enhances reliability and enables single-sided printed circuit board layout•High bandwidth provides fast turn on with no overshoot and excellent transient load response•Extended creepage between DRAIN and all other pins improves field reliability EcoSmart ™– Extremely Energy Efficient•Easily meets all global energy efficiency regulations•No-load <150 mW at 265 VAC without bias winding, <50 mW with bias winding•ON/OFF control provides constant efficiency down to very light loads – ideal for mandatory CEC regulations and 1 W PC standby requirements Applications•Chargers/adapters for cell/cordless phones, PDAs, digital cameras, MP3/portable audio, shavers, etc.•PC Standby and other auxiliary supplies•DVD/PVR and other low power set top decoders•Supplies for appliances, industrial systems, metering, etc.DescriptionTinySwitch™-III incorporates a 700 V power MOSFET, oscillator, high-voltage switched current source, current limit (userselectable) and thermal shutdown circuitry. The IC family uses an ON/OFF control scheme and offers a design flexible solution with a low system cost and extended power capability.Figure 1. Typical Standby Application.PI-4095-082205Wide-Range High-Voltage DC InputDSEN/UV BP/MDC OutputTinySwitch-III++TNY274-280Pin Functional DescriptionDRAIN (D) Pin:This pin is the power MOSFET drain connection. It provides internal operating current for both start-up and steady-state operation.BYPASS/MULTI-FUNCTION (BP/M) Pin:This pin has multiple functions:1.It is the connection point for an external bypass capacitor forthe internally generated 5.85 V supply.2.It is a mode selector for the current limit value, depending onthe value of the capacitance added. Use of a 0.1 m Fcapacitor results in the standard current limit value. Use of a 1 m F capacitor results in the current limit being reduced to that of the next smaller device size. Use of a 10 m F capacitor results in the current limit being increased to that of the next larger device size for TNY275-280.3.It provides a shutdown function. When the current into thebypass pin exceeds I SD , the device latches off until theBP/M voltage drops below 4.9 V , during a power down. This can be used to provide an output overvoltage function with a Zener connected from the BP/M pin to a bias winding supply.ENABLE/UNDERVOLTAGE (EN/UV) Pin:This pin has dual functions: enable input and line undervoltage sense. During normal operation, switching of the power MOSFET is controlled by this pin. MOSFET switching isterminated when a current greater than a threshold current is drawn from this pin. Switching resumes when the current beingFigure 2. Functional Block Diagram.PI-4077-072115CLOCKOSCILLATOR5.85 V 4.9 V SOURCE(S)SR QDC MAX BYPASS/MULTI-FUNCTION(BP/M)+-V ILIMITFAULT PRESENTCURRENT LIMIT COMPARATORENABLELEADING EDGE BLANKINGTHERMAL SHUTDOWN+-DRAIN (D)REGULATOR5.85 VBYPASS PINUNDER-VOLTAGE1.0 V + V TENABLE/UNDER-VOLTAGE (EN/UV)Q115 µA25 µALINE UNDER-VOLTAGERESETAUTO-RESTART COUNTERJITTER 1.0 V6.4 VBYPASSCAPACITORSELECT ANDCURRENTLIMIT STATE MACHINEOVP LATCHFigure 3. Pin Configuration.PI-4078-080905D SBP/MS S EN/UV P Package (DIP-8C)G Package (SMD-8C)857142S 6TNY274-280pulled from the pin drops to less than a threshold current. A modulation of the threshold current reduces group pulsing. The threshold current is between 75 m A and 115 m A.The EN/UV pin also senses line undervoltage conditions through an external resistor connected to the DC line voltage. If there is no external resistor connected to this pin, TinySwitch-III detects its absence and disables the line undervoltage function.SOURCE (S) Pin:This pin is internally connected to the output MOSFET source for high-voltage power return and control circuit common.TinySwitch-III Functional DescriptionTinySwitch-III combines a high-voltage power MOSFET switch with a power supply controller in one device. Unlike conventional PWM (pulse width modulator) controllers, it uses a simple ON/OFF control to regulate the output voltage.The controller consists of an oscillator, enable circuit (sense and logic), current limit state machine, 5.85 V regulator, BYPASS/MULTI-FUNCTION pin undervoltage, overvoltage circuit, and current limit selection circuitry, over-temperature protection, current limit circuit, leading edge blanking, and a 700 V power MOSFET. TinySwitch-III incorporates additional circuitry for line undervoltage sense, auto-restart, adaptive switching cycle on-time extension, and frequency jitter. Figure 2 shows the functional block diagram with the most important features.OscillatorThe typical oscillator frequency is internally set to an average of 132 kHz. Two signals are generated from the oscillator: the maximum duty cycle signal (DC MAX ) and the clock signal that indicates the beginning of each cycle.The oscillator incorporates circuitry that introduces a small amount of frequency jitter, typically 8 kHz peak-to-peak, to minimize EMI emission. The modulation rate of the frequency jitter is set to 1 kHz to optimize EMI reduction for both average and quasi-peak emissions. The frequency jitter should bemeasured with the oscilloscope triggered at the falling edge of the DRAIN waveform. The waveform in Figure 4 illustrates the frequency jitter.Enable Input and Current Limit State MachineThe enable input circuit at the EN/UV pin consists of a low impedance source follower output set at 1.2 V. The current through the source follower is limited to 115 m A. When thecurrent out of this pin exceeds the threshold current, a low logic level (disable) is generated at the output of the enable circuit, until the current out of this pin is reduced to less than the threshold current. This enable circuit output is sampled at the beginning of each cycle on the rising edge of the clock signal. If high, the power MOSFET is turned on for that cycle (enabled). If low, the power MOSFET remains off (disabled). Since thesampling is done only at the beginning of each cycle, subsequent changes in the EN/UV pin voltage or current during the remainder of the cycle are ignored.The current limit state machine reduces the current limit by discrete amounts at light loads when TinySwitch-III is likely to switch in the audible frequency range. The lower current limit raises the effective switching frequency above the audio range and reduces the transformer flux density, including the associated audible noise. The state machine monitors thesequence of enable events to determine the load condition and adjusts the current limit level accordingly in discrete amounts.Under most operating conditions (except when close to no-load), the low impedance of the source follower keeps the voltage on the EN/UV pin from going much below 1.2 V in the disabled state. This improves the response time of the optocoupler that is usually connected to this pin.5.85 V Regulator and6.4 V Shunt Voltage ClampThe 5.85 V regulator charges the bypass capacitor connected to the BYPASS pin to 5.85 V by drawing a current from the voltage on the DRAIN pin whenever the MOSFET is off. The BYPASS/MULTI-FUNCTION pin is the internal supply voltage node. When the MOSFET is on, the device operates from the energy stored in the bypass capacitor. Extremely low power consumption of the internal circuitry allows TinySwitch-III to operate continuously from current it takes from the DRAIN pin. A bypass capacitor value of 0.1 m F is sufficient for both high frequency decoupling and energy storage.In addition, there is a 6.4 V shunt regulator clamping the BYPASS/MULTI-FUNCTION pin at 6.4 V when current is provided to the BYPASS/MULTI-FUNCTION pin through an external resistor. This facilitates powering of TinySwitch-III externally through a bias winding to decrease the no-load consumption to well below 50 mW.BYPASS/MULTI-FUNCTION Pin UndervoltageThe BYPASS/MULTI-FUNCTION pin undervoltage circuitry disables the power MOSFET when the BYPASS/MULTI-FUNCTION pin voltage drops below 4.9 V in steady state operation. Once the BYPASS/MULTI-FUNCTION pin voltage drops below 4.9 V in steady state operation, it must rise back to 5.85 V to enable (turn-on) the power MOSFET.Figure 4. Frequency Jitter.6000510136 kHz 128 kHzV DRAINTime (µs)P I -2741-04190150040030020010004TNY274-280Over Temperature ProtectionThe thermal shutdown circuitry senses the die temperature. The threshold is typically set at 142 °C with 75 °C hysteresis. When the die temperature rises above this threshold the power MOSFET is disabled and remains disabled until the dietemperature falls by 75 °C, at which point it is re-enabled. A large hysteresis of 75 °C (typical) is provided to prevent over-heating of the PC board due to a continuous fault condition.Current LimitThe current limit circuit senses the current in the power MOSFET. When this current exceeds the internal threshold(I LIMIT ), the power MOSFET is turned off for the remainder of that cycle. The current limit state machine reduces the current limit threshold by discrete amounts under medium and light loads.The leading edge blanking circuit inhibits the current limit comparator for a short time (t LEB ) after the power MOSFET is turned on. This leading edge blanking time has been set so that current spikes caused by capacitance and secondary-side rectifier reverse recovery time will not cause premature termination of the switching pulse.Auto-RestartIn the event of a fault condition such as output overload, output short-circuit, or an open loop condition, TinySwitch-III enters into auto-restart operation. An internal counter clocked by the oscillator is reset every time the EN/UV pin is pulled low. If the EN/UV pin is not pulled low for 64 ms, the power MOSFET switching is normally disabled for 2.5 seconds (except in the case of line undervoltage condition, in which case it is disabled until the condition is removed). The auto-restart alternately enables and disables the switching of the power MOSFET until the fault condition is removed. Figure 5 illustrates auto-restart circuit operation in the presence of an output short-circuit.In the event of a line undervoltage condition, the switching of the power MOSFET is disabled beyond its normal 2.5 seconds until the line undervoltage condition ends.Adaptive Switching Cycle On-Time ExtensionAdaptive switching cycle on-time extension keeps the cycle on until current limit is reached, instead of prematurely terminating after the DC MAX signal goes low. This feature reduces theminimum input voltage required to maintain regulation, extending hold-up time and minimizing the size of bulk capacitor required. The on-time extension is disabled during the start-up of the power supply, until the power supply output reaches regulation.Line Undervoltage Sense CircuitThe DC line voltage can be monitored by connecting an external resistor from the DC line to the EN/UV pin. During power up or when the switching of the power MOSFET is disabled in auto-restart, the current into the EN/UV pin must exceed 25 m A to initiate switching of the power MOSFET. During power up, this is accomplished by holding the BYPASS/MULTI-FUNCTION pin to 4.9 V while the line undervoltage condition exists. The BYPASS/MULTI-FUNCTION pin then rises from 4.9 V to 5.85 V when the line undervoltage condition goesaway. When the switching of the power MOSFET is disabled in auto-restart mode and a line undervoltage condition exists, the auto-restart counter is stopped. This stretches the disable time beyond its normal 2.5 seconds until the line undervoltage condition ends.The line undervoltage circuit also detects when there is no external resistor connected to the EN/UV pin (less than ~2 m A into the pin). In this case the line undervoltage function is disabled.TinySwitch-III OperationTinySwitch-III devices operate in the current limit mode. When enabled, the oscillator turns the power MOSFET on at the beginning of each cycle. The MOSFET is turned off when the current ramps up to the current limit or when the DC MAX limit is reached. Since the highest current limit level and frequency of a TinySwitch-III design are constant, the power delivered to the load is proportional to the primary inductance of the transformer and peak primary current squared. Hence, designing the supply involves calculating the primary inductance of the transformer for the maximum output power required. If the TinySwitch-III is appropriately chosen for the power level, the current in the calculated inductance will ramp up to current limit before the DC MAX limit is reached.Enable FunctionTinySwitch-III senses the EN/UV pin to determine whether or not to proceed with the next switching cycle. The sequence of cycles is used to determine the current limit. Once a cycle is started, it always completes the cycle (even when the EN/UV pin changes state half way through the cycle). This operation results in a power supply in which the output voltage ripple is determined by the output capacitor, amount of energy per switch cycle and the delay of the feedback.The EN/UV pin signal is generated on the secondary bycomparing the power supply output voltage with a reference voltage. The EN/UV pin signal is high when the power supply output voltage is less than the reference voltage.Figure 5. Auto-Restart Operation.P I -4098-08230525005000Time (ms)5010100200300VDRAINVDC-OUTPUTTNY274-280In a typical implementation, the EN/UV pin is driven by an optocoupler. The collector of the optocoupler transistor is connected to the EN/UV pin and the emitter is connected to the SOURCE pin. The optocoupler LED is connected in series with a Zener diode across the DC output voltage to be regulated. When the output voltage exceeds the target regulation voltage level (optocoupler LED voltage drop plus Zener voltage), the optocoupler LED will start to conduct, pulling the EN/UV pin low. The Zener diode can be replaced by a TL431 reference circuit for improved accuracy.ON/OFF Operation with Current Limit State MachineThe internal clock of the TinySwitch-III runs all the time. At the beginning of each clock cycle, it samples the EN/UV pin to decide whether or not to implement a switch cycle, and based on the sequence of samples over multiple cycles, it determines the appropriate current limit. At high loads, the state machine sets the current limit to its highest value. At lighter loads, thestate machine sets the current limit to reduced values.。

PLL Controllers7.2.2.2Initializing PLL Mode from PLL Power DownIf the PLL is powered down(PLLPWRDN bit in PLLCTL is set to1),perform the following procedure to initialize the PLL:1.Program the CLKMODE bit in PLLC0PLLCTL.2.Switch the PLL to bypass mode:(a)Clear the PLLENSRC bit in PLLCTL to0(allows PLLEN bit to take effect).(b)For PLL0only,select the clock source by programming the EXTCLKSRC bit in PLLCTL.(c)Clear the PLLEN bit in PLLCTL to0(PLL in bypass mode).(d)Wait for4OSCIN cycles to ensure that the PLLC has switched to bypass mode.3.Clear the PLLRST bit in PLLCTL to0(resets PLL).4.Clear the PLLPWRDN bit in PLLCTL to0(brings PLL out of power-down mode).5.Program the desired multiplier value in PLLM.Program the POSTDIV,as needed.6.If desired,program PLLDIV n registers to change the SYSCLK n divide values:(a)Wait for the GOSTAT bit in PLLSTAT to clear to0(indicates that no operation is currently inprogress).(b)Program the RATIO field in PLLDIV n.(c)Set the GOSET bit in PLLCMD to1(initiates a new divider transition).(d)Wait for the GOSTAT bit in PLLSTAT to clear to0(completion of divider change).7.Set the PLLRST bit in PLLCTL to1(brings PLL out of reset).8.Wait for the PLL to lock.See the device-specific data manual for PLL lock time.9.Set the PLLEN bit in PLLCTL to1(removes PLL from bypass mode).7.2.2.3Changing PLL MultiplierIf the PLL is not powered down(PLLPWRDN bit in PLLCTL is cleared to0),perform the followingprocedure to change the PLL multiplier:1.Switch the PLL to bypass mode:(a)Clear the PLLENSRC bit in PLLCTL to0(allows PLLEN bit to take effect).(b)For PLL0only,select the clock source by programming the EXTCLKSRC bit in PLLCTL.(c)Clear the PLLEN bit in PLLCTL to0(PLL in bypass mode).(d)Wait for4OSCIN cycles to ensure that the PLLC has switched to bypass mode.2.Clear the PLLRST bit in PLLCTL to0(resets PLL).3.Program the desired multiplier value in PLLM.Program the POSTDIV,as needed.4.If desired,program PLLDIV n registers to change the SYSCLK n divide values:(a)Wait for the GOSTAT bit in PLLSTAT to clear to0(indicates that no operation is currently inprogress).(b)Program the RATIO field in PLLDIV n.(c)Set the GOSET bit in PLLCMD to1(initiates a new divider transition).(d)Wait for the GOSTAT bit in PLLSTAT to clear to0(completion of divider change).5.Set the PLLRST bit in PLLCTL to1(brings PLL out of reset).6.Wait for the PLL to lock.See the device-specific data manual for PLL lock time.7.Set the PLLEN bit in PLLCTL to1(removes PLL from bypass mode).Peripheral Clocking6.3.4EMAC ClockingThe EMAC module sources its peripheral bus interface reference clock from PLL0_SYSCLK4that is at a fixed ratio of the CPU clock.The external clock requirement for EMAC varies with the interface used.When the MII interface is active,the MII_TXCLK and MII_RXCLK signals must be provided from anexternal source.When the RMII interface is active,the RMII50MHz reference clock is sourced either from an external clock on the RMII_MHZ_50_CLK pin or from PLL0_SYSCLK7(as shown in Figure6-5).The PINMUX15_3_0bits in the pin multiplexing control15register(PINMUX15)of the SystemConfiguration Module control this clock selection:•PINMUX15_3_0=0:enables sourcing of the50MHz reference clock from an external source on the RMII_MHZ_50_CLK pin.•PINMUX15_3_0=8h:enables sourcing of the50MHz reference clock from PLL0_SYSCLK7.Also, PLL0_SYSCLK7is driven out on the RMII_MHZ_50_CLK pin.Table6-7shows example PLL register settings and the resulting PLL0_SYSCLK7frequencies based on the OSCIN reference clock frequency of25MHz.Figure6-5.EMAC Clocking DiagramRMII_MHZ_50_CLKSignalNOTE:The SYSCLK7output clock does not meet the RMII reference clock specification of50MHz+/-50ppm.。

6.5Write ProtectionApplications that use non-volatile memory must take into consideration the possibility of noise and other adverse system conditions that may compromise data integrity. To address this concern, the W25Q32JV provides several means to protect the data from inadvertent writes.Write Protect Features∙Device resets when VCC is below threshold∙Time delay write disable after Power-up∙Write enable/disable instructions and automatic write disable after erase or program∙Software and Hardware (/WP pin) write protection using Status Registers∙Additional Individual Block/Sector Locks for array protection∙Write Protection using Power-down instruction∙Lock Down write protection for Status Register until the next power-up∙One Time Program (OTP) write protection for array and Security Registers using Status Register* *Note:This feature is available upon special order. Please contact Winbond for details.Upon power-up or at power-down, the W25Q32JV will maintain a reset condition while VCC is below the threshold value of V WI, (See Power-up Timing and Voltage Levels and Figure 43). While reset, all operations are disabled and no instructions are recognized. During power-up and after the VCC voltage exceeds V WI, all program and erase related instructions are further disabled for a time delay of t PUW. This includes the Write Enable, Page Program, Sector Erase, Block Erase, Chip Erase and the Write Status Register instructions. Note that the chip select pin (/CS) must track the VCC supply level at power-up until the VCC-min level and t VSL time delay is reached, and it must also track the VCC supply level at power-down to prevent adverse command sequence. If needed a pull-up resister on /CS can be used to accomplish this.After power-up the device is automatically placed in a write-disabled state with the Status Register Write Enable Latch (WEL) set to a 0. A Write Enable instruction must be issued before a Page Program, Sector Erase, Block Erase, Chip Erase or Write Status Register instruction will be accepted. After completing a program, erase or write instruction the Write Enable Latch (WEL) is automatically cleared to a write-disabled state of 0.Software controlled write protection is facilitated using the Write Status Register instruction and setting the Status Register Protect (SRP, SRL) and Block Protect (CMP, TB, BP[2:0]) bits. These settings allow a portion or the entire memory array to be configured as read only. Used in conjunction with the Write Protect (/WP) pin, changes to the Status Register can be enabled or disabled under hardware control. See Status Register section for further information. Additionally, the Power-down instruction offers an extra level of write protection as all instructions are ignored except for the Release Power-down instruction.The W25Q32JV also provides another Write Protect method using the Individual Block Locks. Each 64KB block (except the top and bottom blocks, total of 62 blocks) and each 4KB sector within the top/bottom blocks (total of 32 sectors) are equipped with an Individual Block Lock bit. When the lock bit is 0, the corresponding sector or block can be erased or programmed; when the lock bit is set to 1, Erase or Program commands issued to the corresponding sector or block will be ignored. When the device is powered on, all Individual Block Lock bits will be 1, so the entire memory array is protected from Erase/Program. An “Individual Block Unlock (39h)” instruction must be issued to unlock any specific sector or block.The WPS bit in Status Register-3 is used to decide which Write Protect scheme should be used. When WPS=0 (factory default), the device will only utilize CMP, SEC, TB, BP[2:0] bits to protect specific areas of the array; when WPS=1, the device will utilize the Individual Block Locks for write protection.Figure 4c. Status Register-3Write Protect Selection (WPS) –Volatile/Non-Volatile WritableThe WPS bit is used to select which Write Protect scheme should be used. When WPS=0, the device will use the combination of CMP, SEC, TB, BP[2:0] bits to protect a specific area of the memory array. When WPS=1, the device will utilize the Individual Block Locks to protect any individual sector or blocks. Thedefault value for all Individual Block Lock bits is 1 upon device power on or after reset.Output Driver Strength (DRV1, DRV0) –Volatile/Non-Volatile WritableThe DRV1 & DRV0 bits are used to determine the output driver strength for the Read operations.Reserved Bits –Non FunctionalThere are a few reserved Status Register bits that may be read out as a “0” or “1”. It is recommended to ignore the values of those bits. During a “Write Status Register” instruction, the Reserved Bits can be written as “0”, but there will not be any effects.Status Register Memory Protection (WPS = 0, CMP = 0)Notes:1.X = don’t care2.L = Lower; U = Upper3.If any Erase or Program command specifies a memory region that contains protected data portion, this commandwill be ignored.Write Status Register-1 (01h), Status Register-2 (31h) & Status Register-3 (11h)The Write Status Register instruction allows the Status Registers to be written. The writable Status Register bits include: SEC, TB, BP[2:0] in Status Register-1; CMP, LB[3:1], QE, SRL in Status Register-2; DRV1, DRV0, WPS in Status Register-3. All other Status Register bit locations are read-only and will not be affected by the Write Status Register instruction. LB[3:1] are non-volatile OTP bits, once it is set to 1, it cannot be cleared to 0.To write non-volatile Status Register bits, a standard Write Enable (06h) instruction must previously have been executed for the device to accept the Write Status Register instruction (Status Register bit WEL must equal 1). Once write enabled, the instruction is entered by driving /CS low, sending the instruction code “01h/31h/11h”, and then writing the status register data byte as illustrated in Figure 9a.To write volatile Status Register bits, a Write Enable for Volatile Status Register (50h) instruction must have been executed prior to the Write Status Register instruction (Status Register bit WEL remains 0). However, SRL and LB[3:1] cannot be changed from “1” to “0” because of the OTP protection for these bits. Upon power off or the execution of a Software/Hardware Reset, the volatile Status Register bit values will be lost, and the non-volatile Status Register bit values will be restored.During non-volatile Status Register write operation (06h combined with 01h/31h/11h), after /CS is driven high, the self-timed Write Status Register cycle will commence for a time duration of t W(See AC Characteristics). While the Write Status Register cycle is in progress, the Read Status Register instruction may still be accessed to check the status of the BUSY bit. The BUSY bit is a 1 during the Write Status Register cycle and a 0 when the cycle is finished and ready to accept other instructions again. After the Write Status Register cycle has finished, the Write Enable Latch (WEL) bit in the Status Register will be cleared to 0.During volatile Status Register write operation (50h combined with 01h/31h/11h), after /CS is driven high, the Status Register bits will be refreshed to the new values within the time period of t SHSL2(See AC Characteristics). BUSY bit will remain 0 during the Status Register bit refresh period.Refer to section 7.1 for Status Register descriptions.Figure 9a. Write Status Register-1/2/3 Instruction。

LPC2131_32_34_36_38All information provided in this document is subject to legal disclaimers.© NXP B.V. 2011. All rights reserved.Product data sheet Rev. 5.1 — 29 July 2011 19 of 45NXP Semiconductors LPC2131/32/34/36/38Single-chip 16/32-bit microcontrollers6.12.1Features•Compliant with Serial Peripheral Interface (SPI) specification.•Synchronous, Serial, Full Duplex, Communication.•Combined SPI master and slave.•Maximum data bit rate of one eighth of the input clock rate.6.13SSP serial I/O controllerThe LPC2131/32/34/36/38 each contain one Serial Synchronous Port controller (SSP).The SSP controller is capable of operation on a SPI, 4-wire SSI, or Microwire bus. It caninteract with multiple masters and slaves on the bus. However, only a single master and asingle slave can communicate on the bus during a given data transfer. The SSP supportsfull duplex transfers, with frames of 4 bits to 16 bits of data flowing from the master to theslave and from the slave to the master. Often only one of these data flows carriesmeaningful data.6.13.1Features•Compatible with Motorola SPI, 4-wire TI SSI and National Semiconductor Microwirebuses.•Synchronous Serial Communication.•Master or slave operation.•8-frame FIFOs for both transmit and receive.•Four bits to 16 bits per frame.6.14General purpose timers/external event countersThe Timer/Counter is designed to count cycles of the peripheral clock (PCLK) or anexternally supplied clock, and optionally generate interrupts or perform other actions atspecified timer values, based on four match registers. It also includes four capture inputsto trap the timer value when an input signal transitions, optionally generating an interrupt.Multiple pins can be selected to perform a single capture or match function, providing anapplication with ‘or’ and ‘and’, as well as ‘broadcast’ functions among them.At any given time only one of peripheral’s capture inputs can be selected as an externalevent signal source, i.e., timer’s clock. The rate of external events that can besuccessfully counted is limited to PCLK/2. In this configuration, unused capture lines canbe selected as regular timer capture inputs.6.14.1Features• A 32-bit Timer/Counter with a programmable 32-bit Prescaler.•External Event Counter or timer operation.•Four 32-bit capture channels per timer/counter that can take a snapshot of the timervalue when an input signal transitions. A capture event may also optionally generatean interrupt.•Four 32-bit match registers that allow:–Continuous operation with optional interrupt generation on match.LPC2131_32_34_36_38All information provided in this document is subject to legal disclaimers.© NXP B.V. 2011. All rights reserved.Product data sheet Rev. 5.1 — 29 July 2011 20 of 45NXP Semiconductors LPC2131/32/34/36/38Single-chip 16/32-bit microcontrollers–Stop timer on match with optional interrupt generation.–Reset timer on match with optional interrupt generation.•Four external outputs per timer/counter corresponding to match registers, with thefollowing capabilities:–Set LOW on match.–Set HIGH on match.–Toggle on match.–Do nothing on match.6.15Watchdog timerThe purpose of the watchdog is to reset the microcontroller within a reasonable amount oftime if it enters an erroneous state. When enabled, the watchdog will generate a systemreset if the user program fails to ‘feed’ (or reload) the watchdog within a predeterminedamount of time.6.15.1Features•Internally resets chip if not periodically reloaded.•Debug mode.•Enabled by software but requires a hardware reset or a watchdog reset/interrupt to bedisabled.•Incorrect/Incomplete feed sequence causes reset/interrupt if enabled.•Flag to indicate watchdog reset.•Programmable 32-bit timer with internal pre-scaler.•Selectable time period from (T cy(PCLK)⨯ 256⨯ 4) to (T cy(PCLK)⨯ 232⨯ 4) in multiples ofT cy(PCLK)⨯4.6.16Real-time clockThe Real-Time Clock (RTC) is designed to provide a set of counters to measure timewhen normal or idle operating mode is selected. The RTC has been designed to use littlepower, making it suitable for battery powered systems where the CPU is not runningcontinuously (Idle mode).6.16.1Features•Measures the passage of time to maintain a calendar and clock.•Ultra-low power design to support battery powered systems.•Provides Seconds, Minutes, Hours, Day of Month, Month, Year, Day of Week, andDay of Year.•Can use either the RTC dedicated 32 kHz oscillator input or clock derived from theexternal crystal/oscillator input at XTAL1. Programmable Reference Clock Dividerallows fine adjustment of the RTC.•Dedicated power supply pin can be connected to a battery or the main 3.3V.。

Figure 2. The MAX3243 Detects RS-232 Activity When the UART and Interface Are Shut Down.MAX3221/MAX3223/MAX3243+3V to +5.5V RS-232Transceivers with AutoShutdown Figure 1. Interface Under Control of PMURS-232 ReceiversThe MAX3221/MAX3223/MAX3243’s receivers convertRS-232 signals to CMOS-logic output levels. All receiv-ers have one inverting three-state output. In shutdown(FORCEOFF = low) or in AutoShutdown, the MAX3221/MAX3223’s receivers are active (Table 1). Driving EN highplaces the receiver(s) in a high-impedance state. TheMAX3243’s receivers are high impedance when the partis shut down.The MAX3243 has an always-active complementaryoutput (R2OUTB). R2OUTB is an extra output thatmonitors receiver activity while the other receiversare high impedance. This allows Ring Indicator to bemonitored without forward biasing other devicesconnected to the receiver outputs. This is ideal forsystems where V CC is set to 0V in shutdown toaccommodate peripherals, such as UARTs (Figure 2).Integrated │ 6Figure 8. Loopback Test CircuitFigure 9. Loopback Test Result at 120kbps Figure 10. Loopback Test Result at 235kbpsTable 3. Required Capacitor Values Table 4. Logic Family Compatibility with Various Supply Voltages V CC (V)C1 (μF)C2, C3, C4 (μF)3.0 to 3.60.10.14.5 to 5.50.0470.333.0 to 5.50.10.47SYSTEM POWER-SUPPLY VOLTAGE (V) V CC SUPPLY VOLTAGE (V)COMPATIBILITY 3.3 3.3Compatible with all CMOS families.55Compatible with all TTL and CMOS-logic families.5 3.3Compatible with ACT and HCT CMOS, and with TTL. Incompatible with AC, HC, or CD4000 CMOS.T1IN R1OUT V CC = +3.3V, 120kbpsC1–C4 = 0.1µFT1OUT 5V/div5V/div5V/div5µs/divT1IN R1OUT V CC = +3.3V, 235kbps C1–C4 = 0.1µF T1OUT 5V/div 5V/div 2µs/div 5V/div MAX3221/MAX3223/MAX3243+3V to +5.5V RS-232Transceivers with AutoShutdown Integrated │ 11。

© Nexperia B.V. 2017. All rights reserved PTVSxS1UR_SER All information provided in this document is subject to legal disclaimers.Product data sheet Rev. 3 — 10 January 2011 10 of 12Nexperia PTVSxS1UR series 400 W Transient Voltage Suppressor13.Legal information13.1 Data sheet status[1]Please consult the most recently issued document before initiating or completing a design. [2]The term ‘short data sheet’ is explained in section “Definitions”. [3]The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL .13.2 DefinitionsDraft — The document is a draft version only. The content is still underinternal review and subject to formal approval, which may result inmodifications or additions. Nexperia does not give anyrepresentations or warranties as to the accuracy or completeness ofinformation included herein and shall have no liability for the consequences ofuse of such information.Short data sheet — A short data sheet is an extract from a full data sheetwith the same product type number(s) and title. A short data sheet is intendedfor quick reference only and should not be relied upon to contain detailed andfull information. For detailed and full information see the relevant full datasheet, which is available on request via the local Nexperia salesoffice. In case of any inconsistency or conflict with the short data sheet, thefull data sheet shall prevail.Product specification — The information and data provided in a Productdata sheet shall define the specification of the product as agreed betweenNexperia and its customer, unless Nexperia andcustomer have explicitly agreed otherwise in writing. In no event however,shall an agreement be valid in which the Nexperia product isdeemed to offer functions and qualities beyond those described in theProduct data sheet.13.3 Disclaimers Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia’s aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.Right to make changes — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of a Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia accepts no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer’s own risk.Applications — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer’s sole responsibility to determine whether the Nexperia product is suitable and fit for the customer’s applications and products planned, as well as for the planned application and use of customer’s third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer’s applications or products, or the application or use by customer’s third party customer(s). Customer is responsible for doing all necessarytesting for the customer’s applications and products using Nexperiaproducts in order to avoid a default of the applications andthe products or of the application or use by customer’s third partycustomer(s). Nexperia does not accept any liability in this respect.Limiting values — Stress above one or more limiting values (as defined inthe Absolute Maximum Ratings System of IEC 60134) will cause permanentdamage to the device. Limiting values are stress ratings only and (proper)operation of the device at these or any other conditions above those given inthe Recommended operating conditions section (if present) or theCharacteristics sections of this document is not warranted. Constant orrepeated exposure to limiting values will permanently and irreversibly affectthe quality and reliability of the device.Terms and conditions of commercial sale — Nexperiaproducts are sold subject to the general terms and conditions of commercialsale, as published at /profile/terms , unless otherwiseagreed in a valid written individual agreement. In case an individualagreement is concluded only the terms and conditions of the respectiveagreement shall apply. Nexperia hereby expressly objects toapplying the customer’s general terms and conditions with regard to thepurchase of Nexperia products by customer.No offer to sell or license — Nothing in this document may be interpreted orconstrued as an offer to sell products that is open for acceptance or the grant,conveyance or implication of any license under any copyrights, patents orother industrial or intellectual property rights.Export control — This document as well as the item(s) described hereinmay be subject to export control regulations. Export might require a priorauthorization from national authorities.Document status [1][2]Product status [3]Definition Objective [short] data sheetDevelopment This document contains data from the objective specification for product development. Preliminary [short] data sheetQualification This document contains data from the preliminary specification. Product [short] data sheetProduction This document contains the product specification.© Nexperia B.V. 2017. All rights reserved PTVSxS1UR_SER All information provided in this document is subject to legal disclaimers.Product data sheet Rev. 3 — 10 January 2011 4 of 12Nexperia PTVSxS1UR series 400 W Transient Voltage Suppressor6.Thermal characteristics[1]Device mounted on an FR4Printed-Circuit Board (PCB), single-sided copper, tin-plated and standard footprint.[2]Device mounted on an FR4PCB, single-sided copper, tin-plated, mounting pad for cathode 1cm 2.[3]Device mounted on a ceramic PCB, Al 2O 3, standard footprint.[4]Soldering point of cathode tab.7.CharacteristicsTable 8.Thermal characteristics Symbol Parameter Conditions Min Typ Max Unit R th(j-a)thermal resistance fromjunction to ambient in free air [1]--220K/W [2]--130K/W [3]--70K/W R th(j-sp)thermal resistance from junction to solder point [4]--18K/W Table 9.Characteristics per type; PTVS3V3S1UR to PTVS7V0S1URT j =25°C unless otherwise specified.Type number Reverse standoffvoltageV RWM (V)Breakdown voltage V BR (V)Reverse leakage current I RM (μA)Clamping voltage V CL (V)I R =10mAat V RWM (V)MaxMin Typ Max Typ Max Max I PPM (A)PTVS3V3S1UR3.3 5.20 5.60 6.0056008.043.8PTVS5V0S1UR5.06.40 6.707.0054009.243.5PTVS6V0S1UR6.0 6.677.027.37540010.338.8PTVS6V5S1UR6.57.227.607.98525011.235.7PTVS7V0S1UR 7.07.788.208.60310012.033.3Table 10.Characteristics per type; PTVS7V5S1UR to PTVS64VS1URT j =25°C unless otherwise specified.Type number Reverse standoffvoltageV RWM (V)Breakdown voltage V BR (V)Reverse leakage current I RM (μA)Clamping voltage V CL (V)I R =1mAat V RWM (V)MaxMin Typ Max Typ Max Max I PPM (A)PTVS7V5S1UR7.58.338.779.210.25012.931.0PTVS8V0S1UR8.08.899.369.830.032513.629.4PTVS8V5S1UR8.59.449.9210.400.011014.427.8PTVS9V0S1UR9.010.0010.5511.100.005515.426.0PTVS10VS1UR1011.1011.7012.300.005 2.517.023.5PTVS11VS1UR1112.2012.8513.500.005 2.518.222.0PTVS12VS1UR1213.3014.0014.700.005 2.519.920.1PTVS13VS1UR1314.4015.1515.900.0010.121.518.6。

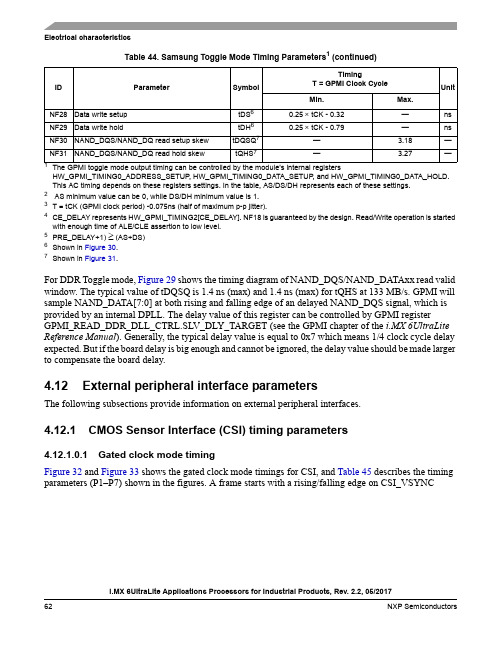

i.MX 6UltraLite Applications Processors for Industrial Products, Rev. 2.2, 05/201762NXP Semiconductors Electrical characteristicsFor DDR Toggle mode, Figure 29 shows the timing diagram of NAND_DQS/NAND_DATAxx read valid window. The typical value of tDQSQ is 1.4 ns (max) and 1.4 ns (max) for tQHS at 133 MB/s. GPMI will sample NAND_DATA[7:0] at both rising and falling edge of an delayed NAND_DQS signal, which is provided by an internal DPLL. The delay value of this register can be controlled by GPMI registerGPMI_READ_DDR_DLL_CTRL.SLV_DLY_TARGET (see the GPMI chapter of the i.MX 6UltraLite Reference Manual ). Generally, the typical delay value is equal to 0x7 which means 1/4 clock cycle delay expected. But if the board delay is big enough and cannot be ignored, the delay value should be made larger to compensate the board delay.4.12External peripheral interface parametersThe following subsections provide information on external peripheral interfaces.4.12.1CMOS Sensor Interface (CSI) timing parameters 4.12.1.0.1Gated clock mode timingFigure 32 and Figure 33 shows the gated clock mode timings for CSI, and Table 45 describes the timing parameters (P1–P7) shown in the figures. A frame starts with a rising/falling edge on CSI_VSYNC NF28Data write setuptDS 60.25⨯tCK - 0.32—ns NF29Data write holdtDH 60.25⨯tCK - 0.79—ns NF30NAND_DQS/NAND_DQ read setup skewtDQSQ 7— 3.18—NF31NAND_DQS/NAND_DQ read hold skewtQHS 7—3.27—1The GPMI toggle mode output timing can be controlled by the module’s internal registers HW_GPMI_TIMING0_ADDRESS_SETUP , HW_GPMI_TIMING0_DATA_SETUP , and HW_GPMI_TIMING0_DATA_HOLD. This AC timing depends on these registers settings. In the table, AS/DS/DH represents each of these settings.2AS minimum value can be 0, while DS/DH minimum value is 1.3T = tCK (GPMI clock period) -0.075ns (half of maximum p-p jitter).4CE_DELAY represents HW_GPMI_TIMING2[CE_DELAY]. NF18 is guaranteed by the design. Read/Write operation is started with enough time of ALE/CLE assertion to low level.5PRE_DELAY+1) ≥ (AS+DS)6Shown in Figure 30.7Shown in Figure 31.Table 44. Samsung Toggle Mode Timing Parameters 1 (continued)ID Parameter Symbol TimingT = GPMI Clock CycleUnit Min.Max.Electrical characteristicsi.MX 6UltraLite Applications Processors for Industrial Products, Rev. 2.2, 05/2017NXP Semiconductors 63(VSYNC), then CSI_HSYNC (HSYNC) is asserted and holds for the entire line. The pixel clock, CSI_PIXCLK (PIXCLK), is valid as long as HSYNC is asserted.Figure 32. CSI Gated Clock Mode—Sensor Data at Falling Edge, Latch Data at Rising EdgeFigure 33. CSI Gated Clock Mode—Sensor Data at Rising Edge, Latch Data at Falling EdgeTable 45. CSI Gated Clock Mode Timing ParametersIDParameter Symbol Min.Max.Units P1CSI_VSYNC to CSI_HSYNC time tV2H 33.5—ns P2CSI_HSYNC setup time tHsu 1—ns P3CSI DATA setup time tDsu 1—nsCSI_PIXCLKCSI_VSYNCCSI_DATA[23:00]P5P1P3P4CSI_HSYNCP2P6P7CSI_PIXCLKCSI_VSYNCCSI_DATA[23:00]P6P1P3P4CSI_HSYNCP2P5P7。

General DescriptionThe DS3231 is a low-cost, extremely accurate I 2C real-time clock (RTC) with an integrated temperature-compensated crystal oscillator (TCXO) and crystal. The device incorporates a battery input, and maintains accurate timekeeping when main power to the device is interrupted. The integration of the crystal resonator enhances the long-term accuracy of the device as well as reduces the piece-part count in a manufacturing line. The DS3231 is available in commercial and industrial temperature ranges, and is offered in a 16-pin, 300-mil SO package.The RTC maintains seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with an AM /PM indicator. Two programmable time-of-day alarms and a programmable square-wave output are provided. Address and data are transferred serially through an I 2C bidirectional bus.A precision temperature-compensated voltage reference and comparator circuit monitors the status of V CC to detect power failures, to provide a reset output, and to automatically switch to the backup supply when necessary. Additionally, the RST pin is monitored as a pushbutton input for generating a μP reset.Benefits and Features●Highly Accurate RTC Completely Manages AllTimekeeping Functions•Real-Time Clock Counts Seconds, Minutes, Hours,Date of the Month, Month, Day of the Week, and Year, with Leap-Year Compensation Valid Up to 2100•Accuracy ±2ppm from 0°C to +40°C •Accuracy ±3.5ppm from -40°C to +85°C •Digital Temp Sensor Output: ±3°C Accuracy •Register for Aging Trim•RST Output/Pushbutton Reset Debounce Input •Two Time-of-Day Alarms•Programmable Square-Wave Output Signal ●Simple Serial Interface Connects to MostMicrocontrollers•Fast (400kHz) I 2C Interface●Battery-Backup Input for Continuous Timekeeping•Low Power Operation Extends Battery-Backup Run Time• 3.3V Operation ●Operating Temperature Ranges: Commercial(0°C to +70°C) and Industrial (-40°C to +85°C)●Underwriters Laboratories ® (UL) Recognized ApplicationsUnderwriters Laboratories is a registered certification mark of Underwriters Laboratories Inc.Ordering Information and Pin Configuration appear at end of data sheet.●Servers ●Telematics●Utility Power Meters ●GPSDS3231Extremely Accurate I 2C-IntegratedRTC/TCXO/Crystalto the DS3231 resets because of a loss of V CC or other event, it is possible that the microcontroller and DS3231 I 2C communications could become unsynchronized, e.g., the microcontroller resets while reading data from the DS3231. When the microcontroller resets, the DS3231 I 2C interface may be placed into a known state by tog-gling SCL until SDA is observed to be at a high level. At that point the microcontroller should pull SDA low while SCL is high, generating a START condition.Clock and CalendarThe time and calendar information is obtained by reading the appropriate register bytes. Figure 1 illustrates the RTC registers. The time and calendar data are set or initialized by writing the appropriate register bytes. The contents of the time and calendar registers are in the binary-codedNote: Unless otherwise specified, the registers’ state is not defined when power is first applied.Figure 1. Timekeeping RegistersADDRESSBIT 7MSB BIT 6BIT 5BIT 4BIT 3BIT 2BIT 1BIT 0LSBFUNCTION RANGE 00h 010 Seconds Seconds Seconds 00–5901h 010 Minutes MinutesMinutes 00–5902h 012/24AM /PM 10 HourHourHours1–12 + AM /PM00–2320 Hour03h 000DayDay 1–704h 0010 DateDate Date 01–3105h Century10 MonthMonth Month/Century 01–12 + Century06h 10 YearYear Year 00–9907h A1M110 Seconds Seconds Alarm 1 Seconds 00–5908h A1M210 Minutes Minutes Alarm 1 Minutes 00–5909h A1M312/24AM /PM 10 HourHour Alarm 1 Hours 1–12 + AM /PM00–2320 Hour0Ah A1M4DY/DT10 DateDay Alarm 1 Day 1–7Date Alarm 1 Date 1–310Bh A2M210 Minutes MinutesAlarm 2 Minutes 00–590Ch A2M312/24AM /PM 10 HourHour Alarm 2 Hours 1–12 + AM /PM00–2320 Hour0Dh A2M4DY/DT 10 Date Day Alarm 2 Day 1–7DateAlarm 2 Date 1–310Eh EOSC BBSQWCONV RS2RS1INTCN A2IE A1IE Control —0Fh OSF 000EN32kHz BSY A2F A1F Control/Status —10h SIGN DATA DATA DATA DATA DATA DATA DATA Aging Offset —11h SIGN DATA DATA DATA DATA DATA DATA DATA MSB of Temp —12hDATADATA 0LSB of Temp—RTC/TCXO/CrystalAddress MapFigure 1 shows the address map for the DS3231 time-keeping registers. During a multibyte access, when the address pointer reaches the end of the register space (12h), it wraps around to location 00h. On an I 2C START or address pointer incrementing to location 00h, the cur-rent time is transferred to a second set of registers. The time information is read from these secondary registers, while the clock may continue to run. This eliminates the need to reread the registers in case the main registers update during a read.I 2C InterfaceThe I 2C interface is accessible whenever either V CC or V BAT is at a valid level. If a microcontroller connecteddecimal (BCD) format. The DS3231 can be run in either 12-hour or 24-hour mode. Bit 6 of the hours register is defined as the 12- or 24-hour mode select bit. When high, the 12-hour mode is selected. In the 12-hour mode, bit 5 is the AM/PM bit with logic-high being PM. In the 24-hour mode, bit 5 is the 20-hour bit (20–23 hours). The century bit (bit 7 of the month register) is toggled when the years register overflows from 99 to 00.The day-of-week register increments at midnight. Values that correspond to the day of week are user-defined but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on). Illogical time and date entries result in undefined operation.When reading or writing the time and date registers, sec-ondary (user) buffers are used to prevent errors when the internal registers update. When reading the time and date registers, the user buffers are synchronized to the internal registers on any START and when the register pointer rolls over to zero. The time information is read from these secondary registers, while the clock continues to run. This eliminates the need to reread the registers in case the main registers update during a read.The countdown chain is reset whenever the seconds register is written. Write transfers occur on the acknowl-edge from the DS3231. Once the countdown chain is reset, to avoid rollover issues the remaining time and date registers must be written within 1 second. The 1Hz square-wave output, if enabled, transitions high 500ms after the seconds data transfer, provided the oscillator is already running.AlarmsThe DS3231 contains two time-of-day/date alarms. Alarm 1 can be set by writing to registers 07h to 0Ah. Alarm 2 can be set by writing to registers 0Bh to 0Dh. The alarms can be programmed (by the alarm enable and INTCN bits of the control register) to activate the INT/SQW output on an alarm match condition. Bit 7 of each of the time-of-day/date alarm registers are mask bits (Table 2). When all the mask bits for each alarm are logic 0, an alarm only occurs when the values in the timekeeping registers match the corresponding val-ues stored in the time-of-day/date alarm registers. The alarms can also be programmed to repeat every second, minute, hour, day, or date. Table 2 shows the possible settings. Configurations not listed in the table will result in illogical operation.The DY/DT bits (bit 6 of the alarm day/date registers) control whether the alarm value stored in bits 0 to 5 of that register reflects the day of the week or the date of the month. If DY/DT is written to logic 0, the alarm will be the result of a match with date of the month. If DY/DT is written to logic 1, the alarm will be the result of a match with day of the week.When the RTC register values match alarm register set-tings, the corresponding Alarm Flag ‘A1F’ or ‘A2F’ bit is set to logic 1. If the corresponding Alarm Interrupt Enable ‘A1IE’ or ‘A2IE’ is also set to logic 1 and the INTCN bit is set to logic 1, the alarm condition will activate the INT/SQW signal. The match is tested on the once-per-second update of the time and date registers.Table 2. Alarm Mask BitsDY/DTALARM 1 REGISTER MASK BITS (BIT 7)ALARM RATE A1M4A1M3A1M2A1M1X1111Alarm once per secondX1110Alarm when seconds matchX1100Alarm when minutes and seconds matchX1000Alarm when hours, minutes, and seconds match 00000Alarm when date, hours, minutes, and seconds match 10000Alarm when day, hours, minutes, and seconds matchDY/DT ALARM 2 REGISTER MASK BITS (BIT 7)ALARM RATE A2M4A2M3A2M2X111Alarm once per minute (00 seconds of every minute)X110Alarm when minutes matchX100Alarm when hours and minutes match0000Alarm when date, hours, and minutes match1000Alarm when day, hours, and minutes matchRTC/TCXO/Crystaling an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line high to enable the master to gener-ate the STOP condition.Figures 3 and 4 detail how data transfer is accomplished on the I 2C bus. Depending upon the state of the R/W bit, two types of data transfer are possible:Data transfer from a master transmitter to a slave receiver. The first byte transmitted by the masteris the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. Data is transferred with the most signifi-cant bit (MSB) first.Data transfer from a slave transmitter to a master receiver. The first byte (the slave address) is transmit-ted by the master. The slave then returns an acknowl-edge bit. Next follows a number of data bytes transmit-ted by the slave to the master. The master returns an acknowledge bit after all received bytes other than theFigure 2. IC Data Transfer OverviewFigure 3. Data Write—Slave Receiver ModeFigure 4. Data Read—Slave Transmitter ModeRTC/TCXO/CrystalRTC/TCXO/CrystalFigure 5. Data Write/Read (Write Pointer, Then Read)—Slave Receive and Transmit。

UART_RXDn 183TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical SpecificationsCopyright ©2008–2014,Texas Instruments Incorporated 6.24.2UART Electrical Data/Timing(1)U =UART baud time =1/programmed baud rate.Table 6-92.Timing Requirements for UARTx Receive (1)(see Figure 6-65)No.PARAMETER MIN MAX UNIT 4t w(URXDB)Pulse duration,receive data bit (RXDn)0.96U 1.05U ns 5t w(URXSB)Pulse duration,receive start bit 0.96U 1.05U ns (1)U =UART baud time =1/programmed baud rate.(2)D =UART input clock in MHz.The UART(s)input clock source is PLL0_SYSCLK2.(3)E =UART divisor x UART sampling rate.The UART divisor is set through the UART divisor latch registers (DLL and DLH).The UART sampling rate is set through the over-sampling mode select bit (OSM_SEL)of the UART mode definition register (MDR).(4)Baud rate is not indicative of data rate.Actual data rate will be limited by system factors such as EDMA loading,EMIF loading,systemfrequency,etc.Table 6-93.Switching Characteristics Over Recommended Operating Conditions for UARTx Transmit (1)(see Figure 6-65)No.PARAMETER MIN MAX UNIT 1f (baud)Maximum programmable baud rate D/E (2)(3)MBaud (4)2t w(UTXDB)Pulse duration,transmit data bit (TXDn)U -2U +2ns 3t w(UTXSB)Pulse duration,transmit start bit U -2U +2ns Figure 6-65.UART Transmit/Receive Timing185TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical SpecificationsCopyright ©2008–2014,Texas Instruments Incorporated 6.26USB0OTG (USB2.0OTG)The C6745/6747USB2.0peripheral supports the following features:•USB 2.0peripheral at speeds high speed (HS:480Mb/s -C6747only)and full speed (FS:12Mb/s)•USB 2.0host at speeds HS (C6747only),FS,and low speed (LS:1.5Mb/s)•All transfer modes (control,bulk,interrupt,and isochronous)•4Transmit (TX)and 4Receive (RX)endpoints in addition to endpoint 0•FIFO RAM–4K endpoint–Programmable size•Integrated USB 2.0High Speed PHY•Connects to a standard Charge Pump for VBUS 5V generation•RNDIS mode for accelerating RNDIS type protocols using short packet termination over USBImportant Notice:On the original device pinout (marked "A"in the lower right corner of the package),pins USB0_VSSA33(ZKB package pin H4;PTP package pin 139)and USB0_VSSA (ZKB package pin F3;PTP package pin 136)were connected to ground outside the package.For more robust ESD performance,the USB0ground references are now connected inside the package on packages marked "B"and the package pins are unconnected.This change will require that any external filter circuits previously referenced to ground at these pins will need to reference the board ground instead.Important Notice:The USB0controller module clock (PLL0_SYSCLK2)must be greater than 30MHz for proper operation of the USB controller.A clock rate of 60MHz or greater is recommended to avoid data throughput reduction.Table 6-96is the list of USB OTG registers.Table 6-96.Universal Serial Bus OTG (USB0)RegistersBYTE ADDRESSACRONYM REGISTER DESCRIPTION 0x01E00000REVID Revision Register 0x01E00004CTRLR Control Register 0x01E00008STATR Status Register 0x01E0000CEMUR Emulation Register 0x01E00010MODE Mode Register 0x01E00014AUTOREQ Autorequest Register 0x01E00018SRPFIXTIME SRP Fix Time Register 0x01E0001CTEARDOWN Teardown Register 0x01E00020INTSRCR USB Interrupt Source Register 0x01E00024INTSETR USB Interrupt Source Set Register 0x01E00028INTCLRR USB Interrupt Source Clear Register 0x01E0002CINTMSKR USB Interrupt Mask Register 0x01E00030INTMSKSETR USB Interrupt Mask Set Register 0x01E00034INTMSKCLRR USB Interrupt Mask Clear Register 0x01E00038INTMASKEDR USB Interrupt Source Masked Register 0x01E0003CEOIR USB End of Interrupt Register 0x01E00040-Reserved 0x01E00050GENRNDISSZ1Generic RNDIS Size EP10x01E00054GENRNDISSZ2Generic RNDIS Size EP20x01E00058GENRNDISSZ3Generic RNDIS Size EP30x01E0005CGENRNDISSZ4Generic RNDIS Size EP40x01E00400FADDR Function Address Register 0x01E00401POWER Power Management Register。

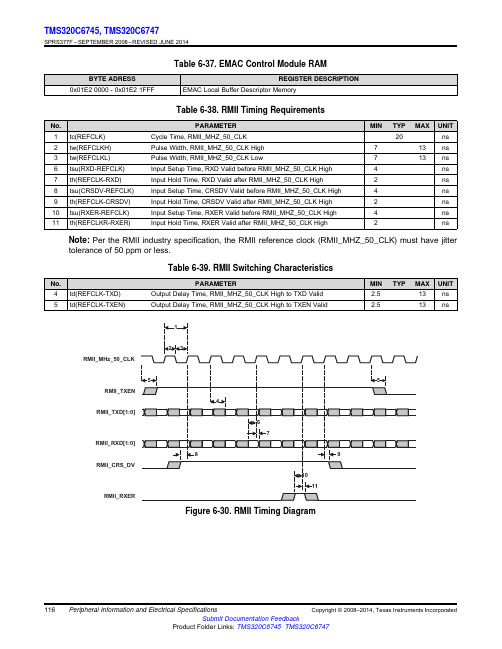

RMII_MHz_50_CLK RMII_TXENRMII_TXD[1:0]RMII_RXD[1:0]RMII_CRS_DVRMII_RXER116TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical Specifications Copyright ©2008–2014,Texas Instruments IncorporatedTable 6-37.EMAC Control Module RAMBYTE ADRESSREGISTER DESCRIPTION 0x01E20000-0x01E21FFF EMAC Local Buffer Descriptor MemoryTable 6-38.RMII Timing RequirementsNo.PARAMETER MIN TYP MAX UNIT 1tc(REFCLK)Cycle Time,RMII_MHZ_50_CLK 20ns 2tw(REFCLKH)Pulse Width,RMII_MHZ_50_CLK High 713ns 3tw(REFCLKL)Pulse Width,RMII_MHZ_50_CLK Low 713ns 6tsu(RXD-REFCLK)Input Setup Time,RXD Valid before RMII_MHZ_50_CLK High 4ns 7th(REFCLK-RXD)Input Hold Time,RXD Valid after RMII_MHZ_50_CLK High 2ns 8tsu(CRSDV-REFCLK)Input Setup Time,CRSDV Valid before RMII_MHZ_50_CLK High 4ns 9th(REFCLK-CRSDV)Input Hold Time,CRSDV Valid after RMII_MHZ_50_CLK High 2ns 10tsu(RXER-REFCLK)Input Setup Time,RXER Valid before RMII_MHZ_50_CLK High 4ns 11th(REFCLKR-RXER)Input Hold Time,RXER Valid after RMII_MHZ_50_CLK High 2nsNote:Per the RMII industry specification,the RMII reference clock (RMII_MHZ_50_CLK)must have jitter tolerance of 50ppm or less.Table 6-39.RMII Switching CharacteristicsNo.PARAMETER MIN TYP MAX UNIT 4td(REFCLK-TXD)Output Delay Time,RMII_MHZ_50_CLK High to TXD Valid 2.513ns 5td(REFCLK-TXEN)Output Delay Time,RMII_MHZ_50_CLK High to TXEN Valid2.513nsFigure 6-30.RMII Timing DiagramAHCLKRx ACLKRx AFSRx AMUTEINx AMUTEx AFSXx ACLKXx AHCLKXx AXRx[0]AXRx[1]AXRx[y]PinsFunction Receive Master Clock Receive Bit Clock Receive Left/Right Clock or Frame Sync Transmit Master Clock Transmit Bit Clock Transmit Left/Right Clock or Frame Sync Transmit/Receive Serial Data Pin Transmit/Receive Serial Data Pin Transmit/Receive Serial Data PinThe McASPs DO NOT have dedicated AMUTEINx pins.119TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical SpecificationsCopyright ©2008–2014,Texas Instruments Incorporated (1)Pins available are the maximum number of pins that may be configured for a particular McASP;not including pin multiplexing.6.16Multichannel Audio Serial Ports (McASP0,McASP1,and McASP2)The McASP serial port is specifically designed for multichannel audio applications.Its key features are:•Flexible clock and frame sync generation logic and on-chip dividers•Up to sixteen transmit or receive data pins and serializers•Large number of serial data format options,including:–TDM Frames with 2to 32time slots per frame (periodic)or 1slot per frame (burst)–Time slots of 8,12,16,20,24,28,and 32bits–First bit delay 0,1,or 2clocks–MSB or LSB first bit order–Left-or right-aligned data words within time slots•DIT Mode (optional)with 384-bit Channel Status and 384-bit User Data registers•Extensive error checking and mute generation logic•All unused pins GPIO-capableAdditionally,while the C674x McASP modules are backward compatible with the McASP on previous devices;the C674x McASP includes the following new features:•Transmit &Receive FIFO Buffers for each McASP.Allows the McASP to operate at a higher sample rate by making it more tolerant to DMA latency.•Dynamic Adjustment of Clock Dividers–Clock Divider Value may be changed without resetting the McASPThe three McASPs on the C6745/6747are configured with the following options:Table 6-43.C6745/6747McASP Configurations (1)ModuleSerializers AFIFO DIT C6745/6747Pins McASP01664Word RX 64Word TX N AXR0[15:0],AHCLKR0,ACLKR0,AFSR0,AHCLKX0,ACLKX0,AFSX0,AMUTE0McASP11264Word RX 64Word TX N AXR1[11:10],AXR1[8:0],AHCLKR1,ACLKR1,AFSR1,AHCLKX1,ACLKX1,AFSX1,AMUTE1McASP2416Word RX 16Word TX Y AXR2[3:0],AHCLKR2,ACLKR2,AFSR2,AHCLKX2,ACLKX2,AFSX2,AMUTE2Figure 6-33.McASP Block Diagram。

144TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical Specifications Copyright ©2008–2014,Texas Instruments Incorporated(1)These parameters are in addition to the general timings for SPI master modes (Table 6-63).(2)P =SYSCLK2period (3)Figure shows only Polarity =0,Phase =0as an example.Table gives parameters for all four master clocking modes.(4)In the case where the master SPI is ready with new data before SPI1_ENA deassertion.(5)Except for modes when SPIDAT1.CSHOLD is enabled and there is additional data to transmit.In this case,SPI1_SCS will remainasserted.(6)This delay can be increased under software control by the register bit field SPIDELAY.T2CDELAY[4:0].(7)If SPI1_ENA is asserted immediately such that the transmission is not delayed by SPI1_ENA.(8)In the case where the master SPI is ready with new data before SPI1_SCS assertion.(9)This delay can be increased under software control by the register bit field SPIDELAY.C2TDELAY[4:0].(10)If SPI1_ENA was initially deasserted high and SPI1_CLK is delayed.Table 6-66.Additional (1)SPI1Master Timings,5-Pin Option (2)(3)No.PARAMATERMIN MAX UNIT 18t d(SPC_ENA)M Max delay for slave todeassert SPI1_ENA after finalSPI1_CLK edge to ensuremaster does not begin thenext transfer.(4)Polarity =0,Phase =0,from SPI1_CLK falling0.5t c(SPC)M +P+5ns Polarity =0,Phase =1,from SPI1_CLK falling P+5Polarity =1,Phase =0,from SPI1_CLK rising0.5t c(SPC)M +P+5Polarity =1,Phase =1,from SPI1_CLK risingP+520t d(SPC_SCS)M Delay from final SPI1_CLKedge tomaster deassertingSPI1_SCS (5)(6)Polarity =0,Phase =0,from SPI1_CLK falling0.5t c(SPC)M +P -3ns Polarity =0,Phase =1,from SPI1_CLK falling P -3Polarity =1,Phase =0,from SPI1_CLK rising0.5t c(SPC)M +P -3Polarity =1,Phase =1,from SPI1_CLK risingP -321t d(SCSL_ENAL)M Max delay for slave SPI to drive SPI1_ENA valid after master asserts SPI1_SCS to delay themaster from beginning the next transfer,C2TDELAY +P ns 22t d(SCS_SPC)M Delay from SPI1_SCS activeto first SPI1_CLK (7)(8)(9)Polarity =0,Phase =0,to SPI1_CLK rising2P -5ns Polarity =0,Phase =1,to SPI1_CLK rising 0.5t c(SPC)M +2P -5Polarity =1,Phase =0,to SPI1_CLK falling2P -5Polarity =1,Phase =1,to SPI1_CLK falling0.5t c(SPC)M +2P -523t d(ENA_SPC)M Delay from assertion ofSPI1_ENA low to firstSPI1_CLK edge.(10)Polarity =0,Phase =0,to SPI1_CLK rising3P +3ns Polarity =0,Phase =1,to SPI1_CLK rising 0.5t c(SPC)M +3P +3Polarity =1,Phase =0,to SPI1_CLK falling3P +3Polarity =1,Phase =1,to SPI1_CLK falling0.5t c(SPC)M +3P +3145TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical SpecificationsCopyright ©2008–2014,Texas Instruments Incorporated(1)These parameters are in addition to the general timings for SPI slave modes (Table 6-63).(2)P =SYSCLK2period (3)Figure shows only Polarity =0,Phase =0as an example.Table gives parameters for all four slave clocking modes.Table 6-67.Additional (1)SPI1Slave Timings,4-Pin Enable Option (2)(3)No.PARAMETERMIN MAX UNIT 24t d(SPC_ENAH)S Delay from finalSPI1_CLK edge toslave deassertingSPI1_ENA.Polarity =0,Phase =0,from SPI1_CLK falling1.5P -32.5P +19ns Polarity =0,Phase =1,from SPI1_CLK falling –0.5t c(SPC)M +1.5P -3–0.5t c(SPC)M +2.5P +19Polarity =1,Phase =0,from SPI1_CLK rising1.5P -32.5P +19Polarity =1,Phase =1,from SPI1_CLK rising–0.5t c(SPC)M +1.5P -3–0.5t c(SPC)M +2.5P +19(1)These parameters are in addition to the general timings for SPI slave modes (Table 6-63).(2)P =SYSCLK2period (3)Figure shows only Polarity =0,Phase =0as an example.Table gives parameters for all four slave clocking modes.Table 6-68.Additional (1)SPI1Slave Timings,4-Pin Chip Select Option (2)(3)No.PARAMETER MIN MAX UNIT 25t d(SCSL_SPC)S Required delay from SPI1_SCS asserted at slave to first SPI1_CLK edge at slave.2P ns 26t d(SPC_SCSH)S Required delay from finalSPI1_CLK edge beforeSPI1_SCS is deasserted.Polarity =0,Phase =0,from SPI1_CLK falling0.5t c(SPC)M +P +5ns Polarity =0,Phase =1,from SPI1_CLK falling P +5Polarity =1,Phase =0,from SPI1_CLK rising0.5t c(SPC)M +P +5Polarity =1,Phase =1,from SPI1_CLK risingP +527t ena(SCSL_SOMI)S Delay from master asserting SPI1_SCS to slave driving SPI1_SOMI valid P +19ns 28t dis(SCSH_SOMI)S Delay from master deasserting SPI1_SCS to slave 3-stating SPI1_SOMI P +19ns (1)These parameters are in addition to the general timings for SPI slave modes (Table 6-63).(2)P =SYSCLK2period (3)Figure shows only Polarity =0,Phase =0as an example.Table gives parameters for all four slave clocking modes.Table 6-69.Additional (1)SPI1Slave Timings,5-Pin Option (2)(3)No.PARAMETER MIN MAX UNIT 25t d(SCSL_SPC)S Required delay from SPI1_SCS asserted at slave to first SPI1_CLK edge at slave.2P ns 26t d(SPC_SCSH)SRequired delay from final SPI1_CLKedge before SPI1_SCS isdeasserted.Polarity =0,Phase =0,from SPI1_CLK falling0.5t c(SPC)M +P +5ns Polarity =0,Phase =1,from SPI1_CLK falling P +5Polarity =1,Phase =0,from SPI1_CLK rising0.5t c(SPC)M +P +5Polarity =1,Phase =1,from SPI1_CLK risingP +527t ena(SCSL_SOMI)S Delay from master asserting SPI1_SCS to slave driving SPI1_SOMI valid P +19ns 28t dis(SCSH_SOMI)S Delay from master deasserting SPI1_SCS to slave 3-stating SPI1_SOMI P +19ns 29t ena(SCSL_ENA)S Delay from master deasserting SPI1_SCS to slave driving SPI1_ENA valid 19ns。

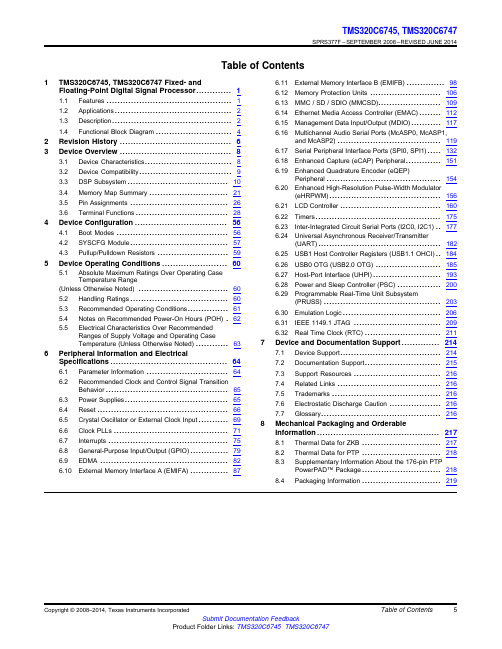

5TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Table of Contents Copyright ©2008–2014,Texas Instruments Incorporated Table of Contents1TMS320C6745,TMS320C6747Fixed-andFloating-Point Digital Signal Processor (1)1.1Features ..............................................11.2Applications ...........................................21.3Description ............................................21.4Functional Block Diagram ............................42Revision History .........................................63Device Overview .........................................83.1Device Characteristics ................................83.2Device Compatibility ..................................93.3DSP Subsystem .....................................103.4Memory Map Summary .............................213.5Pin Assignments ....................................263.6Terminal Functions ..................................284Device Configuration ..................................564.1Boot Modes .........................................564.2SYSCFG Module ....................................574.3Pullup/Pulldown Resistors ..........................595Device Operating Conditions ........................605.1Absolute Maximum Ratings Over Operating Case Temperature Range (Unless Otherwise Noted).................................605.2Handling Ratings ....................................605.3Recommended Operating Conditions ...............615.4Notes on Recommended Power-On Hours (POH).625.5Electrical Characteristics Over RecommendedRanges of Supply Voltage and Operating CaseTemperature (Unless Otherwise Noted)............636Peripheral Information and ElectricalSpecifications (64)6.1Parameter Information ..............................646.2Recommended Clock and Control Signal Transition Behavior .............................................656.3Power Supplies ......................................656.4Reset ................................................666.5Crystal Oscillator or External Clock Input ...........696.6Clock PLLs ..........................................716.7Interrupts ............................................756.8General-Purpose Input/Output (GPIO)..............796.9EDMA ...............................................826.10External Memory Interface A (EMIFA)..............87 6.11External Memory Interface B (EMIFB)..............986.12Memory Protection Units ..........................1066.13MMC /SD /SDIO (MMCSD).......................1096.14Ethernet Media Access Controller (EMAC)........1126.15Management Data Input/Output (MDIO)...........1176.16Multichannel Audio Serial Ports (McASP0,McASP1,and McASP2)......................................1196.17Serial Peripheral Interface Ports (SPI0,SPI1).....1326.18Enhanced Capture (eCAP)Peripheral .............1516.19Enhanced Quadrature Encoder (eQEP)Peripheral ..........................................1546.20Enhanced High-Resolution Pulse-Width Modulator (eHRPWM).........................................1566.21LCD Controller .....................................1606.22Timers ..............................................1756.23Inter-Integrated Circuit Serial Ports (I2C0,I2C1)..1776.24Universal Asynchronous Receiver/Transmitter (UART).............................................1826.25USB1Host Controller Registers (USB1.1OHCI)..1846.26USB0OTG (USB2.0OTG)........................1856.27Host-Port Interface (UHPI).........................1936.28Power and Sleep Controller (PSC)................2006.29Programmable Real-Time Unit Subsystem (PRUSS)...........................................2036.30Emulation Logic ....................................2066.31IEEE 1149.1JTAG .. (209)6.32Real Time Clock (RTC) (2117)Device and Documentation Support ..............2147.1Device Support .....................................2147.2Documentation Support ............................2157.3Support Resources ................................2167.4Related Links ......................................2167.5Trademarks ........................................2167.6Electrostatic Discharge Caution ...................2167.7Glossary ............................................2168Mechanical Packaging and Orderable Information .............................................2178.1Thermal Data for ZKB .............................2178.2Thermal Data for PTP .............................2188.3Supplementary Information About the 176-pin PTP PowerPAD™Package .............................2188.4Packaging Information .. (219)7TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Revision History Copyright ©2008–2014,Texas Instruments Incorporated Revision History (continued)SEE ADDITIONS/MODIFICATIONS/DELETIONSSection 6.11.3EMIFB Electrical Data/Timing Table 6-26,EMIFB SDRAM Interface Timing Requirements:•Updated/Changed Parameter No.19from "t su(DV-CLKH)"to "t (DV-CLKH)"•Added new column:"CVDD =1.3V"•Added new footnote containing "...range rated devices for 456MHz max CPU operating..."•Added new footnote containing "...range rated devices for 400/375/300/266/200MHz max CPU operating ..."Table 6-27,EMIFB SDRAM Interface Switching Characteristics for Commercial (Default)Temperature Range:•Updated/Changed table title from "...Switching Characteristics..."to "...Switching Characteristics for Commercial (Default)Temperature Range "•Added new footnote containing "...range rated devices for 456MHz max CPU operating ..."•Added new footnote containing "...range rated devices for 400/375/300/266/200MHz max CPU operating..."•Updated/Changed CVDD =1.3V MIN column values for Parameter No.4,6,8,10,12,14,16,and 18from "0.9"to "1.1"•Updated/Changed CVDD =1.3V MAX column values for Parameter No.3,5,7,9,11,13,15,and 17from "5.1"to "4.25"•Populated CVDD =1.2V column with values (was empty)•Updated/Changed Parameter No.18from "t ena(CLKH-DLZ)"to "t (CLKH-DLZ)"Table 6-28,EMIFB SDRAM Interface Switching Characteristics for Industrial,Extended,and Automotive Temperature Ranges:•Added NEW tableSection 6.16Multichannel Audio Serial Ports (McASP0,McASP1,and McASP2)Table 6-45,McASP Registers Accessed Through DMA Port:•Updated/Changed Read Accesses Register Description from "XBUSEL =0in XFMT"to "RBUSEL =0in RFMT"•Updated/Changed Write Accesses Register Description from "RBUSEL =0in RFMT"to "XBUSEL =0in XFMT"Section 7.4Related Links Added NEW section.Section 7.7GlossaryAdded NEW section.。

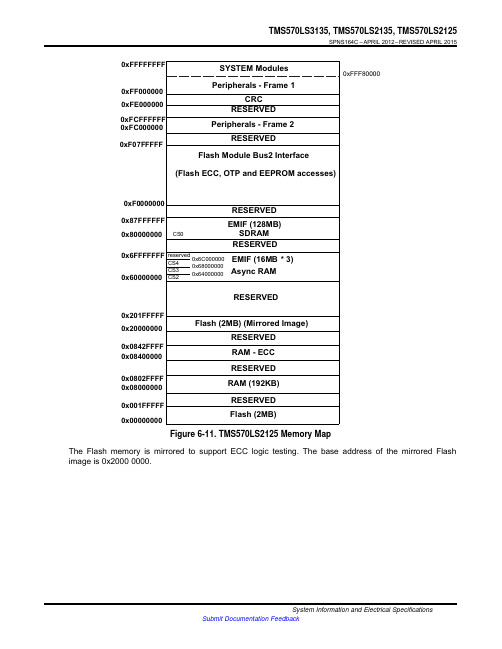

RAM - ECC 0x084000000x0842FFFF RESERVEDRESERVEDRESERVEDRESERVED RESERVEDRESERVEDPeripherals - Frame 20xFC0000000xFCFFFFFF 0xFFF80000EMIF (128MB)0x800000000x87FFFFFF CS0RESERVEDreservedAsync RAM SDRAM 0x640000000x680000000x6C000000Flash Module Bus2 Interface RESERVED(Flash ECC, OTP and EEPROM accesses)CS4CS3CS2TMS570LS3135,TMS570LS2135,TMS570LS2125SPNS164C –APRIL 2012–REVISED APRIL 2015Figure 6-11.TMS570LS2125Memory MapThe Flash memory is mirrored to support ECC logic testing.The base address of the mirrored Flash image is 0x20000000.7.2.2.2Alternate MIBADC1Event Trigger HookupTable7-4.Alternate MIBADC1Event Trigger HookupSOURCE SELECT BITS FOR G1,G2OR EVENTEVENT#TRIGGER(G1SRC[2:0],G2SRC[2:0]or EVSRC[2:0])1000ADEVT2001N2HET2[5]3010N2HET1[27]4011RTI compare0interrupt5100N2HET1[17]6101N2HET1[19]7110N2HET1[11]8111N2HET2[13] The selection between the default MIBADC1event trigger hook-up versus the alternate event trigger hook-up is done by multiplexing control module register30bits0and1.If30[0]=1,then the default MibADC1event trigger hook-up is used.If30[0]=0and30[1]=1,then the alternate MibADC1event trigger hook-up is used.NOTEFor ADEVT trigger source,the connection to the MibADC1module trigger input is made fromthe output side of the input buffer.This way,a trigger condition can be generated either byconfiguring ADEVT as an output function on to the pad(via the mux control),or by drivingthe ADEVT signal from an external trigger source as input.If the mux control module is usedto select different functionality instead of the ADEVT signal,then care must be taken todisable ADEVT from triggering conversions;there is no multiplexing on the input connection.NOTEFor N2HETx trigger sources,the connection to the MibADC1module trigger input is madefrom the input side of the output buffer(at the N2HETx module boundary).This way,atrigger condition can be generated even if the N2HETx signal is not selected to be output onthe pad.NOTEFor the RTI compare0interrupt source,the connection is made directly from the output ofthe RTI module.That is,the interrupt condition can be used as a trigger source even if theactual interrupt is not signaled to the CPU.D i g i t a l O u t p u t C o d eAnalog Input Value (LSB)NOTE A: 1 LSB = (AD –AD )/2REFHI REFLO12TMS570LS3135,TMS570LS2135,TMS570LS2125SPNS164C –APRIL 2012–REVISED APRIL 2015The integral nonlinearity error shown in Figure 7-3(sometimes referred to as linearity error)is the deviation of the values on the actual transfer function from a straight line.Figure 7-3.Integral Nonlinearity (INL)Error。