TMS320VC5402 DSP的并行引导加载

- 格式:pdf

- 大小:151.86 KB

- 文档页数:3

TMS320VC5402外部并行引导装载方法的研究摘要分析了TMS320VC5402DSP的引导装载过程,给出了两个外部并行引导装载的典型电路。

针对这两个电路设计了可脱离Flash烧写器的仿真器在线编程装载方法,并得到了实验验证。

关键词DSP引导装载在线编程装载虚拟扩展程序空间DSP所谓引导方式就是指单片机MCU系统复位时,其系统软件代码所取得的方式。

对于单片机来说,它使用复位矢量方式从程序空间的固定地址处开始取得指令代码。

如果所需代码来自程序空间外部,则引导过程无法进行。

这样的设计有三个突出点一是程序代码可以存储在片外相对慢速、非易失性器件中,而装载运行于高速器件;二是提供多种装载方式,使得DSP可以灵活应用到不同系统;三是省去对DSP片内ROM进行掩膜编程操作,节省大量费用。

引导装载程序根据不同的系统要求提供了多种装载模式,主要包括并行I/O口引导装载、串行口引导装载、HPI引导装载、外部并行引导装载等模式,并且兼容8位和16位字引导装载方式。

1引导装载程序分析TMS320VC5402内部4K字的ROM程序位于0xF000~0xFFFF程序空间,包括引导装载程序、μ律和A律扩充表、正弦对照表、工厂测试码和中断向量表。

其中,引导装载程序位于0xF800~0xFBFF空间。

引导装载程序在决定采用何种装载模式之前,首先对CPU状态寄存器进行初始化。

初始化完成后,引导装载程序执行装载模式判断。

判断的顺序是HPI模式、SPI模式、外部并行模式、标准串口模式、并行I/O模式。

图1说明了整个装载模式的判断流程。

图1引导装载模式选择流程2外部并行装载电路的设计由图1可知,外部并载模式;如果FFFFh处为非有效值,则读数据空间FFFFh,判断是否是有效的并行装载模式。

对于外部并行装载,要求装载时Flash位于数据空间。

下面给出两种实际应用过的并行装载电路,如图2所示。

图2a适用于程序运行时不要求大数据空间的系统。

TMS320VC5402系列DSP 精品实验数例实验一新手上路]初学者编写的第一个程序通常是控制XF引脚的变化,然后用示波器测量XF脚波形或观察与相接的LED。

这个程序也常常用来测度一下DSP能否正常工作。

实验1.1 最简单的程序:控制XF引脚周期性变化实验目的:通过简单的程序了解DSP程序的结构,熟悉CCS开发环境。

**************************************************************最简单的程序:TestXF1.asm*循环对XF位置1和清0,用示波器可以在XF脚检测到电平高低周期性变化*常用于检测DSP是否工作。

*************************************************************.mmregs ;预定义的寄存器.def CodeStart ;定义程序入口标记.text ;程序区CodeStart: ;程序入口SSBX XF ;XF置1RPT #999 ;重复执行1000次空指令产生延时NOPRSBX XF ;XF清0RPT #999 ;重复执行1000次空指令产生延时NOPB CodeStart ;跳转到程序开头循环执行.endNOP指令执行时间为一个时钟周期,设DSP工作频率是50MHz,可以估算出XF引脚电平的变化频率约为:5 0M/2000=25kHz在没有示波器的情况下,就要将程序1.1稍作改进,增加延时,用一个延时子程序将XF脚电平变化频率降到肉眼可分辨的程度,就可以用LED来显示电平的变化,程序如下:实验1.2 子程序调用实验目的:学习子程序的调用**************************************************************TestXF2.asm*对TestXF1.asm稍作改进,用延时子程序设置较长的延时,*可以用试验板上的LED看到XF引脚电平的变化*************************************************************.mmregs ;预定义的寄存器.def CodeStart ;定义程序入口标记.text ;程序区CodeStart: ;程序入口SSBX XF ;XF置1CALL Delay ;调用延时程序RSBX XF ;XF清0CALL Delay ;调用延时程序B CodeStart ;跳转到程序开头循环执行***************************************************************延时子程序:Delay*用两级减一计数器来延时。

郑州轻工业学院DSP课程设计院系:计算机与通信工程学院专业:信息工程12-01姓名:何骞学号: 541207070111指导老师:耿鑫成绩:引言在54x 系列DSP 的应用设计中,DSP 的运行速度是衡量系统性能的一项重要指标.要达到预期的运行速度,就要给DSP系统的程序空间设计一个高速程序存储空间.引导是将程序存储在低速但停电数据不丢失的FLASH中,运行时使用存取速度快的RAM作为程序运行存储体,这样既可保证停电时数据不丢失又可进行高速数据存取.本文介绍TMS320VC5402并行引导方案的设计。

Boot Loaded 是开发 DSP 应用系统的最后一个必要环节 , 也是很重要的环节之一。

Boot Loader 方法是对单片机的一种改进。

众所周知 , 通用单片机的程序是把单片机放入专用的烧写器中 , 先将程序烧入 EEPROM 中 , 然后将单片机装入功能板上工作。

DSP 为了增加软件下载的灵活性 , 将这个EEPROM 等存储器放置到片外 , 由一个或几片FLASH 来代替 ;DSP 的内部 ROM 固化了一个称为Boot 的程序 , 在 DSP 上电硬复位后 (MP/ MC = 0) , DSP 自动执行这个 Boot 程序 , 将外部 FLASH 的程序读入 DSP 内部的高速 RAM 程序区中。

所以 , 所谓的 Boot Loader 就是 DSP 上电后自动将固化在FLASH 中的程序读入到 DSP 的片上 RAM 或片外RAM 映射成的存储区间的一个过程。

按照 Boot 时程序由外部 FLASH 等存储器进入到 DSP 片上RAM 的通道不同分为多种 Boot Loader 的模式 ,VC5402 为脱机运行提供了以下几种启动装载模式 : 并行 I/ O 口引导装载、串行口引导装载、 HPI 引导装载、外部并行引导装载等 , 并且兼容 8 位和 16位字引导装载方式。

对于以 VC5402 为核心的独立系统中 , 实践证明 , 并行口加载方案是最佳的。

TMS320C54x的加载引导 TMS320C5402文章发布人:gxy 共53人阅读文字大小:[ 大中小 ] 文字背景色:摘要:加载引导是TI公司的DSPs系统设计中必不可少的重要环节。

文章对TMS320C54x加载引导的概念、方法及特点做了详细的阐述,同时以TMS320C5402的16位并行加载引导方式为例,给出了加载引导设置文件的程序代码和所生成的引导表文件。

关键词:加载引导;数字信号处理;TMS320C54x1 前言TMS320C54x是TI公司推出的定点系列数字信号处理芯片,它具有运算速度高、CPU结构优化、功耗低和智能化外设等特点,特别适用于实时嵌入式系统的开发,因此,它已成为数字产品设计中低成本,低功耗、高性能的数字信号处理芯片的首选,在便携式仪器、消费类电子、医疗设备等领域得到广泛的应用。

TMS320C54x的加载引导(BOOTLOAD)方式可使系统在上电时将代码从片外加载到程序区,从而允许开发者事先将程序代码放在外部低速的非易失性存储器件中以便快速取址、译址和执行。

开发设计人员可以用不同的控制信号(如中断、外部标志(XF)、通用输出(BIO)等)来选择不同的加载引导方式以满足设计需求。

2 加载引导(BOOTLOAD)方式在上电复位后,DSP只有处于微计算机状态即MP/MC为零时才能进入加载引导过程。

TI公司已在DSP芯片内部ROM的OF800H-OFCOOh中固化了一段加载引导程序(BOOTLOADER),其作用是先根据相关控制信号的不同状态来确定采用何种加载引导方式,然后将代码从外部加载到程序区,最后再将程序入口地址赋给程序指针。

在这段程序的开始,还应对CPU状态寄存器进行初始化设置,包括屏蔽中断(INTM=1)、内部DARAM映射到程序/数据区(OVLY=1)、程序/数据区读写加7个等待周期等设置。

为了满足不同系统的需求,TMS320C54x有多种加载引导方式。

各种加载引导的功能如下:主机接口引导主机接口(HPI)是TI公司DSP的特色之一,即DSP作为协处理器将片内DRAM共享以便让其它智能器件(比如单片机或另外的DSP)作为主机访问,从而提供一种方便快捷的通讯联系方式。

TMS320VC5402 DSP并行8bit EPROM引导装载方法研究摘要:TMS320VC5402 DSP芯片并行引导的特点和引导的过程中,设计了并行8bit EPROM引导装载的电路,并给出了实现方法。

实践证明,该电路和方法在利用TMS320VC5402 DSP芯片设计系统时非常简便,具有很大的实用性。

关键词:DSP 引导装载并行引导表TMS320VC5402(以下简称C5402)是德州仪器公司(TI)推出的性价比极高的16bit定点数字信号处理器(DSP),操作速率可达100MIPS,它的内部资源配置为用户构造系统提供了很大便利。

C5402芯片配置有4K×16bit片内屏蔽式的ROM(F000h-FFFFh)。

在4K ROM资源里,包含了Bootloader程序。

这个Bootloader程序在系统通电后能自动将存放在外部载体的用户代码引导到程序存储器的任何空间或片内RAM。

如果芯片的MP/MC脚在复位时为低电位,指令从片内ROM的FF80h地址开始执行,在FF80h地址后有一个跳转指令自动转入到Bootloader程序,由Bootloader程序进行引导装载用户程序。

C5402芯片内包含有16K×16bit双存取的RAM(DARAM)。

DARAM分成两个块,每个块为8K,每个块在一个机器周期内支持两次读或一次读和一次写。

片内DARAM位于数据空间0080h-3FFFh地址,通过设置C5402寄存器PMST的OVLY位为1,可以把片内RAM映射成程序/数据存储空间。

用户在设计自己的系统时,如程序容量不超过16K,则可考虑充分利用芯片的内部资源,采用引导装载的方式,以降低系统的设计难度和设计成本、缩短产品研制周期。

1 8bit EPROM引导装载的特点和初始化TMS320VC5402 Bootloader用于在芯片通电时将存储于外部的用户代码传输到内部或外部程序存储器,用户代码可存储在外部速度较慢的非失忆性的存储器内,使C5402能外扩普通低速的EPROM。

D S P课程设计报告书题目: 基于TMS320VC5402的DSP最小系统设计专业:电气工程及其自动化班级:电气F1102学号: 201123910507学生姓名:唐智强指导教师:张世杰课程设计题目:基于TMS320VC5402的DSP最小系统设计指导教师评语:成绩:指导教师:张世杰年月日基于TMS320VC5402的DSP最小系统设计李迎春王玉峰王达伟(北华航天工业学院电子工程系,河北廊坊065000)摘要:TMS320VC5402是由TI公司生产的性价比极高的定点DSP芯片。

主要研究了基于TMS320VC5402的最小系统板的软硬件设计。

针对电源电路、复位电路、时钟电路、JTAG接口电路、DSP芯片电路提出可行的设计方案。

同时,给出了一个点亮LED灯的完整汇编源代码。

关键词:DSP;TMS320VC5402;最小系统;硬件设计;软件设计基金项目:河北省教育厅青年基金项目(2010206);北华航天工业学院教研项目(JY-2010-003-Y)收稿日期:2011-12-04作者简介:李迎春(1976-),女,讲师,博士,湖北荆门人,主要从事DSP和图像处理的教学和科研工作。

目录引言........................................................................................................................................ - 4 - 1TMS320VC5402简介........................................................................................................... - 4 - 2系统硬件设计........................................................................................................................ - 4 - 2. 1电平转换............................................................................................................................ - 4 - 2. 2电源控制电路.................................................................................................................... - 5 - 2. 3复位电路............................................................................................................................ - 5 - 2. 4时钟电路............................................................................................................................ - 6 - 2. 5译码电路............................................................................................................................ - 6 - 2. 6输入接口电路.................................................................................................................... - 6 - 2. 7输出接口电路.................................................................................................................... - 7 - 2. 8存储器扩展电路................................................................................................................ - 7 - 2. 9JTAG仿真接口电路 ......................................................................................................... - 7 - 3系统软件设计........................................................................................................................ - 8 - 3. 1引导程序............................................................................................................................ - 8 - 3. 2用户程序.......................................................................................................................... - 10 - 参考文献- 15 -4总结...................................................................................................................................... - 16 -引言在仪器仪表迅速发展的同时,计算机和网络技术也在迅速发展,PC机已经从高速增长进入到平稳发展时期,单纯由PC机带领电子产业蒸蒸日上的时代己经成为历史,嵌入式系统的出现和广泛应用,使计算机和网络进入了后PC时代。

TMS320VC5402的并行引导装载方案的研究与设计摘要:介绍了TMS320VC5402并行Bootloader的原理,分析了设计过程中需要考虑的重点问题并提出了解决问题的可靠的电路方案,设计的电路具有良好的可扩展性。

关键词:TMS320VC5402 Bootloader CPLD EPROMTMS320VC5402(以下简称C5402)是德州仪器公司1999年10月推出的性价比极高的定点数字信号处理器(DSP)。

与TMS32054X系列的其它芯片相比,C5402以其独有的高性能、低功耗和低价格特性,使得一推出就受到业内用户的欢迎。

它大多应用在如机顶盒(STB)、数字无线通信等要求能脱机运行的内嵌式系统中。

但它的内部结构和片内掩模的引导装载 (Bootloader)程序与C54X系列的其它DSP处理器有较大差异。

C5402为脱机运行提供了五种启动装载模式:HPI端口启动模式、标准串口启动模式、I/O口启动模式、串口EEPROM启动模式和并行启动方式。

对于以C5402为核心的独立系统中,并口加载方案被认为是最佳的。

因为前三种方案只适用于由其它处理器为C5402提供运行代码的多处理器系统中,后两种方案虽然都可以适应以C5402为核心的独立系统,但是串口EEPROM 启动模式中只支持价格偏高的SPI端口EEPROM,而并口启动模式却可以采用EPROM,而且并行EPROM和FLASH种类很多,有的价格较低,因而可以充分体现系统的性价比优势。

基于实践经验,本文详细介绍并行Bootloader的实现方法和方案设计重点,并介绍一种方便可靠的可扩展EPROM Bootloader方案。

1 C5402的Bootloader原理C5402的Bootloader在系统加电时把外部源程序传送到内部存储器或内部程序空间。

它允许程序被存放在外部慢速的存储器中,并调到高速的存储器中运行。

这可大大减小C5402内部RAM掩模的需要,降低电路设计的成本。

两类DSP芯片的引导过程分析摘要:详细分析了TI公司TMS320C40和TMS320VC5402两类DSP芯片的系统引导特点。

在了解机理的基础上,叙述了工程设计中创建系统引导表的具体步骤,给出了创建步骤中所需的键接文件范例,并进行了说明。

关键词:TMS320C40 TMS320VC5402 系统引导引导表目前,DSP芯片正逐渐应用到电子设计中,其中应用最广泛的是TI公司生产的DSP 系列产品。

笔者在工程项目的开发中,对TMS320C40和TMS320VC5402(以下简称C40和C5402)进行了系统的研究,并成功的实现了DSP的脱机运行。

本文希望通过对C40和C5402两种芯片系统引导的描述使大家了解设计DSP系列引导的步骤,能够利用DSP设计自己的设备。

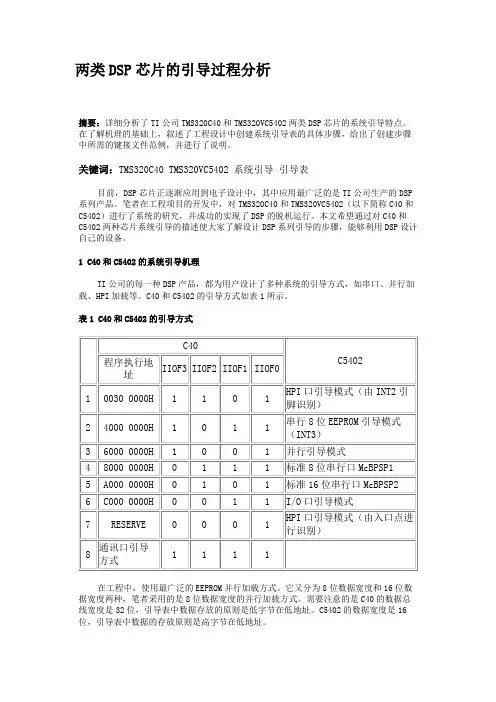

1 C40和C5402的系统引导机理TI公司的每一种DSP产品,都为用户设计了多种系统的引导方式,如串口、并行加载、HPI加载等。

C40和C5402的引导方式如表1所示。

表1 C40和C5402的引导方式C40C5402 程序执行地址IIOF3 IIOF2 IIOF1 IIOF01 0030 0000H 1 1 0 1 HPI口引导模式(由INT2引脚识别)2 4000 0000H 1 0 1 1 串行8位EEPROM引导模式(INT3)3 6000 0000H 1 0 0 1 并行引导模式4 8000 0000H 0 1 1 1 标准8位串行口McBPSP15 A000 0000H 0 1 0 1 标准16位串行口McBPSP26 C000 0000H 0 0 1 1 I/O口引导模式7 RESERVE 0 0 0 1 HPI口引导模式(由入口点进行识别)8 通讯口引导方式1 1 1 1在工程中,使用最广泛的EEPROM并行加载方式。

它又分为8位数据宽度和16位数据宽度两种,笔者采用的是8位数据宽度的并行加载方式。

需要注意的是C40的数据总线宽度是32位,引导表中数据存放的原则是低字节在低地址。

TMS320VC5402 DSP的并行I/O引导装载方法研究TMS320VC5402(以下简称C5402)是德州仪器公司(TI)1999年10月推出的性价比极高(目标价格仅为5美元)的定点数字信号处理器(DSP)。

C5402主要特点如下[1]:·操作速率达100MIPS;·具有先进的多总线结构,三条16位数据存储器总线和一条程序存储器总线;·40位算术逻辑单元(ALU),包括一个40位桶形移位器和两个40位累加器;·一个17×17乘法器和一个40位专用加法器,允许16位带/不带符号的乘法;·整合维特比加速器,用于提高维特比编译码的速度;·单周期正规化及指数译码;·8个辅助寄存器及一个软件栈,允许使用业界最先进的定点DSP C语言编译器;·数据/程序寻址空间1M×16bit,内置4K×16bit ROM和16K×16bit RAM;·内置可编程等待状态发生器、锁相环(PLL)时钟产生器、两个多通道缓冲串行口、一个8位并行与外部处理器通信的HPI口、2个16位定时器以及6通道DMA控制器;·低功耗,工作电源有3V和1.8V(内核),特别适合电池供电设备。

由此可见,与TMS32054X系列的其它芯片相比,C5402以其独有的高性能、低功耗和低价格特性,使得一推出就受到业内用户的欢迎。

但它的内部结构和片内掩模的引导装载(Bootloader)程序与C54X系列的其它DSP处理器[2]有较大的差异,而它的应用对象又大多是要求能脱机运行,如机顶盒(STB)、个人数字助理(PDA)和数字无线通信等内嵌式系统。

为此,本文立足我们的实践经验,简单介绍C5402 Bootloader程序分析和实现方法,并较为详细地介绍并行I/O Bootloader方法。

1 几种引导装载方法C5402片内掩模的Bootloader用于在上电复位时把用户程序从外部引导到高速RAM中,以保证其全速运行。

TMS320VC5402并行引导装载方案设计

凌祥;姜永华;高伟亮;严飞

【期刊名称】《海军航空工程学院学报》

【年(卷),期】2004(019)006

【摘要】主要介绍了DSP TMS320VC5402芯片并行引导装载的实现方案.对硬件电路设计和配置文件编写过程中的要点作了讨论,并给出了实例.

【总页数】3页(P689-691)

【作者】凌祥;姜永华;高伟亮;严飞

【作者单位】海军航空工程学院研究生管理大队;海军航空工程学院电子信息工程系,烟台,264001;海军航空工程学院研究生管理大队;海装驻航天科工集团二院代表室,北京,100083

【正文语种】中文

【中图分类】TP301

【相关文献】

1.TMS320VC5402并行引导装载方法的研究与设计 [J], 李国辉;刘立新;杨宏

2.TMS320VC5402外部并行引导装载方法的研究 [J], 陈斌;施克仁;郭大勇

3.TMS320VC5402 DSP并行8bit EPROM引导装载方法研究 [J], 庾新林

4.TMS320VC5402的并行引导装载方案的研究与设计 [J], 孙友伟;潘瑜;傅丰林

5.TMS320VC5402 DSP的并行I/O引导装载方法研究 [J], 韦江维;廖义奎;农建波;班世炳;李映超

因版权原因,仅展示原文概要,查看原文内容请购买。

TMS320VC5402 8位并行自举引导方案的研究

沈琰

【期刊名称】《电脑知识与技术》

【年(卷),期】2006(000)002

【摘要】在基于DSP的数字信号处理系统中,为了保证掉电时程序不丢失,总是将程序保存在非易失的外部存储器中,以便系统加电时将其引导到DSP内部的RAM 中执行.文中对TMS320VC5402 DSP 8位并行自举引导的过程进行了介绍,设计了8位EEPROM并行自举引导的实现电路,并给出了创建引导表的具体步骤.

【总页数】2页(P161-162)

【作者】沈琰

【作者单位】山东省东营职业学院,山东,东营,257091;东南大学,江苏,南京,210096【正文语种】中文

【中图分类】TP338

【相关文献】

1.TMS320VC5402并行引导装载方案设计 [J], 凌祥;姜永华;高伟亮;严飞

2.TMS320VC5402片外存储器扩展及自举引导程序的设计 [J], 刘苗

3.DSP芯片TMS320VC5402的并行自举加载方法 [J], 孙军英;刘波粒

4.TMS320VC5402的并行引导装载方案的研究与设计 [J], 孙友伟;潘瑜;傅丰林

5.TMS320VC5402系统的Flash存储器并行自举与实现 [J], 柯健

因版权原因,仅展示原文概要,查看原文内容请购买。

’C5402 DSP自举引导方法的分析与研究摘要: 介绍’C5402 DSP芯片几种自举引导方法的特点,对最常用的并行自举引导方式进行了深入的分析及研究,并通过实例说明建立自举表的步骤及应注意的问题。

关键词: 数字信号处理器(DSP) 自举引导并行引导在DSP领域,TI公司(德州仪器公司)一直处于世界霸主地位,它生产的TMS320系列DSP芯片以其独特的哈佛结构、硬件密集型方案和灵活的指令系统成为数字信号处理器产业中的领先者[1]。

其C5000系列DSP芯片具有功耗小、高度并行等优点,可以满足众多领域的实时处理要求。

尤其是新近推出的TMS320VC5402及TMS320UC5402(简称’C5402)以其独有的高性能、低功耗及低价位等优势,在推出之初便受到业界人士的普遍欢迎。

为充分利用DSP快速运行的优点,通常希望用户程序能在DSP中高速运行,这就需要运用DSP自举引导功能。

本文以’C5402为例,说明自举引导的特点及自举表建立的步骤。

1 几种自举引导方式1.1 自举引导方式简介众所周知,欲获得全速的DSP运行速度,方法之一是在DSP芯片出厂前将用户程序掩膜在其片内的ROM上。

这种方法对大部分应用场合并不适用,且成本很高。

对大多数用户而言,可行的方法是利用DSP自举引导功能。

Bootlooader(自举引导程序,也称引导装载程序)是在出厂前固化在DSP芯片内ROM中的一段程序代码,其主要功能是在上电或复位时将用户程序从外部加载至程序存储器(片内RAM或扩展的RAM)中,以便实现高速运行。

因此,用这种方法可以以较低的成本实现高速运行。

不同型号的DSP,其Bootlooader也不同。

如TMS320C54X 系列的DSP提供了四种自举引导方法[2]:并行EPROM、并行I/O口、串行口及主机接口HPI自举引导方式,它们适用于不同的应用场合。

1.2 ’C5402 DSP自举引导方式新近推出的’C5402 DSP片内ROM掩膜的Bootlooader程序与TMS320C54X系列的其它DSP有较大的不同,它包括以下五种自举引导方式:主机接口HPI、并行口、标准串行口、8位串行EEPROM及I/O口自举引导方式。

一种新的TMS320VC5402 DSP上电引导程序的设计方法赵锋荣;卢继平

【期刊名称】《电子产品世界》

【年(卷),期】2002(000)023

【摘要】本文介绍了TMS320VC5402DSP的存储器资源配置,针对用户经常面临的扩展存储器及上电引导加载方案设计中存在的问题,提供了一种实用的扩展存储器设计方案,重点讲述了在这种存储器资源配置的基础上,利用FLASH存储器的在系统编程技术,设计和编写符合系统要求的上电引导程序的方法.

【总页数】3页(P56-58)

【作者】赵锋荣;卢继平

【作者单位】重庆大学电气工程学院;重庆大学电气工程学院

【正文语种】中文

【中图分类】TP3

【相关文献】

1.一种实用的对DSP芯片(TMS320VC5402)进行混合编程方法 [J], 潘国栋;王天明;赵春晖

2.一种DSP处理器接口驱动程序设计方法 [J], 李莉

3.一种新的TMS320VC5402DSP上电引导程序的设计方法 [J], 赵锋荣;卢继平

4.一种保护系统快速下电上电的设计方法 [J], 官亚雄

5.一种跳频信号解调的多核DSP设计方法 [J], 李辉

因版权原因,仅展示原文概要,查看原文内容请购买。