74ACTQ00PCX中文资料

- 格式:pdf

- 大小:102.77 KB

- 文档页数:7

74系列芯片功能大全7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动。

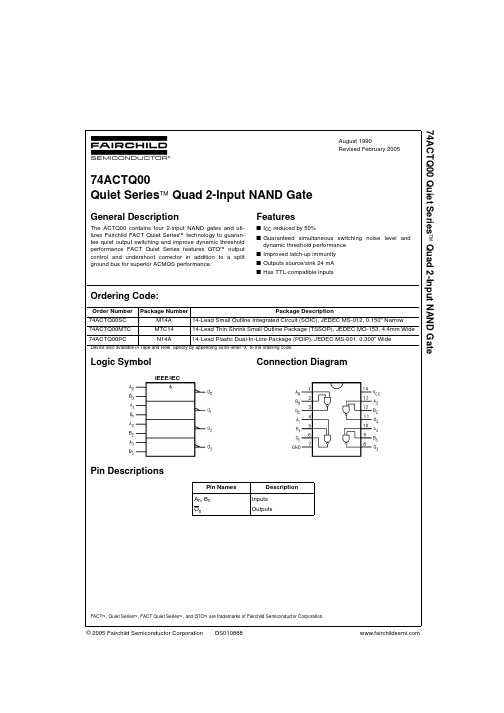

© 2005 Fairchild Semiconductor Corporation DS010888August 1990Revised February 200574ACTQ00 Quiet Series ¥ Quad 2-Input NAND Gate74ACTQ00Quiet Series ¥ Quad 2-Input NAND GateGeneral DescriptionThe ACTQ00 contains four 2-input NAND gates and uti-lizes Fairchild FACT Quiet Series ¥ technology to guaran-tee quiet output switching and improve dynamic threshold performance FACT Quiet Series features GTO ¥ output control and undershoot corrector in addition to a split ground bus for superior ACMOS performance.Featuress I CC reduced by 50%s Guaranteed simultaneous switching noise level and dynamic threshold performance s Improved latch-up immunity s Outputs source/sink 24 mA s Has TTL-compatible inputsOrdering Code:Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.Logic SymbolIEEE/IECConnection DiagramPin DescriptionsFACT ¥, Quiet Series ¥, FACT Quiet Series ¥, and GTO ¥ are trademarks of Fairchild Semiconductor Corporation.Order Number Package NumberPackage Description74ACTQ00SC M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow 74ACTQ00MTC MTC1414-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide 74ACTQ00PCN14A14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" WidePin Names Description A n , B n Inputs O nOutputs 274A C T Q 00Absolute Maximum Ratings (Note 1)Recommended Operating ConditionsNote 1: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, with-out exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation outside databook specifications.DC Electrical CharacteristicsNote 2: All outputs loaded; thresholds on input associated with output under test.Note 3: Maximum test duration 2.0 ms, one output loaded at a time.Note 4: DIP package.Note 5: Max number of outputs defined as (n). Data inputs are 0V to 3V. One output @ GND.Note 6: Max number of data inputs (n) switching. (n 1) inputs switching 0V to 3V. Input-under-test switching: 3V to threshold (V ILD ),0V to threshold (V IHD ), f 1 MHz.Supply Voltage (V CC ) 0.5V to 7.0VDC Input Diode Current (I IK )V I 0.5V 20 mA V I V CC 0.5V 20 mADC Input Voltage (V I )0.5V to V CC 0.5VDC Output Diode Current (I OK )V O 0.5V 20 mA V O V CC 0.5V 20 mADC Output Voltage (V O ) 0.5V to V CC 0.5VDC Output Source or Sink Current (I O )r 50 mA DC V CC or Ground Current per Output Pin (I CC or I GND )r 50 mAStorage Temperature (T STG ) 65q C to 150q CDC Latch-up Sourceor Sink Current r 300 mA Junction Temperature (T J )PDIP140q CSupply Voltage (V CC ) 4.5V to 5.5V Input Voltage (V I )0V to V CC Output Voltage (V O )0V to V CCOperating Temperature (T A ) 40q C to 85q CMinimum Input Edge Rate ('V/'t)V IN from 0.8V to 2.0V 125 mV/nsV CC @ 4.5V, 5.5VSymbol ParameterV CC T A 25q C T A 40q C to 85q C Units Conditions (V)Typ Guaranteed LimitsV IH Minimum HIGH Level 4.5 1.5 2.0 2.0V V OUT 0.1V Input Voltage 5.5 1.5 2.0 2.0or V CC 0.1V V IL Maximum LOW Level 4.5 1.50.80.8V V OUT 0.1V Input Voltage 5.5 1.50.80.8or V CC 0.1V V OHMinimum HIGH Level 4.5 4.49 4.4 4.4VI OUT 50 P A Output Voltage5.5 5.495.4 5.4V IN V IL or V IH4.5 3.86 3.76VI OH 24 mA 5.54.864.76I OH 24 mA (Note 2)V OLMaximum LOW Level 4.50.0010.10.1VI OUT 50 P A Output Voltage5.50.0010.10.1V IN V IL or V IH4.50.360.44V I OL 24 mA5.50.360.44I OL 24 mA (Note 2)I IN Maximum Input Leakage Current 5.5r 0.1r 1.0P A V I V CC , GND I CCT Maximum I CC /Input 5.50.61.5mA V I V CC2.1V I OLD Minimum Dynamic 5.575mA V OLD 1.65V Max I OHD Output Current (Note 3)5.5 75mA V OHD 3.85V Min I CC Maximum Quiescent Supply Current 5.5 2.020.0P A V IN V CC or GND V OLP Quiet Output Maximum Dynamic 5.01.11.5VFigure 1, Figure 2V OL(Note 4)(Note 5)V OLV Quiet Output Minimum Dynamic 5.0 0.6 1.2V Figure 1, Figure 2V OL(Note 4)(Note 5)V IHD Minimum HIGH Level 5.0 1.9 2.2V (Note 4)(Note 6)Dynamic Input Voltage V ILDMaximum LOW Level 5.01.20.8V(Note 4)(Note 6)Dynamic Input Voltage74ACTQ00AC Electrical CharacteristicsNote 7: Voltage Range 5.0 is 5.0V r 0.5V.Note 8: Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (t OSHL ) or LOW-to-HIGH (t OSLH ). Parameter guaranteed by design.CapacitanceV CCT A 25q C T A 40q C to 85q CSymbol Parameter(V)C L 50 pFC L 50 pF Units(Note 7)Min TypMax Min Max t PLH Propagation Delay 5.0 2.07.5 2.08.0ns Data to Output t PHL Propagation Delay 5.0 2.07.5 2.08.0ns Data to Output t OSHL Output to Output 5.00.5 1.01.0ns t OSLHSkew (Note 8)Symbol ParameterTyp Units ConditionsC IN Input Capacitance4.5pF V CC OPEN C PDPower Dissipation Capacitance74pFV CC 5.0V 474A C T Q 00FACT ¥Noise CharacteristicsThe setup of a noise characteristics measurement is critical to the accuracy and repeatability of the tests. The following is a brief description of the setup used to measure the noise characteristics of FACT.Equipment:Hewlett Packard Model 8180A Word Generator PC-163A Test FixtureTektronics Model 7854 OscilloscopeProcedure:1.Verify Test Fixture Loading: Standard Load 50 pF,500:.2.Deskew the HFS generator so that no two channelshave greater than 150 ps skew between them. This requires that the oscilloscope be deskewed first. It is important to deskew the word generator channels before testing. This will ensure that the outputs switch simultaneously.3.Terminate all inputs and outputs to ensure proper load-ing of the outputs and that the input levels are at the correct voltage.4.Set the HFS generator to toggle all but one output at afrequency of 1 MHz. Greater frequencies will increase DUT heating and effect the results of the measure-ment.5.Set the HFS generator input levels at 0V LOW and 3VHIGH for ACT devices and 0V LOW and 5V HIGH for AC devices. Verify levels with an oscilloscopeNote 9: V OHV and V OLP are measured with respect to ground reference.Note 10: Input pulses have the following characteristics: f 1 MHz, t r 3ns,t f 3 ns, skew 150 ps.FIGURE 1. Quiet Output Noise Voltage WaveformsV OLP /V OLV and V OHP /V OHV :•Determine the quiet output pin that demonstrates the greatest noise levels. The worst case pin will usually be the furthest from the ground pin. Monitor the output volt-ages using a 50: coaxial cable plugged into a standard SMB type connector on the test fixture. Do not use an active FET probe.•Measure V OLP and V OLV on the quiet output during the worst case transition for active and enable. Measure V OHP and V OHV on the quiet output during the worst case active and enable transition.•Verify that the GND reference recorded on the oscillo-scope has not drifted to ensure the accuracy and repeat-ability of the measurements.V ILD and V IHD :•Monitor one of the switching outputs using a 50: coaxial cable plugged into a standard SMB type connector on the test fixture. Do not use an active FET probe.•First increase the input LOW voltage level, V IL , until the output begins to oscillate or steps out a min of 2 ns.Oscillation is defined as noise on the output LOW level that exceeds V IL limits, or on output HIGH levels that exceed V IH limits. The input LOW voltage level at which oscillation occurs is defined as V ILD .•Next decrease the input HIGH voltage level.V IH until the output begins to oscillate or steps out a mine of 2 ns.Oscillation is defined as noise on the output LOW level that exceeds V IL limits, or on output HIGH levels that exceed V IH limits. The input HIGH voltage level at which oscillation occurs is defined as V IHD .•Verify that the GND reference recorded on the oscillo-scope has not drifted to ensure the accuracy and repeat-ability of the measurements.FIGURE 2. Simultaneous Switching Test Circuit 74ACTQ00Physical Dimensions inches (millimeters) unless otherwise noted14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" NarrowPackage Number M14A 674A C T Q 00Physical Dimensionsinches (millimeters) unless otherwise noted (Continued)14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePackage Number MTC14774ACTQ00 Quiet Series ¥ Quad 2-Input NAND GatePhysical Dimensions inches (millimeters) unless otherwise noted (Continued)14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" WidePackage Number N14AFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

74系列芯片功能大全+4000系列的选型说明74与40是所有外围最常用的IC,其中包括SN74HC595 8位移位寄存器/锁存器(即串转并转换)等十分重要的芯片。

7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D驱动器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器SN74LSOO 四2输入与非门SN74LSO2 四2输入与非门SN74LS04 六反相器SN74LS06 六反相缓冲器/驱动器SN74LS08 四2输入与非门SN74LS10 三3输入与非门SN74LS12 三3输入与非门SN74LS14 六反相器.斯密特触发SN74LS16 六反相缓冲器/触发器SN74LS20 双4输入与门SN74LS22 双4输入与门SN74LS26 四2输入与非门SN74LS28 四输入端或非缓冲器SN74LS32 四2输入或门SN74LS37 四输入端与非缓冲器SN74LS40 四输入端与非缓冲器SN74LS47 BCD-七段译码驱动器SN74LS49 BCD-七段译码驱动器SN74LS54 四输入与或非门SN74LS63 六电流读出接口门SN74LS74 双D触发器SN74LS76 双J-K触发器SN74LS83 双J-K触发器SN74LS86 四2输入异或门SN74LS90 4位十进制波动计数器SN74LS92 12分频计数器SN74LS96 5位移位寄存器SN74LS109 正沿触发双J-K触发器SN74LS113 双J-K负沿触发器SN74LS121 单稳态多谐振荡器SN74LS123 双稳态多谐振荡器SN74LS125 三态缓冲器SN74LS131 3-8线译码器SN74LS137 地址锁存3-8线译码器SN74LS139 双2-4线译码-转换器SN74LS147 10-4线优先编码器SN74LS153 双4选1数据选择器SN74LS155 双2-4线多路分配器SN74LS157 四2选1数据选择器SN74LS160 同步BDC十进制计数器SN74LS162 同步BDC十进制计数器SN74LS164 8位串入并出移位寄存SN74LS166 8位移位寄存器SN74LS169 4位可逆同步计数器SN74LS172 16位多通道寄存器堆SN74LS174 6D型触发器SN74LS176 可预置十进制计数器SN74LS182 超前进位发生器SN74LS189 64位随机存储器SN74LS191 二进制同步可逆计数器SN74LS193 二进制可逆计数器SN74LS195 并行存取移位寄存器SN74LS197 可预置二进制计数器SN74LS238 3-8线译码/多路转换器SN74LS241 八缓冲/驱动/接收器SN74LS243 四总线收发器SN74LS245 八总线收发器SN74LS248 BCD-七段译码驱动器SN74LS251 三态8-1数据选择器SN74LS256 双四位选址锁存器SN74LS258 四2选1数据选择器SN74LS260 双5输入或非门SN74LS266 四2输入异或非门SN74LS275 七位树型乘法器SN74LS279 四R-S触发器SN74LS283 4位二进制全加器SN74LS293 4位二进制计数器SN74LS365 六缓冲器带公用启动器SN74LS367 六总线三态输出缓冲器SN74LS373 8D锁存器SN74LS375 4位双稳锁存器SN74LS386 四2输入异或门SN74LS393 双4位二进制计数器SN74LS574 8位D型触发器SN74LS684 8位数字比较器SN74LSO1 四2输入与非门SN74LS05 六反相器SN74LS07 六缓冲器/驱动器SN74LS09 四2输入与非门SN74LS11 三3输入与非门SN74LS13 三3输入与非门SN74LS15 三3输入与非门SN74LS17 六反相缓冲器/驱动器SN74LS21 双4输入与门SN74LS25 双4输入与门SN74LS27 三3输入与非门SN74LS30 八输入端与非门SN74LS33 四2输入或门SN74LS38 双2输入与非缓冲器SN74LS42 BCD-十进制译码器SN74LS48 BCD-七段译码驱动器SN74LS51 三3输入双与或非门SN74LS55 四4输入与或非门SN74LS73 双J-K触发器SN74LS75 4位双稳锁存器SN74LS78 双J-K触发器SN74LS85 4位幅度比较器SN74LS88 4位全加器SN74LS91 8位移位寄存器SN74LS93 二进制计数器SN74LS95 4位并入并出寄存器SN74LS107 双J-K触发器SN74LS112 双J-K负沿触发器SN74LS114 双J-K负沿触发器SN74LS122 单稳态多谐振荡器SN74LS124 双压控振荡器SN74LS126 四3态总线缓冲器SN74LS132 二输入与非触发器SN74LS136 四异或门SN74LS138 3-8线译码/转换器SN74LS145 BCD十进制译码/驱动器SN74LS148 8-3线优先编码器SN74LS151 8选1数据选择器SN74LS154 4-16线多路分配器SN74LS156 双2-4线多路分配器SN74LS158 四2选1数据选择器SN74LS161 4位二进制计数器SN74LS163 4位二进制计数器SN74LS165 8位移位寄存器SN74LS168 4位可逆同步计数器SN74LS170 4x4位寄存器堆SN74LS173 4D型寄存器SN74LS175 4D烯触发器SN74LS181 运算器/函数发生器SN74LS183 双进位保存全价器SN74LS190 同步BCD十进制计数器SN74LS192 BCD-同步可逆计数器SN74LS194 双向通用移位寄存器SN74LS196 可预置十进制计数器SN74LS221 双单稳态多谐振荡器SN74LS240 八缓冲/驱动/接收器SN74LS242 四总线收发器SN74LS244 八缓冲/驱动/接收器SN74LS247 BCD-七段译码驱动器SN74LS249 BCD-七段译码驱动器SN74LS253 双三态4-1数据选择器SN74LS257 四3态2-1数据选择器SN74LS259 8位可寻址锁存器SN74LS261 2x4位二进制乘发器SN74LS273 八进制D型触发器SN74LS276 四J-K触发器SN74LS280 9位奇偶数发生校检器SN74LS290 十进制计数器SN74LS295 4位双向通用移位寄存器SN74LS366 六缓冲器带公用启动器SN74LS368 六总线三态输出反相器SN74LS374 8D触发器SN74LS377 8位单输出D型触发器SN74LS390 双十进制计数器SN74LS573 8位三态输出D型锁存器SN74LS670 8位数字比较器SN74HC00 四2输入与非门SN74HC02 四2输入或非门SN74HC03 四2输入或非门SN74HC04 六反相器SN74HC05 六反相器SN74HC08 四2输入与门SN74HC10 三3输入与非门SN74HC11 三3输入与门SN74HC14 六反相器/斯密特触发器SN74HC20 双四输入与门SN74HC21 双四输入与非门SN74HC27 三3输入与非门SN74HC30 八输入端与非门SN74HC32 四2输入或门SN74HC42 BCD十进制译码器SN74HC73 双J-K触发器SN74HC74 双D型触发器SN74HC76 双J-K触发器SN74HC86 四2输入异或门SN74HC107 双J-K触发器SN74HC113 双J-K负沿触发器SN74HC123 双稳态多谐振荡器SN74HC125 三态缓冲器SN74HC126 四三态总线缓冲器SN74HC132 二输入与非缓冲器SN74HC137 二输入与非缓冲器SN74HC138 3-8线译码/解调器SN74HC139 双2-4线译码/解调器SN74HC148 8选1数据选择器SN74HC151 双4选1数据选择器SN74HC154 4-16线多路分配器SN74HC157 四2选1数据选择器SN74HC161 4位二进制计数器SN74HC163 4位二进制计数器SN74HC164 8位串入并出移位寄存器SN74HC165 8位移位寄存器SN74HC173 4D型触发器SN74HC174 6D触发器SN74HC175 4D型触发器SN74HC191 二进制同步可逆计数器SN74HC221 双单稳态多谐振荡器SN74HC238 3-8线译码器SN74HC240 八缓冲器SN74HC244 八总线3态输出缓冲器SN74HC245 八总线收发器SN74HC251 三态8-1数据选择器SN74HC259 8位可寻址锁存器SN74HC266 四2输入异或非门SN74HC273 8D型触发器SN74HC367 六缓冲器/总线驱动器SN74HC368 六缓冲器/总线驱动器SN74HC373 8D锁存器SN74HC374 8D触发器SN74HC393 双4位二进制计数器SN74HC541 8位三态输出缓冲器SN74HC573 8位三态输出D型锁存器SN74HC574 8D型触发器SN74HC595 8位移位寄存器/锁存器SN74HC4028 7级二进制串行加数器SN74HC4046 锁相环SN74HC4050 六同相缓冲器SN74HC4051 8选1模拟开关SN74HC4053 三2选1模拟开关SN74HC4060 14位计数/分频/振荡器SN74HC4066 四双相模拟开关SN74HC4078 3输入端三或门SN74HC4511 7段锁存/译码驱动器SN74HC4520 双二进制加法计数器74F00 高速四2输入与非门74F02 高速四2输入或非门74F04 高速六反相器74F08 高速四2输入与门74F10 高速三3输入与门74F14 高速六反相斯密特触发74F32 高速四2输入或门74F38 高速四2输入或门74F74 高速双D型触发器74F86 高速四2输入异或门74F139 高速双2-4线译码/驱动器74F151 高速双2-4线译码/驱动器74F153 高速双4选1数据选择器74F157 高速双4选1数据选择器74F161 高速6D型触发器74F174 高速6D型触发器74F175 高速4D型触发器74F244 高速八总线3态缓冲器74F245 高速八总线收发器74F373 高速8D锁存器SN74HCT04 六反相器74系列芯片资料反相器驱动器 LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门 LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门 LS02 LS32 LS51 LS64 LS65异或门比较器 LS86译码器 LS138 LS139寄存器 LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04┌┴─┴─┴─┴─┴─┴─┴┐六非门(OC门) 74LS05_ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06Y = A )││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 74L S07│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐_ │14 13 12 11 10 9 8│Y =A+C )│四总线三态门 74LS125 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位总线驱动器 74LS245│20 19 18 17 16 15 14 13 12 11│)│ DIR= 1 A=>B│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = AB )│ 2输入四正与门 74LS08 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS0 0│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐___ │14 13 12 11 10 9 8│Y = ABC )│ 3输入三正与非门 74LS10 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ 8输入与非门 74LS30│ 1 2 3 4 5 6 7│ ________└┬─┬─┬─┬─┬─┬─┬┘ Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或门 74LS32│14 13 12 11 10 9 8│)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或非门 74LS02│14 13 12 11 10 9 8│ ___)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴─┴─┴─┴─┴─┴─┴┐双与或非门 74S51│14 13 12 11 10 9 8│ _____)│ 2Y = AB+DE│ 1 2 3 4 5 6 7│ _______└┬─┬─┬─┬─┬─┬─┬┘ 1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴─┴─┴─┴─┴─┴─┴┐ 4-2-3-2与或非门 74S64 74S65(OC门)│14 13 12 11 10 9 8│ ______________ )│ Y = ABCD+EF+GHI+JK │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门 74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ _ _│ 1 2 3 4 5 6 7│ Y=AB+AB└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器 74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器 74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _ ┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=A B C Y1=A B B Y2=A B C Y3=A B C│16 15 14 13 12 11 10 9 │)│ __ _ _ ___ __ _ __│ 1 2 3 4 5 6 7 8│ Y4=A B C Y5=A B C Y6=A B C Y7 =A B C└┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器 74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __ ┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B│16 15 14 13 12 11 10 9 │)│ __ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│ Y0=1A 1B Y1=1A 1B Y2=1A 1B Y3 =1A 1B└┬─┬─┬─┬─┬─┬─┬─┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器 74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴─┴─┴─┴─┴─┴─┴┐双D触发器 74LS74│14 13 12 11 10 9 8 │)││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位锁存器 74LS373│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND型号器件名称厂牌[数据表]SN7400四2输入端与非门 TI[DATA]SN740 1四2输入端与非门(OC) SN7402四2输入端或非门 TI[DATA]SN7403四2输入端与非门(OC)TI[DATA]SN7404六反相器 TI[DATA]SN7405六反相器(O C)TI[DATA]SN7406六高压输出反相器 (OC,30V)TI[DATA]SN7407六高压输出缓冲,驱动器(OC,30V)TI[DATA]SN7408四2输入端与门 TI[DATA]SN7409四2输入端与门(OC)TI[DATA]SN7410三3输入端与非门 TI[DATA]SN7412三3输入端与非门(OC)TI[DATA]SN7413双4输入端与非门 TI[DATA]SN7414六反相器TI[DATA]SN7416六高压输出反相缓冲/驱动器 I[DATA]SN7417六高压输出缓冲/驱动器(OC,15V)TI[DATA]SN7420双4输入端与非门 TI[DATA]SN7422双4输入端与非门(OC)TI[DATA]SN7423可扩展双4输入端或非门 TI[DATA]SN7425双4输入端或非门TI[DATA]SN7426四2输入端高压输出与非缓冲器 [DATA]SN7427三3输入端或非门TI[DATA]SN7428四2输入端或非缓冲器 I[DATA]SN74308输入端与非门TI[DATA]SN7432四2输入端或门74756Dual 4-bit open-collector inverting buffer/line driver.+---+--+---+/1OE |1 +--+ 20| VCC1A1 |2 19| /2OE/2Y4 |3 18| /1Y11A2 |4 17| 2A4/2Y3 |5 74 16| /1Y21A3 |6 756 15| 2A3/2Y2 |7 14| /1Y31A4 |8 13| 2A2/2Y1 |9 12| /1Y4GND |10 11| 2A1+----------+74757Dual 4-bit open-collector noninverting buffer/line driver.One active low, one active high output enable.+---+--+---+/1OE |1 +--+ 20| VCC1A4 |2 19| 2OE2Y1 |3 18| 1Y11A3 |4 17| 2A42Y2 |5 74 16| 1Y21A2 |6 757 15| 2A32Y3 |7 14| 1Y31A1 |8 13| 2A22Y4 |9 12| 1Y4GND |10 11| 2A1+----------+747584-bit open-collector inverting bus transceiver.Two enable pins control output enables, one active high and one active low.+---+--+---+/GAB |1 +--+ 14| VCC|2 13| GBAA1 |3 74 12|A2 |4 758 11| B1A3 |5 10| B2A4 |6 9| B3GND |7 8| B4+----------+74760Dual 4-bit open-collector noninverting buffer/line driver.+---+--+---+/1OE |1 +--+ 20| VCC1A1 |2 19| /2OE2Y4 |3 18| 1Y11A2 |4 17| 2A42Y3 |5 74 16| 1Y21A3 |6 760 15| 2A32Y2 |7 14| 1Y31A4 |8 13| 2A22Y1 |9 12| 1Y4GND |10 11| 2A1+----------+* - 本贴最后修改时间:2002-12-9 18:46:59 修改者:autwl* - 修改原因:.autwl 发表于 2002-12-9 18:34 技术交流←返回版面补充1 ZT74804Hex 2-input NAND gates/line drivers.+---+--+---+ +---+---*---+ __1A |1 +--+ 20| VCC | A | B |/Y | /Y = AB1B |2 19| 6B +===+===*===+/1Y |3 18| 6A | 0 | 0 | 1 |2A |4 17| /6Y | 0 | 1 | 1 |2B |5 74 16| 5B | 1 | 0 | 1 |/2Y |6 804 15| 5A | 1 | 1 | 0 |3A |7 14| /5Y +---+---*---+3B |8 13| 4B/3Y |9 12| 4AGND |10 11| /4Y+----------+74805Hex 2-input NOR gates/line drivers.+---+--+---+ +---+---*---+ ___ 1A |1 +--+ 20| VCC | A | B |/Y | /Y = A+B1B |2 19| 6B +===+===*===+/1Y |3 18| 6A | 0 | 0 | 1 |2A |4 17| /6Y | 0 | 1 | 0 |2B |5 74 16| 5B | 1 | 0 | 0 |/2Y |6 805 15| 5A | 1 | 1 | 0 |3A |7 14| /5Y +---+---*---+3B |8 13| 4B/3Y |9 12| 4AGND |10 11| /4Y+----------+74808Hex 2-input AND gates/line drivers.+---+--+---+ +---+---*---+1A |1 +--+ 20| VCC | A | B | Y | Y = AB1B |2 19| 6B +===+===*===+1Y |3 18| 6A | 0 | 0 | 0 |2A |4 17| 6Y | 0 | 1 | 0 |2B |5 74 16| 5B | 1 | 0 | 0 |2Y |6 808 15| 5A | 1 | 1 | 1 |3A |7 14| 5Y +---+---*---+3B |8 13| 4B3Y |9 12| 4AGND |10 11| 4Y+----------+7482110-bit 3-state D flip-flop/bus driver.+---+--+---+ +---+---+---*---+/OE |1 +--+ 24| VCC |/OE|CLK| D | Q |D1 |2 23| Q1 +===+===+===*===+D2 |3 22| Q2 | 1 | X | X | Z |D3 |4 21| Q3 | 0 | / | 0 | 0 |D4 |5 20| Q4 | 0 | / | 1 | 1 |D5 |6 74 19| Q5 | 0 |!/ | X | - |D6 |7 821 18| Q6 +---+---+---*---+D7 |8 17| Q7D8 |9 16| Q8D9 |10 15| Q9D10 |11 14| Q10GND |12 13| CLK+----------+7482210-bit 3-state inverting D flip-flop/bus driver.+---+--+---+ +---+---+---*---+/OE |1 +--+ 24| VCC |/OE|CLK| D |/Q |D1 |2 23| /Q1 +===+===+===*===+D2 |3 22| /Q2 | 1 | X | X | Z |D3 |4 21| /Q3 | 0 | / | 0 | 1 |D4 |5 20| /Q4 | 0 | / | 1 | 0 |D5 |6 74 19| /Q5 | 0 |!/ | X | - |D6 |7 822 18| /Q6 +---+---+---*---+D7 |8 17| /Q7D8 |9 16| /Q8D9 |10 15| /Q9D10 |11 14| /Q10GND |12 13| CLK+----------+748239-bit 3-state D flip-flop/bus driver with clock enable and reset.+---+--+---+/OE |1 +--+ 24| VCCD1 |2 23| Q1D2 |3 22| Q2D3 |4 21| Q3D4 |5 20| Q4D5 |6 74 19| Q5D6 |7 823 18| Q6D7 |8 17| Q7D8 |9 16| Q8D9 |10 15| Q9/RST |11 14| /CLKENGND |12 13| CLK+----------+748258-bit 3-state D flip-flop/bus driver with three output enables, clock enable and reset.+---+--+---+/OE1 |1 +--+ 24| VCC/OE2 |2 23| /OE3D1 |3 22| Q1D2 |4 21| Q2D3 |5 20| Q3D4 |6 74 19| Q4D5 |7 825 18| Q5D6 |8 17| Q6D7 |9 16| Q7D8 |10 15| Q8/RST |11 14| /CLKENGND |12 13| CLK+----------+7482710-bit 3-state noninverting buffer/line driver.+---+--+---+/OE1 |1 +--+ 24| VCCA1 |2 23| Y1A2 |3 22| Y2A3 |4 21| Y3A4 |5 20| Y4A5 |6 742 19| Y5A6 |7 827 18| Y6A7 |8 17| Y7A8 |9 16| Y8A9 |10 15| Y9A10 |11 14| Y10GND |12 13| /OE2+----------+74832Hex 2-input OR gates/line drivers.+---+--+---+ +---+---*---+1A |1 +--+ 20| VCC | A | B | Y | Y = A+B1B |2 19| 6B +===+===*===+1Y |3 18| 6A | 0 | 0 | 0 |2A |4 17| 6Y | 0 | 1 | 1 |2B |5 74 16| 5B | 1 | 0 | 1 |2Y |6 832 15| 5A | 1 | 1 | 1 |3A |7 14| 5Y +---+---*---+3B |8 13| 4B3Y |9 12| 4AGND |10 11| 4Y+----------+748338-bit 3-state noninverting bus transceiver with parity generator/checker and parity register.+---+--+---+/OEA |1 +--+ 24| VCCA1 |2 23| B1A2 |3 22| B2A3 |4 21| B3A4 |5 20| B4A5 |6 74 19| B5A6 |7 833 18| B6A7 |8 17| B7A8 |9 16| B8/ERROR |10 15| PAR/CLR |11 14| /OEBGND |12 13| CLK+----------+7484110-bit 3-state transparent latch/bus driver.+---+--+---+ +---+---+---*---+/OE |1 +--+ 24| VCC |/OE| LE| D | Q |D1 |2 23| Q1 +===+===+===*===+D2 |3 22| Q2 | 1 | X | X | Z |D3 |4 21| Q3 | 0 | 0 | X | - |D4 |5 20| Q4 | 0 | 1 | 0 | 0 |D5 |6 74 19| Q5 | 0 | 1 | 1 | 1 |D6 |7 841 18| Q6 +---+---+---*---+D7 |8 17| Q7D8 |9 16| Q8D9 |10 15| Q9D10 |11 14| Q10GND |12 13| LE+----------+748439-bit 3-state transparent latch/bus driver with set and reset.+---+--+---+ +----+----+---+---+---*---+/OE |1 +--+ 24| VCC |/RST|/SET|/OE| LE| D | Q |D1 |2 23| Q1 +====+====+===+===+===*===+D2 |3 22| Q2 | 0 | 1 | 0 | X | X | 0 |D3 |4 21| Q3 | 1 | 0 | 0 | X | X | 0 |D4 |5 20| Q4 | X | X | 1 | X | X | Z |D5 |6 74 19| Q5 | 1 | 1 | 0 | 0 | X | - |D6 |7 843 18| Q6 | 1 | 1 | 0 | 1 | 0 | 0 |D7 |8 17| Q7 | 1 | 1 | 0 | 1 | 1 | 1 |D8 |9 16| Q8 +----+----+---+---+---*---+D9 |10 15| Q9/RST |11 14| /SETGND |12 13| LE+----------+748458-bit 3-state transparent latch/bus driver with three output enables, set and reset.+---+--+---+/OE1 |1 +--+ 24| VCC/OE2 |2 23| /OE3D1 |3 22| Q1D2 |4 21| Q2D3 |5 20| Q3D4 |6 74 19| Q4D5 |7 845 18| Q5D6 |8 17| Q6D7 |9 16| Q7D8 |10 15| Q8/RST |11 14| /SETGND |12 13| LE+----------+7485712-to-6 line inverting/noninverting data selector/multiplexer with masking and zero detect.+---+--+---+S0 |1 +--+ 24| VCC1A0 |2 23| S11A1 |3 22| 6A01Y |4 21| 6A12A0 |5 20| 6Y2A1 |6 74 19| 5A02Y |7 857 18| 5A13A0 |8 17| 5Y3A1 |9 16| 4A03Y |10 15| 4A1ZD |11 14| 4YGND |12 13| COMP+----------+7486110-bit 3-state noninverting bus transceiver.+---+--+---+/GBA |1 +--+ 24| VCCA1 |2 23| B1A2 |3 22| B2A3 |4 21| B3A4 |5 20| B4A5 |6 74 19| B5A6 |7 861 18| B6A7 |8 17| B7A8 |9 16| B8A9 |10 15| B9A10 |11 14| B10GND |12 13| /GAB+----------+748639-bit 3-state noninverting bus transceiver.+---+--+---+/GBA1 |1 +--+ 24| VCCA1 |2 23| B1A2 |3 22| B2A3 |4 21| B3A4 |5 20| B4A5 |6 74 19| B5A6 |7 863 18| B6A7 |8 17| B7A8 |9 16| B8A9 |10 15| B9/GBA2 |11 14| /GAB2GND |12 13| /GAB1+----------+748678-bit synchronous binary up/down counter with load, asynchronous reset and ripple carry outp ut.+---+--+---+S0 |1 +--+ 24| VCCS1 |2 23| /ENPP0 |3 22| Q0P1 |4 21| Q1P2 |5 20| Q2P3 |6 74 19| Q3P4 |7 867 18| Q4P5 |8 17| Q5P6 |9 16| Q6P7 |10 15| Q7/ENT |11 14| CLKGND |12 13| /RCO+----------+748698-bit synchronous binary up/down counter with load, reset and ripple carry output.+---+--+---+S0 |1 +--+ 24| VCCS1 |2 23| /ENPP0 |3 22| Q0P1 |4 21| Q1P2 |5 20| Q2P3 |6 74 19| Q3P4 |7 869 18| Q4P5 |8 17| Q5P6 |9 16| Q6P7 |10 15| Q7/ENT |11 14| CLKGND |12 13| /RCO+----------+74873Dual 4-bit 3-state transparent latch with reset.+---+--+---+/1RST |1 +--+ 24| VCC/1OE |2 23| 1LE1D1 |3 22| 1Q11D2 |4 21| 1Q21D3 |5 20| 1Q31D4 |6 74 19| 1Q42D1 |7 873 18| 2Q12D2 |8 17| 2Q22D3 |9 16| 2Q32D4 |10 15| 2Q4/2OE |11 14| 2LEGND |12 13| /2RST+----------+74874Dual 4-bit 3-state D flip-flops with reset.+---+--+---+ +----+---+---+---*---+ /1RST |1 +--+ 24| VCC |/RST|/OE|CLK| D | Q |/1OE |2 23| 1CLK +====+===+===+===*===+1D1 |3 22| 1Q1 | 0 | 1 | X | X | Z | 1D2 |4 21| 1Q2 | X | 0 | X | X | 0 | 1D3 |5 20| 1Q3 | 1 | 0 | / | 0 | 0 | 1D4 |6 74 19| 1Q4 | 1 | 0 | / | 1 | 1 |2D1 |7 874 18| 2Q1 | 1 | 0 |!/ | X | - |2D2 |8 17| 2Q2 +----+---+---+---*---+ 2D3 |9 16| 2Q32D4 |10 15| 2Q4/2OE |11 14| 2CLKGND |12 13| /2RST+----------+74878Dual 4-bit 3-state D flip-flops with reset.+---+--+---+ +----+---+---+---*---+ /1RST |1 +--+ 24| VCC |/RST|/OE|CLK| D | Q |/1OE |2 23| 1CLK +====+===+===+===*===+1D1 |3 22| 1Q1 | 0 | 1 | X | X | Z | 1D2 |4 21| 1Q2 | X | 0 | X | X | 0 | 1D3 |5 20| 1Q3 | 1 | 0 | / | 0 | 0 |1D4 |6 74 19| 1Q4 | 1 | 0 | / | 1 | 1 |2D1 |7 878 18| 2Q1 | 1 | 0 |!/ | X | - |2D2 |8 17| 2Q2 +----+---+---+---*---+2D3 |9 16| 2Q32D4 |10 15| 2Q4/2OE |11 14| 2CLKGND |12 13| /2RST+----------+748814-bit 16- arithmetic logic unit (ALU)+---+--+---+/B0 |1 +--+ 24| VCC/A0 |2 23| /A1S3 |3 22| /B1S2 |4 21| /A2S1 |5 20| /B2S0 |6 74 19| /A3CIN |7 881 18| /B3M |8 17| /G/F0 |9 16| COUT/F1 |10 15| /P/F2 |11 14| A=BGND |12 13| /F3+----------+748858-bit noninverting magnitude comparator with cascade inputs and latchable A inputs.+---+--+---+L+/A |1 +--+ 24| VCCIA<B |2 23| ALEIA>B |3 22| A7B7 |4 21| A6B6 |5 20| A5B5 |6 74 19| A4B4 |7 885 18| A3B3 |8 17| A2B2 |9 16| A1B1 |10 15| A0B0 |11 14| OA<BGND |12 13| OA>B+----------+748998-bit 3-state noninverting latchable bus transceiver with parity generator/checker and indep endent latch-enable inputs.+---+--+---+O//E |1 +--+ 28| VCC/ERRA |2 27| /OEABLEAB |3 26| B1A1 |4 25| B2A2 |5 24| B3A3 |6 23| B4A4 |7 74 22| B5A5 |8 899 21| B6A6 |9 20| B7A7 |10 19| B8A8 |11 18| BPARAPAR |12 17| LEBA/OEBA |13 16| /SELGND |14 15| /ERRB+----------+749568-bit 3-state noninverting latched transceiver.+---+--+---+LEAB |1 +--+ 24| VCCSAB |2 23| LEBADIR |3 22| SBAA1 |4 21| /OEA2 |5 20| B1A3 |6 74 19| B2A4 |7 956 18| B3A5 |8 17| B4A6 |9 16| B5A7 |10 15| B6A8 |11 14| B7GND |12 13| B8+----------+749908-bit transparent latch with readback.+---+--+---+/OERB |1 +--+ 20| VCCD1 |2 19| Q1D2 |3 18| Q2D3 |4 17| Q3D4 |5 74 16| Q4D5 |6 990 15| Q5D6 |7 14| Q6D7 |8 13| Q7D8 |9 12| Q8GND |10 11| LE+----------+749929-bit 3-state transparent latch with readback and reset.+---+--+---+/OERB |1 +--+ 24| VCCD1 |2 23| Q1D2 |3 22| Q2D3 |4 21| Q3D4 |5 20| Q4D5 |6 74 19| Q5D6 |7 992 18| Q6D7 |8 17| Q7D8 |9 16| Q8D9 |10 15| Q9/RST |11 14| /OEGND |12 13| LE+----------+7499410-bit transparent latch with readback.+---+--+---+/OERB |1 +--+ 24| VCCD1 |2 23| Q1D2 |3 22| Q2D3 |4 21| Q3D4 |5 20| Q4D5 |6 74 19| Q5D6 |7 994 18| Q6D7 |8 17| Q7D8 |9 16| Q8D9 |10 15| Q9D10 |11 14| Q10GND |12 13| LE+----------+741000Quad 2-input NAND gates with buffered output.+---+--+---+ +---+---*---+ __1A |1 +--+ 14| VCC | A | B |/Y | /Y = AB1B |2 13| 4B +===+===*===+/1Y |3 7410 12| 4A | 0 | 0 | 1 |2A |4 00 11| /4Y | 0 | 1 | 1 |2B |5 10| 3B | 1 | 0 | 1 |/2Y |6 9| 3A | 1 | 1 | 0 |GND |7 8| /3Y +---+---*---++----------+741004Hex inverters with buffered output.+---+--+---+ +---*---+ _ 1A |1 +--+ 14| VCC | A |/Y | /Y = A/1Y |2 13| 6A +===*===+2A |3 7410 12| /6Y | 0 | Z |/2Y |4 04 11| 5A | 1 | 0 |3A |5 10| /5Y +---*---+/3Y |6 9| 4AGND |7 8| /4Y+----------+741005Hex open-collector inverters with buffered output.+---+--+---+ +---*---+ _ 1A |1 +--+ 14| VCC | A |/Y | /Y = A/1Y |2 13| 6A +===*===+2A |3 7410 12| /6Y | 0 | Z |/2Y |4 05 11| 5A | 1 | 0 |3A |5 10| /5Y +---*---+/3Y |6 9| 4AGND |7 8| /4Y+----------+741032Quad 2-input OR gates with buffered output.+---+--+---+ +---+---*---+1A |1 +--+ 14| VCC | A | B | Y | Y = A+B1B |2 13| 4B +===+===*===+1Y |3 7410 12| 4A | 0 | 0 | 0 |2A |4 32 11| 4Y | 0 | 1 | 1 |2B |5 10| 3B | 1 | 0 | 1 |2Y |6 9| 3A | 1 | 1 | 1 |GND |7 8| 3Y +---+---*---++----------+74335110-tap noninverting delay lines (20, 50 or 100ns total delay).+---+--+---+A |1 +--+ 16| VCC|2 15||3 14| Y1Y2 |4 743 13| Y3Y4 |5 351 12| Y5Y6 |6 11| Y7Y8 |7 10| Y9GND |8 9| Y10+----------+7443748-bit 3-state dual-ranking D flip flop.Designed to prevent stable conditions in data synchronization applications in which setup an d hold times may be violated.+---+--+---+Q1 |1 +--+ 20| D1Q2 |2 19| D2Q3 |3 18| D3Q4 |4 17| D4GND |5 744 16| VCCQ5 |6 374 15| D5Q6 |7 14| D6Q7 |8 13| D7Q8 |9 12| D8/OE |10 11| CLK+----------+747001Quad 2-input AND gates with schmitt-trigger inputs.0.8V typical input hysteresis at VCC=+5V.+---+--+---+ +---+---*---+1A |1 +--+ 14| VCC | A | B | Y | Y = AB1B |2 13| 4B +===+===*===+。

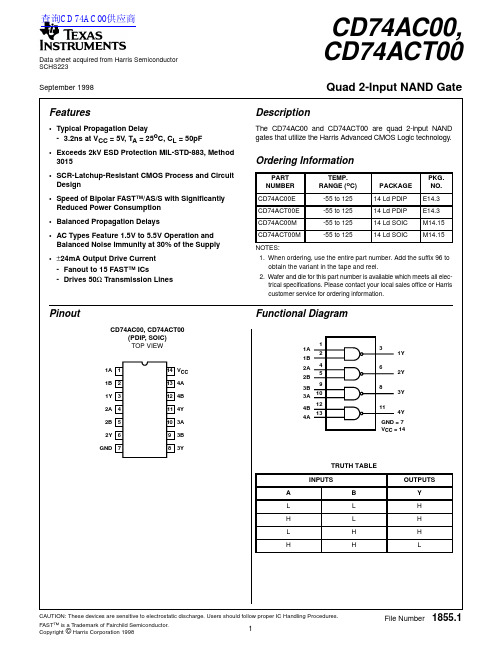

Data sheet acquired from Harris Semiconductor SCHS223Features•Typical Propagation Delay- 3.2ns at V CC = 5V , T A = 25o C, C L = 50pF•Exceeds 2kV ESD Protection MIL-STD-883, Method 3015•SCR-Latchup-Resistant CMOS Process and Circuit Design•Speed of Bipolar FAST™/AS/S with Significantly Reduced Power Consumption •Balanced Propagation Delays•AC Types Feature 1.5V to 5.5V Operation and Balanced Noise Immunity at 30% of the Supply •±24mA Output Drive Current -Fanout to 15 FAST™ ICs-Drives 50Ω Transmission LinesDescriptionThe CD74AC00and CD74ACT00are quad 2-input NAND gates that utilize the Harris Advanced CMOS Logic technology.PinoutCD74AC00, CD74ACT00(PDIP , SOIC)TOP VIEWFunctional DiagramOrdering InformationPART NUMBER TEMP.RANGE (o C)PACKAGE PKG.NO.CD74AC00E -55 to 12514 Ld PDIP E14.3CD74ACT00E -55 to 12514 Ld PDIP E14.3CD74AC00M -55 to 12514 Ld SOIC M14.15CD74ACT00M -55 to 12514 Ld SOICM14.15NOTES:1.When ordering,use the entire part number.Add the suffix 96to obtain the variant in the tape and reel.2.Wafer and die for this part number is available which meets all elec-trical specifications.Please contact your local sales office or Harris customer service for ordering information.1A 1B 1Y 2A 2B 2Y GND V CC 4A 4B 4Y 3A 3B 3Y1234567141312111098TRUTH TABLEINPUTSOUTPUTSA B Y L L H H L H L H H HHL1A 1B 2A 2B 3B 3A 4B 4A12459101213368111Y 2Y3Y 4YGND = 7V CC = 14September 1998CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.CD74AC00,CD74ACT00Quad 2-Input NAND GateFile Number1855.1查询CD74AC00供应商Absolute Maximum Ratings Thermal InformationDC Supply Voltage, V CC. . . . . . . . . . . . . . . . . . . . . . . .-0.5V to 6V DC Input Diode Current, I IKFor V I < -0.5V or V I > V CC + 0.5V. . . . . . . . . . . . . . . . . . . . . .±20mA DC Output Diode Current, I OKFor V O < -0.5V or V O > V CC + 0.5V . . . . . . . . . . . . . . . . . . . .±50mA DC Output Source or Sink Current per Output Pin, I OFor V O > -0.5V or V O < V CC + 0.5V . . . . . . . . . . . . . . . . . . . .±50mA DC V CC or Ground Current, I CC or I GND (Note 3) . . . . . . . . .±100mA Operating ConditionsTemperature Range, T A . . . . . . . . . . . . . . . . . . . . . .-55o C to 125o C Supply Voltage Range, V CC (Note 4)AC T ypes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1.5V to 5.5V ACT T ypes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V DC Input or Output Voltage, V I, V O . . . . . . . . . . . . . . . . .0V to V CC Input Rise and Fall Slew Rate, dt/dvAC T ypes, 1.5V to 3V . . . . . . . . . . . . . . . . . . . . . . . . .50ns (Max) AC T ypes, 3.6V to 5.5V. . . . . . . . . . . . . . . . . . . . . . . .20ns (Max) ACT T ypes, 4.5V to 5.5V. . . . . . . . . . . . . . . . . . . . . . .10ns (Max)Thermal Resistance (T ypical, Note 5)θJA (o C/W) PDIP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . .90 SOIC Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . .175 Maximum Junction T emperature (Plastic Package) . . . . . . . . . .150o C Maximum Storage Temperature Range . . . . . . . . . .-65o C to 150o C Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . .300o CCAUTION:Stresses above those listed in“Absolute Maximum Ratings”may cause permanent damage to the device.This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.NOTES:3.For up to 4 outputs per device, add±25mA for each additional output.4.Unless otherwise specified, all voltages are referenced to ground.5.θJA is measured with the component mounted on an evaluation PC board in free air.DC Electrical SpecificationsPARAMETER SYMBOLTESTCONDITIONS VCC(V)25o C-40o C TO85o C-55o C TO125o CUNITS V I(V)I O(mA)MIN MAX MIN MAX MIN MAXAC TYPESHigh Level Input Voltage V IH-- 1.5 1.2- 1.2- 1.2-V3 2.1- 2.1- 2.1-V5.5 3.85- 3.85- 3.85-V Low Level Input Voltage V IL-- 1.5-0.3-0.3-0.3V3-0.9-0.9-0.9V5.5- 1.65- 1.65- 1.65V High Level Output Voltage V OH V IH or V IL-0.05 1.5 1.4- 1.4- 1.4-V-0.053 2.9- 2.9- 2.9-V-0.05 4.5 4.4- 4.4- 4.4-V-43 2.58- 2.48- 2.4-V-24 4.5 3.94- 3.8- 3.7-V-75(Note 6, 7)5.5-- 3.85---V-50(Note 6, 7)5.5---- 3.85-VLow Level Output VoltageV OLV IH or V IL0.05 1.5-0.1-0.1-0.1V 0.053-0.1-0.1-0.1V 0.05 4.5-0.1-0.1-0.1V 123-0.36-0.44-0.5V 24 4.5-0.36-0.44-0.5V 75(Note 6, 7) 5.5--- 1.65--V 50(Note 6, 7)5.5----- 1.65V Input Leakage Current I I V CC or GND - 5.5-±0.1-±1-±1µA Quiescent Supply Current,SSI I CCV CC or GND5.5-4-40-80µAACT TYPESHigh Level Input Voltage V IH -- 4.5 to 5.52-2-2-V Low Level Input Voltage V IL -- 4.5 to 5.5-0.8-0.8-0.8V High Level Output VoltageV OHV IH or V IL-0.05 4.5 4.4- 4.4- 4.4-V -24 4.5 3.94- 3.8- 3.7-V -75 5.5-- 3.85---V -505.5---- 3.85-V Low Level Output VoltageV OLV IH or V IL0.05 4.5-0.1-0.1-0.1V 24 4.5-0.36-0.44-0.5V 75(Note 6, 7) 5.5--- 1.65--V 50(Note 6, 7)5.5----- 1.65V Input Leakage Current I I V CC or GND - 5.5-±0.1-±1-±1µA Quiescent Supply Current,SSII CC V CC or GND 0 5.5-4-40-80µA Additional Supply Current per Input Pin TTL Inputs High 1 Unit Load ∆I CCV CC -2.1- 4.5 to 5.5- 2.4- 2.8-3mANOTES:6.Test one output at a time for a 1-second maximum duration.Measurement is made by forcing current and measuring voltage to minimize power dissipation.7.Test verifies a minimum 50Ω transmission-line-drive capability at 85o C, 75Ω at 125o C.ACT Input Load TableINPUT UNIT LOADAll0.15NOTE:Unit load is ∆I CC limit specified in DC Electrical Specifications T able, e.g., 2.4mA max at 25o C.DC Electrical Specifications(Continued)PARAMETERSYMBOL TEST CONDITIONSV CC (V)25o C -40o C TO 85o C -55o C TO 125o C UNITS V I (V)I O (mA)MIN MAX MIN MAX MIN MAXSwitching Specifications Input t r , t f = 3ns, C L = 50pF (Worst Case)PARAMETERSYMBOLV CC (V)-40o C TO 85o C-55o C TO 125o CUNITSMIN TYPMAXMINTYPMAXAC TYPESPropagation Delay, Input to Outputt PLH , t PHL1.5--83--91ns 3.3(Note 9)2.7-9.3 2.6-10.2ns 5(Note 10)1.9- 6.6 1.8-7.3ns Input CapacitanceC I ---10--10pF Power Dissipation Capacitance C PD (Note 11)--45--45-pFACT TYPESPropagation Delay, Input to Outputt PHL 5(Note 10)2.8-8 2.7-8ns t PLH3.4-9.5 3.3-9.5ns Input CapacitanceC I ---10--10pF Power Dissipation Capacitance C PD (Note 11)--45--45-pFNOTES:8.Limits tested at 100%.9.3.3V Min at 3.6V, Max at 3V.10.5V Min at 5.5V, Max at 4.5V.11.C PD is used to determine the dynamic power consumption per gate.AC: P D = V CC 2 f i (C PD + C L )ACT: P D = V CC 2 f i (C PD + C L ) + V CC ∆I CC where f i = input frequency, C L = output load capacitance, V CC = supply voltage.DUT OUTPUTR L (NOTE)OUTPUT LOAD500ΩC L 50pFNOTE:For AC Series Only: When V CC = 1.5V , R L = 1k Ω.FIGURE 1.PROPAGATION DELAY TIMESCD74ACCD74ACTInput LevelV CC 3V Input Switching Voltage, V S 0.5 V CC 1.5V Output Switching Voltage, V S0.5 V CC0.5 V CCFIGURE 2.WAVEFORMSt r = 3ns t f = 3ns90%V S 10%GNDINPUT t PHLt PLHV SLEVEL V I V OIMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

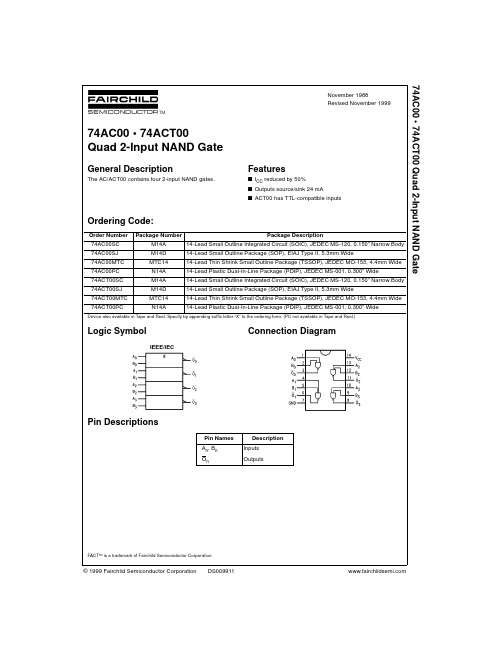

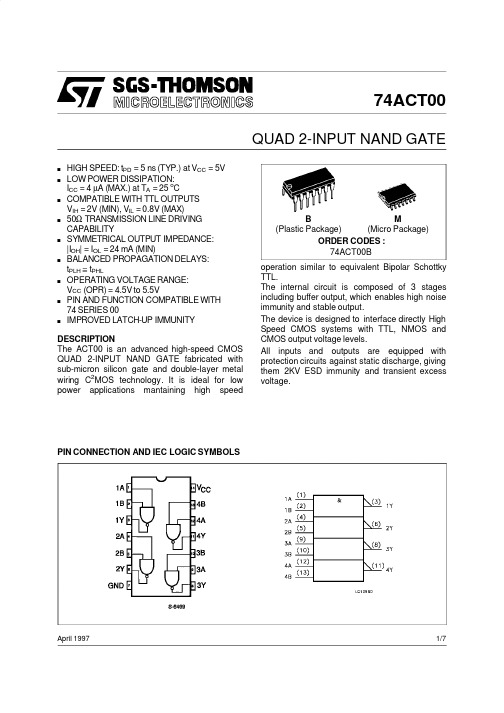

74ACT00QUAD 2-INPUT NAND GATEApril 1997s HIGH SPEED:t PD =5ns (TYP.)at V CC =5V sLOW POWER DISSIPATION:I CC =4µA (MAX.)at T A =25o CsCOMPATIBLE WITH TTL OUTPUTS V IH =2V (MIN),V IL =0.8V (MAX)s50ΩTRANSMISSION LINE DRIVING CAPABILITYsSYMMETRICAL OUTPUT IMPEDANCE:|I OH |=I OL =24mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅t PHLsOPERATING VOLTAGE RANGE:V CC (OPR)=4.5V to 5.5VsPIN AND FUNCTION COMPATIBLE WITH 74SERIES 00sIMPROVED LATCH-UP IMMUNITYDESCRIPTIONThe ACT00is an advanced high-speed CMOS QUAD 2-INPUT NAND GATE fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology.It is ideal for low power applications mantaining high speedoperation similar to equivalent Bipolar Schottky TTL.The internal circuit is composed of 3stages including buffer output,which enables high noise immunity and stable output.The device is designed to interface directly High Speed CMOS systems with TTL,NMOS and CMOS output voltage levels.All inputs and outputs are equipped with protection circuits against static discharge,giving them 2KV ESD immunity and transient excess voltage.PIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODES :74ACT00B M(Micro Package)B (Plastic Package)1/7INPUT AND OUTPUT EQUIVALENT CIRCUITABSOLUTE MAXIMUM RATINGSSymbol ParameterValue Unit V CC Supply Voltage -0.5to +7V V I DC Input Voltage -0.5to V CC +0.5V V O DC Output Voltage -0.5to V CC +0.5V I IK DC Input Diode Current ±20mA I OK DC Output Diode Current ±20mA I O DC Output Current ±50mA I CC or I GND DC V CC or Ground Current±200mAT stg Storage Temperature -65to +150o C T LLead Temperature (10sec)300oCAbsolute Maximum Ratings are those values beyond which damage to the device may occur.Functional operation under these condition is not implied.TRUTH TABLEA B Y L L H L H H H L H HHLPIN DESCRIPTIONPIN No SYMBOL NAME AND FUNCTION 1,4,9,121A to 4A Data Inputs 2,5,10,131B to 4B Data Inputs 3,6,8,111Y to 4Y Data Outputs 7GND Ground (0V)14V CCPositive Supply VoltageRECOMMENDED OPERATING CONDITIONSSymbol ParameterValue Unit V CC Supply Voltage 4.5to 5.5V V I Input Voltage 0to V CC V V O Output Voltage0to V CC VT op Operating Temperature:-40to +85oCdt/dvInput Rise and Fall Time V CC =4.5to 5.5V (note 1)8ns/V1)V IN from 0.8V to 2.0V74ACT002/7CAPACITIVE CHARACTERISTICSSymbolParameterTest ConditionsValueUnitV CC (V)T A =25oC -40to 85oC Min.Typ.Max.Min.Max.C IN Input Capacitance 5.04pF C PDPower Dissipation Capacitance (note 1)5.031pF1)C PD isdefined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load.(Refer to Test Circuit).Ave rage operating current can be obtained by the following equation.I CC (opr)=C PD •V CC •f IN +I CC /n (per circuit)AC ELECTRICAL CHARACTERISTICS (C L =50pF,R L =500Ω,Input t r =t f =3ns)SymbolParameterTest ConditionValueUnitV CC (V)T A =25oC -40to 85o CMin.Typ.Max.Min.Max.t PLH t PHLPropagation Delay Time5.0(*)1.5 5.09.0 1.09.5ns(*)Voltage range is 5V ±0.5VDC SPECIFICATIONSSymbolParameterTest ConditionsValueUnitV CC (V)T A =25oC -40to 85oC Min.Typ.Max.Min.Max.V IH High Level Input Voltage 4.5V O =0.1V or V CC -0.1V 2.0 1.5 2.0V 5.5 2.01.52.0V IL Low Level Input Voltage 4.5V O =0.1V or V CC -0.1V 1.50.80.8V 5.5 1.50.80.8V OHHigh Level Output Voltage4.5V I (*)=V IH or V ILI O =-50µA 4.4 4.49 4.4V5.5I O =-50µA 5.4 5.495.44.5I O =-24mA 3.86 3.765.5I O =-24mA 4.864.76V OLLow Level Output Voltage4.5V I (*)=V IH or V ILI O =50µA 0.0010.10.1V5.5I O =50mA 0.0010.10.14.5I O =24mA 0.360.445.5I O =24mA0.360.44I I Input Leakage Current 5.5V I =V CC or GND ±0.1±1µA I CCT Max I CC /Input 5.5V I =V CC -2.1V 0.61.5mA I CC Quiescent Supply Current5.5V I =V CC or GND 440µA I OLD Dynamic Output Current (note 1,2)5.5V OLD =1.65V max 75mA I OHDV OHD =3.85V min-75mA1)Maximum test duration 2ms,one output loaded at time2)Incident wave switch ing is guaranteed on transmission lines with impe dances as low as 50Ω.(*)All outputs loaded.74ACT003/774ACT00TEST CIRCUITC L=50pF or equivalent(includes jig and probe capacitance)R L=R1=500Ωor equiva lentR T=Z OUT of pulse generator(typically50Ω)WAVEFORM:PROPAGATION DELAYS(f=1MHz;50%duty cycle) 4/7DIM.mminch MIN.TYP.MAX.MIN.TYP.MAX.a10.510.020B 1.391.650.0550.065b 0.50.020b10.250.010D 200.787E 8.50.335e 2.540.100e315.240.600F 7.10.280I 5.10.201L 3.30.130Z1.272.540.0500.100P001APlastic DIP14MECHANICAL DATA74ACT005/7DIM.mm inch MIN.TYP.MAX.MIN.TYP.MAX.A 1.750.068a10.10.20.0030.007a2 1.650.064b 0.350.460.0130.018b10.190.250.0070.010C 0.50.019c145(typ.)D 8.558.750.3360.344E 5.86.20.2280.244e 1.270.050e37.620.300F 3.8 4.00.1490.157G 4.6 5.30.1810.208L 0.5 1.270.0190.050M 0.680.026S8(max.)P013GSO14MECHANICAL DATA74ACT006/774ACT00 Information furnished is believed to be accurate and reliable.However,SGS-THOMSON Microelectronics assumes no responsabilit y for the consequences of use of such information nor for any infringemen t of patents or other rights of third parties which may results from its use.No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectr onics.Specifications mention ed in this publication are subject to change without notice.This publication supersede s and replaces all information previously supplied.SGS-THOMSON Microelectr onics products are not auth orized for use as critical compon ents in life support devices or systems without expre ss written approval of SGS-THOMSON Microelectonics.©1997SGS-THOMSON Microelectronics-Printed in Italy-All Rights Reserve dSGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia-Brazil-Canada-China-France-Germany-Hong Kong-Italy-Japan-Korea-Malaysia-Malta-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A.7/7。

74系列功能大全(中文)74、74HC、74LS系列芯片资料,从网上下的,集合了一下系列电平典型传输延迟ns 最大驱动电流(-Ioh/Lol)mAAHC CMOS 8.5 -8/8AHCT COMS/TTL 8.5 -8/8HC COMS 25 -8/8HCT COMS/TTL 25 -8/8ACT COMS/TTL 10 -24/24F TTL 6.5 -15/64ALS TTL 10 -15/64LS TTL 18 -15/24注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

74LSxx的使用说明如果找不到的话,可参阅74xx或74HCxx的使用说明。

有些资料里包含了几种芯片,如74HC161资料里包含了74HC160、74HC161、74HC162、74HC163四种芯片的资料。

找不到某种芯片的资料时,可试着查看一下临近型号的芯片资料。

7400 QUAD 2-INPUT NAND GATES 与非门7401 QUAD 2-INPUT NAND GATES OC 与非门7402 QUAD 2-INPUT NOR GATES 或非门7403 QUAD 2-INPUT NAND GATES 与非门7404 HEX INVERTING GATES 反向器7406 HEX INVERTING GATES HV 高输出反向器7408 QUAD 2-INPUT AND GATE 与门7409 QUAD 2-INPUT AND GATES OC 与门7410 TRIPLE 3-INPUT NAND GATES 与非门7411 TRIPLE 3-INPUT AND GATES 与门74121 ONE-SHOT WITH CLEAR 单稳态74132 SCHMITT TRIGGER NAND GATES 触发器与非门7414 SCHMITT TRIGGER INVERTERS 触发器反向器74153 4-LINE TO 1 LINE SELECTOR 四选一74155 2-LINE TO 4-LINE DECODER 译码器74180 PARITY GENERATOR/CHECKER 奇偶发生检验74191 4-BIT BINARY COUNTER UP/DOWN 计数器7420 DUAL 4-INPUT NAND GATES 双四输入与非门7426 QUAD 2-INPUT NAND GATES 与非门7427 TRIPLE 3-INPUT NOR GATES 三输入或非门7430 8-INPUT NAND GATES 八输入端与非门7432 QUAD 2-INPUT OR GATES 二输入或门7438 2-INPUT NAND GATE BUFFER 与非门缓冲器7445 BCD-DECIMAL DECODER/DRIVER BCD译码驱动器7474 D-TYPE FLIP-FLOP D型触发器7475 QUAD LATCHES 双锁存器7476 J-K FLIP-FLOP J-K触发器7485 4-BIT MAGNITUDE COMPARATOR 四位比较器7486 2-INPUT EXCLUSIVE OR GATES 双端异或门74HC00 QUAD 2-INPUT NAND GATES 双输入与非门74HC02 QUAD 2-INPUT NOR GATES 双输入或非门74HC03 2-INPUT OPEN-DRAIN NAND GATES 与非门74HC04 HEX INVERTERS 六路反向器74HC05 HEX INVERTERS OPEN DRAIN 六路反向器74HC08 2-INPUT AND GATES 双输入与门74HC107 J-K FLIP-FLOP WITH CLEAR J-K触发器74HC109A J-K FLIP-FLOP W/PRESET J-K触发器74HC11 TRIPLE 3-INPUT AND GATES 三输入与门74HC112 DUAL J-K FLIP-FLOP 双J-K触发器74HC113 DUAL J-K FLIP-FLOP PRESET 双JK触发器74HC123A RETRIGGERABLE MONOSTAB 可重触发单稳74HC125 TRI-STATE QUAD BUFFERS 四个三态门74HC126 TRI-STATE QUAD BUFFERS 六三态门74HC132 2-INPUT TRIGGER NAND 施密特触发与非门74HC133 13-INPUT NAND GATES 十三输入与非门74HC137 3-TO-8 DECODERS W/LATCHES 3-8线译码器74HC138 3-8 LINE DECODER 3线至8线译码器74HC139 2-4 LINE DECODER 2线至4线译码器74HC14 TRIGGERED HEX INVERTER 六触发反向器74HC147 10-4 LINE PRIORITY ENCODER 10-4编码器74HC148 8-3 LINE PRIORITY ENCODER 8-3编码器74HC149 8-8 LINE PRIORITY ENCODER 8-8编码器74HC151 8-CHANNEL DIGITAL MUX 8通道多路器74HC153 DUAL 4-INPUT MUX 双四输入多路器74HC154 4-16 LINE DECODER 4线至16线译码器74HC155 2-4 LINE DECODER 2线至4线译码器74HC157 QUAD 2-INPUT MUX 四个双端多路器74HC161 BINARY COUNTER 二进制计数器74HC163 DECADE COUNTERS 十进制计数器74HC164 SERIAL-PARALLEL SHIFT REG 串入并出74HC165 PARALLEL-SERIAL SHIFT REG 并入串出74HC166 SERIAL-PARALLEL SHIFT REG 串入并出74HC173 TRI-STATE D FLIP-FLOP 三态D触发器74HC174 HEX D FLIP-FLOP W/CLEAR 六D触发器74HC175 HEX D FLIP-FLOP W/CLEAR 六D触发器74HC181 ARITHMETIC LOGIC UNIT 算术逻辑单元74HC182 LOOK AHEAD CARRYGENERATR 进位发生器74HC190 BINARY UP/DN COUNTER 二进制加减计数器74HC191 DECADE UP/DN COUNTER 十进制加减计数器74HC192 DECADE UP/DN COUNTER 十进制加减计数器74HC193 BINARY UP/DN COUNTER 二进制加减计数器74HC194 4BIT BI-DIR SHIFT 4位双向移位寄存器74HC195 4BIT PARALLEL SHIFT 4位并行移位寄存器74HC20 QUAD 4-INPUT NAND GATE 四个四入与非门74HC221A NON-RETRIG MONOSTAB 不可重触发单稳74HC237 3-8 LINE DECODER 地址锁3线至8线译码器74HC242/243 TRI-STAT TRANSCEIVER 三态收发器74HC244 OCTAL 3-STATE BUFFER 八个三态缓冲门74HC245 OCTAL 3-STATE TRANSCEIVER 三态收发器74HC251 8-CH 3-STATE MUX 8路3态多路器74HC253 DUAL 4-CH 3-STATE MUX 4路3态多路器74HC257 QUAD 2-CH 3-STATE MUX 4路3态多路器74HC258 2-CH 3-STATE MUX 2路3态多路器74HC259 3-8 LINE DECODER 8位地址锁存译码器74HC266A 2-INPUT EXCLUSIVE NOR GATE 异或非74HC27 TRIPLE 3-INPUT NOR GATE三个3输入或非门74HC273 OCTAL D FLIP-FLOP CLEAR 8路D触发器74HC280 9BIT ODD/EVEN GENERATOR 奇偶发生器74HC283 4BIT BINARY ADDER CARRY 四位加法器74HC299 3-STATE UNIVERSAL SHIFT 三态移位寄存74HC30 8-INPUT NAND GATE 8输入端与非门74HC32 QUAD 2-INPUT OR GATE 四个双端或门74HC34 NON-INVERTER 非反向器74HC354 8-CH 3-STATE MUX 8路3态多路器74HC356 8-CH 3-STATE MUX 8路3态多路器74HC365 HEX 3-STATE BUFFER 六个三态缓冲门74HC366 3-STATE BUFFER INVERTER 缓冲反向器74HC367 3-STATE BUFFER INVERTER 缓冲反向器74HC368 3-STATE BUFFER INVERTER 缓冲反向器74HC373 3-STATE OCTAL D LATCHES 三态D型锁存器74HC374 3-STATE OCTAL D FLIPFLOP 三态D触发器74HC393 4-BIT BINARY COUNTER 4位二进制计数器74HC4016 QUAD ANALOG SWITCH 四路模拟量开关74HC4020 14-Stage Binary Counter 14输出计数器74HC4017 Decade Counter/Divider with 10 Decoded Outputs 十进制计数器带10个译码输出端74HC4040 12 Stage Binary Counter 12出计数器74HC4046 PHASE LOCK LOOP 相位监测输出器74HC4049 LEVEL DOWN CONVERTER 电平变低器74HC4050 LEVEL DOWN CONVERTER 电平变低器74HC4051 8-CH ANALOG MUX 8通道多路器74HC4052 4-CH ANALOG MUX 4通道多路器74HC4053 2-CH ANALOG MUX 2通道多路器74HC4060 14-STAGE BINARY COUNTER 14阶BIN计数74HC4066 QUAD ANALOG MUX 四通道多路器74HC4075 TRIPLE 3-INPUT OR GATE 3输入或门74HC42 BCD TO DECIMAL BCD转十进制译码器74HC423A RETRIGGERABLE MONOSTAB 可重触发单稳74HC4511 BCD-7 SEG DRIVER/DECODER 7段译码器74HC4514 4-16 LINE DECODER 4至16线译码器74HC4538A RETRIGGERAB MONOSTAB 可重触发单稳74HC4543 LCD BCD-7 SEG LCD用的BCD-7段译码驱动74HC51 AND OR GATE INVERTER 与或非门74HC521 8BIT MAGNITUDE COMPARATOR 判决定路74HC533 3-STATE D LATCH 三态D锁存器74HC534 3-STATE D FLIP-FLOP 三态D型触发器74HC540 3-STATE BUFFER 三态缓冲器74HC541 3-STATE BUFFER INVERTER三态缓冲反向器74HC58 DUAL AND OR GATE 与或门74HC589 3STATE 8BIT SHIFT 8位移位寄存三态输出74HC594 8BIT SHIFT REG 8位移位寄存器74HC595 8BIT SHIFT REG 8位移位寄存器出锁存74HC597 8BIT SHIFT REG 8位移位寄存器入锁存74HC620 3-STATE TRANSCEIVER 反向3态收发器74HC623 3-STATE TRANSCEIVER 八路三态收发器74HC640 3-STATE TRANSCEIVER 反向3态收发器74HC643 3-STATE TRANSCEIVER 八路三态收发器74HC646 NON-INVERT BUS TRANSCEIVER 总线收发器74HC648 INVERT BUS TRANCIVER 反向总线收发器74HC688 8BIT MAGNITUDE COMPARATOR 8位判决电路74HC7266 2-INPUT EXCLUSIVE NOR GATE 异或非门74HC73 DUAL J-K FLIP-FLOP W/CLEAR 双JK触发器74HC74A PRESET/CLEAR D FLIP-FLOP 双D触发器74HC75 4BIT BISTABLE LATCH 4位双稳锁存器74HC76 PRESET/CLEAR JK FLIP-FLOP 双JK触发器74HC85 4BIT MAGNITUDE COMPARATOR 4位判决电路74HC86 2INPUT EXCLUSIVE OR GATE 2输入异或门74HC942 BAUD MODEM 300BPS低速调制解调器74HC943 300 BAUD MODEM 300BPS低速调制解调器74LS00 QUAD 2-INPUT NAND GATES 与非门74LS02 QUAD 2-INPUT NOR GATES 或非门74LS03 QUAD 2-INPUT NAND GATES 与非门74LS04 HEX INVERTING GATES 反向器74LS05 HEX INVERTERS OPEN DRAIN 六路反向器74LS08 QUAD 2-INPUT AND GATE 与门74LS09 QUAD 2-INPUT AND GATES OC 与门74LS10 TRIPLE 3-INPUT NAND GATES 与非门74LS109 QUAD 2-INPUT AND GATES OC 与门74LS11 TRIPLE 3-INPUT AND GATES 与门74LS112 DUAL J-K FLIP-FLOP 双J-K触发器74LS113 DUAL J-K FLIP-FLOP PRESET 双JK触发器74LS114 NEGATIVE J-K FLIP-FLOP 负沿J-K触发器74LS122 Retriggerable Monostab 可重触发单稳74LS123 Retriggerable Monostable 可重触发单稳74LS125 TRI-STATE QUAD BUFFERS 四个三态门74LS13 QUAL 4-in NAND TRIGGER 4输入与非触发器74LS160 BCD DECADE 4BIT BIN COUNTERS 计数器74LS136 QUADRUPLE 2-INPUT XOR GATE 异或门74LS138 3-8 LINE DECODER 3线至8线译码器74LS139 2-4 LINE DECODER 2线至4线译码器74LS14 TRIGGERED HEX INVERTER 六触发反向器74HC147 10-4 LINE PRIORITY ENCODER 10-4编码器74HC148 8-3 LINE PRIORITY ENCODER 8-3编码器74HC149 8-8 LINE PRIORITY ENCODER 8-8编码器74LS151 8-CHANNEL DIGITAL MUX 8通道多路器74LS153 DUAL 4-INPUT MUX 双四输入多路器74LS155 2-4 LINE DECODER 2线至4线译码器74LS156 2-4 LINE DECODER/DEMUX 2-4译码器74LS157 QUAD 2-INPUT MUX 四个双端多路器74LS158 2-1 LINE MUX 2-1线多路器74LS160A BINARY COUNTER 二进制计数器74LS161A BINARY COUNTER 二进制计数器74LS162A BINARY COUNTER 二进制计数器74LS163A DECADE COUNTERS 十进制计数器74LS164 SERIAL-PARALLEL SHIFT REG 串入并出74LS168 BI-DIRECT BCD TO DECADE 双向计数器74LS169 4BIT UP/DN BIN COUNTER 四位加减计数器74LS173 TRI-STATE D FLIP-FLOP 三态D触发器74LS174 HEX D FLIP-FLOP W/CLEAR 六D触发器74LS175 HEX D FLIP-FLOP W/CLEAR 六D触发器74LS190 BINARY UP/DN COUNTER 二进制加减计数器74LS191 DECADE UP/DN COUNTER 十进制加减计数器74LS192 DECADE UP/DN COUNTER 十进制加减计数器74LS193 BINARY UP/DN COUNTER 二进制加减计数器74LS194A 4BIT BI-DIR SHIFT 4位双向移位寄存器74LS195A 4BIT PARALLEL SHIFT4位并行移位寄存器74LS20 QUAD 4-INPUT NAND GATE 四个四入与非门74LS21 4-INPUT AND GATE 四输入端与门74LS240 OCTAL 3-STATE BUFFER 八个三态缓冲门74LS244 OCTAL 3-STATE BUFFER 八个三态缓冲门74LS245 OCTAL 3-STATE TRANSCEIVER 三态收发器74LS253 DUAL 4-CH 3-STATE MUX 4路3态多路器74LS256 4BIT ADDRESS LATCH 四位可锁存锁存器74LS257 QUAD 2-CH 3-STATE MUX 4路3态多路器74LS258 2-CH 3-STATE MUX 2路3态多路器74LS27 TRIPLE 3-INPUT NOR GATES 三输入或非门74LS279 QUAD R-S LATCHES 四个RS非锁存器74LS28 QUAD 2-INPUT NOR BUFFER 四双端或非缓冲74LS283 4BIT BINARY ADDER CARRY 四位加法器74LS30 8-INPUT NAND GATES 八输入端与非门74LS32 QUAD 2-INPUT OR GATES 二输入或门74LS352 4-1 LINE SELECTOR/MUX 4-1线选择多路器74LS365 HEX 3-STATE BUFFER 六个三态缓冲门74LS367 3-STATE BUFFER INVERTER 缓冲反向器74LS368A 3-STATE BUFFER INVERTER 缓冲反向器74LS373 OCT LATCH W/3-STATE OUT三态输出锁存器74LS76 Dual JK Flip-Flop w/set 2个JK触发器74LS379 QUAD PARALLEL REG 四个并行寄存器74LS38 2-INPUT NAND GATE BUFFER 与非门缓冲器74LS390 DUAL DECADE COUNTER 2个10进制计数器74LS393 DUAL BINARY COUNTER 2个2进制计数器74LS42 BCD TO DECIMAL BCD转十进制译码器74LS48 BCD-7 SEG BCD-7段译码器74LS49 BCD-7 SEG BCD-7段译码器74LS51 AND OR GATE INVERTER 与或非门74LS540 OCT Buffer/Line Driver 8路缓冲驱动器74LS541 OCT Buffer/LineDriver 8路缓冲驱动器74LS74 D-TYPE FLIP-FLOP D型触发器74LS682 8BIT MAGNITUDE COMPARATOR 8路比较器74LS684 8BIT MAGNITUDE COMPARATOR 8路比较器74LS75 QUAD LATCHES 双锁存器74LS83A 4BIT BINARY ADDER CARRY 四位加法器74LS85 4BIT MAGNITUDE COMPARAT 4位判决电路74LS86 2INPUT EXCLUSIVE OR GATE 2输入异或门74LS90 DECADE/BINARY COUNTER 十/二进制计数器74LS95B 4BIT RIGHT/LEFT SHIFT 4位左右移位寄存74LS688 8BIT MAGNITUDE COMPARAT 8位判决电路74LS136 2-INPUT XOR GATE 2输入异或门74LS651 BUS TRANSCEIVERS 总线收发器74LS653 BUS TRANSCEIVERS 总线收发器74LS670 3-STATE 4-BY-4 REG 3态4-4寄存器74LS73A DUAL J-K FLIP-FLOP W/CLEAR 双JK触发器。

74系列芯片数据手册大全74系列集成电路名称与功能常用74系列标准数字电路的中文名称资料7400 TTL四2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压缓冲驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相高压缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器7425 双4输入端或非门(有选通端74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门缓冲器74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器7443 4线-10线译码器(余3码输入)7444 4线-10线译码器(余3葛莱码输入) 74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动7449 4线-7段译码器74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门7452 4路2-3-2-2输入与或门7453 4路2-2-2-2输入与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器7460 双4输入与扩展器7461 三3输入与扩展器7462 4路2-3-3-2输入与或扩展器7464 4路4-2-3-2输入与或非门74645 TTL 三态输出八同相总线传送接收器7465 4路4-2-3-2输入与或非门(OC)74670 TTL 三态输出4×4寄存器堆7470 与门输入J-K触发器√7471 与或门输入J-K触发器√7472 与门输入J-K触发器7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双上升沿D触发器7476 TTL 带预置清除双J-K触发器7478 双D型触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7487 4位二进制原码/反码7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器74101 与或门输入J-K触发器74102 与门输入J-K触发器74107 双主-从J-K触发器74108 双主-从J-K触发器74109 双主-从J-K触发器74110 与门输入J-K触发器74111 双主-从J-K触发器74112 双下降沿J-K触发器74113 双下降沿J-K触发器74114 双下降沿J-K触发器74116 双4位锁存器74120 双脉冲同步驱动器74121 单稳态触发器74122 可重触发单稳态触发器74123 可重触发双稳态触发器74125 四总线缓冲器74126 四总线缓冲器74128 四2输入端或非线驱动器74132 四2输入端与非门。

To all our customersRegarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.Renesas Technology Home Page: Renesas Technology Corp.Customer Support Dept.April 1, 2003CautionsKeep safety first in your circuit designs!1. Renesas Technology Corporation puts the maximum effort into making semiconductor products betterand more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.Notes regarding these materials1. These materials are intended as a reference to assist our customers in the selection of the RenesasTechnology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of anythird-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.3. All information contained in these materials, including product data, diagrams, charts, programs andalgorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.The information described here may contain technical inaccuracies or typographical errors.Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page().4. When using any or all of the information contained in these materials, including product data, diagrams,charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from theinformation contained herein.5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a deviceor system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce inwhole or in part these materials.7. If these products or technologies are subject to the Japanese export control restrictions, they must beexported under a license from the Japanese government and cannot be imported into a country other than the approved destination.Any diversion or reexport contrary to the export control laws and regulations of Japan and/or thecountry of destination is prohibited.8. Please contact Renesas Technology Corporation for further details on these materials or the productscontained therein.HD74AC107/HD74ACT107Dual JK Flip-Flop (with Separate Clear and Clock)ADE-205-363 (Z)1st. EditionSep. 2000 DescriptionThe HD74AC107/HD74ACT107 dual JK master/slave flip-flops have a separate clock for each flip-flop. Inputs to the master section are controlled by the clock pulse. The clock pulse also regulates the state of the coupling transistors which connect the master and slave sections. The sequence of operation is as follows: 1) isolate slave from master; 2) enter information from J and K inputs to master; 3) disable J and K inputs;4) transfer information from master to slave.Features• Outputs Source/Sink 24 mA• HD74ACT107 has TTL-Compatible InputsPin ArrangementHD74AC107/HD74ACT1072Logic SymbolPin NamesJ 1, J 2, K 1, K 2Data InputsCP 1, CP 2Clock Pulse Inputs (Active Falling Edge)C D1, C D2Direct Clear Inputs (Active Low)Q 1, Q 2, Q 1, Q 2OutputsTruth TableInputs Outputs @ t n @ t n + 1J K Q L L Qn L H L H L H H HQ nH :High Voltage Level L :Low Voltage Levelt n :Bit time before clock pulse.t n + 1:Bit time after clock pulse.HD74AC107/HD74ACT1073Logic DiagramDC Characteristics (unless otherwise specified)ItemSymbol Max Unit ConditionMaximum quiescent supply current I CC 40µA V IN = V CC or ground, V CC = 5.5 V,Ta = Worst caseMaximum quiescent supply current I CC 4.0µA V IN = V CC or ground, V CC = 5.5 V,Ta = 25°CMaximum additional I CC /input (HD74ACT107)I CCT1.5mAV IN = V CC – 2.1 V, V CC = 5.5 V Ta = Worst caseHD74AC107/HD74ACT1074AC Characteristics: HD74AC107Ta = +25°C C L = 50 pFTa = –40°C to +85°C C L = 50 pF ItemSymbol V CC (V)*1Min Typ Max Min Max Unit Maximum clock f max3.3125——100—MHzfrequency 5.0150——125—Propagation delay t PLH 3.3 1.09.513.0 1.014.0ns C P to Q or Q 5.0 1.07.510.0 1.011.0Propagation delay t PHL 3.3 1.010.013.5 1.014.5ns C P to Q or Q 5.0 1.08.010.5 1.011.5Propagation delay t PLH 3.3 1.09.513.0 1.014.0ns C D to Q5.0 1.07.510.0 1.011.0Propagation delay t PHL 3.3 1.09.513.0 1.014.0ns C D to Q 5.01.07.510.01.011.0Note:1.Voltage Range 3.3 is 3.3 V ± 0.3 VVoltage Range 5.0 is 5.0 V ± 0.5 VOperating Requirements: HD74AC107Ta = +25°C C L = 50 pFTa = –40°C to +85°C C L = 50 pFItem Symbol V CC (V)*1Typ Guaranteed MinimumUnit Setup time t su3.3 3.0 5.5 6.0nsJ or k to C P 5.0 2.0 4.0 4.5Hold time t h3.3–1.50.00.0C P to J or k 5.0–0.50.00.0Pulse width t w 3.3 2.0 5.57.0C P or C D5.0 2.0 4.5 5.0Recovery time t rec 3.3 1.5 3.0 3.0C D to C P 5.01.03.03.0Note:1.Voltage Range 3.3 is 3.3 V ± 0.3 VVoltage Range 5.0 is 5.0 V ± 0.5 VHD74AC107/HD74ACT1075AC Characteristics: HD74ACT107Ta = +25°C C L = 50 pFTa = –40°C to +85°C C L = 50 pF ItemSymbol V CC (V)*1Min Typ Max Min Max Unit Maximum clock frequency f max 5.0100——80—MHz Propagation delay C P to Q or Q t PLH 5.0 1.09.512.5 1.013.5nsPropagation delay C P to Q or Q t PHL 5.0 1.010.513.0 1.014.0Propagation delay C D to Qt PLH 5.0 1.08.511.0 1.012.0Propagation delay C D to Q t PHL5.01.08.511.01.012.0Note:1.Voltage Range 5.0 is 5.0 V ± 0.5 VOperating Requirements: HD74ACT107Ta = +25°C C L = 50 pFTa = –40°C to +85°C C L = 50 pFItem Symbol V CC (V)*1Typ Guaranteed MinimumUnit Setup time J or k to C P t su 5.0 2.57.08.0nsHold time C P to J or k t h 5.00.0 1.5 1.5Pulse width C P or C Dt w 5.0 4.57.08.0Recovery time C D to C P t rec5.0—3.03.0Note:1.Voltage Range 5.0 is 5.0 V ± 0.5 VCapacitanceItemSymbol Typ Unit Condition Input capacitanceC IN 4.5pF V CC = 5.5 V Power dissipation capacitanceC PD35.0pFV CC = 5.0 VHD74AC107/HD74ACT107 Package Dimensions6HD74AC107/HD74ACT1077HD74AC107/HD74ACT1078Cautions1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, includingintellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Hitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright © Hitachi, Ltd., 2000. All rights reserved. Printed in Japan.Hitachi Asia Ltd. Hitachi Tower16 Collyer Quay #20-00, Singapore 049318Tel : <65>-538-6533/538-8577 Fax : <65>-538-6933/538-3877URL : .sg URLNorthAmerica : /Europe : /hel/ecg Asia : Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.(Taipei Branch Office)4/F, No. 167, Tun Hwa North Road, Hung-Kuo Building, Taipei (105), Taiwan Tel : <886>-(2)-2718-3666 Fax : <886>-(2)-2718-8180 Telex : 23222 HAS-TPURL : Hitachi Asia (Hong Kong) Ltd. Group III (Electronic Components) 7/F., North Tower, World Finance Centre,Harbour City, Canton Road Tsim Sha Tsui, Kowloon, Hong KongTel : <852>-(2)-735-9218 Fax : <852>-(2)-730-0281URL : Hitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 585160Hitachi Europe GmbHElectronic Components Group Dornacher Stra βe 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:Colophon 2.0。