2DPSK信号产生器的设计

- 格式:doc

- 大小:130.00 KB

- 文档页数:12

2dpsk的课程设计一、课程目标知识目标:1. 学生能理解2DPSK(二维相位偏移键控)的基本概念,掌握其调制解调原理。

2. 学生能运用2DPSK的相关知识,分析其在通信系统中的应用和优势。

3. 学生能掌握2DPSK与2D FSK、2D QPSK等其他调制方式的区别和联系。

技能目标:1. 学生能够运用所学知识,设计简单的2DPSK调制解调系统。

2. 学生能够通过实验和仿真,验证2DPSK系统的性能,并分析其影响因素。

3. 学生能够运用相关软件工具,对2DPSK通信系统进行建模和仿真。

情感态度价值观目标:1. 学生培养对通信科学的兴趣,激发探索精神,提高创新意识。

2. 学生通过团队合作,培养沟通协调能力和团队精神。

3. 学生能够认识到通信技术在国家发展和社会进步中的重要作用,增强社会责任感。

课程性质:本课程为高二年级通信技术课程的拓展内容,以理论教学和实践操作相结合的方式进行。

学生特点:学生已具备一定的物理和数学基础,对通信技术有一定了解,但2DPSK相关知识尚未接触。

教学要求:教师需以生动的案例引入,结合实际应用场景,激发学生兴趣。

注重理论与实践相结合,提高学生的动手操作能力。

在教学过程中,关注学生的个体差异,因材施教,确保每个学生都能达到课程目标。

通过课程学习,使学生能够掌握2DPSK相关知识,提高通信技术素养。

二、教学内容1. 2DPSK基本概念:介绍2DPSK的原理、特点及其在通信系统中的应用。

- 章节:第二章第二节- 内容:2DPSK的定义、调制解调过程、信号空间图。

2. 2DPSK调制解调技术:讲解2DPSK的调制解调方法及其相关技术。

- 章节:第二章第三节- 内容:相位偏移、载波生成、差分检测、解调方法。

3. 2DPSK系统性能分析:分析2DPSK系统的性能及其影响因素。

- 章节:第二章第四节- 内容:误码率、抗干扰性能、信号带宽、功率效率。

4. 2DPSK与其他调制方式的比较:探讨2DPSK与2D FSK、2D QPSK等其他调制方式的区别和联系。

2dpsk调制系统设计2 DPSK调制系统设计引言:2 DPSK调制是一种常用的数字调制技术,它在无线通信系统中起着重要的作用。

本文将介绍2 DPSK调制系统的设计原理、关键技术和性能评估。

一、2 DPSK调制系统设计原理2 DPSK调制是一种通过改变相位来表示数字信息的调制技术。

在 2 DPSK调制中,每个符号代表2个比特,相位的改变表示0和1。

系统设计的关键是确定相位改变的规则和解调方法。

二、2 DPSK调制系统的关键技术1. 调制器设计:调制器将数字信号转换为相位信号。

常用的调制器有差分编码调制器和相位调制器。

差分编码调制器通过差分编码的方式来表示相位改变,而相位调制器直接改变相位。

2. 解调器设计:解调器将接收到的相位信号转换为数字信号。

常用的解调器有差分解调器和相位解调器。

差分解调器通过差分解码的方式来还原数字信号,而相位解调器直接解析相位信息。

3. 抗噪性能优化:2 DPSK调制系统对噪声非常敏感,为了提高抗噪性能,可以采用前向纠错编码、抗干扰滤波器等技术。

4. 频率偏移补偿:频率偏移会导致相位解调错误,可以采用PLL (锁相环)等技术来对频率进行补偿。

5. 时钟同步:时钟同步是解调中的一个重要问题,可以通过导频插入、时钟同步算法等方式来实现。

三、2 DPSK调制系统的性能评估1. 误码率(Bit Error Rate, BER):误码率是衡量系统性能的重要指标,通过统计接收到的比特与发送比特不一致的比例来计算。

误码率越低,系统性能越好。

2. 带宽效率:带宽效率是衡量信道利用率的指标,表示每个比特所占用的带宽。

带宽效率越高,信道利用率越高。

3. 抗多径干扰性能:多径干扰是无线通信中常见的问题,可以通过信道估计、等化器等技术来提高抗多径干扰性能。

4. 抗多普勒频移性能:多普勒频移是由于移动终端速度引起的信号频率偏移,可以通过频率偏移补偿技术来提高抗多普勒频移性能。

结论:2 DPSK调制系统是一种常用的数字调制技术,它通过改变相位来表示数字信息。

2DPSK调制器文章作者:汪兴华日期:2004-01-081.1中文摘要和关键字本次课程设计实现载波的2DPSK调制输出。

晶振电路产生10MHz 正弦波,经过74LS190的10分频,一路通过74LS74D1触发器产生触发器输出Q端产生正相的载波,另外一端产生反相载波,实现载波的两路输出。

经过74LS153数据选择器,m序列对载波进行相位选择,形成BPSK的调制。

要实现2DPSK调制需要在74LS164的输出端再加74LS74的D2触发器,使绝对码输入成为相对码输出,成DPSK调制输出。

其间电路用到74LS04反相器,74LS86进行m序列产生的模2的反馈。

关键字:m序列,BPSK,2DPSK1.2 英文摘要和关键字Abstract: Research on 2DPSK modulate is an important aspect of research,the 2DPSK have more superiority,compared with other Signal modulate . The paper shows how the 2DPSK signal produce. In this class design we will use CMOS chip 74LS153, 74LS04 and so on.Keyword s: m sequence,BPSK,2DPSK第二章前言2.1 m序列m序列:m序列是最长线性反馈移存器序列的简称,是由带线性反馈的移存器产生的周期最长的一种序列。

具有较强的抗干扰能力和较低的截获概率,而且长的m序列更容易在一定的强噪声中被提取,这样就能够充分保证数据的正常通信。

通常产生伪随机序列的电路为反馈移存器.一般说来,一个n级反馈移位寄存器可能产生的最大周期等于(2n-1).现在我们引入M序列的本原多项式的概念。

若一个n次多项式f(x)满足以下条件(1)f(x)为既约的(2)f(x)可整除(x m+1),m=2n-1(3)f(x)除不尽(x q+1),q<m,则f(x)为本原多项式m序列通过线形反馈移位寄存器产生如图:(图1-2)设n级移位寄存器的初始状态:a-1,a-2,a-3,a-4,…a-n经过一次移位后,状态变为a0,a1,…a-n+1,经过n次移位以后状态变为a-n-1,a-n-…a1,a0。

2DPSK系统设计和仿真2DPSK(2-Differential Phase Shift Keying)是一种数字调制技术,通过在相邻的两个符号间比较相位差来传输数字信息。

在2DPSK系统中,每个符号都对应着2个相位状态,即+180°和-180°,通过在相邻符号间相位差的改变来表示二进制数据。

1.2DPSK调制器设计:2DPSK调制器是将数字数据转换为相位信号的关键组件。

常用的方法是采用相移键控(PSK)调制器。

相移键控调制器通过改变每个符号间的相位差来进行调制。

在2DPSK系统中,相位差的变化为180°,即+180°和-180°。

2.2DPSK解调器设计:3.信道设计:在2DPSK系统设计中,信道是一个重要的考虑因素。

信道可以引入噪声和失真,对系统性能产生影响。

设计合适的信道模型,可以更好地评估系统的性能。

4.误码率性能评估:误码率(BER)是衡量2DPSK系统性能的重要指标。

通过使用理论模型或进行仿真,可以评估不同调制参数和信道条件下系统的BER性能。

5.系统参数优化:对于设计的2DPSK系统,可以通过仿真来优化系统参数。

这包括调制索引、信道带宽、功率衰减等。

通过调整这些参数,系统的性能可以得到改善。

在进行2DPSK系统的仿真时,可以使用MATLAB等工具来实现。

利用MATLAB中提供的相关函数,可以方便地进行信号的生成、调制、解调和误码率性能评估等。

通过设置合适的参数,模拟实际场景下的信号传输过程,进而优化系统设计。

总结起来,2DPSK系统设计和仿真的关键步骤包括调制器和解调器的设计、信道建模、误码率性能评估以及系统参数优化。

通过合理的设计和仿真,可以有效地评估系统的性能,并进行参数调整以满足要求。

2DPSK调制解调系统的设计和仿真第一部分:调制器设计调制器是将输入比特流转换为相位差,从而进行调制的部分。

2DPSK 调制器的设计可以采用查表法。

首先,将输入比特流分为两个并行流,分别表示实部和虚部。

然后,通过比较当前比特和上一个比特的差异,确定下一个相位的差别。

假设当前比特为0,上一个比特为1,则相位差为π/2;假设当前比特为1,上一个比特为1,则相位差为0。

最后,根据相位差确定相位(0、π/2、π、3π/2)。

设计调制器时,可以使用Matlab或Simulink等工具进行仿真。

根据输入比特流,通过调制器可以得到相应的相位差输出。

第二部分:信道建模信道建模是模拟实际传输环境中的信道特性。

在信道建模过程中,需要考虑到信道带宽、噪声等因素。

可以采用高斯信道模型或瑞利信道模型进行仿真。

其中,高斯信道模型适用于室内或受干扰较少的环境,瑞利信道模型适用于室外或有多径衰落的环境。

第三部分:解调器设计解调器是将接收到的信号恢复为原始比特流的部分。

2DPSK解调器的设计可以采用软判决法。

首先,检测接收到的相位与已知相位差之间的关系。

根据相位差的不同,确定当前接收到的比特是0还是1、然后,根据比特的变化进行恢复,即将当前比特与上一个比特进行异或运算,得到输出比特流。

设计解调器时,可以使用Matlab或Simulink等工具进行仿真。

根据接收到的相位差,通过解调器可以得到恢复后的比特流输出。

总结:通过以上三个步骤,可以设计并仿真一个完整的2DPSK调制解调系统。

首先,设计调制器将输入比特流转换为相位差;然后,建立信道模型进行仿真;最后,设计解调器将接收到的信号恢复为原始比特流。

通过仿真,可以评估系统的性能指标,如误比特率(BER)等,并进行调试和优化。

2DPSK数字调制器的研究与设计_毕业论文华中师范大学武汉传媒学院毕业论文(设计) 2DPSK数字调制器的研究与设计院系:传媒技术学院专业:电子信息工程班级: B1101班姓名:李恒学号: 11405010125指导教师:谈新权2015年5月7日2DPSK数字调制器的研究与设计The Research and Design of 2DPSK Digital Modulator摘要数字相位调制广泛应用于通信领域。

2DPSK是一种基本的相移键控。

PSK调制通常有两种实现方法:乘法器法和相位选择法。

本文采用相位选择法实现PSK调制。

文章首先介绍了两种实现方法的电路框图。

接着论述了相位选择法实现2DPSK 调制的各部分电路设计。

相位选择开关采用了集成芯片74HC4051,这种模拟开关可通过三位数字信号的控制从8路模拟信号中选通其中的一路输出。

本文中只用了二选一开关。

用一位数字信号的高低电平选出其中的一路信号,即选出初始相位为0°或180°的载波。

从而实现了2DPSK的调制。

文中还详细介绍了其他单元电路的设计,包括低通滤波电路,载波放大和形成电路,以及调制输出电路。

论文最后完成了用Protel设计的总体电原理图。

关键词:数字通信数字调制相移键控相对相移键控AbstractDigital phase modulation is widely used in the field of communication.2DPSK is a kind of basic phase shift keying.PSK usually have two ways to realize the modulation:multiplier method and the phase selection method.T he phase selection method is adopted to realize PSK modulation in this paper.Two methods are introduced to realize circuit diagram first.Then discussesed design of circuit that is the phase selection method to realize 2DPSK modulation.The integrated chip 74HC4051 is adopted as the phase selection switch which can be controlled by 3bit digital signals so that a channel signal is selected from eight analog signnals.One of two switch is only used for this paper .High and low level of a digital signal are used to choose one of the signals, that selectes the initial carrier phase that is 0 degrees or 180 degrees.In order to the modulation of 2DPSK modulation is achieved.And the design of the other circuit unit are introduced in this paper,including low pass filter circuit, amplifying circuit and the formation of carrier modulation, and the output circuitof modulation.Finally,The whole design of the electrical schematic diagram is completed by using the Protel.Key word: Digital Communication Digital Modulation Phase Shift Keying Relative Phase Shift Keying目录摘要................................................................. Abstract .. (I)目录 (II)绪论 01 总体方案设计 (1)1.1 2PSK的乘法器实现 (1)1.2 2PSK的相位选择法的实现 (2)1.3 相对调相 (2)2 单元电路设计 (5)2.1 低通滤波器设计 (5)2.2 载波放大与形成电路 (5)2.3 模拟开关MC74HC4051介绍(2DPSK调制器) (6)2.4 调制输出电路设计 (7)2.5 差分编码器电路设计 (7)3 Protel 99 SE介绍 (8)3.1 protel 99se主要的功能模块 (9)3.2 protel 99se的组成 (9)3.3 protel 99se的基本操作 (9)3.4 电路原理总图 (10)结束语 (12)参考文献 (14)致谢 (15)绪论数字调相(PSK)是一种基本的数字调制,数字调相适合于非线性衡参信道。

2DPSK差分相干解调器设计差分相干解调器是一种用于2DPSK(二进制差分相移键控)调制信号的解调器。

在设计差分相干解调器时,需要考虑以下几个方面:调制信号特性、解调原理、差分相干解调器的架构、设计参数、实现方法以及性能评估。

1.调制信号特性:2.解调原理:差分相干解调器的主要工作原理是通过追踪相位差和修正相位差来恢复原始数字信号。

它利用差分编码和相移键控的特性,通过比较相邻两个信号的相位差来判断数字信息。

3.差分相干解调器的架构:差分相干解调器的架构一般包括载波恢复模块、符号再构成模块和差分解调模块。

载波恢复模块用于估计调制信号中的载波频率和相位,符号再构成模块用于恢复原始的2DPSK符号,差分解调模块用于判断相邻符号间的相位差。

4.设计参数:差分相干解调器的设计参数包括采样率、码间间隔、滤波器设计、相位误差估计等。

采样率需要满足奈奎斯特采样定理,码间间隔需要根据调制信号的特性确定,滤波器设计需要考虑到基带信号频谱特性,相位误差估计需要通过适当的算法进行估计。

5.实现方法:差分相干解调器可以通过硬件电路实现,也可以通过软件算法实现。

硬件电路实现可以使用专用的DSP器件或FPGA芯片,软件算法实现可以使用MATLAB或其他通信工具箱来模拟和实现。

6.性能评估:差分相干解调器的性能评估主要包括误码率和频谱效益两个方面。

误码率是判断解调器性能的主要指标,频谱效益是指解调器对信号频谱的利用率。

差分相干解调器在数字通信系统中起着重要的作用,设计合理的解调器可以有效地对2DPSK调制信号进行解调,实现可靠的数字信息传输。

在设计过程中,需要综合考虑调制信号特性、解调原理、架构设计、参数选择、实现方法和性能评估等方面。

2DPSK调制系统的课程设计摘要二进制差分相移键控简称为二相相对调相,记作2DPSK。

它不是利用载波相位的绝对数值传送数字信息,而是用前后码元的相对载波相位值传送数字信息。

所谓相对载波相位是指本码元初相与前一码元初相之差。

现代通信系统要求通信距离远、通信容量大、传输质量好。

作为其关键技术之一的调制解调技术一直是人们研究的一个重要方向。

从最早的模拟调幅调频技术的日臻完善,到现在数字调制技术的广泛运用,使得信息的传输更为有效和可靠。

2DPSK信号的调试方法有两种,即模拟调制法和移相键控法,本课程设计采用的是模拟调制法。

对基带信号进行差分编码得到相对码,再一同和载波输入开关电路进行绝对调相,从而产生2DPSK信号。

关键字: 2DPSK、模拟调制法、差分编码、绝对调相一、基本原理这是一个2DPSK数字调制电路,当然2DPSK离不开二进制相移键控2PSK。

用二进制数字信号控制正弦载波的相位称为2PSK,采用绝对移相,在发送端必须以某一相位作为基准,在接收端也必须有一个固定的相位作基准,如果参考相位发生变化,导致恢复的数字信号1变为0,0变为1,从而造成错码,这种现象称为2PSK方式的“倒π”现象或“反向工作”现象,因此实际中一般不采用2PSK而采用差分相位键控(2DPSK)方式。

2DPSK方式是利用前后相邻码元的相对载波相位值去表示数字信息的一种方式。

对于2DPSK波形的同一相位并不对应相同的数字信号,只有前后码元相位差才能决定数字信息符号,2DPSK也可以用相对码经绝对移相而形成。

这说明,只有已知移相键控方式是绝对的还是相对的,才能正确判定原信息;相对移相信号可以看作是把数字信息序列(绝对码)变换成相对码,然后再根据相对码进行绝对移相而形成。

图1 2PSK与2DPSK波形对比二、举例分析1.设信息代码为10011010,载频分别为码元速率的1倍和1.5倍,画出2PSK及2DPSK信号波形。

1倍载频:1.5倍载频:2.总结绝对码至相对码的变换规律,相对码至绝对码的变换规律。

2DPSK调制与解调电路设计解析2DPSK(2-Differential Phase Shift Keying)是一种数字调制和解调技术,通过改变相位来传输数字信号。

在2DPSK中,每个数字符号代表两个相邻相位之间的相位差。

设计2DPSK调制和解调电路需要考虑多个因素,包括相位调制器、相位解调器、时钟恢复电路等。

相位调制器是2DPSK调制电路的核心组件。

它负责将输入的数字信号转换成相应的相位变化。

一种常见的实现方式是使用两个电压控制振荡器(VCO)来控制相位变化。

其中一个VCO负责产生参考相位,另一个VCO负责产生相位差。

通过将两个VCO的输出相位差与输入数字信号进行乘积运算,就可以实现2DPSK的相位调制。

相位解调器是2DPSK解调电路的核心组件。

它负责将接收到的2DPSK信号解调成原始的数字信号。

相位解调器通常包含相位鉴别器、低通滤波器和时钟恢复电路。

相位鉴别器用于测量接收到的信号相位与参考相位之间的相位差,从而恢复原始的相位变化。

低通滤波器用于去除高频噪声,以便提取出原始的数字信号。

时钟恢复电路用于恢复原始信号的时钟信息,以确保解调的准确性。

在设计2DPSK调制和解调电路时,还需要考虑相位差的灵敏度、相位误差的补偿、功耗和带宽等因素。

相位差的灵敏度表示相位差的变化对数字信号的影响程度,通过选择合适的VCO参数可以实现合适的灵敏度。

相位误差补偿可以通过引入相位预取偏来实现,从而提高系统的可靠性。

功耗和带宽也是设计中需要考虑的因素,可以通过选择适当的电路结构和参数来平衡功耗和带宽之间的关系。

总结起来,2DPSK调制和解调电路设计需要考虑相位调制器、相位解调器、时钟恢复电路等多个组件。

合理选择电路结构和参数,可以实现高灵敏度、低功耗和较宽的带宽。

相位误差补偿和时钟恢复等技术可以提高系统的可靠性和抗干扰能力。

对于2DPSK调制和解调电路的设计,需要综合考虑以上因素,以满足具体的应用需求。

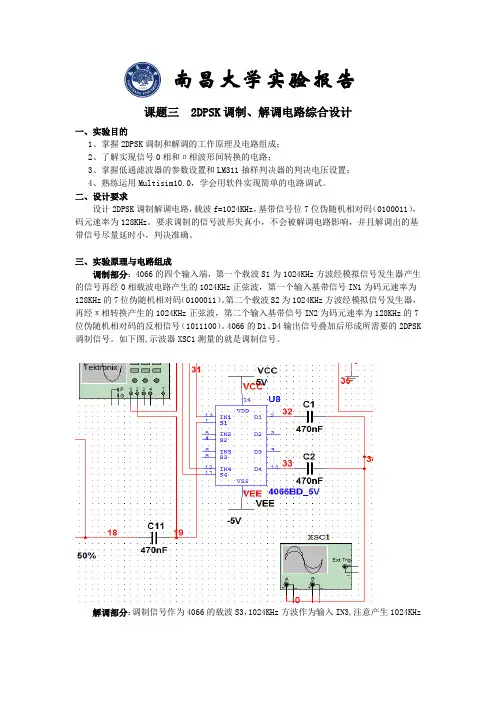

南昌大学实验报告课题三 2DPSK调制、解调电路综合设计一、实验目的1、掌握2DPSK调制和解调的工作原理及电路组成;2、了解实现信号0相和π相波形间转换的电路;3、掌握低通滤波器的参数设置和LM311抽样判决器的判决电压设置;4、熟练运用Multisim10.0,学会用软件实现简单的电路调试。

二、设计要求设计2DPSK调制解调电路,载波f=1024KHz,基带信号位7位伪随机相对码(0100011),码元速率为128KHz。

要求调制的信号波形失真小,不会被解调电路影响,并且解调出的基带信号尽量延时小,判决准确。

三、实验原理与电路组成调制部分:4066的四个输入端,第一个载波S1为1024KHz方波经模拟信号发生器产生的信号再经0相载波电路产生的1024KHz正弦波,第一个输入基带信号IN1为码元速率为128KHz的7位伪随机相对码(0100011)。

第二个载波S2为1024KHz方波经模拟信号发生器,再经π相转换产生的1024KHz正弦波,第二个输入基带信号IN2为码元速率为128KHz的7位伪随机相对码的反相信号(1011100)。

4066的D1、D4输出信号叠加后形成所需要的2DPSK 调制信号。

如下图,示波器XSC1测量的就是调制信号。

解调部分:调制信号作为4066的载波S3,1024KHz方波作为输入IN3,注意产生1024KHz方波的函数信号发生器设置如右图:两个信号经4066开关电路相乘输出的信号即为解调出的一路信号,由于是2DPSK,解调出了一路信号,则另一路信号也就知道了。

接下来要做的就是滤波,将4066输出的信号的包络解调出,由于基带信号是128KHz,低通滤波器的门限就是128KHz。

对于RC滤波器,有f=经过RC低通滤波器时,令R2=1K,得C3=1.2n F,如下左图此时由于信号电压较大,不需要经过放大就能判决。

然后经过抽样判决器LM311,经示波器观察,判决电平设为0就很合适判决(引脚3所接电平)。

信息科学与技术学院——2DPSK通信系统设计课程设计报告题目名称:2DPSK通信系统设计学生姓名:学号:专业年级:指导教师:时间:目录一、二进制差分相移键控(2DPSK)基本原理 (2)1.1 2DPSK信号基本原理 (2)1.2 2DPSK信号的解调原理 (3)二、2DPSK解调总体设计思路 (3)三、2DPSK解调系统的设计 (4)3.1带通滤波器 (4)3.2本地载波与2DPSK信号相乘 (5)3.3低通滤波电路 (6)3.4 抽样判决器 (7)3.4.1 抽样判决的比较器 (7)3.4.2样值的抽取 (7)3.5 逆码变换 (8)四、系统仿真 (9)4.1根据proteus的设计,利用SystemView仿真 (9)4.2系统输出仿真波形 (10)五、PCB制版图 (11)六、2DPSK解调总图 (12)七、课程设计心得 (12)八、参考文献 (13)二进制差分相移键控2DPSK 通信系统设计一、二进制差分相移键控(2DPSK )基本原理1.1 2DPSK 信号基本原理传输系统中要保证信息的有效传输就必须要有较高的传输速率和很低的误码率。

在传输信号中,2PSK 信号和2ASK 及2FSK 信号相比,具有较好的误码率性能,但是,在2PSK 信号传输系统中存在相位不确定性,并将造成接收码元“0”和“1”的颠倒,产生误码。

为了保证2PSK 的优点,又不会产生误码,将2PSK 体制改进为二进制差分相移键控(2DPSK ),及相对相移键控。

2DPSK 方式即是利用前后相邻码元的相对相位值去表示数字信息的一种方式。

现假设用Φ表示本码元初相与前一码元初相之差,并规定:Φ=0表示0码,Φ=π表示1码。

则数字信息序列与2DPSK 信号的码元相位关系可举例表示如2PSK 信号是用载波的不同相位直接去表示相应的数字信号而得出的,在接收端只能采用相干解调,它的时域波形图如图1所示。

图1 2DPSK 信号 在这种绝对移相方式中,发送端是采用某一个相位作为基准,所以在系统接收端也必须采用相同的基准相位。

王毓银著《数字电路逻辑设计》高等教育出版社徐志军著《CPLD/FPGA的开发与应用》电子工业出版社林明权著《VHDL数字控制系统设计范例》电子工业出版社冯涛著《可编程逻辑器件开发技术MAX+plusⅡ入门与提高》人民邮电出版社谭会生著《EDA技术综合应用实例与分析》西安电子科技大学出版社曾繁泰著《VHDL程序设计》清华大学出版社侯伯亨著《硬件描述语言与数字逻辑电路设计》西安电子科技大学出版社甘历著《VHDL应用与开发实践》科学技术出版社主要仪器设备及材料:微机一台及相应的仿真平台论文(设计)过程中教师的指导安排:每周答疑一至两次对计划的说明:独立按时完成设计注:本计划一式两份,一份交系,一份自己保存。

指导教师签字:2009年 3 月23 日课题名称:2DPSK信号产生器的设计目录摘要........................................................................ V II ABSTRACT ..................................................................... V III 引言.. (1)1. 绪论 (2)1.1信号发生器简介 (2)1.2EDA技术简介 (2)1.4VHDL简介 (5)1.5MAX+PLUS II简介 (5)2. 2DPSK信号产生器的设计 (7)2.12DPSK信号产生器的基本原理 (7)2.2分频器: (8)2.3M序列产生器: (8)2.4跳变检测及正弦波信号发生器 (10)2.52DPSK仿真波形 (11)2.62DPSK仿真波形的分析 (11)3. 总结 (12)3.1设计实现 (12)3.2设计中的不足和改进 (12)3.3毕业设计心得 (12)参考文献 (15)附录 (16)附录一 (16)附录二 (22)摘要本文介绍利用硬件描述语言(VHDL)来实现2DPSK信号发生器系统,数字调制解调技术在数字通信中占有非常重要的地位。

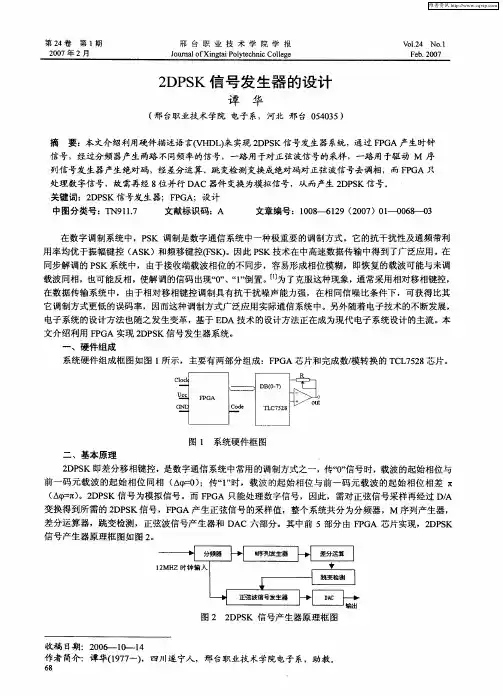

基于FPGA的2DPSK信号产生器的设计摘要:随着时代的进步,FPGA的应用也越来越广泛,FPGA用硬件描述语言(Verilog HDL)来实现2DPSK信号的调制系统,不仅简单方便,而且还能满足现代设备快速、准确、功耗低的特点。

Verilog语言有着灵活多样的电路描述风格,语言功能性强,并且简单易学,这些优良的性能使其得到广泛流行。

数字通信技术与FPGA的结合是现代通信系统发展的一个必然趋势。

FPGA实现2DPSK信号可用如下方法,先通过FPGA产生时钟信号,经过分频器产生两路时钟,一路用于基带码的产生,也就是用于驱动M序列信号发生器产生绝对码,另一路用于采样正弦信号。

M序列产生的绝对码经过差分运算转换成相对码,再把相对码加到正弦信号上输出,这就相当于对原码进行了调相输出。

而FPGA只能处理数字信号,因此要经过DAC器件转换为模拟信号,从而产生2DPSK信号。

通过对仿真波形的分析可知,该方案很好的实现了2DPSK信号产生器的功能。

关键词:FPGA;Verilog HDL;2DPSK信号产生器;数字调制;串并转换;Design of 2DPSK Signal Generator Based on FPGAAbstract:With the progress of the times, FPGA is used more and more popularly. FPGA used hardware description language ( Verilog HDL ) to achieve the 2DPSK signal modulation system. It's not only simple and convenient, but also equipped with many excellent characteristics of modern devices, such as fast, accurate, low power consumption. Verilog language can descript circuit variously and flexibly, and has powerful function. What’s more, it’s easy to learn for us. These excellent properties make Verilog language applied widely. The combination of digital communication technology and FPGA is a certainly trend of the development of modern communication system. The process of producing 2DPSK signal by FPGA is as follows. The clock signal generated by FPGA will generate two signals with different frequency. One is used to sampling, the other is to drive M array signal generator. It will be converted to absolute code, and be used to modulate. Because only the digital signal can be processed by FPGA, DAC is needed to generate 2DPSK signal.Key words:FPGA;Verilog HDL;2DPSK signal generator;digital modulation;目录1 绪论 (3)2 应用软件及器件介绍 (4)2.1 信号发生器简介 (4)2.2 EDA技术简介 (4)2.3 FPGA和CPLD器件简介 (5)2.4 Verilog HDL简介 (6)2.5 Quartus II简介 (7)3 2DPSK信号产生器的设计 (8)3.1 2DPSK信号产生器的基本原理 (8)3.1.1 2DPSK信号原理 (8)3.1.2 设计思路及方法 (9)3.2 软件设计 (10)3.2.1 分频器 (10)3.2.2 M序列产生器 (11)3.2.3 差分运算 (12)3.2.4 选相调制 (12)3.2.5 正弦信号发生器 (13)3.2.6 2DPSK信号波形仿真 (14)3.3 硬件设计 (15)3.3.1 器件说明 (16)3.3.2 并行输入方式设计 (19)3.3.3 串行输入方式设计 (21)3.3.4 串并对比分析 (23)4 调试 (24)5 总结 (25)参考文献 (26)附录 (27)致谢 (36)1 绪论人们为了掌握足够的信息,适应复杂多变的客观世界,满足生活、工作和学习的需要就必须进行信息的获取、传递、交换和处理。

信息与电气工程学院课程设计说明书(2010/2011学年第一学期)课程名称:电子线路题目:2DPSK数字调制电路设计专业班级:通信0802学生姓名:***学号:08031****指导教师:设计周数:1周设计成绩:总体论述一、设计任务1、查阅相关资料,了解2DPSK通信系统的基本原理和数字信号的传输过程2、进行功能分析,给出设计方案3、熟悉所用器件的功能特性4、用分立器件设计电路原理图5、进行调试,实现技术要求6、撰写设计报告二、设计要求1、要求设计一个2DSPK调制电路,实现移相键控。

2、载波频率为5Mhz;3、利用通信系统原理实验装置;4、利用示波器观察波形;5、M序列发生器的码长M=31三、性能指标1、能在示波器上显示清晰地正弦波2、能根据波形的初始相位变化得出正确的相对码信息3、有相对码可得出正确的绝对码信息四、实际电路所能完成的功能在输入端接入一个时钟方波脉冲信号,在输出端显示初始相位交替变化的正弦波。

五、理论电路所能完成的功能在输入端任意接入一个包含信息的方波信号,在输出端用不同初始相位的正弦波表示出来。

方案选型一、设计电路使其能产生两种不同相位的正弦波1、利用74ls74(双上升沿D触发器)对输入的时钟信号进行二分频,输出为原信号频率的一半的时钟方波信号2、利用放大器和电感电容组成滤波器(带通滤波器),将方波时钟信号转换成正弦信号3、射随器的输入阻抗答输出阻抗小,在电子技术中应用非常广泛。

它能使信号电压最大程度地往后传递。

因此利用射随器能够保证信号在传输过程中衰减最小。

4、利用三极管的发射极和集电极点位相反的特性分别输出两路相位相反的正弦波信号,作为2DPSK信号调制实验的载波信号。

其特点使频率相同初始相位相反,即可根据初始相位的不同进行二进制的数字调制。

二、AK(绝对码)编译成BK(相对码)1、74LS74的1、4引脚解电源,3号引脚解BS-IN(同步信号),5号引脚(Q)输出到74LS86。

2DPSK调制解调电路设计引言:2DPSK(2-Differential Phase Shift Keying)是一种数字调制技术,常用于高速数据传输。

传统的2DPSK调制解调电路通常包含相位调制器、载波发生器、混频器、低通滤波器和相位解调器等模块。

本文将详细介绍2DPSK调制解调电路的设计过程。

设计目标:设计一个2DPSK调制解调电路,输入一个数字比特序列,经过调制后输出相位调制信号,再经过解调后得到原始的数字比特序列。

设计要求:1)基带信号频率为10kHz;2)载波频率为100kHz;3)输出信号的带宽小于基带信号频率。

设计过程:1.相位调制器设计:根据输入的数字比特序列产生相应的相位调制信号。

可以使用数字电路实现相位调制器,其中包括时钟发生器、计数器、比较器以及D触发器等元件。

时钟发生器产生一个基准时钟信号,计数器将基准时钟信号进行计数,计数值用来选择不同的比特序列。

比较器将输入的数字比特序列与计数器输出的比特序列进行比较,当两者相等时,则输出对应的相位调制信号。

2.载波发生器设计:载波发生器产生一个具有恒定频率和恒定幅度的正弦波信号。

可以使用晶振和放大器等元件实现载波发生器。

晶振将电能转换为机械能,使晶体振动,从而产生一个电压信号。

放大器对晶振产生的信号进行放大,以得到所需的载波信号。

3.相干混频器设计:相干混频器将相位调制信号与载波信号进行混频,产生一个带有相位信息的调制信号。

可以使用乘法器实现相干混频器,乘法器将相位调制信号与载波信号相乘,得到一个调幅信号。

此调幅信号中包含有载波频率和相位信息。

4.低通滤波器设计:低通滤波器将调幅信号中的高频分量滤除,只保留基带信号。

可以使用RC滤波器或者数字滤波器等元件实现低通滤波器。

RC滤波器通过一个电容和一个电阻组成,将高频分量通过电容的电势将其滤除。

数字滤波器通过计算和延迟等方法将高频分量去除。

5.相位解调器设计:相位解调器将调幅信号恢复为相位调制信号,从而实现相位信息的解调。

2DPSK系统的设计2DPSK(2-Differential Phase Shift Keying)是一种调制技术,适用于数字通信系统中的信息传输。

在设计2DPSK系统时,需要考虑多个方面,包括调制器、解调器、信道编码、抗噪声性能等。

首先,调制器是2DPSK系统的关键组成部分。

调制器负责将数字信息转换为相应的相位差,从而实现信息的调制。

在2DPSK中,采用两个相邻符号之间的相位差来表示不同数据。

可以通过使用延迟元件和相移元件来实现这一目的。

延迟元件可以引入一定的延迟,而相移元件可以改变信号的相位。

调制器的设计需要考虑相位差的准确性和稳定性。

其次,解调器是2DPSK系统中的关键组成部分。

解调器负责将接收到的模拟信号转换为数字信息。

解调器可以通过比较接收到的信号的相位差,来判断所传输的数据是0还是1、解调器的设计需要考虑相位差的准确性和噪声的抑制。

另外,信道编码在2DPSK系统中也非常重要。

信道编码可以提高系统的纠错性能,减少传输错误率。

常见的信道编码技术包括海明码、卷积码等。

这些编码技术可以通过增加冗余信息来增强系统的抗干扰和抗噪声性能。

在2DPSK系统的设计中,需要选取适当的信道编码方法,并合理选择编码参数,以达到性能最佳化。

在2DPSK系统的设计中,还需要考虑系统的带宽利用率和传输速率。

带宽利用率和传输速率一般是矛盾的,在设计中需要进行平衡。

可以通过适当的调制速率、编码方式和信道处理技术,以及合理选择调制器和解调器的参数,来提高两者的平衡性。

总的来说,2DPSK系统的设计需要考虑调制器、解调器、信道编码、抗噪声性能等多个方面。

在设计中,需要综合考虑各个方面的要求和问题,选择合适的方案和参数,从而实现系统的高性能和高可靠性。

2DPSK信号产生器的设计一、设计任务及要求:根据通信原理,设计一个2DPSK的基带信号调制器,即用基带信号(二进制)对载波信号(正弦波)进行调制,使载波信号的相位跟着基带信号进行变换,产生符合要求的2DPSK 信号进行发送。

要求:载波信号频率为2.2MHz。

信息码元速率自定,可以用模拟电路、数字电路、单片机、FPGA等方法进行设计,给出波形仿真结果。

二、设计方案:2DPSK调制器可用模拟法如图(a),也可用键控法如图(b)。

方案一:键控法,用数字电路来设计,方案框图如下:方案二:框图如下:由于FPGA系统频率可以达到几百兆赫兹,故系统时钟经过一定的分频可以得到载波信号——正弦波信号发生器的要求频率2.2MHz。

信息码经过差分运算后的输出信号控制正弦波信号发生器的不同相位输出(类似键控法),便可得到设计要求的2DPSK信号。

方案三:框图如下此方案由信息码进行差分编码后得到的差分码控制两个不同相位的正弦信号发生器的不同时间输出便可以得到2DPSK信号。

FPGA具有可编程逻辑器件现场可编程的灵活性,又具有门陈列器件功能强、高集成度和高速度的优点,因此在要求功能越来越强,体积越来越小,功耗越来越低的现代通信系统设计中被越来越广泛的应用。

而且这学期我们学习了FPGA的相关知识——《EDA技术使用教程》,且方案二只用设计一个正弦波信号发生器,因此选择方案二。

三、详细设计原理及实现方法二进制差分相移键控常简称为二相相对调相,记作2DPSK,是数字通信系统中常用的调制方式之一,2DPSK信号为模拟信号,而FPGA只能处理数字信号,因此,需对正弦信号采样再经过数/模变换得到所需的2DPSK信号,FPGA产生正弦信号的采样值。

(一)差分编码的设计2DPSK。

它不是利用载波相位的绝对数值传送数字信息,而是用前后码元的相对载波相位值传送数字信息。

所谓相对载波相位是指本码元初相与前一码元初相之差。

假设相对载波相位值用相位偏移表示,并规定数字信息序列与之间的关系为绝对码和相对码是可以互相转换的,其转换关系为由此转换关系可知,在FPGA应用中,用VHDL语言中的XOR(异或)语句即可实现差分编码。

(二)正弦波信号发生器的设计在FPGA程序设计应用中,用VHDL语言列出正弦波信号的抽样值即可实现正弦波信号发生器的设计,亦可通过定义宏功能模块建立正弦波喜欢发生器的LPM储存器的宏功能块来实现。

在本设计中,对正弦波每个周期采样100个点,即采样速率为原正弦信号频率的100倍,因此可以将原正弦信号不失真地恢复出来。

由于要求正弦波信号的频率为2.2MHz,而且对正弦波每个周期采样100个点,所以要求系统时钟频率应该为2.2MHz×100=220MHz。

这样即可实现设计要求的载波为2.2MHz的正弦波信号。

(三)分频器的设计由于对正弦波每个周期采样100个点,即100个正弦波周期内包含100个系统周期,故信息码的频率应为系统频率的1/100,故应设计出一个信息码的同步信号,搞信号应为系统频率的100分频,及要求设计1个100分频器,100分频器可用VHDL很容易实现。

(四)总体VHDL语言编程设计由上述分析可用VHDL语言编程实现2DPSK信号发生器的设计,程序及注释如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity MY2DPSK2 isport(rst,kongzhi,clk :in std_logic; --FPGA时钟输入x :in std_logic; --信息码输入z,aa_out :out std_logic; --相对码输出coderate1: out std_logic; --同步信号value1 :out std_logic_vector(7 downto 0)); -- 正弦波抽样值输出 end;architecture behav of MY2DPSK2 issignal xx,yy,aa:std_logic;signal q1,q2:std_logic_vector(6 downto 0);signal w:integer range 0 to 99;signal count100:std_logic_vector(6 downto 0);signal coderate:std_logic;beginprocess(clk) --100分频进程信号同步beginif(clk'event and clk='1') thenif kongzhi='1' thenif(count100="1100011") thencount100<="0000000";coderate<=not coderate;coderate1<=coderate;else count100<=count100+'1';end if;end if;end if;end process;process(clk) -- 差分编码进程beginif rst='1' then aa<='0';elsif (clk'event and clk='1' ) then aa<='1';if w=0 then w<=1;xx<=xx xor x; -- 现在XX是相对码z<=xx xor x; -- 现在z是相对码yy<=xx xor x; -- 现在YY是相对码elsif w=99 then w<=0;else w<=w+1;end if;end if;--Z<=YY;aa_out<=aa;end process;process(clk) --控制正弦波的不同相位输出beginif clk'event and clk='1' then q1<=q1+'1';if (q1="1100011" and yy='0') then --相对码YY为0时输出0°正弦波信号q1<="0000000";elsif (q1="1100011" and yy='1') thenq1<="0110010"; --相对码YY为0时输出180°正弦波信号end if;end if;end process;process(q1,clk,en,aa) -- 正弦波信号进程beginif clk'event and clk='1' thenif kongzhi='1' and aa='1' thencase q1 iswhen "0000000"=>value1<="01111111"; -- 0 127when"0000001"=>value1<="10000111"; -- 1 135when"0000010"=>value1<="10001111"; -- 2 143when"0000011"=>value1<="10010111";when"0000110"=>value1<="10101110";when"0000111"=>value1<="10110101";when"0001000"=>value1<="10111100";when"0001001"=>value1<="11000011";when"0001010"=>value1<="11001010";when"0001011"=>value1<="11010000";when"0001100"=>value1<="11010110";when"0001101"=>value1<="11011100";when"0001110"=>value1<="11100001";when"0001111"=>value1<="11100110";when"0010000"=>value1<="11101011";when"0010001"=>value1<="11101111";when"0010010"=>value1<="11110010"; when"0010011"=>value1<="11110110";when"0010100"=>value1<="11111000";when"0010101"=>value1<="11111010";when"0010110"=>value1<="11111100";when"0010111"=>value1<="11111101";when"0011000"=>value1<="11111110";when"0011001"=>value1<="11111111";when"0011010"=>value1<="11111110";when"0011011"=>value1<="11111101";when"0011100"=>value1<="11111100";when"0011101"=>value1<="11111010";when"0011110"=>value1<="11111000";when"0011111"=>value1<="11110110";when"0100000"=>value1<="11110010";when"0100001"=>value1<="11101111"; when"0100010"=>value1<="11101011";when"0100011"=>value1<="11100110";when"0100110"=>value1<="11010110";when"0100111"=>value1<="11010000";when"0101000"=>value1<="11001010";when"0101001"=>value1<="11000011";when"0101010"=>value1<="10111100";when"0101011"=>value1<="10110101";when"0101100"=>value1<="10101110";when"0101101"=>value1<="10100110";when"0101110"=>value1<="10011111";when"0101111"=>value1<="10010111";when"0110000"=>value1<="10001111"; ----- 48 143 when"0110001"=>value1<="10000111"; ----- 49 135 when"0110010"=>value1<="01111111"; ----- 50 127 when"0110011"=>value1<="01110111"; ------51 119 when"0110100"=>value1<="01101111"; ------52 111when"0110101"=>value1<="01100111"; ------53 103when"0110110"=>value1<="01011111";when"0110111"=>value1<="01011000";when"0111000"=>value1<="01010000";when"0111001"=>value1<="01001001";when"0111010"=>value1<="01000010";when"0111011"=>value1<="00111011";when"0111100"=>value1<="00110100";when"0111101"=>value1<="00101110";when"0111110"=>value1<="00101000";when"0111111"=>value1<="00100010";when"1000000"=>value1<="00011101";when"1000001"=>value1<="00011000";when"1000010"=>value1<="00010011";when"1000011"=>value1<="00001111";when"1000100"=>value1<="00001100";when"1000101"=>value1<="00001000";when"1001000"=>value1<="00000010";when"1001001"=>value1<="00000001";when"1001010"=>value1<="00000000"; ------74 0 when"1001011"=>value1<="00000000"; ------75 0 when"1001100"=>value1<="00000000"; ------76 0 when"1001101"=>value1<="00000001";when"1001110"=>value1<="00000010";when"1001111"=>value1<="00000100";when"1010000"=>value1<="00000110";when"1010001"=>value1<="00001000";when"1010010"=>value1<="00001100";when"1010011"=>value1<="00001111";when"1010100"=>value1<="00010011";when"1010101"=>value1<="00011000";when"1010110"=>value1<="00011101";when"1010111"=>value1<="00100100";when"1011000"=>value1<="00101000";when"1011001"=>value1<="00101110";when"1011010"=>value1<="00110100";when"1011011"=>value1<="00111011";when"1011100"=>value1<="01000010";when"1011101"=>value1<="01001001";when"1011110"=>value1<="01010000";when"1011111"=>value1<="01001000";when"1100000"=>value1<="01011111";when"1100001"=>value1<="01100111";when"1100010"=>value1<="01101111"; ------98 111 when"1100011"=>value1<="01110111"; ------99 119when others=>null;end case;end if;end if;end process;end ;四、设计仿真结果及分析:对上述程序进行仿真,设置好CLK的频率为220MHz,由于正弦波信号发生器是对一个正弦波周期的100个抽样点,故可以算出正弦波信号的频率为220MHz/100=2.2MHz。