第5章 存储器和IO空间

- 格式:ppt

- 大小:865.00 KB

- 文档页数:32

第二章 8086体系结构与80x86CPU1.8086CPU由哪两部分构成?它们的主要功能是什么?答:8086CPU由两部分组成:指令执行部件(EU,Execution Unit)和总线接口部件(BIU,Bus Interface Unit)。

指令执行部件(EU)主要由算术逻辑运算单元(ALU)、标志寄存器FR、通用寄存器组和EU控制器等4个部件组成,其主要功能是执行指令。

总线接口部件(BIU)主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数参加EU运算或存放运算结果等。

2.8086CPU预取指令队列有什么好处?8086CPU内部的并行操作体现在哪里?答:8086CPU的预取指令队列由6个字节组成,按照8086CPU的设计要求,指令执行部件(EU)在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在CPU内部,EU从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086系统中物理地址的形成过程。

8086系统中的物理地址最多有多少个?逻辑地址呢?答:8086系统中的物理地址是由20根地址总线形成的。

8086系统采用分段并附以地址偏移量办法形成20位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部分构成,都是16位二进制数。

通过一个20位的地址加法器将这两个地址相加形成物理地址。

具体做法是16位的段基址左移4位(相当于在段基址最低位后添4个“0”),然后与偏移地址相加获得物理地址。

由于8086CPU的地址线是20根,所以可寻址的存储空间为1M字节,即8086系统的物理地址空间是1MB。

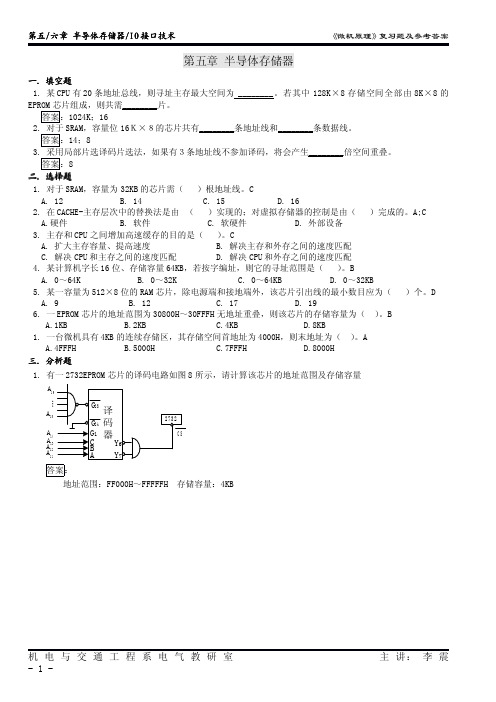

第五章半导体存储器一.填空题1.某CPU 有20条地址总线,则寻址主存最大空间为________。

若其中128K×8存储空间全部由8K×8的EPROM 答案:1024K;162.对于SRAM,容量位16K×8的芯片共有________条地址线和________条数据线。

答案:14;83.采用局部片选译码片选法,如果有3条地址线不参加译码,将会产生________倍空间重叠。

答案:8二.选择题1.对于SRAM,容量为32KB 的芯片需()根地址线。

CA.12B.14C.15D.162.在CACHE-主存层次中的替换法是由()实现的;对虚拟存储器的控制是由()完成的。

A;CA.硬件B.软件C.软硬件D.外部设备3.主存和CPU 之间增加高速缓存的目的是()。

CA.扩大主存容量、提高速度B.解决主存和外存之间的速度匹配C.解决CPU 和主存之间的速度匹配D.解决CPU 和外存之间的速度匹配4.某计算机字长16位、存储容量64KB,若按字编址,则它的寻址范围是()。

BA.0~64KB.0~32KC.0~64KBD.0~32KB5.某一容量为512×8位的RAM 芯片,除电源端和接地端外,该芯片引出线的最小数目应为()个。

DA.9B.12C.17D.196.一EPROM 芯片的地址范围为30800H~30FFFH 无地址重叠,则该芯片的存储容量为()。

BA.1KBB.2KBC.4KBD.8KB1.一台微机具有4KB 的连续存储区,其存储空间首地址为4000H,则末地址为()。

AA.4FFFHB.5000HC.7FFFHD.8000H三.分析题1.有一2732EPROM 芯片的译码电路如图8所示,请计算该芯片的地址范围及存储容量A 11A 12A 13A 14A 15A 19地址范围:FF000H~FFFFFH存储容量:4KB第六章I/O接口技术一.填空题1.CPU通过一个外设接口同外设之间交换的信息包括数据信息、状态信息和______,这三个信息通常都是通过CPU的______总线来传送到。

![[电脑基础知识]存储器原理与接口-du_OK](https://img.taocdn.com/s1/m/f8b43de655270722182ef7a6.png)

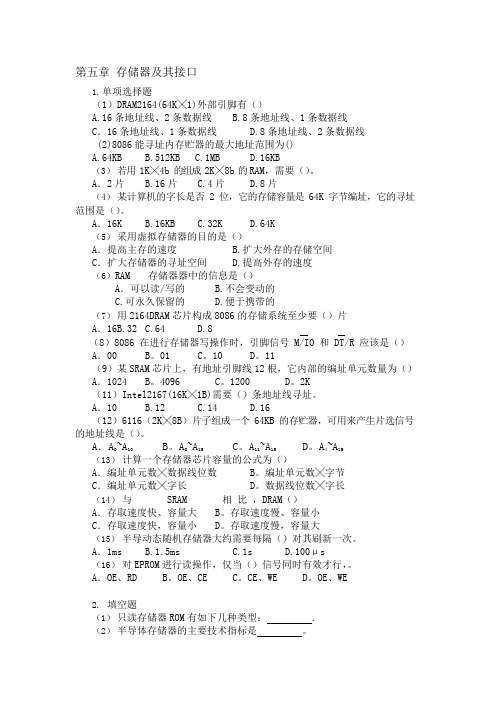

第五章存储器及其接口1.单项选择题(1)DRAM2164(64K╳1)外部引脚有()A.16 条地址线、2 条数据线B.8 条地址线、1 条数据线C.16 条地址线、1 条数据线 D.8 条地址线、2 条数据线(2)8086 能寻址内存贮器的最大地址范围为()A.64KBB.512KBC.1MBD.16KB(3)若用1K╳4b的组成2K╳8b的RAM,需要()。

A.2 片 B.16 片 C.4 片 D.8 片(4)某计算机的字长是否 2 位,它的存储容量是 64K 字节编址,它的寻址范围是()。

A.16K B.16KB C.32K D.64K(5)采用虚拟存储器的目的是()A.提高主存的速度 B.扩大外存的存储空间C.扩大存储器的寻址空间 D.提高外存的速度(6)RAM 存储器器中的信息是()A.可以读/写的 B.不会变动的C.可永久保留的D.便于携带的(7)用2164DRAM 芯片构成8086 的存储系统至少要()片A.16 B.32 C.64 D.8(8)8086 在进行存储器写操作时,引脚信号 M/IO 和 DT/R 应该是()A.00 B。

01 C。

10 D。

11(9)某SRAM 芯片上,有地址引脚线12 根,它内部的编址单元数量为()A.1024 B。

4096 C。

1200 D。

2K(11)Intel2167(16K╳1B)需要()条地址线寻址。

A.10 B.12 C.14 D.16(12)6116(2K╳8B)片子组成一个 64KB 的存贮器,可用来产生片选信号的地址线是()。

A.A0~A10B。

A~A15C。

A11~A15D。

A4~A19(13)计算一个存储器芯片容量的公式为()A.编址单元数╳数据线位数B。

编址单元数╳字节C.编址单元数╳字长D。

数据线位数╳字长(14)与 SRAM 相比,DRAM()A.存取速度快、容量大B。

存取速度慢、容量小C.存取速度快,容量小D。

存取速度慢,容量大(15)半导动态随机存储器大约需要每隔()对其刷新一次。

8086对存储器和io端口的编址方式-回复8086微处理器是Intel公司于1979年推出的一款16位微处理器,广泛应用于个人电脑和工业控制系统等领域。

在8086中,存储器和I/O端口被分别编址,下面将一步一步回答关于8086对存储器和I/O端口的编址方式的问题。

一、存储器的编址方式:8086微处理器使用20位地址总线,整个寻址空间范围为1MB(2^20)。

这种编址方式称为“段:偏移”地址形式。

1. 段选择器:在8086中,用于选择段的寄存器有CS(Code Segment, 代码段)、DS (Data Segment, 数据段)、SS(Stack Segment, 栈段)和ES(Extra Segment, 附加段)。

这些寄存器的值是16位的,用于存储存储器段的起始地址,偏移地址的计算需要与这些寄存器的值相结合。

2. 偏移地址:8086通过16位的偏移地址来表示存储器中的特定字节。

偏移地址可以是由程序员指定的常数,也可以是由程序中的地址计算得出的。

3. 存储器地址计算:8086微处理器将段选择器的值左移4位(乘以16),加上偏移地址的值。

例如,当使用DS和SI寄存器来指定一个存储器地址时,计算公式为:物理地址= DS * 16 + SI二、I/O端口的编址方式:8086微处理器使用16位地址总线寻址I/O端口。

I/O端口被视为存储器中的特殊地址,可以访问外部设备。

1. I/O端口地址空间:8086将I/O端口地址空间映射到存储器地址空间的一部分,称为I/O端口地址空间。

I/O端口地址空间的范围为0x0000到0xFFFF,共有65536个端口地址。

2. IN指令:IN指令用于从指定的I/O端口读取数据。

它需要提供一个8位或16位的端口地址。

IN指令执行时,8086将相应的端口地址发送给外部设备,然后接收来自该设备的数据。

例如,以下指令从I/O端口0x01 读取数据:IN AL, 0x013. OUT指令:OUT指令用于向指定的I/O端口写入数据。

第二章 8086 体系结构与80x86CPU1.8086CPU 由哪两部份构成?它们的主要功能是什么?答:8086CPU 由两部份组成:指令执行部件<EU,Execution Unit>和总线接口部件<BIU,Bus Interface Unit>。

指令执行部件〔EU 主要由算术逻辑运算单元<ALU>、标志寄存器F R、通用寄存器组和E U 控制器等4个部件组成,其主要功能是执行指令。

总线接口部件<BIU>主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或者I/O 端口读取操作数参加E U 运算或者存放运算结果等。

2.8086CPU 预取指令队列有什么好处? 8086CPU 内部的并行操作体现在哪里?答: 8086CPU 的预取指令队列由6个字节组成,按照8086CPU 的设计要求, 指令执行部件〔EU 在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在C PU 内部,EU 从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU 内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086 系统中物理地址的形成过程。

8086 系统中的物理地址最多有多少个?逻辑地址呢?答: 8086 系统中的物理地址是由20 根地址总线形成的。

8086 系统采用分段并附以地址偏移量办法形成20 位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部份构成,都是16 位二进制数。

通过一个20 位的地址加法器将这两个地址相加形成物理地址。

具体做法是16 位的段基址左移4位<相当于在段基址最低位后添4个"0">,然后与偏移地址相加获得物理地址。

第1章微型计算机概述1.微型计算机的硬件系统包括____A____.A.控制器、运算器、存储器和输入输出设备 B控制器、主机、键盘和显示器C.主机、电源、CPU和输入输出 D CPU、键盘、显示器和打印机2.CPU是由___B__组成的。

A.内存储器和控制器B.控制器和运算器C.内存储器和运算器D.内存储器、控制器和运算器3.中央处理器英文缩写是___B___。

A.MP B.CPU C.CU D.ALU4.微型计算机各部件之间是用__A___连接起来的。

A.系统总线B.AB C.CB D.DB5.通常计算机系统中的外围设备是指__A___A.外存储器、输入设备、输出设备B.外存储器、输入设备C.外存储器、输出设备D.输入设备、输出设备6.若把组成计算机中的运算器和控制器集成在一块芯片上成为___C__A.微型计算机B.单片机C.微处理器D.单板机7.8086是_C_A.单片机B.单板机C.微处理器D.微机系统8.将微处理器、内存储器及I/O接口连接起来的总线是__C_____。

A.片总线B.外总线C.系统总线D.局部总线9.微型计算机是以__B___为核心部件。

A.寄存器 B.微处理器 C.逻辑部件 D.控制部件10.微型计算机系统以__C__为主体。

A.系统软件 B.外部设备 C.微型计算机 D.操作系统11.目前微型机系统上广泛使用的机械式鼠标是一种___A___A.输入设备 B.输出设备C.输入输出设备 D.显示设备组成之一12.计算机系统总线中,用于传送读、写信号的是__C__。

A.地址总线B、数据总线C、控制总线D、以上都不对13.不属于微机应用特点的是__D__。

A.轻便、功耗低B.性能可靠C.结构灵活适宜性好D.应用面窄第2章 16位和32位微处理器1.当8086CPU的INTR=“1”时,且中断允许位IF=“1”,则CPU完成_C____后,响应该中断请求,进行中断处理。

A.当前时钟周期 B.当前总线周期 C.当前指令周期 D.下一个指令周期2.CPU的ALU主要完成_D_A.地址指针的变换B.中断管理C.产生各种时序D.算术,逻辑运算及移动操作3.8086/8088微机处理器的内部(C ),只负责指令的译码和执行.A.ALUB.BIUC.EUD.IEU4.8086CPU是__B___CPU。

第2章微型计算机基础2.8 在执行指令期间,BIU能直接访问存储器吗?为什么?解:可以.因为EU和BIU可以并行工作,EU需要的指令可以从指令队列中获得,这时BIU预先从存储器中取出并放入指令队列的。

在EU执行指令的同时,BIU 可以访问存储器取下一条指令或指令执行时需要的数据。

2.9 8086与8088CPU的主要区别有哪些?解:主要区别有以下几点:①8086的外部数据总线有16位,而8088的外部数据总线只有8位。

②8086指令队列深度为6个字节,而8088的指令队列深度为4个字节.③因为8086的外部数据总线有16位,故8086每个总线周期可以存取两个字节.而8088的外部数据总线因为只有8位,所以每个总线周期只能存取1个字节.④个别引脚信号的含义稍有不同.2.10 解:(1)要利用信号线包括WR#、RD#、IO/M#、ALE 以及AD0~AD7、A8~A19。

(2)同(1)。

(3)所有三态输出的地址信号、数据信号和控制信号均置为高阻态。

2.11解:在每个总线周期的T3的开始处若READY 为低电平,则CPU在T3后插入一个等待周期TW。

在TW的开始时刻,CPU还要检查READY状态,若仍为低电平,则再插入一个TW 。

此过程一直进行到某个TW开始时,READY已经变为高电平,这时下一个时钟周期才转入T4。

可以看出,插入TW周期的个数取决于READY电平维持的时间。

2.14 解:通用寄存器包含以下8个寄存器:AX、BX、CX和DX寄存器一般用于存放参与运算的数据或运算的结果。

除此之外:AX:主要存放算术逻辑运算中的操作数,以及存放I/O操作的数据。

BX:存放访问内存时的基地址。

CX:在循环和串操作指令中用作计数器。

DX:在寄存器间接寻址的I/O指令中存放I/O地址。

在做双字长乘除法运算时,DX与AX合起来存放一个双字长数。

SP:存放栈顶偏移地址。

BP:存放访问内存时的基地址。

SP和BP也可以存放数据,但它们的默认段寄存器都是SS。

第五章通用和复用功能IO口1.引言通用和复用功能IO口是现代数字电路设计中的重要组成部分。

它们允许电路与外部设备进行通信和控制,实现数据的输入、输出和处理。

在本章中,我们将介绍通用和复用功能IO口的基本原理和应用。

通用功能IO口是一种通用的输入/输出接口,可以通过软件来配置不同的功能。

它可以被用作输入口,用来读取外部设备的状态;也可以被用作输出口,用来控制外部设备的运行。

通用功能IO口通常由一组引脚组成,每个引脚都可以配置为不同的功能。

通过编程的方式,我们可以根据需要来选择引脚的功能,并进行相应的输入和输出操作。

复用功能IO口是一种多功能的输入/输出接口,可以通过硬件设置来选择不同的功能。

它通常由一个多路器和多个外设模块组成。

多路器的作用是选择不同的外设模块进行连接,从而实现不同的输入和输出功能。

使用复用功能IO口,可以有效地减少芯片上的引脚数量,提高系统的可扩展性和灵活性。

4.通用功能IO口的应用通用功能IO口广泛应用于各种数字电路设计中。

它可以连接各种外设设备,如按钮、开关、传感器、LED灯等。

通过编程的方式,我们可以读取外设的状态,并根据需要来控制外设的运行。

通用功能IO口还可以连接到其他数字电路中,实现数据的输入、输出和处理。

例如,它可以与存储器、处理器、通信接口等进行连接,实现数据的存储、处理和传输。

5.复用功能IO口的应用复用功能IO口广泛应用于嵌入式系统和通信系统中。

它可以连接各种外设设备,如显示器、触摸屏、以太网接口、USB接口等。

通过硬件设置,我们可以选择不同的外设模块进行连接,并根据需要来实现不同的输入和输出功能。

复用功能IO口还可以连接到其他模块中,实现数据的传输和处理。

例如,它可以与显示模块、通信模块等进行连接,实现图形的显示、数据的传输等。

6.小结通用和复用功能IO口是现代数字电路设计中的重要组成部分。

它们允许电路与外部设备进行通信和控制,实现数据的输入、输出和处理。

通过软件和硬件的配置,我们可以选择引脚的功能,并进行相应的输入和输出操作。

&电子工业出版社&第二章 8086体系结构与80x86CPU1.8086CPU由哪两部分构成?它们的主要功能是什么?答:8086CPU由两部分组成:指令执行部件(EU,Execution Unit)和总线接口部件(BIU,Bus Interface Unit)。

指令执行部件(EU)主要由算术逻辑运算单元(ALU)、标志寄存器FR、通用寄存器组和EU控制器等4个部件组成,其主要功能是执行指令。

总线接口部件(BIU)主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数参加EU运算或存放运算结果等。

2.8086CPU预取指令队列有什么好处?8086CPU内部的并行操作体现在哪里?答:8086CPU的预取指令队列由6个字节组成,按照8086CPU的设计要求,指令执行部件(EU)在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在CPU内部,EU从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086系统中物理地址的形成过程。

8086系统中的物理地址最多有多少个?逻辑地址呢?答:8086系统中的物理地址是由20根地址总线形成的。

8086系统采用分段并附以地址偏移量办法形成20位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部分构成,都是16位二进制数。

通过一个20位的地址加法器将这两个地址相加形成物理地址。

具体做法是16位的段基址左移4位(相当于在段基址最低位后添4个“0”),然后与偏移地址相加获得物理地址。

由于8086CPU的地址线是20根,所以可寻址的存储空间为1M字节,即8086系统的物理地址空间是1MB。