数电课后答案康华光第五版 完整

- 格式:pdf

- 大小:2.23 MB

- 文档页数:33

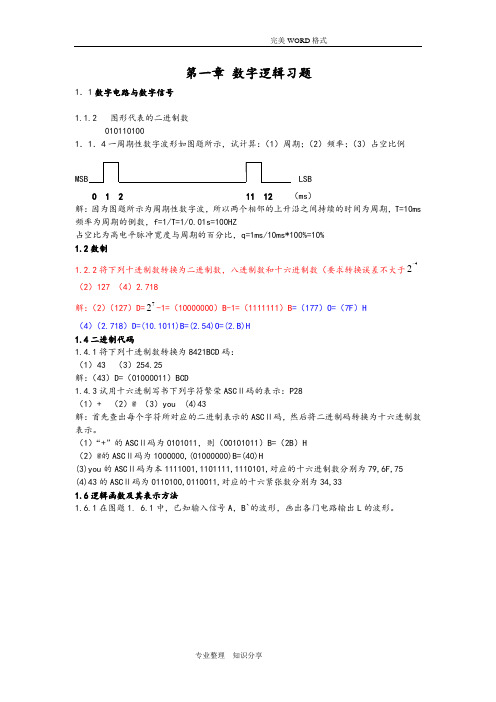

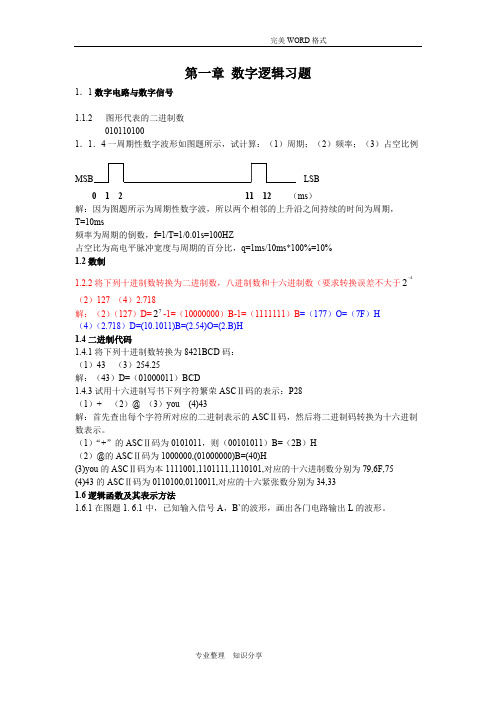

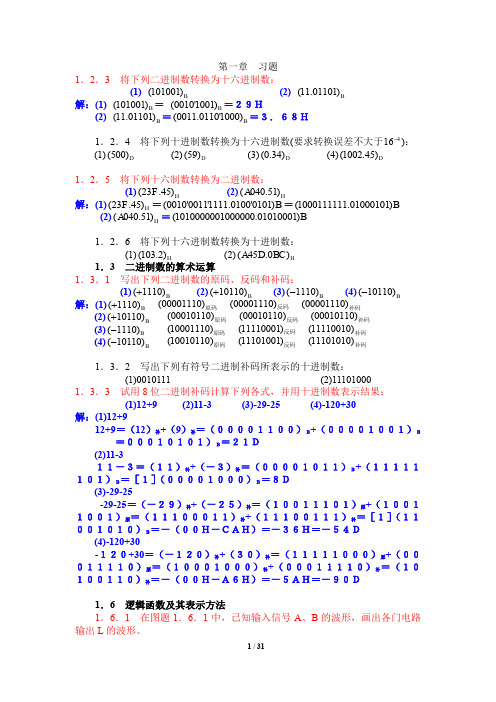

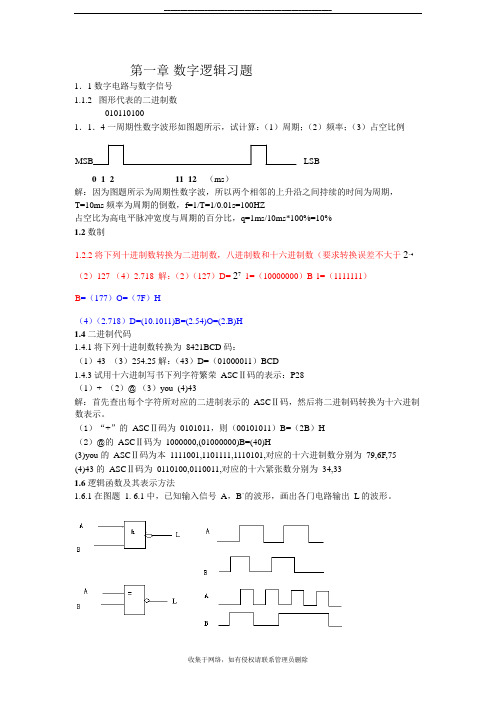

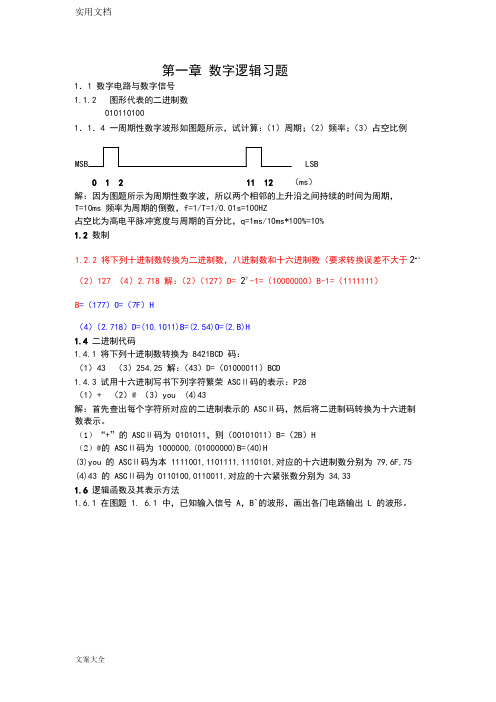

第一章数字逻辑习题1.1数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2数制2 1.2.2将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于4(2)127 (4)2.718解:(2)(127)D=72-1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4二进制代码1.4.1将下列十进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1.4.3试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6逻辑函数及其表示方法1.6.1在图题1. 6.1中,已知输入信号A,B`的波形,画出各门电路输出L的波形。

解: (a)为与非, (b)为同或非,即异或第二章 逻辑代数 习题解答2.1.1 用真值表证明下列恒等式 (3)A B AB AB ⊕=+(A ⊕B )=AB+AB 解:真值表如下A B A B ⊕ABAB A B ⊕AB +AB0 0 0 1 0 1 1 0 1 1 0 0 0 0 1 0 1 0 0 0 0 11111由最右边2栏可知,A B ⊕与AB +AB 的真值表完全相同。

gragnieban dAl l t h i ng st he i rb ei n gtllAdnaemitaat i me an d2>由真值表画出卡诺图eragniebnisgnihtllAdehtnisgnhtllAdnaet h 000=(Vcc-ehtnisgan dAl l t h i ni nt he i rb ei D I 4.5mA解:由逻辑电路写出逻辑表达式L AB AB A B=+=A 信号相同时,输出为1,不同时,输出为0如图所示试用2输入与非门设计一个3输入的组合逻辑电路。

当输入的二进制码小于;输入大于等于3时,输出为1。

根据组合逻辑的设计过程,首先要确定输入输出变量,列出真值表。

由卡诺图化简得到最简与或式,然后根据要求对表达式进行变换,画出逻辑图Al l t h i ng si nt he *L A BC A BC=+=用2输入与非门实现上述逻辑表达式某足球评委会由一位教练和三位球迷组成,对裁判员的判罚进行表决。

当满足以下条件时表示同意;有三人或三人以上同意,或者有两人同意,但其中一人是叫教练。

输入与非门设计该表决电路。

)设一位教练和三位球迷分别用A 和时表示不同意,输出L 表示表决结果。

me an dAl l t h i ng si n由卡诺图化简得L=AB+AC+AD+BCD由于规定只能用2输入与非门,将上式变换为两变量的与非 ****L AB AC AD BCD AB AC ==.3 判断图所示电路在什么条件下产生竞争冒险,怎at i me an dAl l t h i ng si nt he i rb 解: 根据电路图写出逻辑表达式并化简得*L A B = 当A=0,C=1时, 有可能产生竞争冒险,为消除可能产生的竞争冒险,L B B =+4.4.4 试用74HC147设计键盘编码电路,十个按键分别对应十进制数为8421BCD 码。

要求按键9的优先级别最高,并且有工作状态标志,以说明没有按键按下和按键0按下两种情况。

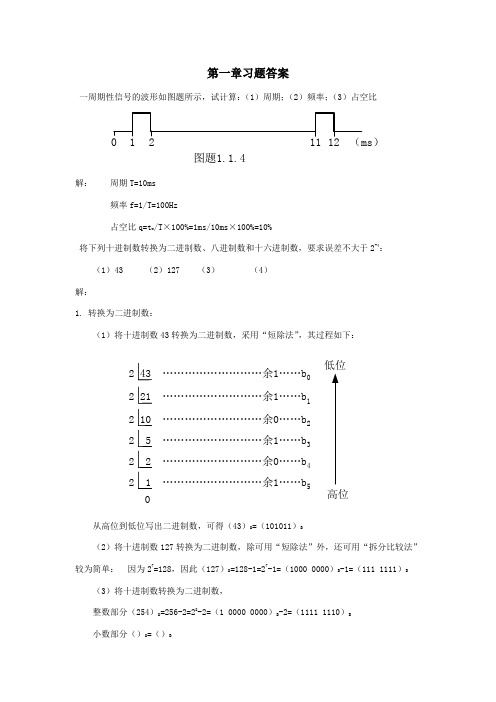

第一章习题答案一周期性信号的波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比0121112(ms)图题1.1.4解: 周期T=10ms 频率f=1/T=100Hz占空比q=t w /T ×100%=1ms/10ms ×100%=10%将下列十进制数转换为二进制数、八进制数和十六进制数,要求误差不大于2-4:(1)43(2)127(3)(4)解:1. 转换为二进制数:(1)将十进制数43转换为二进制数,采用“短除法”,其过程如下:2 43 ………………………余1……b 02 21 ………………………余1……b 12 1 ………………………余1……b 52 2 ………………………余0……b 42 5 ………………………余1……b 32 10 ………………………余0……b 2高位低位从高位到低位写出二进制数,可得(43)D =(101011)B(2)将十进制数127转换为二进制数,除可用“短除法”外,还可用“拆分比较法”较为简单: 因为27=128,因此(127)D =128-1=27-1=(1000 0000)B -1=(111 1111)B(3)将十进制数转换为二进制数,整数部分(254)D =256-2=28-2=(1 0000 0000)B -2=(1111 1110)B 小数部分()D =()B()D=(1111 )B(4)将十进制数转换为二进制数整数部分(2)D=(10)B小数部分()D=()B演算过程如下:0.718×2=1.436……1……b-1 0.436×2=0.872……0……b-2 0.872×2=1.744……1……b-3 0.744×2=1.488……1……b-4 0.488×2=0.976……0……b-5 0.976×2=1.952……1……b-6高位低位要求转换误差小于2-4,只要保留小数点后4位即可,这里算到6位是为了方便转换为8进制数。

数电课后标准答案康华光第五版(完整)第⼀章数字逻辑习题1.1数字电路与数字信号1.1.2 图形代表的⼆进制数0101101001.1.4⼀周期性数字波形如图题所⽰,试计算:(1)周期;(2)频率;(3)占空⽐例MSB LSB0 1 2 11 12 (ms)解:因为图题所⽰为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空⽐为⾼电平脉冲宽度与周期的百分⽐,q=1ms/10ms*100%=10%1.2数制2 1.2.2将下列⼗进制数转换为⼆进制数,⼋进制数和⼗六进制数(要求转换误差不⼤于4(2)127 (4)2.718解:(2)(127)D=72-1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4⼆进制代码1.4.1将下列⼗进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1.4.3试⽤⼗六进制写书下列字符繁荣ASCⅡ码的表⽰:P28(1)+ (2)@ (3)you (4)43解:⾸先查出每个字符所对应的⼆进制表⽰的ASCⅡ码,然后将⼆进制码转换为⼗六进制数表⽰。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的⼗六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的⼗六紧张数分别为34,331.6逻辑函数及其表⽰⽅法1.6.1在图题1. 6.1中,已知输⼊信号A,B`的波形,画出各门电路输出L的波形。

解: (a)为与⾮, (b)为同或⾮,即异或第⼆章逻辑代数习题解答2.1.1 ⽤真值表证明下列恒等式 (3)A B AB AB ⊕=+(A ⊕B )=AB+AB 解:真值表如下A B A B ⊕ABAB A B ⊕AB +AB0 0 0 1 0 1 1 0 1 1 0 0 0 0 1 0 1 0 0 0 0 11111由最右边2栏可知,A B ⊕与AB +AB 的真值表完全相同。

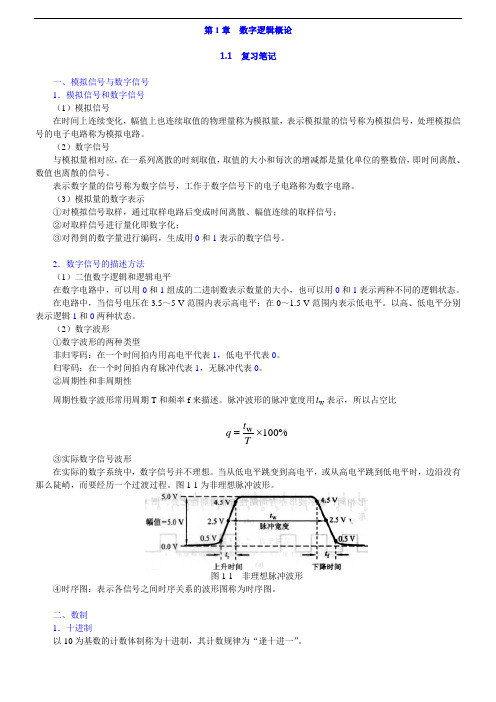

第1章 数字逻辑概论1.1 复习笔记一、模拟信号与数字信号 1.模拟信号和数字信号 (1)模拟信号在时间上连续变化,幅值上也连续取值的物理量称为模拟量,表示模拟量的信号称为模拟信号,处理模拟信号的电子电路称为模拟电路。

(2)数字信号 与模拟量相对应,在一系列离散的时刻取值,取值的大小和每次的增减都是量化单位的整数倍,即时间离散、数值也离散的信号。

表示数字量的信号称为数字信号,工作于数字信号下的电子电路称为数字电路。

(3)模拟量的数字表示①对模拟信号取样,通过取样电路后变成时间离散、幅值连续的取样信号; ②对取样信号进行量化即数字化;③对得到的数字量进行编码,生成用0和1表示的数字信号。

2.数字信号的描述方法(1)二值数字逻辑和逻辑电平在数字电路中,可以用0和1组成的二进制数表示数量的大小,也可以用0和1表示两种不同的逻辑状态。

在电路中,当信号电压在3.5~5 V 范围内表示高电平;在0~1.5 V 范围内表示低电平。

以高、低电平分别表示逻辑1和0两种状态。

(2)数字波形①数字波形的两种类型非归零码:在一个时间拍内用高电平代表1,低电平代表0。

归零码:在一个时间拍内有脉冲代表1,无脉冲代表0。

②周期性和非周期性周期性数字波形常用周期T 和频率f 来描述。

脉冲波形的脉冲宽度用W t 表示,所以占空比100%t q T=⨯W③实际数字信号波形在实际的数字系统中,数字信号并不理想。

当从低电平跳变到高电平,或从高电平跳到低电平时,边沿没有那么陡峭,而要经历一个过渡过程。

图1-1为非理想脉冲波形。

图1-1 非理想脉冲波形④时序图:表示各信号之间时序关系的波形图称为时序图。

二、数制 1.十进制以10为基数的计数体制称为十进制,其计数规律为“逢十进一”。

任意十进制可表示为:()10iDii N K ∞=-∞=⨯∑式中,i K 可以是0~9中任何一个数字。

如果将上式中的10用字母R 代替,则可以得到任意进制数的表达式:()iR ii N K R ∞=-∞=⨯∑2.二进制(1)二进制的表示方法以2为基数的计数体制称为二进制,其只有0和1两个数码,计数规律为“逢二进一”。

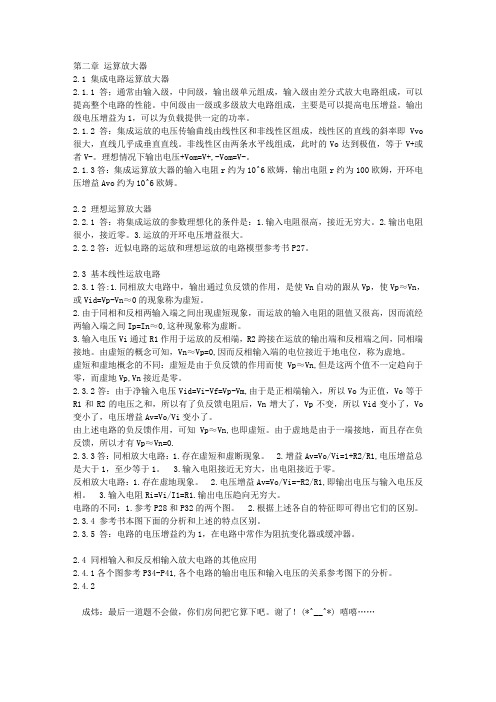

第二章运算放大器2.1 集成电路运算放大器2.1.1答;通常由输入级,中间级,输出级单元组成,输入级由差分式放大电路组成,可以提高整个电路的性能。

中间级由一级或多级放大电路组成,主要是可以提高电压增益。

输出级电压增益为1,可以为负载提供一定的功率。

2.1.2答:集成运放的电压传输曲线由线性区和非线性区组成,线性区的直线的斜率即Vvo 很大,直线几乎成垂直直线。

非线性区由两条水平线组成,此时的Vo达到极值,等于V+或者V-。

理想情况下输出电压+Vom=V+,-Vom=V-。

2.1.3答:集成运算放大器的输入电阻r约为10^6欧姆,输出电阻r约为100欧姆,开环电压增益Avo约为10^6欧姆。

2.2 理想运算放大器2.2.1答:将集成运放的参数理想化的条件是:1.输入电阻很高,接近无穷大。

2.输出电阻很小,接近零。

3.运放的开环电压增益很大。

2.2.2答:近似电路的运放和理想运放的电路模型参考书P27。

2.3 基本线性运放电路2.3.1答:1.同相放大电路中,输出通过负反馈的作用,是使Vn自动的跟从Vp,使Vp≈Vn,或Vid=Vp-Vn≈0的现象称为虚短。

2.由于同相和反相两输入端之间出现虚短现象,而运放的输入电阻的阻值又很高,因而流经两输入端之间Ip=In≈0,这种现象称为虚断。

3.输入电压Vi通过R1作用于运放的反相端,R2跨接在运放的输出端和反相端之间,同相端接地。

由虚短的概念可知,Vn≈Vp=0,因而反相输入端的电位接近于地电位,称为虚地。

虚短和虚地概念的不同:虚短是由于负反馈的作用而使Vp≈Vn,但是这两个值不一定趋向于零,而虚地Vp,Vn接近是零。

2.3.2答:由于净输入电压Vid=Vi-Vf=Vp-Vm,由于是正相端输入,所以Vo为正值,Vo等于R1和R2的电压之和,所以有了负反馈电阻后,Vn增大了,Vp不变,所以Vid变小了,Vo 变小了,电压增益Av=Vo/Vi变小了。

由上述电路的负反馈作用,可知Vp≈Vn,也即虚短。

第一章习题答案1.1.4 一周期性信号的波形如图题1.1.4所示,试计算:(1)周期;(2)频率;(3)占空比012(ms)图题1.1.4解: 周期T=10ms 频率f=1/T=100Hz 占空比q=t w /T ×100%=1ms/10ms ×100%=10%1.2.2 将下列十进制数转换为二进制数、八进制数和十六进制数,要求误差不大于2-4: (1)43 (2)127 (3)254.25 (4)2.718 解:1. 转换为二进制数:(1)将十进制数43转换为二进制数,采用“短除法”,其过程如下:2 43 ………………………余1……b 02 21 ………………………余1……b 12 1 ………………………余1……b 52 2 ………………………余0……b 42 5 ………………………余1……b 32 10 ………………………余0……b20高位低位从高位到低位写出二进制数,可得(43)D =(101011)B(2)将十进制数127转换为二进制数,除可用“短除法”外,还可用“拆分比较法”较为简单: 因为27=128,因此(127)D =128-1=27-1=(1000 0000)B -1=(111 1111)B(3)将十进制数254.25转换为二进制数,整数部分(254)D =256-2=28-2=(1 0000 0000)B -2=(1111 1110)B 小数部分(0.25)D =(0.01)B (254.25)D =(1111 1110.01)B(4)将十进制数2.718转换为二进制数 整数部分(2)D =(10)B小数部分(0.718)D =(0.1011)B 演算过程如下:0.718×2=1.436……1……b-1 0.436×2=0.872……0……b-2 0.872×2=1.744……1……b-3 0.744×2=1.488……1……b-4 0.488×2=0.976……0……b-5 0.976×2=1.952……1……b-6高位低位要求转换误差小于2-4,只要保留小数点后4位即可,这里算到6位是为了方便转换为8进制数。

第一章数字逻辑习题1.1 数字电路与数字信号图形代表的二进制数1.1.4 一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%数制将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于24(2)127 (4)解:(2)(127)D= 27 -1=()B-1=(1111111)B=(177)O=(7F)H(4)()D=B=O=H二进制代码将下列十进制数转换为 8421BCD 码:(1)43 (3)解:(43)D=(01000011)BCD试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为 0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为 1000000,(01000000)B=(40)H(3)you 的ASCⅡ码为本 1111001,1101111,1110101,对应的十六进制数分别为 79,6F,75(4)43 的ASCⅡ码为 0110100,0110011,对应的十六紧张数分别为 34,33 逻辑函数及其表示方法在图题 1. 中,已知输入信号 A,B`的波形,画出各门电路输出 L 的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答用真值表证明下列恒等式(3)A⊕ =B AB AB+(A⊕B)=AB+AB用逻辑代数定律证明下列等式(3)A+ABC ACD C D E A CD E+ + +( ) = + + 解:A+ABC ACD C D E+ + +( )=A(1+BC ACD CDE)+ += +A ACD CDE+= +A CD CDE+ = +A CD+ E用代数法化简下列各式(3) ABC B( +C) 解:ABC B( +C)= + +(A B C B C)( + )=AB AC BB BC CB C++ + + +=AB C A B B+ ( + + +1)=AB C+(6)(A+ + + +B A B AB AB) ( ) ()( ) 解:(A+ + + +B A B ABAB) ( ) ( )( )= A B + A B+(A+ B A)(+ B)=AB(9)ABCD ABD BCD ABCBD BC+ + + + 解:ABCD ABD BCD ABCBD BC+ + + + =ABC D D ABD BC D C( + +) + ( + ) =B AC AD C D( + + + ) =B A C A D( + + + ) =B A C D( + + ) =AB BC BD+ +画出实现下列逻辑表达式的逻辑电路图,限使用非门和二输入与非门B AB AB = + + AB B = + A B= + (1) L AB AC= + (2) ( ) L DAC= +已知函数L (A ,B ,C ,D )的卡诺图如图所示,试写出函数L 的最简与或表达式用卡诺图化简下列个式(3)( )() L ABCD=+ + 解: ( , , , ) L ABCDBCDBCDBCDABD= + + +(1)ABCD ABCD AB AD ABC++ + + 解:ABCD ABCD AB AD ABC+ + + +=ABCD ABCD ABC C D D AD B B C C ABC D D+ + ( + )( + +) ( + )( + +) ( + ) =ABCD ABCD ABCD ABCD ABCD ABCD ABCD+ + ++ + +(6)L A B C D( , , , ) =∑m (0,2,4,6,9,13)+∑d(1,3,5,7,11,15)L= +A D(7)L A B C D( , , , ) =∑m (0,13,14,15)+∑d(1,2,3,9,10,11)L AD AC AB=+ +解:解:已知逻辑函数L AB BC CA= + +,试用真值表,卡诺图和逻辑图(限用非门和与非门)表示解:1>由逻辑函数写出真值表A B C L0 0 0 00 0 1 10 1 0 10 1 1 11 0 0 11 0 1 11 1 0 11 1 1 0用摩根定理将与或化为与非表达式L = AB + BC + AC = AB BC AC4>由已知函数的与非-与非表达式画出逻辑图2>由真值表画出卡诺图3>由卡诺图,得逻辑表达式LABBCAC=++第三章习题MOS 逻辑门电路根据表题所列的三种逻辑门电路的技术参数,试选择一种最合适工作在高噪声环境下的门电路。

第一章数字逻辑习题1.1数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSBLSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2数制1.2.2将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于 42.(2)127 (4)2.718解:(2)(127)D=-1=(10000000)B-1=(1111111)B=(177)O=(7F)H 72(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4二进制代码1.4.1将下列十进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1.4.3试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6逻辑函数及其表示方法1.6.1在图题1. 6.1中,已知输入信号A,B`的波形,画出各门电路输出L的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答2.1.1 用真值表证明下列恒等式(3)ABABAB⊕=+(A⊕B)=AB+AB 解:真值表如下ABAB⊕ABABAB⊕AB+AB111111111111由最右边2栏可知,与AB+AB的真值表完全相同。

第一章数字逻辑习题1.1 数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4 一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSBLSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2 数制1.2.2 将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于42. (2)127 (4)2.718解:(2)(127)D=-1=(10000000)B-1=(1111111)B=(177)O=(7F)H 72(4)(2.718 )D=(10.1011)B=(2.54)O=(2.B)H1.4 二进制代码1.4.1 将下列十进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1.4.3 试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@(3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

...4>由已知函数的与非-与非表达式画出逻辑图...4>由已知函数的与非-与非表达式画出逻辑图4>由已知函数的与非-与非表达式画出逻辑图4>由已知函数的与非-与非表达式画出逻辑图...OLV=0.1V, ILV=1.5V, 因此有:(1) =0< ViILV=1.5V, 属于逻辑门0(2) <1.5V=ViILV, 属于逻辑门0(3) <0.1<ViILV=1.5V, 属于逻辑门0(4) 由于CMOS管的栅极电流非常小, 通常小于1uA,在10kΩ电阻上产生的压降小于10mV即...OLV=0.1V, ILV=1.5V, 因此有:(1) =0< ViILV=1.5V, 属于逻辑门0(2) <1.5V=ViILV, 属于逻辑门0(3) <0.1<ViILV=1.5V, 属于逻辑门0(4) 由于CMOS管的栅极电流非常小, 通常小于1uA,在10kΩ电阻上产生的压降小于10mV即OLV=0.1V, ILV=1.5V, 因此有:(1) =0< ViILV=1.5V, 属于逻辑门0(2) <1.5V=ViILV, 属于逻辑门0(3) <0.1<ViILV=1.5V, 属于逻辑门0(4) 由于CMOS管的栅极电流非常小, 通常小于1uA,在10kΩ电阻上产生的压降小于10mV即...高阻113.1.12 (a)AL11...高阻113.1.12 (a)AL11高阻113.1.12 (a)AL11高阻113.1.12 (a)AL11高阻113.1.12 (a)AL11高阻113.1.12 (a)AL11...1.1.3vmA..≈444Ω...1.1.4vmA..≈444Ω...1111111111110 1 0 0 1 0 0 0 1 1 1 1 0 0 1 1 0 1 1 1 10 1 0 0 1 0 0 0 1 1 1 1 0 0 1 1 0 1 1 1 11 0 0 0 1 1 1 1 1 0 0 0 0 1 0 0 1 1 1 0 111112 )由真值表画卡诺图11112 )由真值表画卡诺图11112 )由真值表画卡诺图11112 )由真值表画卡诺图11112 )由真值表画卡诺图11112 )由真值表画卡诺图...输入输出ABCLL=C1111__LC=...输入输出ABCLL=C 01111__ LC=输入输出ABCLL=C 01111__ LC=输入输出ABCLL=C 01111__ LC=第六章习题答案1.1.5已知某时序电路的状态表如表题6.1,6所示,输人为A,试画出它的状态图。

第一章数字逻辑习题1.1 数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4 一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2 数制1.2.2 将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于2−4(2)127 (4)2.718解:(2)(127)D= 27 -1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4 二进制代码1.4.1 将下列十进制数转换为8421BCD 码:(1)43 (3)254.25 解:(43)D=(01000011)BCD1.4.3 试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you 的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43 的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6 逻辑函数及其表示方法1.6.1 在图题1. 6.1 中,已知输入信号A,B`的波形,画出各门电路输出L 的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答2.1.1 用真值表证明下列恒等式(3)A⊕ =B AB AB+ (A⊕B)=AB+AB解:真值表如下由最右边2栏可知,A⊕B与AB+AB的真值表完全相同。

第一章数字逻辑习题1.1数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSBLSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2数制1.2.2将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于 42. (2)127 (4)2.718解:(2)(127)D=-1=(10000000)B-1=(1111111)B=(177)O=(7F)H 72 (4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4二进制代码1.4.1将下列十进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1.4.3试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6逻辑函数及其表示方法1.6.1在图题1. 6.1中,已知输入信号A,B`的波形,画出各门电路输出L的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答2.1.1 用真值表证明下列恒等式(3)ABABAB⊕=+(A⊕B)=AB+AB 解:真值表如下ABAB⊕ABABAB⊕AB+AB111111111111由最右边2栏可知,与AB+AB的真值表完全相同。

第一章数字逻辑习题1.1 数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4 一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2 数制1.2.2 将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于2−4(2)127 (4)2.718 解:(2)(127)D= 27 -1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4 二进制代码1.4.1 将下列十进制数转换为 8421BCD 码:(1)43 (3)254.25 解:(43)D=(01000011)BCD1.4.3 试用十六进制写书下列字符繁荣 ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的 ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的 ASCⅡ码为 0101011,则(00101011)B=(2B)H(2)@的 ASCⅡ码为 1000000,(01000000)B=(40)H(3)you 的 ASCⅡ码为本 1111001,1101111,1110101,对应的十六进制数分别为 79,6F,75(4)43 的 ASCⅡ码为 0110100,0110011,对应的十六紧张数分别为 34,331.6 逻辑函数及其表示方法1.6.1 在图题 1. 6.1 中,已知输入信号 A,B`的波形,画出各门电路输出 L 的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答2.1.1 用真值表证明下列恒等式(3)A⊕ =B AB AB+ (A⊕B)=AB+AB解:真值表如下由最右边2栏可知,A⊕B与AB+AB的真值表完全相同。

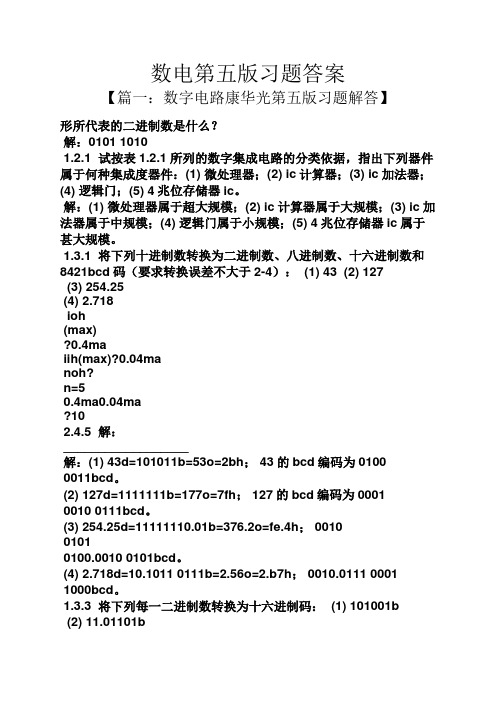

数电第五版习题答案【篇一:数字电路康华光第五版习题解答】形所代表的二进制数是什么?解:0101 10101.2.1 试按表1.2.1所列的数字集成电路的分类依据,指出下列器件属于何种集成度器件:(1) 微处理器;(2) ic计算器;(3) ic加法器;(4) 逻辑门;(5) 4兆位存储器ic。

解:(1) 微处理器属于超大规模;(2) ic计算器属于大规模;(3) ic加法器属于中规模;(4) 逻辑门属于小规模;(5) 4兆位存储器ic属于甚大规模。

1.3.1 将下列十进制数转换为二进制数、八进制数、十六进制数和8421bcd码(要求转换误差不大于2-4): (1) 43 (2) 127(3) 254.25(4) 2.718ioh(max)?0.4maiih(max)?0.04manoh?n=50.4ma0.04ma?102.4.5 解:__________________解:(1) 43d=101011b=53o=2bh; 43的bcd编码为01000011bcd。

(2) 127d=1111111b=177o=7fh; 127的bcd编码为00010010 0111bcd。

(3) 254.25d=11111110.01b=376.2o=fe.4h; 001001010100.0010 0101bcd。

(4) 2.718d=10.1011 0111b=2.56o=2.b7h; 0010.0111 00011000bcd。

1.3.3 将下列每一二进制数转换为十六进制码: (1) 101001b(2) 11.01101b解:(1) 101001b=29h (2) 11.01101b=3.68h1.3.4 将下列十进制转换为十六进制数:(1) 500d(2) 59d(3) 0.34d(4) 1002.45d解:(1) 500d=1f4h(2) 59d=3bh(3) 0.34d=0.570ah(4) 1002.45d=3ea.7333h1.3.5 将下列十六进制数转换为二进制数:(1) 23f.45h(2) a040.51h解:(1) 23f.45h=10 0011 1111.0100 0101b(2) a040.51h=1010 0000 0100 0000.0101 0001b1.3.6 将下列十六进制数转换为十进制数: (1) 103.2h(2) a45d.0bch解:(1) 103.2h=259.125d (2) a45d.0bch=41024.046d 2.4.3 解:(1) lsttl驱动同类门iol(max)?8maiil(max)?0.4man8maol?0.4ma?20ioh(max)?0.4maiih(max)?0.02man4maoh?0.0.02ma?20n=20(2) lsttl驱动基本ttl门iol(max)?8maiil(max)?1.6manmaol?81.6ma?5________l?ab?bc?d?e?ab?bc?d?e2.6.3 解:b=0时,传输门开通,l=a;b=1时,传输门关闭,a相当于经过3个反相器到达输出l,l=aa b l0 00 0 11 1 01 1 10所以,l?ab?ab?a?b 2.7.1 解:__________c,bc?bc__________d,ed?de________________________________________________________________bc?de,abc?de?a(bc?de)_________________________________________________________________________________af?gf,eaf?gf?e(af?gf)?ef(a?g)______________________________________________________ __________3.1.3 ____用代数法化简下列等式 (a) ab(bc?a)l?a(bc?de)?ef(a?g)?a(bc?de)?ef(ag)2.7.2 解:ab(bc?a)?abc?ab?ab(b) (a?b)(ab)(a?b)(ab)?ab________________________ab?b?a?ab?(a?b)?ab?ab?a?b_________(c) abc(b?c)_______l?a?b=a⊙babc(b?c)?(a?b?c)(b?c)?ab?bc?ac?bc?c?ab?c2.9.11 解:当没有车辆行驶时,道路的状态设为0,有车辆行驶时,道路的状态为1;通道允许行驶时的状态设为1,不允许行驶时的状态设为0。

第一章数字逻辑习题1.1数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2数制2 1.2.2将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于4(2)127 (4)2.718解:(2)(127)D=72-1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4二进制代码1.4.1将下列十进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1.4.3试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6逻辑函数及其表示方法1.6.1在图题1. 6.1中,已知输入信号A,B`的波形,画出各门电路输出L的波形。

解: (a)为与非, (b)为同或非,即异或第二章 逻辑代数 习题解答2.1.1 用真值表证明下列恒等式 (3)A B AB AB ⊕=+(A ⊕B )=AB+AB 解:真值表如下A B A B ⊕ABAB A B ⊕AB +AB0 0 0 1 0 1 1 0 1 1 0 0 0 0 1 0 1 0 0 0 0 11111由最右边2栏可知,A B ⊕与AB +AB 的真值表完全相同。

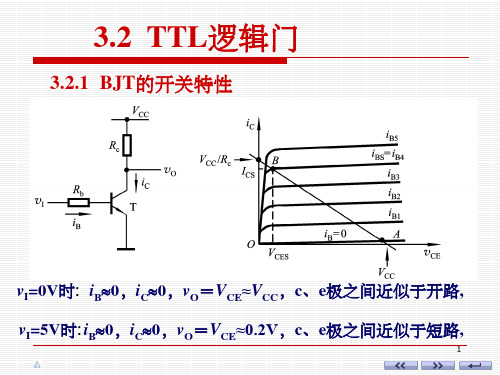

2.1.3 用逻辑代数定律证明下列等式(3)()A ABC A CD C D E A CD E ++++=++ 解:()A ABC A CD C D E ++++ (1)A BC A CD CDE =+++ A A CD CDE =++ A CD CDE =++A CD E =++2.1.4 用代数法化简下列各式 (3)()ABC B C + 解:()ABC B C +()()A B C B C =+++AB AC BB BC CB C =+++++ (1)AB C A B B =++++AB C =+(6)()()()()A B A B AB AB ++++ 解:()()()()A B A B AB AB ++++()()A B A B A B A B =⋅+⋅+++B AB AB =++ AB B =+ A B =+ AB =(9)ABCD ABD BCD ABCBD BC ++++ 解:ABCD ABD BCD ABCBD BC ++++()()()()()ABC D D ABD BC D C B AC AD C D B A C A D B A C D AB BC BD=++++=+++=+++=++=++2.1.7 画出实现下列逻辑表达式的逻辑电路图,限使用非门和二输入与非门 (1)L AB AC =+(2)()L D A C =+(3)()()L A B C D =++2.2.2 已知函数L (A ,B ,C ,D )的卡诺图如图所示,试写出函数L 的最简与或表达式解:(,,,)L A B C D BCD BCD BCD ABD =+++ 2.2.3 用卡诺图化简下列个式(1)ABCD ABCD AB AD ABC ++++ 解:ABCD ABCD AB AD ABC ++++()()()()()ABCD ABCD AB C C D D AD B B C C ABC D D =+++++++++ABCD ABCD ABCD ABCD ABCD ABCD ABCD =++++++(6)(,,,)(0,2,4,6,9,13)(1,3,5,7,11,15)L A B C D m d =+∑∑解:L A D =+(7)(,,,)(0,13,14,15)(1,2,3,9,10,11)L A B C D m d =+∑∑解:L AD AC AB =++2.2.4 已知逻辑函数L AB BC C A =++,试用真值表,卡诺图和逻辑图(限用非门和与非门)表示解:1>由逻辑函数写出真值表A B C L 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1112>由真值表画出卡诺图3>由卡诺图,得逻辑表达式L AB BC A C =++ 用摩根定理将与或化为与非表达式L AB BC A C AB BC A C =++=⋅⋅4>由已知函数的与非-与非表达式画出逻辑图第三章习题3.1 MOS 逻辑门电路3.1.1根据表题3.1.1所列的三种逻辑门电路的技术参数,试选择一 种最合适工作在高噪声环境下的门电路。

表题3.1.1 逻辑门电路的技术参数表(min)/OH V V V OL(max)/V (min)/IH V V (max)/IL V V 逻辑门A 2.4 0.4 2 0.8 逻辑门B 3.5 0.2 2.5 0.6 逻辑门C4.20.23.20.8解:根据表题3.1.1所示逻辑门的参数,以及式(3.1.1)和式(3.1.2),计算出逻辑门A 的高电平和低电平噪声容限分别为: NHA V =(min)OH V —(min)IH V =2.4V —2V=0.4V (max)NLA V =(max)IL V —(max)OL V =0.8V —0.4V=0.4V同理分别求出逻辑门B 和C 的噪声容限分别为: NHB V =1V NLB V =0.4V NHC V =1V NLC V =0.6V电路的噪声容限愈大,其抗干扰能力愈强,综合考虑选择逻辑门C3.1.3根据表题3.1.3所列的三种门电路的技术参数,计算出它们的延时-功耗积,并确定哪一种逻辑门性能最好表题3.1.3 逻辑门电路的技术参数表/pLH t ns /pHL t ns /D P mW 逻辑门A11.216逻辑门B 5 6 8 逻辑门C10101解:延时-功耗积为传输延长时间与功耗的乘积,即DP = t pd P D根据上式可以计算出各逻辑门的延时-功耗分别为A DP =2PLH PHL t t +D P =(1 1.2)2ns +*16mw=17.6* 1210-J=17.6PJ 同理得出: B DP =44PJ C DP =10PJ,逻辑门的DP 值愈小,表明它的特性愈好,所以逻辑门C 的性能最好.3.1.5 为什么说74HC 系列CMOS 与非门在+5V 电源工作时,输入端在以下四种接法下都属于逻辑0: (1)输入端接地; (2)输入端接低于1.5V 的电源; (3)输入端接同类与非门的输出低电压0.1V; (4)输入端接10k Ω的电阻到地.解:对于74HC 系列CMOS 门电路来说,输出和输入低电平的标准电压值为: OL V =0.1V, IL V =1.5V ,因此有:(1) Vi =0< IL V =1.5V ,属于逻辑门0 (2) Vi <1.5V=IL V ,属于逻辑门0 (3) Vi <0.1<IL V =1.5V ,属于逻辑门0(4)由于CMOS 管的栅极电流非常小,通常小于1uA,在10k Ω电阻上产生的压降小于10mV 即Vi <0.01V<IL V =1.5V ,故亦属于逻辑0.3.1.7求图题3.1.7所示电路的输出逻辑表达式.解:图解 3.1.7所示电路中L1=AB ,L2=BC ,L3=D ,L4实现与功能,即L4=L1∙L2∙L3,而L=4L E ,所以输出逻辑表达式为L=AB BC D E3.1.9 图题3.1.9表示三态门作总线传输的示意图,图中n 个三态门的输出接到数据传输总线,D1,D2,……Dn 为数据输入端,CS1,CS2……CSn 为片选信号输入端.试问:(1) CS 信号如何进行控制,以便数据D 1,D 2, ……Dn 通过该总线进行正常传输; (2)CS 信号能否有两个或两个以上同时有效?如果出现两个或两个以上有效,可能发生什么情况? (3)如果所有CS 信号均无效,总线处在什么状态?解: (1)根据图解3.1.9可知,片选信号CS1,CS2……CSn为高电平有效,当CSi=1时第i个三态门被选中,其输入数据被送到数据传输总线上,根据数据传输的速度,分时地给CS1,CS2……CSn端以正脉冲信号,使其相应的三态门的输出数据能分时地到达总线上.(2)CS信号不能有两个或两个以上同时有效,否则两个不同的信号将在总线上发生冲突,即总线不能同时既为0又为1.(3)如果所有CS信号均无效,总线处于高阻状态.3.1.12 试分析3.1.12所示的CMOS电路,说明它们的逻辑功能(A)(B)(C)(D)解:对于图题3.1.12(a)所示的CMOS电路,当EN=0时,2P T和2N T均导通,1P T和1N T 构成的反相器正常工作,L=A,当EN=1时,2P T和2N T均截止,无论A为高电平还是低电平,输出端均为高阻状态,其真值表如表题解3.1.12所示,该电路是低电平使能三态非门,其表示符号如图题解3.1.12(a)所示。

图题3.1.12(b)所示CMOS电路,EN=0时,2P T导通,或非门打开,1P T和1N T构成反相器正常工作,L=A;当EN=1时,2P T截止,或非门输出低电平,使1N T截止,输出端处于高阻状态,该电路是低电平使能三态缓冲器,其表示符号如图题解3.1.12(b)所示。

同理可以分析图题3.1.12(c)和图题3.1.12(d)所示的CMOS电路,它们分别为高电平使能三态缓冲器和低电平使能三态非门,其表示符号分别如图题3.1.12(c)和图题3.1.12(d)所示。

A L0 0 10 1 01 0高阻1 13.1.12(a)A L0 0 00 1 11 0 高阻1 1 高阻3.1.12(b)EN A L0 0 高阻0 1 高阻1 0 01 1 13.1.12(cA L0 0 10 1 01 0 高阻1 1 高阻3.1.12(d)3.2.2 为什么说TTL与非门的输入端在以下四种接法下,都属于逻辑1:(1)输入端悬空;(2)输入端接高于2V的电源;(3)输入端接同类与非门的输出高电压3.6V;(4)输入端接10kΩ的电阻到地。