PS21963-A中文资料

- 格式:pdf

- 大小:153.12 KB

- 文档页数:10

ASTM A6/A6M-2004 a结构用轧制钢板、型钢、板桩和棒钢通用要求ASTM A36/A36M2004碳结构钢标准规范ASTM A106-2002a高温用无缝碳钢公称管规范ASTM A143-2003热侵镀锌结构钢制品防脆化的标准实施规程和催化探测方法ASTM A179/A179M-1990a(R2001)热交换器和冷凝器用无缝冷拉低碳钢管标准规范ASTM A192-2002高压设备用无缝碳钢锅炉管标准规范ASTM A209/A209M-2003锅炉和过热器用无缝碳钼合金钢管标准规范ASTM A210/A210M-2003锅炉和过热器用无缝中碳钢管技术条件ASTM A213/A213Mb-2004锅炉过热器和换热器用无缝铁素体和奥氏体合金钢传热管技术条件ASTM A234/A234M-2004中、高温用锻制碳钢和合金钢管道配件ASTM A252-98(R2002)焊接钢和无缝钢管桩的标准规范ASTM A262-2002a探测奥氏体不锈钢晶间腐蚀敏感度的标准实施规范ASTM A269/A269-2004通用无缝和焊接奥氏体不锈钢管标准规范ASTM A333/A333M-2004低温设备用无缝和焊接钢管的规范标准ASTM A334/A334M-2004低温设备用无缝和焊接碳素和合金钢管的标准规范ASTM A335-2003高温设备用无缝铁素体合金钢管标准规范ASTM A370/A370M-2003a钢制品力学性能试验方法和定义标准ASTM A387/A387M-2003压力容器用铬钼合金钢板的标准规范ASTM A403/A403M-2004锻制奥氏体不锈钢管配件的标准规范ASTM A450/A450M-2004碳素钢管、铁素体合金钢管及奥氏体合金钢管一般要求的标准规范ASTM A500-2003a圆形与异型冷成型焊接与无缝碳素钢结构管标准规范ASTM A515-2003中温及高温压力容器用碳素钢板的标准规范ASTM A516-2004a中温及低温压力容器用碳素钢板的标准规范ASTM A530-2003特种碳素钢和合金钢管一般要求的标准规范ASTM A615/A615M-2004a混凝土配筋用异形钢筋和无节钢胚棒标准规范ASTM A703/A703M-2004标准技术条件—承压件钢铸件通用要求ASTM A781/A781M-2004a铸件、钢和合金的标准规范及通用工业的一般性要求ASTM A788/A788M-2004a标准技术条件—钢锻件通用要求ASTM B209/B209M -2004铝和铝合金薄板和中厚板标准规范ASTM E6-2003金属材料布氏硬度的标准测试方法ASTM E18-2003金属材料洛氏硬度和洛氏表面硬度的标准测试方法ASTM E29-2002使用有效数字确定试验数据与规范符合性作法ASTM E8-2004金属材料拉伸试验的标准测试方法ASTM E94-2004放射性检查的标准指南ASTM E125-1963(R2003)铁铸件的磁粉检验用标准参考照片ASTM E164-2003焊件的超声接触检验的标准操作规程ASTM E208-1995a(R2000)用导向落锤试验测定铁素体钢无塑性转变温度的标准试验方法ASTM E213-2004金属管超声检验方法ASTM F36-1995测定垫片材料压缩率及回弹率的标准试验方法ASTM F37-1995垫片材料密封性的标准试验方法ASTM F38-1995垫片材料的蠕变松弛的标准试验方法ASTM F112-1995色覆垫片密封性能的标准试验方法ASTM F146-1995a垫片材料耐液体标准试验方法ASTM F1311-1995(R2001)大口径组装式碳钢法兰标准规范ASTM G1-2003腐蚀试样的制备、清洁处理和评定用标准实施规范ASTM G36-73(R1981) 参考资料标准实用规程:在沸的氯化镁溶液中进行的应力腐蚀裂纹试验ASTM G46-1976(R1986) 参考资料标准实用规程:麻点腐蚀的检验和评定ASTM G48-1976(R1980) 参考资料使用三氯化铁溶液做不锈钢及其合金的耐麻点腐蚀和抗裂口腐蚀性试验的标准方法ASTM标准中译本丛书(一)碳钢、铸铁、不锈钢及合金钢材料标准规范(含18个标准)ASTM A105/A105M-2002管道部件用碳钢锻件ASTM A126-1995(R2001)阀门、法兰和管道附件用灰铁铸件ASTM A181/A181M-2001通用管路用碳钢锻件标准规范ASTM A193/A193M-2001高温用合金钢和不锈钢螺栓材料ASTM A194/A194M-2001 a高温用合金钢和不锈钢螺栓材料ASTM A216/A216M-2001 a高温用可熔焊碳钢铸件标准规范ASTM A217/A217M-2002高温承压件用马氏体不锈钢和合金钢铸件标准规范ASTM A276-2002 a不锈钢棒材和型材ASTM A278/A278M-2001高温不超过650°F(350℃)的承压部件用灰铸铁件ASTM A320/A320M-2002低温用合金钢栓接材料ASTM A350/A350M-2002要求冲击韧性试验的管件用碳钢及低合金钢锻件标准规范ASTM A351/A351M-2000承压件用奥氏体、奥氏体-铁素体(双相)钢铸件规范ASTM A352/A352M-1993(R1998)低温承压件用铁素体和马氏体钢铸件标准规范ASTM A395/A395M-1999高温用铁素体球墨铸铁承压铸件ASTM A439-1983(R1999)奥氏体球墨铸铁件ASTM A536-1984(R1999)球墨铸铁件ASTM A694/A694M-2000高温输送用管法兰、管件、阀门及零件用碳钢和合金钢锻件标准规范ASTM A965/A965M-2002高温高压部件用奥氏体钢锻件ASTM标准中译本丛书(二)法兰、管件、阀门及部件(含9个标准)ASTM A182/A182M-2002高温用锻制或轧制合金钢法兰、锻制管件、阀门和部件ASTM A961-2002管道用钢制法兰、锻制管件、阀门和零件的通用要求标准规范ASTM B462-2002高温耐腐蚀用锻制或轧制的UNS NO6030、UNS NO6022、UNS NO6200、UNS NO8020、UNS NO8024、UNS NO8026、UNS NO8367、UNS NO10276、UNS N10665、UNS N10675和UNS R20033合金管法兰、锻制管件、阀门和零件标准规范ASTM F885-1984公称管径为NPS 1/4~2的青铜截止阀外形尺寸标准规范ASTM F992-1986(R2001)阀门铭牌标准规范ASTM F993-1986(R2001)阀门锁紧装置标准规范ASTM F1030-1986(R1998)阀门操作装置的选择准则ASTM F1098-1987(R1998)公称管径有NPS2~24的蝶阀外形尺寸标准规范。

External—Free ReleaseOxford Semiconductor, Inc.1900 McCarthy Boulevard, Suite 210 © Oxford Semiconductor, Inc. 2007F EATURES• Four 16C950 High performance UART channels • 8-bit Pass-through Local Bus (PCI Bridge )• IEEE1284 Compliant SPP/EPP/ECP parallel port (with external transceiver)• Efficient 32-bit, 33 MHz, multi-function target-only PCIcontroller, fully compliant to PCI Local Bus Specification 3.0 and PCI Power Management Specification 1.1 • Software compatible with OXmPCI954• UARTs fully software compatible with 16C550-type devices • UART operation up to 60 MHz via external clock source. Up to 20 MHz with the crystal oscillator• Baud rates up to 60 Mbps in external 1x clock mode and 15 Mbps in asynchronous mode• 128-byte deep FIFO per transmitter and receiver • Flexible clock prescaler, from 1 to 31.875• Automated in-band flow control using programmable Xon/Xoff in both directions•Automated out-of-band flow control using CTS#/RTS# and/or DSR#/DTR#• Programmable RS485 turnaround delay• Arbitrary trigger levels for receiver and transmitter FIFO interrupts and automatic in-band and out-of-band flow control• Infra-red (IrDA) receiver and transmitter operation • 9-bit data framing, as well as 5, 6, 7, and 8 bits • Detection of bad data in the receiver FIFO• Global Interrupt Status and readable FIFO levels to facilitate implementation of efficient device drivers.• Local registers to provide status/control of device functions • 11 multi-purpose I/O pins, which can be configured as input interrupt pins or ‘wake-up’• Auto-detection of a wide range of optional MICROWIRE TM compatible EEPROMs, to re-configure device parameters • Function access , to pre-configure each function prior to handover to generic device drivers • Operation via I/O or memory mapping• 3.3 V or 5 V operation (PCI Universal Voltage)• Extended operating temperature range: -40° C to 85° C •176-pin LQFP packageD ESCRIPTIONThe OXuPCI954 is a single chip solution for PCI-based serial and parallel expansion add-in cards. It is a dual function PCI device, where function 0 offers four ultra-high performance OX16C950 UARTs, and function 1 is configurable either as an 8-bit local bus or a bi-directional parallel port.Each UART channel in the OXuPCI954 is the fastest available PC-compatible UART, offering data rates up to 15 Mbps and 128-byte deep transmitter and receiver FIFOs. The deep FIFOs reduce CPU overhead and allow utilization of higher data rates. Each UART channel is software compatible with the widely used industry-standard 16C550 devices (and compatibles), as well as the OX16C95x family of high performance UARTs. In addition to increased performance and FIFO size, the UARTs also provide the full set of OX16C95x enhanced features including automated in-band flow control, readable FIFO levels, etc.To enhance device driver efficiency and reduce interrupt latency, internal UARTs have multi-port features such as shadowed FIFO fill levels, a global interrupt source register and Good-Data Status, readable in four adjacent DWORD registers visible to logical functions in I/O space and memory space.Expansion of serial ports beyond four channels is possible using the 8-bit pass-through Local Bus function. This provides a general address/data bus and interrupt capability to a discrete UART part, such as the Oxford SemiconductorOX16C954. Other controllers could be used to provide capabilities beyond additional UART ports. The addressable space provided by the Local Bus can be increased up to 256 bytes, and divided into four chip-select regions. This flexible expansion scheme caters for cards with up to 20 serial ports using external 16C950, 16C954 or compatible devices, or composite applications such as combined serial and parallel port expansion cards. Serial port cards with up to 20 ports (or with 4 serial ports and a parallel port) can be designed without redefining any device or timing parameters.The parallel port is an IEEE 1284 compliant SPP/EPP/ECP parallel port that fully supports the existing Centronics interface. The parallel port can be enabled in place of the local bus. A n external bus transceiver is required for 5V parallel port operation if device is 3.3V sourced.For full flexibility, all the default configuration register values can be overwritten using an optional M ICROWIRE compatibleserial EEPROM. This EEPROM can also be used to provide function access to pre-configure devices on the local bus/parallel port, prior to any PCI configuration accesses and before control is handed to (generic) device drivers.The OXuPCI954 can be used to replace the OXmPCI954 in a PCI application where quad UARTs and a local bus/parallel port functionality are required.OXuPCI954 DATA SHEETIntegrated High Performance Quad UARTs,8-bit Local Bus/Parallel Port,3.3 V and 5 V (Universal Voltage) PCI Interface .Improvements of the OXuPCI954 over Discrete SolutionsHigher degree of integrationThe OXuPCI954 device offers four internal 16C950 high-performance UARTs and an 8-bit local bus or abi-directional parallel port.Multi-function deviceThe OXuPCI954 is a multi-function device to enable users to load individual device drivers for the internal serial ports, drivers for the peripheral devices connected to the local bus or drivers for the internal parallel port.Quad Internal OX16C950 UARTsThe OXuPCI954 device contains four ultra-high performance UARTs, which can increase driver efficiency by using features such as the 128-byte deep transmitter and receiver FIFOs, flexible clock options, automatic flow control, programmable interrupt and flow control trigger levels and readable FIFO levels. Data rates are up to 60 Mbps.Improved access timingAccess to the internal UARTs require zero or one PCI wait state. A PCI read transaction from an internal UART can complete within five PCI clock cycles and a write transaction to an internal UART can complete within four PCI clock cycles. Reduces interrupt latencyThe OXuPCI954 device offers shadowed FIFO levels and Interrupt status registers on the internal UARTs and the MIO pins. This reduces the device driver interrupt latency. Power managementThe OXuPCI954 device complies with the PCI Power Management Specification 1.1 and the Microsoft Communications Device-class Power Management Specification 2.0 (2000). Both functions offer the extended capabilities for Power Management. This achieves significant power savings by enabling device drivers to power down the PCI functions. For function 0, this is through switching off the channel clock, in power state D3. Wake-up (PME# generation) can be requested by either functions. For function 0, this is via the RI# inputs of the UARTs in the power-state D3 or any modem line and SIN inputs of the UARTs in power-state D2. For function 1, this is via the MIO[2] input.Optional EEPROMThe OXuPCI954 device can be reconfigured from an external EEPROM to the end-user’s requirements. However, this is not required in many applications as the default values are sufficient for typical applications. An overrun detection mechanism built into the EEPROM controller prevents the PCI system from ‘hanging’ due to an incorrectly programmed EEPROM.R EVISION H ISTORYRevision Modification May 2007 First publication.Sep 2007 Feature revision, including removal of D3coldT ABLE OF C ONTENTS1OXuPCI954 Device Modes (6)2Block Diagram (7)3Pin Information—176-Pin LQFP (8)3.1Mode ‘0’ Quad UARTs + 8-bit Local Bus (8)3.1.1Mode ‘1’ : Quad UARTs + Parallel Port (9)3.2Pin Descriptions (10)4Configuration and Operation (16)5PCI Target Controller (17)5.1Operation (17)5.2Configuration Space (17)5.2.1PCI Configuration Space Register Map (18)5.3Accessing Logical Functions (20)5.3.1PCI Access to Internal UARTs (21)5.3.2PCI Access to 8-bit Local Bus (22)5.3.3PCI Access to Parallel Port (22)5.4Accessing Local Configuration Registers (23)5.4.1Local Configuration and Control Register ‘LCC’ (Offset 0x00) (23)5.4.2Multi-purpose I/O Configuration Register ‘MIC’ (Offset 0x04) (24)5.4.3Local Bus Timing Parameter Register 1 ‘LT1’ (Offset 0x08) (26)5.4.4Local Bus Timing Parameter Register 2 ‘LT2’ (Offset 0x0C) (27)5.4.5UART Receiver FIFO Levels ‘URL’ (Offset 0x10) (28)5.4.6UART Transmitter FIFO Levels ‘UTL’ (Offset 0x14) (29)5.4.7UART Interrupt Source Register ‘UIS’ (Offset 0x18) (29)5.4.8Global Interrupt Status and Control Register ‘GIS’ (Offset 0x1C) (30)5.5PCI Interrupts (31)5.6Power Management (32)5.6.1Power Management of Function 0 (32)5.6.2Power Management of Function 1 (33)5.6.3Universal Voltage (34)5.7Unique Bar Option – for Function 0 (35)6Internal OX16C950 UARTs (36)6.1Operation – Mode Selection (36)6.1.1450 Mode (36)6.1.2550 Mode (36)6.1.3Extended 550 Mode (36)6.1.4750 Mode (36)6.1.5650 Mode (36)6.1.6950 Mode (37)6.2Register Description Tables (38)6.3UART Reset Configuration (41)6.3.1Hardware Reset (41)6.3.2Software Reset (41)6.4Transmitter and Receiver FIFOs (42)6.4.1FIFO Control Register ‘FCR’ (42)6.5Line Control and Status (43)6.5.1False Start Bit Detection (43)6.5.2Line Control Register ‘LCR’ (43)6.5.3Line Status Register ‘LSR’ (44)6.6Interrupts and Sleep Mode (45)6.6.1Interrupt Enable Register ‘IER’ (45)6.6.2Interrupt Status Register ‘ISR’ (46)6.6.3Interrupt Description (46)6.6.4Sleep Mode (47)6.7Modem Interface (47)6.7.1Modem Control Register ‘MCR’ (47)6.7.2Modem Status Register ‘MSR’ (48)6.8Other Standard Registers (48)6.8.1Divisor Latch Registers ‘DLL and DLM’ (48)6.8.2Scratch Pad Register ‘SPR’ (48)6.9Automatic Flow Control (49)6.9.1Enhanced Features Register ‘EFR’ (49)6.9.2Special Character Detection (50)6.9.3Automatic In-band Flow Control (50)6.9.4Automatic Out-of-band Flow Control (50)6.10Baud Rate Generation (51)6.10.1General Operation (51)6.10.2Clock Prescaler Register ‘CPR’ (51)6.10.3Times Clock Register ‘TCR’ (51)6.10.4External 1x Clock Mode (53)6.10.5Crystal Oscillator Circuit (53)6.11Additional Features (54)6.11.1Additional Status Register ‘ASR’ (54)6.11.2FIFO Fill Levels ‘TFL and RFL’ (54)6.11.3Additional Control Register ‘ACR’ (54)6.11.4Transmitter Trigger Level ‘TTL’ (55)6.11.5Receiver Interrupt. Trigger Level ‘RTL’ (55)6.11.6Flow Control Levels ‘FCL’ and ‘FCH’ (56)6.11.7Device Identification Registers (56)6.11.8Clock Select Register ‘CKS’ (56)6.11.9Nine-bit Mode Register ‘NMR’ (57)6.11.10Modem Disable Mask ‘MDM’ (57)6.11.11Readable FCR ‘RFC’ (58)6.11.12Good-data Status Register ‘GDS’ (58)6.11.13Port Index Register ‘PIX’ (58)6.11.14Clock Alteration Register ‘CKA’ (58)6.11.15RS485 Delay Enable ‘RS485_DLYEN’ (58)6.11.16RS485 Delay Count ‘RS485_DLYCNT’ (59)7Local bus (60)7.1Overview (60)7.2Operation (60)7.3Configuration and Programming (61)8Bidirectional Parallel Port (62)8.1Operation and Mode Selection (62)8.1.1SPP Mode (62)8.1.2PS2 Mode (62)8.1.3EPP Mode (62)8.1.4ECP Mode (62)8.2Parallel Port Interrupt (63)8.3Register Description (63)8.3.1Parallel Port Data Register ‘PDR’ (64)8.3.2ECP FIFO Address / RLE (64)8.3.3Device Status Register ‘DSR’ (64)8.3.4Device Control Register ‘DCR’ (64)8.3.5EPP Address register ‘EPPA’ (65)8.3.6EPP Data Registers ‘EPPD1-4’ (65)8.3.7ECP Data FIFO (65)8.3.8Test FIFO (65)8.3.9Configuration A Register (65)8.3.10Configuration B Register (65)8.3.11Extended Control Register ‘ECR’ (65)9Serial EEPROM (66)9.1Specification (66)9.1.1Zone 0: Header (67)9.1.2Zone 1: Local Configuration Registers (68)9.1.3Zone 2: Identification Registers (69)9.1.4Zone 3: PCI Configuration Registers (69)9.1.5Zone 4: Power Management DATA (and DATA_SCALE Zone) (70)9.1.6Zone 5: Function Access (70)10Operating Conditions (72)10.1DC Electrical Characteristics (72)11AC Electrical Characteristics (76)11.1PCI Bus Timings (76)11.2Local Bus (77)11.3Serial Ports (79)12Timing Waveforms (80)13Package Information (95)13.1176-Pin LQFP (95)14Ordering Information (96)1OX U PCI954D EVICE M ODESThe OXuPCI954 supports two modes of operation. These modes are summarized in the following table.Device Mode Mode Pin Selection Functionality0 MODE = 0 Function 0 : Quad UARTs Function 1 : 8-bit local bus1 MODE = 1 Function 0 : Quad UARTs Function 1 : Parallel Port* The OXuPCI954 is not pin-compatible with the OX16PCI954 or the OXmPCI954, but is the same in all other aspects.2B LOCK D IAGRAMFIFOSELMODEAD[31:0]C/BE[3:0]#PCI_CLKFRAME#DEVSEL#IRDY#TRDY#STOP#PARPERR#IDSELRST#INTA#PME#XTLIXTLOUART_Clk_Out Local_Bus ClkEE_DIEE_CSEE_CKEE_DOSOUT[3:0]SIN[3:0]RTS[3:0]DTR[3:0]CTS[3:0]DSR[3:0]DCD[3:0]RI[3:0]MIO[10:0]PD[7:0]ACK#PEBUSYSLCTERR#SLIN#INIT#AFD#STB#LBA[7:0]LBD[7:0]LBCS[3:0]LBWR#LBRD#LBRSTDATA_DIR OXuPCI954 Block DiagramOSCDIS XTLSEL3P IN I NFORMATION—176-P IN LQFP 3.1Mode ‘0’ Quad UARTs + 8-bit Local Bus7 NC. Do not connect these pins:23, 40, 41, 136, 137, 138, 1393.1.1Mode ‘1’ : Quad UARTs + Parallel Port15 NC. Do not connect these pins:23, 40, 41, 74, 112, 113, 114, 115, 116, 117, 124, 136, 137, 138, 1393.2Pin DescriptionsFor the actual pinouts of the OXuPCI954 device (for the various modes), refer to the Section 3, Pin Information. The I/O direction key table is on page 15.PCI Interface – All ModesPin Dir1Name Description149, 150, 151, 154, 155,157, 158, 160, 164, 165,167, 168, 169, 170, 171,174, 13, 14, 15, 17, 18, 20,24, 25, 27, 28, 31, 32, 33,34, 35, 39P_I/O AD[31:0] Multiplexed PCI Address/Data bus161, 175, 12, 26 P_I C/BE[3:0]# PCI Command/Byte enable146 P_I CLK PCI system clock (33MHz)176 P_IFRAME#CycleFrame5 P_ODEVSEL#DeviceSelect1 P_IIRDY#Initiatorready2 P_OTRDY#Targetready6 P_O STOP# Target Stop request10 P_I/OPAR Parity8 P_OSERR#Systemerror7 P_I/OPERR#Parityerror163 P_I IDSEL Initialization device select144 P_I RST# PCI system reset142 P_ODINTA# PCIinterrupt147 P_OD PME# Power management eventSerial Port Pins – All ModesPin Dir1Name Description50 I FIFOSEL FIFO select. For backward compatibility with 16C550,16C650 and 16C750 devices the UARTs’ FIFO depth is 16when FIFOSEL is low. The FIFO size is increased to 128when FIFOSEL is high. The unlatched state of this pin isreadable by software. The FIFO size may also be set to 128by setting FCR[5] when LCR[7] is set, or by putting thedevice into Enhanced mode.82, 81, 63, 62 O(h)SOUT[3:0]IrDA_Out[3:0] These four pins are present in all modes but they can serve one of two functions, as follows:UART serial data outputs.UART IrDA data output when MCR[6] of the corresponding channel is set in Enhanced mode.91, 73, 72, 55I(h) I(h) SIN[3:0]IrDA_In[3:0]These four pins are present in all modes but they can serveone of two functions, as follows:UART serial data inputs.UART IrDA data input when IrDA mode is enabled (seeabove).Serial Port Pins – All ModesPin Dir1Name Description89, 76, 71, 57 I(h) DCD[3:0]# Active-low modem data-carrier-detect input 84, 79, 65, 60O(h) O(h) O(h) DTR[3:0]#485_En[3:0]Tx_Clk_Out[3:0]These four pins are present in all modes but they can serveone of three functions, as follows:Active-low modem data-terminal-ready output. If automatedDTR# flow control is enabled, the DTR# pin is asserted anddeasserted if the receiver FIFO reaches or falls below theprogrammed thresholds, respectively.In RS485 half-duplex mode, the DTR# pin may beprogrammed to reflect the state of the transmitter empty bitto automatically control the direction of the RS485transceiver buffer (see register ACR[4:3]).Transmitter 1x clock (baud rate generator output). Forisochronous applications, the 1x (or Nx) transmitter clockmay be asserted on the DTR# pins (see register CKS[5:4]).83, 80, 64, 61 O(h) RTS[3:0]# Active-low modem request-to-send output. If automatedRTS# flow control is enabled, the RTS# pin is deassertedand reasserted whenever the receiver FIFO reaches or fallsbelow the programmed thresholds, respectively.85, 78, 67, 59 I(h) CTS[3:0]# Active-low modem clear-to-send input. If automated CTS#flow control is enabled, upon deassertion of the CTS# pin,the transmitter will complete the current character and enterthe idle mode until the CTS# pin is reasserted. Note: any in-band flow control characters are transmitted regardless ofthe state of the CTS# pin.86, 77, 66, 58I(h) I(h) DSR[3:0]#Rx_Clk_In[3:0]These four pins are present in all modes but they can serveone of two functions, as follows:Active-low modem data-set-ready input. If automated DSR#flow control is enabled, upon deassertion of the DSR# pin,the transmitter will complete the current character and enterthe idle mode until the DSR# pin is reasserted. Note: any in-band flow control characters are transmitted regardless ofthe state of the DSR# pin.External receiver clock for isochronous applications. TheRx_Clk_In is selected when CKS[1:0] = ‘01’.90, 75, 70, 56 I(h)I(h) RI[3:0]#Tx_Clk_In[3:0]Active-low modem Ring-Indicator inputExternal transmitter clock. This clock can be used by thetransmitter (and indirectly by the receiver) when CKS[6]=’1’.Clock Interface Pins – All ModesPin Dir 1 Name Description49 I/OXTLOCrystal oscillator output when OSCDIS = ‘0’.External clock source input when OSCDIS = ‘1’48 I XTLI Crystal oscillator input when OSCDIS = ‘0’, up to 20MHz.N/C when OSCDIS = ‘1’45 I OSCDIS Oscillator disable.When 0, the internal crystal oscillator is enabled and a crystal needs to be attached to XTLI/XTLO.XTLSEL must be set according to the crystal frequency that is used (up to 20Mhz).When 1, the internal crystal oscillator is disabled and an external oscillator source (up to 60MHz) can be input to XTLO. XTLI is N/C and XTLSEL must be 0130 I XTLSEL Defines the frequency of the crystal attached to XTLI/XTLO(when OSCDIS = ‘0’)0 = 1 MHz – 12 MHz 1 = 12 MHz – 20 MHz8-bit Local Bus – Mode 0Pin Dir 1 Name Description 111O UART_CLK_Out Buffered crystal output. This clock can drive external UARTsconnected to the local bus. Can be enabled / disabled by software.123 O(h) LBRST Local bus active-high reset. 124 O LBRST# Local bus active-low reset. 104 O LBDOUT Local bus data out enable. This pin can be used by externaltransceivers; it is high when LBD[7:0] are in output mode and low when they are in input mode.74 O LBCLK Buffered PCI clock. Can be enabled / disabled by software. 114, 115, 116, 117 O(h) O(h) LBCS[3:0]# LBDS[3:0]# Local bus active-low Chip-Select (Intel mode).Local bus active-low Data-Strobe (Motorola mode).112 O O LBWR# LBRDWR# Local bus active-low write-strobe (Intel mode).Local bus Read-not-Write control (Motorola mode).113 O Z LBRD# Hi-Z Local bus active-low read-strobe (Intel mode).Permanent high impedance (Motorola mode).105, 106, 108, 109 118, 119, 120, 122 O(h) LBA[7:0] Local bus address signals. 96, 97, 98, 99 100, 101, 102, 103I/O(h) LBD[7:0] Local bus data signals.Parallel Port – Mode 1Pin Dir 1 NameDescription123 I(h) I(h) ACK#INTR#Acknowledge (SPP mode). ACK# is asserted (low) by the peripheral to indicate that a successful data transfer has taken place.Identical function to ACK# (EPP mode).122 I(h) PEPaper Empty. Activated by printer when it runs out of paper. 120 I(h) I(h) BUSYWAIT#Busy (SPP mode). BUSY is asserted (high) by the peripheral when it is not ready to accept data.Wait (EPP mode). Handshake signal for interlocked IEEE 1284 compliant EPP cycles.109 OD(h) O(h) SLIN#ADDRSTB#Select (SPP mode). Asserted by host to select the peripheral.Address strobe (EPP mode) provides address read and write strobe.119 I(h) SLCT Peripheral selected. Asserted by peripheral when selected. 118 I(h) ERR#Error. Held low by the peripheral during an error condition. 108 OD(h) O(h) INIT#INIT#Initialize (SPP mode). Commands the peripheral to initialize.Initialize (EPP mode). Identical function to SPP mode. 106 OD(h) O(h) AFD#DATASTB# Auto Feed (SPP mode, open-drain).Data strobe (EPP mode) provides data read and write strobe.105 OD(h) O(h) STB#WRITE#Strobe (SPP mode). Used by peripheral to latch data currently available on PD[7:0].Write (EPP mode). Indicates a write cycle when low and a read cycle when high . 96, 97, 98, 99, 100, 101, 102, 103I/O(h) PD[7:0] Parallel data bus.104OPDOUTParallel port data out enable. This pin should be used by external transceivers for 5 V signaling; it is high when PD[7:0] are in output mode and low when they are in input mode.Multi-purpose and External Interrupt Pins – All ModesPin Dir1Name DescriptionMODE0 1135 --135I/O(h)OMIO0NCMulti-purpose I/O 0. Can drive high or low, or assert a PCIinterrupt.Output Driving ‘0’. Can be left as a No-connect.134 134 134134I/O(h)MIO1NCMulti-purpose I/O 1. Can drive high or low, or assert a PCIinterrupt (as long as LCC[6:5] = “00”).Output Driving ‘0’ (when LCC[6:5] ≠ ‘00’)Can be left as a No-Connect.133 133 133133I/O(h)IMIO2PME_InMulti-purpose I/O 2. When LCC[7] = 0, this pin can drive highor low, or assert a PCI interrupt.Input power management event. When LCC[7] is set thisinput pin can assert a function 1 PME#.93, 94, 95, 125, 126, 127, 128, 132 I/O(h) MIO[10:3] Multi-purpose I/O pins. Can drive high or low, or assert a PCIinterrupt.EEPROM Pins – All ModesPin Dir1Name Description53 OEE_CKEEPROMclock.52 O EE_CS EEPROM active-high Chip Select.54 IU(h) EE_DI EEPROM data in, with internal pull-up.When the serial EEPROM is connected, this pin should bepulled up using a 1-10k resistor. When the EEPROM is notused the internal pull-up is sufficient.Pin to be connected to the external EEPROM’s EE_DO pin(if used).51 O EE_DO EEPROM data out.Pin to be connected to the external EEPROM’s EE_DI pin(if used).Table 1: Pin DescriptionsI/O Direction Key P_I PCI input 3.3 V Only P_O PCI output / PCITristates 3.3 V Only P_I/O PCI bi-directional 3.3 V Only P_OD PCI open drain 3.3 V OnlyI Input LVTTL level I(h) Input LVTTL level, 5 V tolerant IU(h) Input with internal pull-up LVTTL level, 5 V tolerant I/O(h) Bi-Directional LVTTL level, 5 V tolerantO Output Standard Output O(h) Output 5 V tolerant (High Voltage BI-Direct in output mode) OD Open drain Standard Open-drain Output OD(h) Open drain 5 V tolerant (High Voltage BI-Direct in open-drain mode) NC No connectG Ground V VoltageMiscellaneous PinsPin Dir 1 NameDescription44 IMODEMode selector Pin0 : Function 0 : Quad UART. Function 1 : 8-bit local bus.1 : Function 0 : Quad UART. Function 1 : Parallel port.Power and GroundPinType Name Description19, 42, 47, 69, 88, 107, 131, 148VVDDPower Supply (3.3 V)11, 22, 36, 140, 156, 162, 173 V VIOPCI I/O Universal VoltageDefines the (clamping) voltage of the PCI I/O Buffers.To be connected to the VIO pin of the PCI connector. 3, 4, 9, 16, 21, 29, 30, 37, 38, 43, 46, 68, 87, 92, 110, 121, 129, 141, 143, 145, 152, 153, 159, 166, 172G GNDPower Supply Ground (0 V)4C ONFIGURATION AND O PERATIONThe OXuPCI954 is a multi-function, target-only PCI device, compliant with the PCI Local Bus Specification, Revision 3.0 and the PCI Power Management Specification, Revision 1.1.The OXuPCI954 affords maximum configuration flexibility by treating the internal UARTs, the local bus and the parallel port as separate logical functions. Each function has its own configuration space and is therefore recognized and configured by the PCI BIOS separately. The functions used are configured by the Mode Selection Pin as shown in Section 1 OXuPCI954 Device Modes.The OXuPCI954 is configured by system start-up software during the bootstrap process that follows bus reset. The system scans the bus and reads the vendor and device identification codes from any devices it finds. It then loads device-driver software according to this information and configures the I/O, memory and interrupt resources. Device drivers can then access the functions at the assigned addresses in the usual fashion, with the improved data throughput provided by PCI.Each function operates as though it was a separate device. However there are a set of Local Configuration Registers that can be used to enable signals and interrupts, configure timings, and improve the efficiency of multi-port drivers. This architecture enables separate drivers to be installed for each function. Generic port drivers can be hooked to use the functions individually, or more efficient multi-port drivers can hook both functions, accessing the Local Configuration Registers from either.All registers default after reset to suitable values for typical applications such a 4/8 port serial, or combo 4-port serial/1-port parallel add-in cards. However, all identification, control and timing registers can be redefined using an optional serial EEPROM.5PCI T ARGET C ONTROLLER5.1OperationThe OXuPCI954 responds to the following PCI transactions:-•Configuration access: The OXuPCI954 responds to type 0 configuration reads and writes if the IDSELsignal is asserted and the bus address is selecting theconfiguration registers for function 0 or 1. The devicewill respond to the configuration transaction by asserting DEVSEL#. Data transfer then follows. Anyother configuration transaction will be ignored by theOXuPCI954.•I/O reads/writes: The address is compared with the addresses reserved in the I/O Base Address Registers(BARs). If the address falls within one of the assignedranges, the device will respond to the I/O transactionby asserting DEVSEL#. Data transfer follows thisaddress phase. For the UARTs and 8-bit local buscontroller, only byte accesses are possible. For I/Oaccesses to these regions, the controller comparesAD[1:0] with the byte-enable signals as defined in thePCI specification. The access is always completed;however if the correct BE signal is not present thetransaction will have no effect.•Memory reads/writes: These are treated in the same way as I/O transactions, except that the memoryranges are used. Memory access to single-byte regions is always expanded to DWORDs in theOXuPCI954. In other words, OXuPCI954 reserves aDWORD per byte in single-byte regions. The deviceallows the user to define the active byte lane usingLCC[4:3] so that in Big-Endian systems the hardwarecan swap the byte lane automatically. For Memorymapped access in single-byte regions, the OXuPCI954 compares the asserted byte-enable withthe selected byte-lane in LCC[4:3] and completes theoperation if a match occurs, otherwise the access willcomplete normally on the PCI bus, but it will have noeffect on either the internal UARTs or the local buscontroller.•All other cycles (64-bit, special cycles, reserved encoding etc.) are ignored.The OXuPCI954 will complete all transactions as disconnect-with-data, i.e. the device will assert the STOP# signal alongside TRDY#, to ensure that the Bus Master does not continue with a burst access. The exception to this is Retry, which will be signaled in response to any access while the OXuPCI954 is reading from the serial EEPROM.The OXuPCI954 performs medium-speed address decoding as defined by the PCI specification. It asserts the DEVSEL# bus signal two clocks after FRAME# is first sampled low on all bus transaction frames which address the chip. The internal UARTs are accessed with zero wait states inserted. Fast back-to-back transactions are supported by the OXuPCI954 as a target, so a bus master can perform faster sequences of write transactions to the UARTs or local bus when an inter-frame turn-around cycle is not required.The device supports any combination of byte-enables to the PCI Configuration Registers and the Local Configuration Registers. If a byte-enable is not asserted, that byte is unaffected by a write operation and undefined data is returned upon a read.The OXuPCI954 performs parity generation and checking on all PCI bus transactions as defined by the standard. Note this is entirely unrelated to serial data parity which is handled within the UART functional modules themselves. If a parity error occurs during the PCI bus address phase, the device will report the error in the standard way by asserting the SERR# bus signal. However if that address/command combination is decoded as a valid access, it will still complete the transaction as though the parity check was correct.The OXuPCI954 does not support any kind of caching or data buffering in addition to that already provided within the UARTs by the transmit and receive data FIFOs. In general, registers in the UARTs and on the local bus can not be pre-fetched because there may be side-effects on read.5.2Configuration SpaceThe OXuPCI954 is a dual-function device, where each logical function has its own configuration space. All required fields in the standard header are implemented, plus the Power Management Extended Capability register set. The format of the configuration space is shown in the following tables.In general, writes to any registers that are not implemented are ignored, and all reads from unimplemented registers return 0.。

Powerex, Inc., 200 E. Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272Intellimod™ ModuleDual-In-Line Intelligent Power Module50 Amperes/600 VoltsPS2186999Description:DIP-IPMs are intelligent power modules that integrate power devices, drivers, and protection circuitry in an ultra compactdual-in-line transfer-mold package for use in driving small three phase motors. Use of 5thgeneration IGBTs, DIP packaging, and application specific HVICs allow the designer to reduce inverter size and overall design time.Features:£ Compact Packages £ Single Power Supply £ Integrated HVICs£ Direct Connection to CPU Applications:£ Washing Machines £ Refrigerators £ Air Conditioners £ Small Servo Motors £ Small Motor ControlOrdering Information:PS21869 is a 600V , 50 Ampere DIP Intelligent Power Module.Dimensions Inches Millimeters A 3.11±0.02 79.0±0.5 B 1.22±0.02 31.0±0.5 C 0.28±0.02 7.0±0.5 D 2.64±0.01 67.0±0.3 E 0.53±0.02 13.4±0.5 F 0.84±0.02 21.4±0.5 G 1.37±0.02 34.9±0.5 H 0.15±0.01 3.8±0.2 J 0.11±0.01 2.8±0.3 K 0.39±0.01 10.0±0.3 L 0.79±0.01 20.0±0.3 M 0.50±0.04 12.8±1.0 N 2.98 75.6Dimensions Inches MillimetersP 0.04 1.0 Q 0.18±0.01 Dia. 4.5±0.2 Dia. R 0.15 3.8 S Min. 1.0 Min. T 0.02 Min. 0.7 Min. U 0.1 2.5 V 0.03±0.01 0.8±0.2 W 0.02 0.7 X 0.45±0.02 11.5±0.5 Y 0.18 4.5 Z 0.12 3.1 AA 0.02 0.6Powerex, Inc., 200 E. Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272PS21869Intellimod™ ModuleDual-In-Line Intelligent Power Module50 Amperes/600 VoltsAbsolute Maximum Ratings, T j = 25°C unless otherwise specifiedCharacteristics Symbol PS21869 Units Power Device Junction Temperature* T j-20 to 125 °C Module Case Operation T emperature (See T f Measurement Point Illustration) T f-20 to 100 °C Storage Temperature T stg-40 to 125 °C Mounting Torque, M4 Mounting Screws — 13 in-lb Module Weight (Typical) — 65 Grams Self-protection Supply Voltage Limit (Short Circuit Protection Capability)** V CC(prot.)400 Volts Isolation Voltage, AC 1 minute, 60Hz Sinusoidal, Connection Pins to Heatsink Plate V ISO2500 Volts *The maximum junction temperature rating of the power chips integrated within the DIP-IPM is 150°C (@T f≤ 100°C). However, to ensure safe operation of the DIP-IPM,the average junction temperature should be limited to T j(avg)≤ 125°C (@T f≤ 100°C).**V D = 13.5 ~ 16.5V, Inverter Part, T j = 125°C, Non-repetitive, Less than 2µsIGBT Inverter SectorCollector-Emitter Voltage (T f = 25°C) V CES600 Volts Collector Current (T f = 25°C) ±I C50 Amperes Peak Collector Current (T f = 25°C, <1ms) ±I CP100 Amperes Supply Voltage (Applied between P - N) V CC450 Volts Supply Voltage, Surge (Applied between P - N) V CC(surge)500 Volts Collector Dissipation (T f = 25°C, per 1 Chip) P C70.4 WattsControl SectorP1PC N1NC DSupply Voltage (Applied between V UFB-V UFS,V VFB-V VFS, V WFB-V WFS) V DB20 Volts Input Voltage (Applied between U P, V P, W P-V PC, U N, V N, W N-V NC) V IN-0.5 ~ V D+0.5 Volts Fault Output Supply Voltage (Applied between F O-V NC) V FO-0.5 ~ V D+0.5 Volts Fault Output Current (Sink Current at F O Terminal) I FO 1 mA Current Sensing Input Voltage (Applied between C IN-V NC) V SC-0.5 ~ V D+0.5 Volts100Powerex, Inc., 200 E. Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272PS21869Intellimod™ ModuleDual-In-Line Intelligent Power Module50 Amperes/600 VoltsElectrical and Mechanical Characteristics, T j = 25°C unless otherwise specifiedCharacteristics Symbol Test Conditions Min. Typ. Max.UnitsIGBT Inverter SectorCollector-Emitter Cutoff Current I CES V CE = V CES, T j = 25°C —— 1.0 mAV CE = V CES, T j = 125°C ——10 mADiode Forward Voltage V EC T j = 25°C, -I C = 50A, V IN = 5V — 1.70 2.20 Volts Collector-Emitter Saturation Voltage V CE(sat) I C = 50A, T j = 25°C, V D = V DB = 15V, V IN = 0V — 1.50 2.00 VoltsI C = 50A, T j = 125°C, V D = V DB = 15V, V IN = 0V — 1.60 2.10 Volts Inductive Load Switching Times t on0.70 1.30 1.90 µsrr CC D DBC(on)C j INoffC(off)T fMeasurement Point101Powerex, Inc., 200 E. Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272PS21869Intellimod™ ModuleDual-In-Line Intelligent Power Module50 Amperes/600 VoltsElectrical and Mechanical Characteristics, T j = 25°C unless otherwise specifiedCharacteristics Symbol Test Conditions Min. Typ. Max.UnitsControl SectorSupply Voltage V D Applied between V P1-V PC, V N1-V NC13.5 15.0 16.5 Volts V DB Applied between V UFB-V UFS, 13.0 15.0 18.5 VoltsV VFB-V VFS, V WFB-V WFSCircuit Current I D V D = V DB = 15V, V IN = 5V,—— 5.00 mATotal of V P1-V PC, V N1-V NCV D = V DB = 15V, V IN = 0V, —— 7.00 mATotal of V P1-V PC, V N1-V NCV D = V DB = 15V, V IN = 5V, —— 0.40 mAV UFB-V UFS, V VFB-V VFS, V WFB-V WFSV D = V DB = 15V, V IN = 0V, —— 0.55 mAV UFB-V UFS, V VFB-V VFS, V WFB-V WFSFault Output Voltage V FOH V SC = 0V, F O Circuit: 10k Ω to 5V Pull-up 4.9 —— Volts V FOL V SC = 1V, I FO = 1mA—— 0.95 Volts Input Current I IN V IN = 5V 1.00 1.50 2.00 mA Short-Circuit Trip Level* V SC(ref) T j = 25°C, V D = 15V0.43 0.48 0.53 Volts Supply Circuit Undervoltage UV DBt Trip Level, T j≤ 125°C10.0 — 12.0 Volts Protection UV DBr Reset Level, T j≤ 125°C10.5 — 12.5 VoltsUV Dt Trip Level, T j≤ 125°C10.3 — 12.5 VoltsUV Dr Reset Level, T j≤ 125°C10.8 — 13.0 Volts Fault Output Pulse Width** t FO C FO = 22nF 1.0 1.8—msth(on)P P P PC,Thermal CharacteristicsCharacteristic Symbol Condition Min. Typ. Max.Units Junction to Fin R th(j-f)Q IGBT Part (Per 1/6 Module)—— 1.42°C/Watt Thermal Resistance R th(j-f)D FWDi Part (Per 1/6 Module)—— 2.00°C/WattRecommended Conditions for UseCharacteristic Symbol Condition Min. Typ. Max.Units Supply Voltage V CC Applied between P-N T erminals 0300400 Volts Control Supply Voltage V D Applied between V P1-V PC, V N1-V NC13.5 15.0 16.5 Volts V DB Applied between V UFB-V UFS,13.0 15.0 18.5 VoltsV VFB-V VFS, V WFB-V WFSControl Supply VariationΔV D, ΔV DB-1 — 1 V/µs PWM Input Frequency f PWM T f ≤ 100°C, T j≤ 125°C——20 kHz * Short-Circuit protection is functioning only at the lower arms. Please select the value of the external shunt resistor such that the SC trip level is less than 85A.**Fault signal is asserted when the lower arm short circuit or control supply under-voltage protective functions operate. The fault output pulse-width t FO depends on the capacitance value of C FO according to the following approximate equation: C FO = (12.2 x 10-6) x t FO {F} .102103PS21869Intellimod™ ModuleDual-In-Line Intelligent Power Module 50 Amperes/600 VoltsPowerex, Inc., 200 E. Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272EMITTER CURRENT, I E , (AMPERES)R E V E R S E R E C O V E R Y T I M E , t r r , (n s )103100102101102101COLLECTOR CURRENT, I C , (AMPERES)100102101100102101COLLECTOR CURRENT, I C , (AMPERES)C O L L E C T O R -E M I T T E R S A T U R A T I O N V O L T A G E , V C E (s a t ), (V O L T S )COLLECTOR-EMITTERSATURATION VOLTAGE CHARACTERISTICS(TYPICAL)1.81.51.20.90.60.30FREE-WHEEL DIODEFORWARD CHARACTERISTICS(TYPICAL)REVERSE RECOVERY CHARACTERISTICS(TYPICAL)Recommended Conditions for UseCharacteristic Symbol Condition Min. Typ. Max. Units Allowable rms Current* I O V CC = 300V , V D = 15V , f C = 5kHz, — — 23.6 Arms PF = 0.8, Sinusoidal, T j ≤ 125°C, T f ≤ 100°CV CC = 300V , V D = 15V , f C = 15kHz, — — 13.8 Arms PF = 0.8, Sinusoidal, T j ≤ 125°C, T f ≤ 100°CMinimum Input P WIN(on)** 0.3 — — µs Pulse Width P WIN(off)***CC D Between Rated Current 13.0 ≤ V DB ≤ 18.5V , -20°C ≤ T f ≤ 100°C, 5.0 — — µs V NC Variation V NC Between V NC -N (Including Surge) -5.0 — 5.0 Volts Arm Shoot-through t DEAD For Each Input Signal, T f < 100°C 2.0 — — µs Blocking Time* The allowable rms current value depends on the actual application conditions.**If input signal ON pulse is less than P WIN(on), the device may not respond.***The IPM may fail to respond to an ON pulse if the preceeding OFF pulse is less than P WIN(off).Powerex, Inc., 200 E. Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272PS21869Intellimod™ ModuleDual-In-Line Intelligent Power Module50 Amperes/600 VoltsDIP-IPM Application Circuit (Shown Pins Up)plane.Component Selection:Dsgn.Typ. Value DescriptionD11A, 600V Boot strap supply diode – Ultra fast recoveryC110-100uF, 50V Boot strap supply reservoir – Electrolytic, long life, low Impedance, 105°C (Note 5)C20.22-2.0uF, 50V Local decoupling/High frequency noise filters – Multilayer ceramic (Note 8)C310-100uF, 50V Control power supply filter – Electrolytic, long life, low Impedance, 105°CC422nF, 50V Fault lock-out timing capacitor – Multilayer ceramic (Note 4)C5100pF, 50V Optional input signal noise filter – Multilayer ceramic (Note 1)C6200-2000uF, 450V Main DC bus filter capacitor – Electrolytic, long life, high ripple current, 105°CC70.1-0.22uF, 450V Surge voltage suppression capacitor – Polyester/Polypropylene film (Note 9)C SF1000pF, 50V Short circuit detection filter capacitor – Multilayer Ceramic (Note 6, Note 7)R SF 1.8k ohm Short circuit detection filter resistor (Note 6, Note 7)R SHUNT5-100 mohm Current sensing resistor - Non-inductive, temperature stable, tight tolerance (Note 10)R110 ohm Boot strap supply inrush limiting resistor (Note 5)R2330 ohm Optional control input noise filter (Note 1, Note 2)R310k ohm Fault output signal pull-up resistor (Note 3)Notes:1) To prevent input signal oscillations minimize wiring length to controller (~2cm). Additional RC filtering (C5 etc.) may berequired. If filtering is added be careful to maintain proper dead time. See application notes for details.2) Internal HVIC provides high voltage level shifting allowing direct connection of all six driving signals to the controller.3) F O output is an open collector type. Pull up resistor (R3) should be adjusted to current sink capability of the module.4) C4 sets the fault output duration and lock-out time. C4 ≈ 12.2E-6 x t FO, 22nF gives ~1.8ms5) Boot strap supply component values must be adjusted depending on the PWM frequency and technique.6) Wiring length associated with R SHUNT, R SF, C SF must be minimized to avoid improper operation of the SC function.7) R SF, C SF set short-circuit protection trip time. Recommend time constant is 1.5us-2.0us. See application notes.8) Local decoupling/high frequency filter capacitors must be connected as close as possible to the modules pins.9) The length of the DC link wiring between C6, C7, the DIP’s P terminal and the shunt must be minimized to preventexcessive transient voltages. In particular C7 should be mounted as close to the DIP as possible.10) Use high quality, tight tolorance current sensing resistor. Connect resistor as close as possible to the DIP’sN terminal. Be careful to check for proper power rating. See application notes for calculation of resistance value.104。

PS2全型号详细介绍索尼公司推出了著名的电视游戏机PLAYSTATION2,时至今日已经走过了5个年头。

在这5年之中索尼推出了许多不同型号的机器,同时在国内非常不规范的电子游戏市场中也流入了众多的水货,翻新,二手机器,使广大玩家一面渴望享受游戏带来的快乐,一面又不得不去承受没有质量保证,没有完善服务的痛苦。

为了帮助大家对PS2众多型号有个大概的了解,我发表如下此文。

好了,废话不说了。

列位上眼喽10000系列机型:10000型,这是PS2的日版首发机型,他奠定了PS2的经典造型,此后的四年时间里PS2一直沿用这个外型,但是在内部构件中在不断进行优化。

不久后又发行了15000型和18000型PS2。

在当时有一部分10000系列机器漂洋过海流入中国市场,但是因为成本很高,实在是一种奢侈的数码玩物,所以拥有的人很少,当时首发的价格是39800日圆,后来经过一次降价降为35000日圆。

我的一个高中同学买了一台,在北京鼓楼砸了5500元人民币拿下的。

这批机器当时应该都是从日本游戏店里直接运过来的,包装盒上都有从店中出货的条形码标志。

目前市场上几乎见不到10000系列机器了,因为他实在太古老了,而且这种型号的机器出仓盘使用太久会出现质量问题,并且10000系列没有特别合适的直读,所以目前某网上的个人再出售此系列的机器大家就不要考虑了,没有购买价值。

但是现在还在用10000系列的玩家实在是铁杆老玩家了,值得敬佩。

30000系列机型:这是PS2中期的主力机型。

随着直读芯片的不断完善,这时候在中国电子游戏市场有大批的PS2涌入。

先来介绍30000型,30000型是日版机器,也就是在日本发行的行货机器,在2001.11月左右降价后是29800日圆,一方面科技的发展使PS2制造工艺更加成熟,造配合当时的“完美直读”使更多玩家用大约2500-3000元人民币就享受到了这个当时带给人们强大冲击力的超级游戏机。

30000型的机器也是来自日本,货也是从日本的游戏机店直接进的国内,质量上非常可*,30000型机器是直到现在口碑最好的型号。

Powerex, Inc., 200 Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272Intellimod™ ModuleDual-In-Line Intelligent Power Module20 Amperes/600 VoltsPS21965, PS21965-A,PS21965-C1112/05Description:DIP-IPMs are intelligent power modules that integrate power devices, drivers, and protection circuitry in an ultra compactdual-in-line transfer-mold package for use in driving small three phase motors. Use of 5thgeneration IGBTs, DIP packaging, and application specific HVICs allow the designer to reduce inverter size and overall design time.Features:£ Compact Packages £ Single Power Supply £ Integrated HVICs£ Direct Connection to CPU £ Reduced R th Applications:£ Refrigerators £ Air Conditioners £ Small Servo Motors £ Small Motor ControlOrdering Information:PS21965 is a 600V , 20 Ampere short pin DIP Intelligent Power Module.PS21965-A – long pin type PS21965-C – zigzag pin typeDimensions Inches Millimeters A 1.50±0.02 38.0±0.5 B 0.94±0.02 24.0±0.5 C 0.14 3.5 D 1.40 35.56 E 0.57±0.02 14.4±0.5 F 0.74±0.02 18.9±0.5 G 1.15±0.02 29.2±0.5 H 0.14 3.5 J 0.13 3.3 K 0.016 0.4 L 0.06±0.02 1.5±0.05 M 0.031 0.8 N 1.39±0.019 35.0±0.3 O 0.07±0.0081.778±0.2P 0.02 0.5Q0.4712.0Dimensions Inches Millimeters R 0.011 0.28 S 0.12 3.08 T 0.024 0.6 U 0.1±0.008 2.54±0.2 V 1.33±0.02 33.7±0.5 W 0.03 0.678 X 0.04 1.0 Y 0.05 1.2 Z 1.40 35.56 AA 0.55±0.02 14.0±0.5 BB 0.37±0.02 9.5±0.5 CC 0.22±0.02 5.5±0.5 DD 0 ~ 5° 0 ~ 5° EE 0.06 MIN. 1.5 Min. FF 0.05 1.2GG0.063 Rad.1.6 Rad.PS21965, PS21965-A, PS21965-C Intellimod™ ModuleDual-In-Line Intelligent Power Module 20 Amperes/600 Volts2Powerex, Inc., 200 Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272212/05Absolute Maximum Ratings, T j = 25°C unless otherwise specifiedPS21965, PS21965-ACharacteristicsSymbol PS21965-CUnits Power Device Junction Temperature* T j -20 to 150 °C Storage TemperatureT stg -40 to 125 °C Case Operating Temperature (Note 1) T C -20 to 100°C Mounting Torque, M3 Mounting Screws — 6.9 in-lb Module Weight (Typical) — 10 Grams Heatsink Flatness (Note 2)— -50 to 100 µm Self-protection Supply Voltage Limit (Short Circuit Protection Capability)**V CC(prot.) 400 Volts Isolation Voltage, AC 1 minute, 60Hz Sinusoidal, Connection Pins to Heatsink PlateV ISO1500Volts*The ma ximum junction temperature rating of the power chips integrated within the DIP-IPM is 150°C (@T C ≤ 100°C). However, to ensure safe operation of the DIP-IPM, the average junction temperature should be limited to T j(avg) ≤125°C (@T C ≤ 100°C). **V D = 13.5 ~ 16.5V , Inverter Part, T j = 125°C, Non-repetitive, Less than 2µsIGBT Inverter SectorCollector-Emitter VoltageV CES 600 Volts Each Collector Current, ± (T C = 25°C)I C 20 Amperes Each Peak Collector Current, ± (T C = 25°C, Less than 1ms) I CP 40 Amperes Supply Voltage (Applied between P - N) V CC 450 Volts Supply Voltage, Surge (Applied between P - N) V CC(surge)500 Volts Collector Dissipation (T C = 25°C, per 1 Chip)P C35.7WattsControl SectorSupply Voltage (Applied between V P1-V NC , V N1-V NC ) V D 20 Volts Supply Voltage (Applied between V UFB -U, V VFB -V , V WFB -W) V DB 20 Volts Input Voltage (Applied between U P , V P , W P -V NC , U N , V N , W N -V NC ) V IN -0.5 ~ V D +0.5 Volts Fault Output Supply Voltage (Applied between F O -V NC ) V FO -0.5 ~ V D +0.5Volts Fault Output Current (Sink Current at F O Terminal) I FO 1 mA Current Sensing Input Voltage (Applied between C IN -V NC )V SC-0.5 ~ V D +0.5VoltsNote 1 – T C Measure PointPOWER TERMINALSHEATSINKNote 2 – Flatness Measurement Position3PS21965, PS21965-A, PS21965-C Intellimod™ ModuleDual-In-Line Intelligent Power Module 20 Amperes/600 VoltsPowerex, Inc., 200 Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272312/05Electrical and Mechanical Characteristics, T j = 25°C unless otherwise specifiedCharacteristicsSymbolTest ConditionsMin.Typ.Max.UnitsIGBT Inverter SectorCollector-Emitter Saturation Voltage V CE(sat)V D = V DB = 15V , I C = 20A, V IN = 5V , T j = 25°C — 1.70 2.20 VoltsV D = V DB = 15V , I C = 20A, V IN = 5V , T j = 125°C— 1.80 2.30 Volts Diode Forward Voltage V EC -I C = 20A, V IN = 0V— 1.90 2.40 Volts Inductive Load Switching Times t on0.70 1.30 1.90 µS rr CC D DB C(on)C j off INCollector Cutoff Current I CES V CE = V CES , T j = 25°C — — 1.0 mAV CE = V CES , T j = 125°C——10mAControl SectorCircuit Current I D V IN = 5VTotal of V P1-V NC , V N1-V NC — — 2.80 mA V D = V DB = 15V V UFB -U, V VFB -V , V WFB -W — — 0.55 mA V IN = 0VTotal of V P1-V NC , V N1-V NC — — 2.80 mAV UFB -U, V VFB -V , V WFB -W— — 0.55 mA Fault Output Voltage V FOH V SC = 0V , F O Terminal Pull-up to 5V by 10k Ω4.9 — — VoltsV FOL V SC = 1V , I FO = 1mA— — 0.95 Volts Input CurrentI IN V IN = 5V 0.70 1.00 1.50 mA Short Circuit Trip Level* V SC(ref) V D = 15V* 0.43 0.48 0.53 Volts Supply Circuit Under-voltage UV DBt Trip Level, T j ≤ 125°C 10.0 — 12.0 Volts UV DBr Reset Level, T j ≤ 125°C 10.5 — 12.5 Volts UV Dt T rip Level, T j ≤ 125°C 10.3 — 12.5 VoltsUV Dr Reset Level, T j ≤ 125°C10.8 — 13.0 Volts Fault Output Pulse Width** t FO20 — — µs th(on)th(off)P P P NC,th(hys)N N N NC * Short Circuit protection is functioning only for the low-arms. Please select the value of the external shunt resistor such that the S C trip level is less than 1.7 times the current rating.**Fault signal is asserted only for a U V or S C condition on the low side. On a S C fault the F O duration will be 20µsec. On a U V condition the fault signal will be asserted as long as the U V condition exists or for 20µsec, whichever is longer.PS21965, PS21965-A, PS21965-C Intellimod™ ModuleDual-In-Line Intelligent Power Module 20 Amperes/600 Volts4Powerex, Inc., 200 Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272412/05Thermal CharacteristicsCharacteristic Symbol ConditionMin. Typ. Max. Units Junction to Case R th(j-c)Q Inverter IGBT (Per 1/6 Module) — — 2.8 °C/WattR th(j-c)DInverter FWDi (Per 1/6 Module)——3.9°C/WattRecommended Conditions for UseCharacteristic Symbol ConditionMin. Typ. Max. Units Supply Voltage V CC Applied between P-N T erminals 0 300 400 Volts Control Supply Voltage V D Applied between V P1-V NC , V N1-V NC13.5 15.0 16.5 Volts V DB Applied between V UFB -U,13.0 15.0 18.5 VoltsV VFB -V , V WFB -WControl Supply VariationdV D , dV DB-1 — 1 V/µs Arm Shoot-through Blocking Time t DEAD For Each Input Signal, T C ≤ 100°C 1.5 — — µs Output r.m.s. Current*O PWM CC D DB rmsO PWM rmsT j ≤ 125°C, T C ≤ 100°CAllowable Minimum Input P WIN(on)0.5 — — µs Pulse Width** P WIN(off)0.5 — — µs V NC Voltage VariationV NCBetween V NC -N (Including Surge)-5.0—5.0Volts*The allowable r.m.s. current also depends on the actual application conditions.**DIP-IPM might not make response or work properly if the input signal plus width is less than the recommended minimum value.5PS21965, PS21965-A, PS21965-C Intellimod™ ModuleDual-In-Line Intelligent Power Module 20 Amperes/600 VoltsPowerex, Inc., 200 Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272512/05PS21965, PS21965-A, PS21965-C Intellimod™ ModuleDual-In-Line Intelligent Power Module 20 Amperes/600 Volts6Powerex, Inc., 200 Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272612/05Protection Function Timing DiagramsLOWER-ARMS CONTROL INPUT PROTECTION CIRCUIT STATEINTERNAL IGBT GATEOUTPUT CURRENT I C SENSE VOLTAGE OF THE SHUNT RESISTORFAULT OUTPUT F OShort-Circuit Protection (Lower-arms only with the external shunt resistor and RC filter)CONTROL INPUT PROTECTION CIRCUIT STATECONTROL SUPPLYVOLTAGE V DOUTPUT CURRENT I C FAULT OUTPUT F OUnder-Voltage Protection (Lower-side, UV D )A1: Normal operation – IGBT turn on and conducting current.A2: Short-circuit current detected (SC trigger).A3: IGBT gate hard interrupted.A4: IGBT turn off.A5: F O output with a fixed pulse width of t FO(min) = 20µs.A6: Input “L” – IGBT off.A7: Input “H” – IGBT on is blocked during the F O output period.A8: IGBT stays in off state.B1: Control supply voltage rise – After the voltage level reaches UV Dr , the drive circuit begins to work at the rising edge of the next input signal.B2 : Normal operation – IGBT turn on and conducting current.B3: Under-voltage trip (UV Dt ).B4: IGBT turn off regardless of the control input level.B5: F O output during under-voltage period, however, the minimum pulse width is 20µs.B6: Under-voltage reset (UV Dr ).B7: Normal operation – IGBT turn on and conducting current.7PS21965, PS21965-A, PS21965-C Intellimod™ ModuleDual-In-Line Intelligent Power Module 20 Amperes/600 VoltsPowerex, Inc., 200 Hillis Street, Youngwood, Pennsylvania 15697-1800 (724) 925-7272712/05Protection Function Timing DiagramsCONTROL INPUT PROTECTION CIRCUIT STATECONTROL SUPPLYVOLTAGE V DBOUTPUT CURRENT I CFAULT OUTPUT F OUnder-Voltage Protection (Upper-side, UV DB )C1: Control supply voltage rises – After the voltage level reaches UV DBr , the drive circuit begins to work at the rising edge of the next input signal.C2: Normal operation – IGBT turn on and conducting current.C3: Under-voltage trip (UV DBt ).C4: IGBT stays off regardless of the control input level, but there is no F O signal output.C5: Under-voltage reset (UV Dr ).C6: Normal operation – IGBT turn on and conducting current.Typical Interface CircuitWiring Method Around Shunt ResistorNC should be as NOTE: RC coupling at each input (parts shown dotted) may change depending on the PWM controlscheme used in the application and the wiring impedance of the printed circuit board. The DIP-IPM input signal section integrates a 3.3k Ω (min) pull-down resistor. Therefore, when using an external filtering resistor, care must be taken tosatisfy the turn-on threshold voltage requirement.。

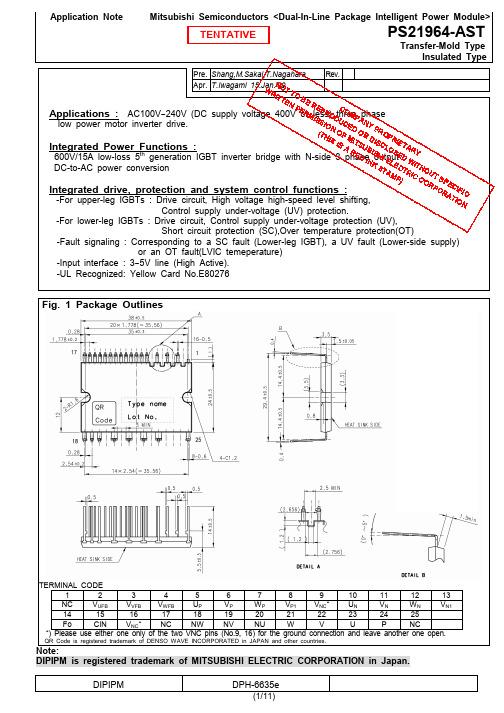

INSULATED TYPE

INSULATED TYPE

INSULATED TYPE

INSULATED TYPE

2.202.302.201.70—0.602.100.80110

3.7

4.5

mA

V T j = 25°C T j = 125°C

I C = 10A, T j = 25°C I C = 10A, T j = 125°C V CE(sat)V EC t on t rr t c(on)t off t c(off)I CES

Condition

Symbol Parameter

Limits Inverter IGBT part (per 1/6 module)Inverter FWD part (per 1/6 module)

R th(j-c)Q R th(j-c)F

Min.THERMAL RESISTANCE

Typ.Max.——

——

Unit T j = 25°C, –I C = 10A, V IN = 0V Condition

Symbol Parameter

Limits Min.Typ.Max.———0.60——————

Unit ELECTRICAL CHARACTERISTICS (T j = 25°C, unless otherwise noted)INVERTER PART

Collector-emitter saturation voltage

FWD forward voltage

Junction to case thermal

resistance (Note 3)

V D = V DB = 15V

V IN = 5V Switching times

V CC = 300V, V D = V DB = 15V

I C = 10A, T j = 125°C, V IN = 0 ↔ 5V Inductive load (upper-lower arm)

Collector-emitter cut-off current

V CE = V CES

1.701.801.701.100.300.401.500.50——

V µs µs µs µs µs °C/W °C/W

CONTROL (PROTECTION) PART

Note 4:Short circuit protection is functioning only for the lower-arms. Please select the external shunt resistance such that the SC trip-level is

less than 1.7 times of the current rating.

5:Fault signal is asserted corresponding to a short circuit or lower side control supply under-voltage failure.

Symbol

I D V FOH V FOL V SC(ref)I IN

UV DBt UV DBr UV Dt UV Dr t FO V th(on)V th(off)V th(hys)

Parameter

Condition

Limits Unit V D = V DB = 15V V IN = 5V V SC = 0V, F O terminal pull-up to 5V by 10k ΩV SC = 1V, I FO = 1mA

T j = 25°C, V D = 15V (Note 4)V IN = 5V

Trip level Reset level

Trip level Reset level

(Note 5)Applied between U P , V P , W P , U N , V N , W N -V NC

————4.9—0.430.7010.010.510.310.820—0.80.35

——————0.481.00—————2.11.30.65

2.800.552.800.55—0.950.531.5012.012.512.51

3.0—2.6——

Min.Typ.Max.mA mA mA mA V V V mA V V V V µs V V V

V D = V DB = 15V

V IN = 0V T j ≤ 125°C

Note 3:Grease with good thermal conductivity should be applied evenly with about +100µm~+200µm on the contacting surface of DIP-IPM

and heat-sink.

The contacting thermal resistance between DIP-IPM case and heat sink (R th(c-f)) is determined by the thickness and the thermal conductivity of the applied grease. For reference, R th(c-f) (per 1/6 module) is about 0.3°C/W when the grease thickness is 20µm and the thermal conductivity is 1.0W/m ·k.

Circuit current

F O output voltage Short circuit trip level Control supply under-voltage protection

Fault output pulse width ON threshold voltage OFF threshold voltage

ON/OFF threshold hysteresis voltage

Total of V P1-V NC , V N1-V NC V UFB -U, V VFB -V, V WFB -W

Total of V P1-V NC , V N1-V NC V UFB -U, V VFB -V, V WFB -W Input current

INSULATED TYPE

INSULATED TYPE

INSULATED TYPE

INSULATED TYPE

INSULATED TYPE。