NIOSII里的uart操作

- 格式:doc

- 大小:99.50 KB

- 文档页数:7

NIOS2完整教程NIOS II 是一款高度可配置的32位嵌入式软核处理器,由Intel旗下的Altera(现在归属于英特尔)推出。

它具有低功耗、高性能和可扩展性的特点,适用于各种嵌入式应用领域。

下面是一份简要的NIOSII完整教程,帮助您了解如何开始使用NIOSII。

1. Nios II 架构Nios II 架构包括处理器核、总线接口、存储器和外设设备。

处理器核包括CPU和一些协处理器,如乘法器、除法器等。

总线接口用于连接处理器核、存储器和外设设备。

存储器用于存储指令和数据。

外设设备包括UART、GPIO、SPI、I2C等。

2. Nios II 开发环境搭建首先,您需要安装Altera的Quartus软件来进行Nios II的开发。

Quartus提供了一个开发工具套件,包括编译器、仿真器和调试器。

您还需要安装Nios II EDS,这是一个集成开发环境,用于配置和生成Nios II处理器的软件。

安装完软件后,您可以创建一个新的Nios II项目。

3. Nios II 项目配置在Quartus中创建新的Nios II项目时,您需要指定处理器类型、时钟频率和存储器大小等参数。

您还可以选择添加外设设备和协处理器。

一旦项目创建完成,您可以使用Nios II EDS来配置处理器和外设设备,并生成相关的软件。

4. Nios II 软件开发Nios II 支持多种软件开发工具,包括C/C++编译器、汇编器和调试器。

您可以使用C/C++编译器来编写和调试应用程序。

您还可以使用汇编器来编写高性能的关键代码。

调试器可以帮助您检测和修复应用程序中的错误。

5. Nios II 系统调试在开发过程中,您可能需要进行系统调试,以解决应用程序的问题。

Nios II 支持硬件和软件调试。

硬件调试通过连接JTAG接口进行,可以在硬件级别上进行调试。

软件调试使用Nios II调试器进行,可以在软件级别上进行调试。

6. Nios II 系统验证在完成软件开发和调试后,您可以进行系统验证,确保系统的正确性和稳定性。

//串口程序已经试过//实现发A收到E 发数字收到ERROR#ifndef UART_H_#define UART_H_#define UART ((UART_STR *) UART_BASE)#include"inc.h"#include "sys/alt_irq.h"#include "system.h"#include "stdlib.h"#include "stdio.h"#include <unistd.h>#include <io.h>unsigned char receive_temp;//接收到的临时数据unsigned char buffer[6]="ERROR";#define BUFFER_SIZE 200 /*---------------------------------------------------------------- * Define *---------------------------------------------------------------*/typedef struct{unsigned char mode_flag; //xmodem 1;uart 0;unsigned int receive_flag;unsigned int receive_count;unsigned char receive_buffer[BUFFER_SIZE];int (* send_byte)(unsigned char data);void (* send_string)(unsigned int len, unsigned char *str);int (* init)(void);unsigned int (* baudrate)(unsigned int baudrate);}UART_T;extern UART_T uart;/* * ==================================================== * Filename: uart.c* Description: RS232 device driver* Version: * Created: * Revision: none* Compiler: Nios II IDE* Author: AVIC* Company:* ===================================================*//*--------------------------------------------------------------* Include*-------------------------------------------------------------*//*--------------------------------------------------------------* Function Prototype*--------------------------------------------------------------*/static int uart_send_byte(unsigned char data);static void uart_send_string(unsigned int len, unsigned char *str);static int uart_init(void); static void uart_ISR(void);static int set_baudrate(unsigned int baudrate);//初始uart结构体,注意结构体初始化方式UART_T uart={.mode_flag=0,.receive_flag=0,.receive_count=0,.send_byte=uart_send_byte,.send_string=uart_send_string,.init=uart_init,.baudrate=set_baudrate };/** === FUNCTION ========================================* Name: uart_send_byte* Description: 収送一个字节数据* Description: 収送一个字节数据*/static int uart_send_byte(unsigned char data){//将収送癿数据放刡収送数据缓冲区内,等徃状忞寄存器TRDY置1,当TRDY置1,说明//接收完毕UART->TXDATA.BITS.TRANSMIT_DATA = data;while(!UART->STATUS.BITS.TRDY);return 0;}/** === FUNCTION ========================================* Name: uart_send_string* Description: 収送字符串数据* ===================================================== */static void uart_send_string(unsigned int len, unsigned char *str){while(len--){uart_send_byte(*str++);}}/* * === FUNCTION ========================================* Name: uart_init* Description: 初始化程序* ===================================================== */static int uart_init(void){//设置波特率为9600set_baudrate(9600);// 对控制寄存器的irrdy进行置1,表示当接收准备好后,中断使能UART->CONTROL.BITS.IRRDY=1;//清除状忞寄存器,返就是处理整个寄存器的方式UART->STATUS.WORD=0;//注册uart中断,ISR为uart_ISRalt_irq_register(UART_IRQ, NULL, uart_ISR);return 0;}/** === FUNCTION ========================================* Name: uart_ISR* Description: 串口中断* =====================================================*/static void uart_ISR(void){//等待状态寄存器的接收数据状态位rrdy,当rrdy位为1时,说明新接收的值传输到了接//收数据寄存器while(!(UART->STATUS.BITS.RRDY));//reveive_buffer为我们通过栈的方式在内存中开设的内存块,将接受数据寄存器中的//数据放到返个内存块中receive_temp=UART->RXDATA.BITS.RECEIVE_DATA;if(((receive_temp>64)&&(receive_temp<91))||((receive_temp>96)&&(receive_temp<123))) {if((receive_temp==119)||(receive_temp==87)||(receive_temp==120)||(receive_temp==88)||(re ceive_temp==121)||(receive_temp==89)||(receive_temp==122)||(receive_temp==90)) receive_temp=receive_temp-22;else receive_temp=receive_temp+4;}else uart.send_string(sizeof(buffer),buffer);uart_send_byte(receive_temp);//将接收到的一个数据发送出去}/** === FUNCTION ========================================* Name: set_baudrate* Description: 设置波特率* =====================================================*/static int set_baudrate(unsigned int baudrate){//设置波特率有一个公式的,波特率=时钟频率/(divisor+1),转换以后就是下面了。

一、Nios II中断简述Nios II 的中断处理方式带有典型的RISC处理器的特征,所有的中断处理都从同一入口进入,然后由软件加以分配。

负责分配工作的软件叫系统ISR,它是由开发系统提供的,自动的连接到可执行程序上。

系统ISR维护着一个中断向量表,表中的每一项代表着一个专项处理程序的入口。

所有的专项处理程序都是由用户定义然后注册到中断向量表中的,叫做用户ISR。

系统ISR的入口地址是在SOPC_Builder中定义的,叫Exception Address。

和中断有关的CPU寄存器有:ctl0、ctl1、ctl3、ctl4。

Ctl0 是程序状态字,它的bit0位是全局中断允许位,1代表允许,0代表禁止。

Ctl1是程序状字的堆栈,当发生中断时,由它保留一个程序状态字的备份。

Ctl3是中断允许寄存器,其中每一位控制着一个中断源,1代表允许,0代表禁止,共计32位。

Ctl4是中断申请寄存器,每一位对应着一个中断源的中断请求,1代表有中断,0代表没有……计32位。

NiosII的中断处理过程是这样的:1. 拷贝一份程序状态字到ctl1;2. 清除全局中断允许位PIE,禁止中断;3. 将下一条将执行的指令的地址存入R29,以便中断返回之用;4. 跳转到中断入口地址,进入系统ISR;5. 系统ISR保护现场;6. 系统ISR检测ctl1的PIE位,如为0则进入软中断处理程序从11继续,否则由7继续;7. 系统ISR检测Ctl4,如果有中断申请,则转到硬中断处理和序,否则进入软中断处理程序;8. 硬中断处理程序将检测中断申请号,并检索中断向量表,跳转到用户中断处理程序;9. 用户中断处理程序做出具体的处理,最后返回系统ISR;10. 系统ISR恢复现场,并返回;11. 软中断处理程序进行陷井指令、模拟指令判断,并做相应处理,然后返回系统ISR;12. 系统ISR恢复现场并返回;软中断处理程序是用来处理由软件发起的中断事件的,包括调试指令引起的中断及未定义指令引起的中断。

一、建立quartus ii工程首先,双击quartus ii 9.1图标打开软件,界面如下图1.1所示图1.11.1新建工程(1)点击file –>New Project Wizard 出现图1.2所示的对话框。

图1.2(2)点击Next。

如图1.3所示:第一行是工程的路径,二、三行为实体名。

填好后点击Next。

图1.3(3)此处可选择加入已设计好的文件到工程,点击Next。

图1.4(4)选择设计器件如图1.5所示。

接着点击Next。

图1.5(5)接着点击Next。

无需改动,点击finish,显示如下图所示。

图1.6(6)此时,工程已经建立完成,接下来需要建立一个原理图输入文件,点击file –>New ->Block Diagram/Schematic File 后如图1.7所示。

图1.7二、构建一个nios ii 软核(1)首先点击Tools ->Sopc Builder图2.1在System Name中输入软核的名称,注意:软核的名称不能和quartus工程的实体名相同,否则编译会出现错误,接着点击ok。

图2.2图中clk_0为时钟名称,100.0为时钟值双击可修改其值。

即软核的时钟就是100MHZ。

(2)建立nios ii处理器点击Processors -> Nios ii Processor 如图2.3所示图2.3点击后,将出现下图,在下图中选择软核的类型。

这里提供了三种类型,Nios II/e占用资源最少600-800LEs,功能也最简单,速度最慢。

Nios II/s占资源比,前者多一些,功能也多了,速度也忚一些Nios II/f 占资源最多,功能也最多,速度就最快,用户可根据实际的需要选择不同的类型。

此处选择Nios II/f型,速度和功能都能满足。

下方Reset Vector是复位后启动的Memory类型和偏移量。

待SDRAM设置号以后再来设置此处。

IDE: Quartus Prime 18.0 Standard Edition,max10能用的只有Standard和lite版本.开发板: DE10-Lite, 芯片型号为:10M50DAF484C7G语言: Verilog HDL, C.Step 1.建立一个MAX10的工程. 注意Device and pin options的configuration mode的选择。

基于MAX10的NIOS II入门Step 2. 启动Platform designer (老版本叫Qsys),添加Nios II Processor、onchip_memory、onchip_flash、pio、jtag_uart以及sysid_qsys几个简单的模块。

采用默认就可以了,Clk直接使用的是50 MHZ。

连接相关clk等的连线(连线都连上就行)。

Step 3. 设置NIOS. 程序储存在FLASH中,在RAM运行Step 4. 设置flash. 注意configuration mode. 需要与Device and pin options的configuration mode设置一致。

Step 5. 基本就这些设置,完后generate,生成HDL文件。

在Test.v中调用NIOS_CPU,然后在Quartus左侧的文件列表中添加synthesis目录下的NIOS_CPU.qip文件。

此处NIOS_CPU是你自己命名保持的platform designer工程名,编译,下载到Max10中。

Step 6. Tool -> NIOS II software build tools for eclipse. 新建一个Nios II Application and BSP form Template. SOPC information file name选择上一步生成的NIOS_CPU.sopcinfo. Template选择hello_world_small应用,点击finish完成应用程序创建。

NIOS II功能模块说明(一)结合前面的NIOS II处理器架构简介,后面对各功能模块进行简要说明。

NIOS II功能模块说明(一)l 通用寄存器NIOS II架构包含32个32位通用寄存器,还包含32个32位的控制寄存器。

处理器架构能支持超级用户模式和普通用户模式,以便系统软件保护不同应用的控制寄存器。

这可以通过设置控制寄存器来实现。

NIOS II架构还能兼容未来增加的浮点寄存器。

算术逻辑单元(ALU)NIOS II的算术逻辑操作是基于通用寄存器来完成的,整个操作需要将一个或两个输入操作数进行运算,然后将计算结果输出并存储到寄存器中。

NIOS II支持的数据运算包括:1.算术运算:包括对有符号和无符号操作数进行的加、减、乘和除运算。

2.关系运算:包括对有符号和无符号操作数进行的等于、不等于、大于等于和小于运算。

EDA中国门户网站2e#t;jF"{1S3.逻辑运算:包括对逻辑操作数进行的与、或、或非和异或操作4.移位和循环移位操作:可以在单指令对操作数进行0至31位的移位和循环移位操作,并且能支持左移和右移、左循环和右循环移位。

NIOS II核并没有采用硬件来实现全部的NIOS II指令集,对没有用硬件实现的指令又称为未实现指令(Unimplemented Instructions)。

NIOS II核支持IEEE标准754‐1985规定的单精度浮点指令,这些单精度定制指令包括浮点加、减和乘运算,浮点除运算作为扩展的简单指令集有效。

这些指令均作为定制指令在NIOS II中实现,通过NIOS II Processor MegaWizard接口可以很容易的设计这些浮点指令。

需要注意的是,浮点除指令若采用硬件来实现,或占用比其他指令多的多的资源,若在设计中不使用硬件实现,则处理器会使用软件来实现浮点除运算。

另外,由于指令集仿真器不支持定制指令,若需要在指令集仿真器上运行软件,可以使用如下的#pragma描述在软件中禁止浮点定制指令,而是用软件实现浮点指令。

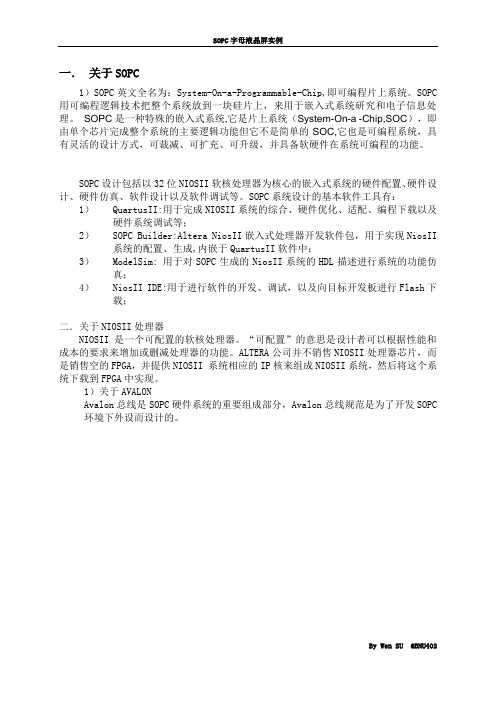

一.关于SOPC1)SOPC英文全名为:System-On-a-Programmable-Chip,即可编程片上系统。

SOPC 用可编程逻辑技术把整个系统放到一块硅片上,来用于嵌入式系统研究和电子信息处理。

SOPC是一种特殊的嵌入式系统,它是片上系统(System-On-a -Chip,SOC),即由单个芯片完成整个系统的主要逻辑功能但它不是简单的SOC,它也是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

SOPC设计包括以32位NIOSII软核处理器为核心的嵌入式系统的硬件配置、硬件设计、硬件仿真、软件设计以及软件调试等。

SOPC系统设计的基本软件工具有:1)QuartusII:用于完成NIOSII系统的综合、硬件优化、适配、编程下载以及硬件系统调试等;2)SOPC Builder:Altera NiosII嵌入式处理器开发软件包,用于实现NiosII 系统的配置、生成,内嵌于QuartusII软件中;3)ModelSim: 用于对SOPC生成的NiosII系统的HDL描述进行系统的功能仿真;4)NiosII IDE:用于进行软件的开发、调试,以及向目标开发板进行Flash下载;二.关于NIOSII处理器NIOSII 是一个可配置的软核处理器。

“可配置”的意思是设计者可以根据性能和成本的要求来增加或删减处理器的功能。

ALTERA公司并不销售NIOSII处理器芯片,而是销售空的FPGA,并提供NIOSII 系统相应的IP核来组成NIOSII系统,然后将这个系统下载到FPGA中实现。

1)关于AVALONAvalon总线是SOPC硬件系统的重要组成部分,Avalon总线规范是为了开发SOPC 环境下外设而设计的。

图1-1 一个SOPC的示例二. SOPC简单实例:软核控制LCD液晶字母显示器1.系统构成规划1)系统功能:在character LCD上显示”Hello LCD from NiosII!”2)本系统中需要的外围器件:(1)L CD:输出显示(2)S RAM存储器:程序运行时将其导入SRAM3)SOPC中建立系统需要添加的模块包括:(1)N ios II 32bit CPU(2)L CD display(3)外部RAM总线(4)外部RAM接口(5)J TAG UART Interface(6)定时器2.硬件系统的建立1)首先打开Quartus II 建立工程文件:将工程文件命名为hello_lcd,顶层文件与工程文件同名。

NIOSII教程NIOS II 是一种基于软核的处理器,可用于 FPGA 设计中。

它是由Altera 公司所开发的。

NIOS II 可以在 FPGA 中进行快速原型设计,并且具有高度可配置性和可扩展性。

本文将介绍 NIOS II 的基本架构和使用方法。

NIOSII架构基于RISC架构,它是一个32位的处理器,并且具有可选的指令扩展。

它的流水线深度可以根据设计的需求进行配置,以实现不同的性能要求。

NIOSII支持多种功能,包括硬件中断、异常处理以及浮点运算等。

在开始使用NIOSII进行开发之前,首先要进行软核处理器的配置。

配置包括选择所需的指令集、流水线深度和其他性能参数。

配置完成后,可以将软核处理器添加到FPGA设计中。

一旦软核处理器被添加到FPGA设计中,就可以开始编写应用程序。

NIOSII支持标准的C/C++语法,并且还提供了一些特殊的函数和指令,用于访问FPGA的硬件资源。

例如,可以使用特殊函数来配置GPIO引脚、读取和写入存储器以及执行其他与硬件交互的操作。

使用NIOSII进行FPGA开发具有许多优点。

首先,它提供了一种快速原型设计的方法,可以大大加快开发进程。

其次,NIOSII的可扩展性和高度可配置性使得它适用于各种不同的FPGA设计需求。

最后,NIOSII的开发工具和调试接口使得开发和调试过程更加简单和高效。

总结起来,NIOS II 是一种基于软核的处理器,适用于 FPGA 设计中。

它具有灵活性和可配置性,可以使用 C/C++ 或 HDL 进行开发,并通过Altera 公司提供的工具链进行编译和调试。

NIOS II 提供了一种快速原型设计的方法,并且适用于各种不同的 FPGA 设计需求。

uart的基本编程步骤UART(通用异步收发传输)是一种常见的串行通信协议,用于在微控制器和外部设备之间进行数据传输。

下面是UART的基本编程步骤:1. 初始化UART,首先,你需要在微控制器上初始化UART模块。

这通常涉及设置波特率(通信速率)、数据位、停止位和校验位等参数。

这些参数的设置取决于你的具体应用需求和外部设备的要求。

2. 配置引脚,UART通常使用两个引脚进行数据传输,一个用于发送(TX),一个用于接收(RX)。

你需要在微控制器上配置这些引脚,并确保它们与外部设备正确连接。

3. 发送数据,要发送数据,你需要将要发送的数据加载到UART发送缓冲区。

一旦数据被加载,UART模块将自动开始发送数据。

你需要确保发送的数据符合UART的规范,并且在发送数据之前,需要检查发送缓冲区是否为空,以避免数据丢失。

4. 接收数据,接收数据与发送类似,你需要设置接收缓冲区,并在接收到数据后从中读取数据。

同样,你需要检查接收缓冲区是否有新的数据可用,以避免数据丢失。

5. 中断处理(可选),在一些情况下,你可能需要使用中断来处理UART的发送和接收。

这可以帮助你及时响应数据的到来或发送完成等事件。

6. 错误处理,最后,你需要考虑如何处理可能出现的错误,比如数据丢失、校验错误等。

这可能涉及到错误标志的检查和相应的处理流程。

总的来说,UART的基本编程步骤包括初始化UART模块、配置引脚、发送数据、接收数据、中断处理(可选)和错误处理。

在实际编程中,你需要根据具体的微控制器型号和外部设备的通信协议要求来进行相应的设置和处理。

Nios II中断简述及中断调试技巧2008-11-05 17:35一、Nios II中断简述Nios II 的中断处理方式带有典型的RISC处理器的特征,所有的中断处理都从同一入口进入,然后由软件加以分配。

负责分配工作的软件叫系统ISR,它是由开发系统提供的,自动的连接到可执行程序上。

系统ISR维护着一个中断向量表,表中的每一项代表着一个专项处理程序的入口。

所有的专项处理程序都是由用户定义然后注册到中断向量表中的,叫做用户ISR。

系统ISR的入口地址是在SOPC_Builder中定义的,叫Exception Address。

和中断有关的CPU寄存器有:ctl0、ctl1、ctl3、ctl4。

Ctl0 是程序状态字,它的bit0位是全局中断允许位,1代表允许,0代表禁止。

Ctl1是程序状字的堆栈,当发生中断时,由它保留一个程序状态字的备份。

Ctl3是中断允许寄存器,其中每一位控制着一个中断源,1代表允许,0代表禁止,共计32位。

Ctl4是中断申请寄存器,每一位对应着一个中断源的中断请求,1代表有中断,0代表没有……计32位。

NiosII的中断处理过程是这样的:1.拷贝一份程序状态字到ctl1;2.清除全局中断允许位PIE,禁止中断;3.将下一条将执行的指令的地址存入R29,以便中断返回之用;4.跳转到中断入口地址,进入系统ISR;5.系统ISR保护现场;6.系统ISR检测ctl1的PIE位,如为0则进入软中断处理程序从11继续,否则由7继续;7.系统ISR检测Ctl4,如果有中断申请,则转到硬中断处理和序,否则进入软中断处理程序;8.硬中断处理程序将检测中断申请号,并检索中断向量表,跳转到用户中断处理程序;9.用户中断处理程序做出具体的处理,最后返回系统ISR;10.系统ISR恢复现场,并返回;11.软中断处理程序进行陷井指令、模拟指令判断,并做相应处理,然后返回系统ISR;12.系统ISR恢复现场并返回;软中断处理程序是用来处理由软件发起的中断事件的,包括调试指令引起的中断及未定义指令引起的中断。

UART总线协议详解UART(Universal Asynchronous Receiver Transmitter)是一种常用的串行通信接口协议,可用于数据传输和通信控制。

它是一种同步/异步方式实现数据传输的协议,在计算机、嵌入式系统和通信设备等领域得到广泛应用。

下面详细介绍UART总线协议。

1. 起始位(Start Bit):用于表示数据传输的开始,一般为低电平,持续一个周期。

2. 数据位(Data Bit):用于传输数据,可以是5、6、7或8个位。

3. 校验位(Parity Bit):用于校验数据的正确性,可选性的,可以是奇偶校验或无校验。

4. 停止位(Stop Bit):用于表示数据传输的结束,一般为高电平,持续一个周期。

1.简单易用:UART总线协议是一种简单的串行通信协议,易于实现和使用。

2.可靠性高:UART总线协议的数据传输是通过电平的转变来实现的,相对稳定可靠。

3.兼容性好:UART总线协议是一种通用协议,在许多设备和领域都得到广泛应用。

1.传输速率有限:UART总线协议的传输速率受限于波特率,相对于其他高速传输协议较慢。

2.线数较多:UART总线协议需要两条线进行通信,占用了相对较多的硬件资源。

1.计算机通信:UART总线协议可用于计算机之间或计算机与外部设备之间的通信,如串口通信、打印机通信等。

2.嵌入式系统:UART总线协议可用于嵌入式系统中的数据传输和通信控制,如单片机与外部设备的通信等。

3.通信设备:UART总线协议可用于网络设备、通信设备等的数据传输和控制。

总结:UART总线协议是一种常用的串行通信接口协议,可以实现数据传输和通信控制。

它通过两条线进行全双工通信,采用起始位、数据位、校验位和停止位的格式进行数据传输。

UART总线协议简单易用,可靠性高,应用广泛。

尽管它的传输速率有限,并且需要占用相对较多的硬件资源,但在许多计算机、嵌入式系统和通信设备领域都得到了广泛应用。

【翻译】NiosII处理器简介(NiosII)处理器简介本⽂介绍的Altera Nios II处理器是⼀个可在Altera FPGA器件⾥实现的软核处理器。

主要讲述Nios II的基本架构和其指令集。

配合Quartus II 软件,使⽤Altera的SOPC Builder可以很容易的把Nios II处理器和它的内存及外围组件例化。

关于Nios II处理的完整描述请参阅《Nios II处理器参考⼿册》,在Altera官⽹的⽂献区可找到该⼿册。

SOPC Builder的简介在⼊门简介⾥有提供,也可在官⽹的⼤学计划板块找到。

本⽂包含的内容:⽬录Altera Nios II处理器是⼀个软核处理器,⽤硬件描述语⾔定义,使⽤Quartus II软件可在Altera的FPGA器件⾥实现。

本⽂为想要在Altera DE2开发板上实现⼀个基本Nios II系统的⽤户提供⼀个关于Nios II处理器的简介。

系统Nios II处理器可使⽤许多其他组件构成⼀个完整的系统。

这些组件包括许多标准外设之外,还可由⽤户⾃定义外设。

Altera DE2开发板含有⼏个可集成在Nios II系统⾥的组件。

图1就是⼀个这样的系统。

Nios II处理器和⽤来连接DE2上其他芯⽚的接⼝都在Cyclone II FPGA⾥实现。

这些组件通过Avalon 交换结构连接。

Cyclone II器件的内存块可为Nios II处理器提供⽚上内存。

它们可直接或通过Avalon⽹络与处理连接。

通过相应的接⼝访问DE2上的SRAM和SDRAM。

系统使⽤的I/O设备例化为I/O接⼝。

连接主机和DE2的USB线缆接⼝由⼀个特殊的JTAG UART接⼝提供。

这个接⼝电路和其相应的软件叫做USB_Blaster。

另⼀个名为JTAG Debug的模块,⽤来使主机控制Nios II处理器。

这样,就可以执⾏操作,⽐如,下载程序到内存⾥,启动和停⽌执⾏,设置程序断点,和搜集实时数据。

基于NIOS2的SOPC系统构建1 NIOS II体系结构Nios2处理器是Altera公司推出的32位RISC嵌入式处理器它是SOPC的核心。

具有200DMIPS 用来计算同一秒内系统的处理能力它的单位以百万来计算以上的运算能力处理器以软核的形式实现具有高度的灵活性和可配置性。

Nios II系列包括三种产品1 Nios II/f快速最共的系统性能中等FPGA使用量 2 Nios II/s标准高性能低FGPA使用量 3 Nios II/e经济低性能最低的FGPA 使用量。

Nios II系列支持使用专用指令。

专用指令是用户增加的硬件模块它增加了算术逻辑单元ALU。

开发者能为系统中使用的每个Nios II 砥鞔唇ǘ啻?56个专用指令这使得设计者能够细致地调整系统硬件以满足性能目标。

专用指令逻辑和本身Nios II指令相同能够从多达两个源寄存器取值可选择将结果写回目标寄存器。

同时Nios II系列支持60多个外设选项通过选择合适的外设获得最合适的处理器、外设和接口组合而不必支付根本不使用的硅片功能。

Nios II特性全32位指令集、数据和地址路径32个通用寄存器32个外部中断源单指令3232乘法器、除法器可产生32位的结果专门用于计算64位和128位乘法的指令用于单精度浮点运算的浮点运算指令单指令筒形移位寄存器可以同很多片上外设、接口、片外存储器和片外外设接口使用IDE驱动硬件调试模块可以轻松的对处理器进行开始、停止、中断等操作图1.1是Nios II处理器核的结构图各模块将分别做简要介绍。

图1.1 Nios II处理器核模块图数据处理主要由算术逻辑单元ALU完成现有的Nios II 内核中暂时没有协处理器。

用户逻辑接口Custom Instruction Logic用来连接用户定制的逻辑电路与Nios II内核。

在上图中可以看出Nios II采用哈佛结构数据总线和指令总线分开。

为了调试方便Nios II处理器集成了一个JTAG调试模块可以方便的与IDE 环境联合调试。

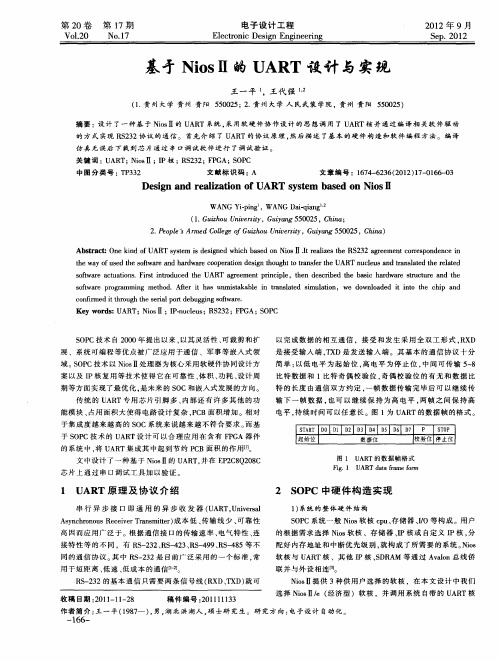

基于NiosⅡ的UART设计与实现王一平;王代强【摘要】One kind of UART system is designed which based on Nios II .It realizes the RS232 agreement correspondence in the way of used the software and hardware cooperation design thought to transfer the UART nucleus and translated the related software actuations. First introduced the UART agreement principle, then described the basic hardware structure and the software programming method. After it has unmistakable in translated simulation, we downloaded it into the chip and confirmed it through the serial port debugging software.%设计了一种基于NiosⅡ的UART系统。

采用软硬件协作设计的思想调用了UART核并通过编译相关软件驱动的方式实现RS232协议的通信。

首先介绍了UART的协议原理,然后描述了基本的硬件构造和软件编程方法。

编译仿真无误后下栽到芯片通过串口调试软件进行了调试验证。

【期刊名称】《电子设计工程》【年(卷),期】2012(020)017【总页数】3页(P166-168)【关键词】UART;NiosⅡ;IP核;RS232;FPGA;SOPC【作者】王一平;王代强【作者单位】贵州大学,贵州贵阳550025;贵州大学人民武装学院,贵州贵阳550025【正文语种】中文【中图分类】TP332SOPC技术自2000年提出以来,以其灵活性、可裁剪和扩展、系统可编程等优点被广泛应用于通信、军事等嵌入式领域。

uart验证功能点(原创版)目录1.UART 简介2.UART 验证的重要性3.UART 验证的功能点4.如何进行 UART 验证5.总结正文一、UART 简介UART,全称为 Universal Asynchronous Receiver/Transmitter,即通用异步收发器,是一种串行通信接口。

它广泛应用于电子设备之间的数据传输,如计算机与外设、手机与蓝牙设备等。

UART通过将数据字符从并行转换为串行,以及将从串行转换为并行的数据字符传输,实现了数据在设备之间的高效传输。

二、UART 验证的重要性在各类电子设备和系统中,UART 通信模块的稳定性和可靠性至关重要。

因为一旦 UART 通信出现问题,可能导致整个系统无法正常工作。

因此,对 UART 进行验证以确保其功能正常,成为电子产品研发和生产的关键环节。

三、UART 验证的功能点UART 验证的主要功能点包括以下几个方面:1.通信协议验证:检查 UART 通信是否遵循所规定的通信协议,如波特率、数据位、停止位等。

2.信号完整性验证:验证接收和发送的信号在传输过程中是否保持完整,没有受到干扰或衰减。

3.传输速率验证:测试 UART 通信的传输速率,确保其达到设计要求。

4.误码率验证:评估 UART 通信过程中的误码率,以确保数据传输的准确性。

5.接口兼容性验证:检查 UART 与其他接口的兼容性,如与串口、I2C、SPI 等接口的互操作性。

四、如何进行 UART 验证UART 验证的过程通常包括以下几个步骤:1.制定验证计划:根据产品需求和 UART 通信规范,制定详细的验证计划,明确验证的目标、方法、工具和标准。

2.搭建验证环境:搭建与实际应用场景相符的硬件和软件环境,以便对 UART 通信进行实际测试。

3.设计测试用例:针对 UART 验证的功能点,设计一系列测试用例,包括正常情况和异常情况。

4.执行测试用例:按照测试用例执行 UART 通信测试,记录测试结果。

传真机作为图文通信设备得到了广泛应用。

为了进行正常通信,需要在通信过程中进行一些“操作”,或者由机器自动执行某些操作,发送方和接收方要进行“磋商”。

接收/发送双方要经过发出表示信号、命令信号、响应信号和证实信号这一过程,这是一个不断“操作”和“确认”的渐进过程。

这个通信规程就是ITU-T在T.30建议中作的规定,T.30建议书作为传真机在公用电话交换网上的传输规程,对公用电话交换网上传真业务的发展起到了决定性的作用。

目前传真通信的产品开发主要是基于Conexant等公司的专用传真芯片,对系统二次开发。

本文从替代传统专用芯片的角度,提出一种新的基于NiosII传真系统方案,即软硬件协同开发的流程,分析并设计实现传真通信。

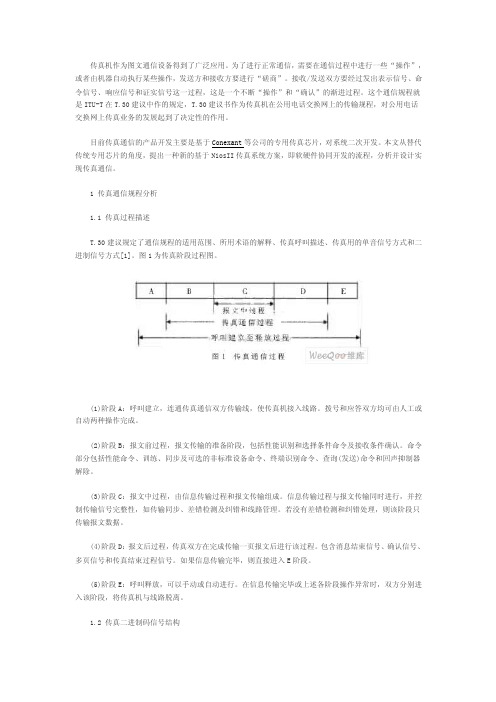

1 传真通信规程分析1.1 传真过程描述T.30建议规定了通信规程的适用范围、所用术语的解释、传真呼叫描述、传真用的单音信号方式和二进制信号方式[1]。

图1为传真阶段过程图。

(1)阶段A:呼叫建立,连通传真通信双方传输线,使传真机接入线路。

拨号和应答双方均可由人工或自动两种操作完成。

(2)阶段B:报文前过程,报文传输的准备阶段,包括性能识别和选择条件命令及接收条件确认。

命令部分包括性能命令、训练、同步及可选的非标准设备命令、终端识别命令、查询(发送)命令和回声抑制器解除。

(3)阶段C:报文中过程,由信息传输过程和报文传输组成。

信息传输过程与报文传输同时进行,并控制传输信号完整性,如传输同步、差错检测及纠错和线路管理。

若没有差错检测和纠错处理,则该阶段只传输报文数据。

(4)阶段D:报文后过程,传真双方在完成传输一页报文后进行该过程。

包含消息结束信号、确认信号、多页信号和传真结束过程信号。

如果信息传输完毕,则直接进入E阶段。

(5)阶段E:呼叫释放,可以手动或自动进行。

在信息传输完毕或上述各阶段操作异常时,双方分别进入该阶段,将传真机与线路脱离。

1.2 传真二进制码信号结构传真过程用的二进制信号,以300 b/s的速率传送,这是三类机二进制代码过程数据传输的标准速率。

NIOSII里的uart操作第一步,在sopc里增加一个串口第二步:操作UART的三种方法(1)直接寄存器操作。

NIOS II 的串口编程有多种方式,很多地方给的程序大多数更像纯C语言写法,占用程序空间比较大,这里以一个更像单片机串口的程序,占用空间当对而言要小,且对像工业控制的数据传输更实用简单些(个人觉得)。

extern unsigned char leddata[8];//UART发送一个字节子程序void Uart_send(unsigned char data){alt_u16 status;status=IORD_ALTERA_AVALON_UART_STATUS(UART_BASE);while(!(status&0x0040))//等待发送完成status=IORD_ALTERA_AVALON_UART_STATUS(UART_BASE);IOWR_ALTERA_AVALON_UART_TXDATA(UART_BASE,data);}//UART发送多个字节子程序void Uart_send_n(unsigned char *ptr,unsigned char n){for(;n>0;n--){Uart_send(*ptr);ptr++;}}//UART接收子程序int Uart_receive(void){alt_u16 status;int temp;status=IORD_ALTERA_AVALON_UART_STATUS(UART_BASE);while(!(status&0x0080))//等待发送完成status=IORD_ALTERA_AVALON_UART_STATUS(UART_BASE);temp=IORD_ALTERA_AVALON_UART_RXDATA(UART_BASE);return temp;}//串口接收中断服务程序void Uart_ISR(void * context,alt_u32 id){unsigned char temp;temp=IORD_ALTERA_AVALON_UART_RXDATA(UART_BASE);leddata[5]=temp;}//串口中断初始化void Uart_init(){IOWR_ALTERA_AVALON_UART_CONTROL(UART_BASE, 0x80);//接收中断使能IOWR_ALTERA_AVALON_UART_STATUS(UART_BASE, 0x0);//清状态标志// IOWR_ALTERA_AVALON_UART_RXDATA(UART_BASE, 0x0);//清接收寄存器alt_irq_register(UART_IRQ,0,Uart_ISR);//中断注册,此处编译总出现警告,还请高手能指点。

warning: implicit declaration of function `alt_irq_register' test3 uart_zx.h}程序中接收部分写了一个扫描的和一个中断的,可跟据需要选择。

我想中断接收的更实用些吧。

其中UART_BASE请更换为你自己UART的名字即可。

(2)类似C语言的操作,用printf函数。

(编译过程太慢!可以喝杯茶了!)使用这种方法要加上这一句 #include <stdio.h>别忘了在System library Properties 的stdout/stdin 选择你的串口。

int main (){printf("Hello world.\n");return 0;}执行上述程序可以看到效果!(3)转载(没试过)下面介绍第三种串口编程的方法,我们还是从一个简单的例子看起吧:#i nclude <stdio.h>#i nclude <string.h>int main (void){char* msg = “hello world”;FILE* fp;fp = fopen (“/dev/jtag_uart”, “r+”);if (fp){fprintf(fp, “%s”,msg);fclose (fp);}return 0;}这种方法才是标准的串口操作方法。

说实话,NiosII下的串口编程比Nios下的已经简化了很多。

Nios下的串口操作要调用Altera自定义的函数,而NiosII 下,由于有了HAL(详见NiosII step by step 2关于HAL的介绍)的存在,串口编程已经成为标准的文件操作了。

我们知道,在Unix/Linux等操作系统里所有的流操作都可以看成是文件,NiosII 吸收了这一点(可能是因为Nios吸收了Cygwin的很多特性吧,呵呵),把对串口的流操作也当成了一种文件操作。

操作一个串口时,只需要对它相应的设备驱动读写数据就好了。

fp = fopen (“/dev/jtag_uart”, “r+”);这个语句的意思就是打开jtag_uart的驱动,并且可以对其进行读写(r+),if (fp){fprintf(fp, “%s”,msg);fclose (fp);}这段语句的意思就是如果文件打开没问题,指针句柄有效,就可以用fprintf 语句向这个串口写数据了,这里要写的数据是一个字符串。

写完之后关闭文件。

你看,所有的操作几乎与C语言下的文件操作没什么区别,呵呵,唯一不同的就是待操作的文件是你要操作的外设,而不是一个“文件”。

利用这种方法,你可以立刻举一反三,只要改动一点点,就可以操作所有的串口外设了。

要改动的就是/dev/jtag_uart,把/dev/后面的外设名改改就是了。

例如我要操作NiosII与PC之间的通信,只要改为/dev/pc_uart就行啦。

再延伸一点,如果你的系统里面要添加四个使用串口流的设备,分别是JTAG UART、PC UART、GSM UART、GPS UART,那么对于每个外设,只要编写四个相应的文件操作程序就行了:fp = fopen (“/dev/jtag_uart”, “r+”);fp = fopen (“/dev/pc_uart”, “r+”);fp = fopen (“/dev/gps_uart”, “r+”);fp = fopen (“/dev/gsm_uart”, “r+”);当然,不要把所有外设的操作都写在一个程序里,应该分开写,最后分成不同的函数,再最后集成到一个main函数里。

这是编程细节方面的问题了,不多说了。

以上介绍的方法就是我们一般会采用的方法,具有很大的灵活性,可随时更改、添加外设程序,克服了第一种方法的局限性。

说到这里,你应该知道其实第一种方法就是第二种方法的在NiosII IDE里面的隐含集成,其实图形用户界面背后也不过就是第二种方法的程序,只是stdin/stdout/stder都是由你指定罢了,呵呵。

(估计Altera设计这三个选项就是为了方便懒人和初学者,呵呵)nios串口接收--中断方式(源码)#include<stdio.h>#include<string.h>#include<fcntl.h>#include"system.h"#include"unistd.h"#include "alt_types.h"#include <unistd.h>#include "altera_avalon_uart_regs.h"#include "altera_avalon_pio_regs.h"#include "sys/alt_irq.h"#define quelen 2048char queue[quelen];int indexc = 0;int temp_index=0;char ch;static void init_uart_receiver();static void handle_uart_interrups(void* context, alt_u32 id);int main(void){init_uart_receiver();printf("successful");int f=0;while (f<1){if (temp_index!=indexc){printf("%c", queue[temp_index]);temp_index++;}}return 0;}static void init_uart_receiver(){void* status_ptr;IOWR_ALTERA_AVALON_UART_CONTROL(UART_BASE, 0x80);IOWR_ALTERA_AVALON_UART_STATUS(UART_BASE, 0x0);IOWR_ALTERA_AVALON_UART_RXDATA(UART_BASE, 0x0);alt_irq_register(UART_IRQ,status_ptr,handle_uart_interrups); }static void handle_uart_interrups(void* context, alt_u32 id) {volatile char* status_ptr =(volatile char*)context;*status_ptr =IORD_ALTERA_AVALON_UART_STATUS(UART_BASE);if((IORD_ALTERA_AVALON_UART_STATUS(UART_BASE)&(0x80)) ==0x80) {ch =IORD_ALTERA_AVALON_UART_RXDATA(UART_BASE);queue[indexc] =ch;indexc++;}IOWR_ALTERA_AVALON_UART_STATUS(UART_BASE, 0x0);}。