PE-65967NL中文资料

- 格式:pdf

- 大小:121.97 KB

- 文档页数:4

增加强度掺AFFINITY-OG增加韧性LLDPE缠绕LLDPE膜缠绕LLDPE膜缠绕LLDPE膜缠绕LLDPE膜缠绕膜LLDPE缠绕膜LLDPE缠绕膜LLDPE缠绕膜LLDPE缠绕膜LLDPE (6c)薄膜级LLDPE薄膜级LLDPE缠绕膜LLDPE (6c)缠绕膜LLDPE (6c)缠绕膜LLDPE( 8C线性)茂金属茂金属茂金属茂金属茂金属茂金属茂金属茂金属缠绕茂金属膜缠绕茂金属膜缠绕茂金属膜缠绕膜茂金属(6c)缠绕膜茂金属缠绕膜茂金属茂金属缠绕膜茂金属茂金属茂金属茂金属茂金属茂金属茂金属茂金属烯超低密度聚乙烯超低密度聚乙烯POE弹性体PE弹性体PE弹性体PE弹性体PP弹性体弹性体弹性体薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE 薄膜级LLDPE 薄膜级LLDPE 薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE 薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE缠绕膜LLDPE缠绕膜LLDPE缠绕膜LLDPE缠绕膜LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE 薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE 薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE 薄膜级LLDPE薄膜级LLDPE薄膜级LLDPE 薄膜级LLDPE 薄膜级 LLDPE薄膜级 LLDPE 薄膜级 LLDPE 1820S1 印尼 薄膜级 LLDPE 201XV 福建联合 薄膜级 LLDPE 7087 科威特EQUATE 1 薄膜级 LLDPE 新加坡注塑级 LLDPE 注塑级 LLDPE 注塑LLDPE级注塑级LLDPE 注塑级 LLDPE 注塑级LLDPE注塑级LLDPE注塑级LLDPE 注塑级LLDPE 注塑级LLDPE 高压花料 挤出涂覆级LDPE 注塑级LDPELDPE注塑LDPE 级LDPE注塑LDPE 级LDPELDPELDPE 高压涂覆挤出LDPE 级涂覆LDPE 级涂覆LDPE 级涂覆LDPE 级注塑LDPE 级挤出LDPE 级挤出LDPE 级挤出级LDPELDPE高压薄膜LDPELDPELDPELDPE 高压重包装注塑级LDPELDPELDPELDPE 薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE 薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE 薄膜级LDPE 薄膜级LDPE薄膜级LDPE薄膜级LDPE薄膜级LDPE注塑级LDPE注塑级LDPE注塑级LDPE 注塑级LDPE注塑级LDPE注塑级LDPE注塑级LDPE注塑级LDPE注塑级LDPE涂覆级LDPE涂覆级LDPE涂覆级LDPE涂覆级LDPE 涂覆级LDPE涂覆级LDPE 涂覆级LDPE 涂覆级LDPE 涂覆级 LDPE 7008 美国陶氏 薄膜级 HDPE 薄膜HDPE级薄膜HDPE 级薄膜HDPE 级薄膜HDPE 级薄膜HDPE 级薄膜HDPE 级薄膜HDPE 级薄膜HDPE 级薄膜HDPE 级薄膜HDPE 级薄膜HDPE 级薄膜HDPE 级薄膜HDPE 级薄膜HDPE 级薄膜HDPE 级薄膜HDPE 级薄膜HDPE级 薄膜级HDPE薄膜级 HDPE 薄膜级 HDPE 薄膜级HDPE薄膜级HDPE 薄膜级HDPE注塑级HDPE 低压聚乙烯 MI :5属于低熔指 MI :10属于中熔指 MI :20属于高熔指注塑级HDPE 注塑级 HDPE 注塑级 HDPE 注塑HDPE级注塑HDPE 级注塑HDPE 级注塑HDPE 级注塑HDPE 级注塑HDPE 级注塑HDPE 级注塑HDPE 级注塑HDPE 级注塑级HDPE 注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE 注塑级HDPE注塑级HDPE注塑级HDPE注塑级HDPE拉丝级HDPE拉丝级HDPE拉丝级HDPE拉丝级HDPE拉丝级HDPE拉丝级HDPE拉丝级HDPE拉丝级HDPE拉丝级HDPE 拉丝级HDPE拉丝级HDPE拉丝级HDPE拉丝级HDPE拉丝级HDPE拉丝级HDPE中空级HDPE中空级HDPE中空级HDPE中空级HDPE中空级HDPE中空级HDPE中空级HDPE 中空HDPE级中空HDPE 级中空HDPE 级中空HDPE 级中空HDPE 级中空HDPE 级中空级HDPE中空级HDPE中空级HDPE中空级HDPE中空级HDPE中空级HDPE中空级HDPE中空级HDPE中空级HDPE中空级HDPE中空级HDPE中空级HDPE 中空级HDPE中空级HDPE 拉丝级PP拉丝级PP拉丝级 PP拉丝级PP拉丝级PP 拉丝级 PP 拉丝级 PP 拉丝级PP注塑级PP注塑级PP注塑级PP注塑级PP 注塑级PP 注塑级 PP 注塑级PP 注塑级PP。

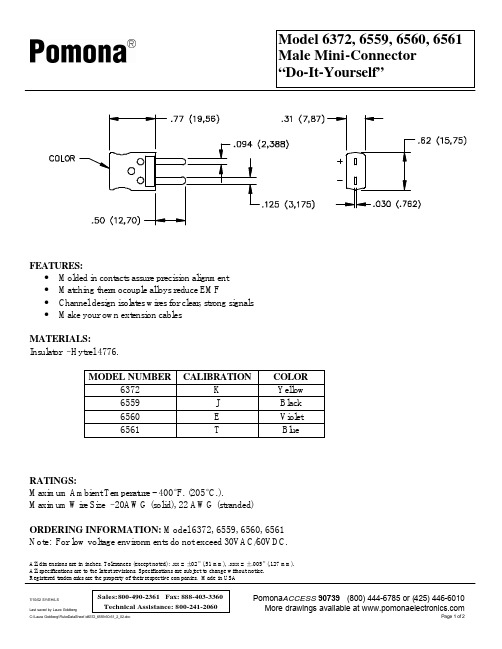

All dimensions are in inches. Tolerances (except noted): .xx = ±.02” (,51 mm), .xxx = ± .005” (,127 mm). All specifications are to the latest revisions. Specifications are subject to change without notice. Registered trademarks are the property of their respective companies. Made in USA“Do-It-Yourself”FEATURES:• Molded in contacts assure precision alignment • Matching thermocouple alloys reduce EMF• Channel design isolates wires for clear, strong signals • Make your own extension cablesMATERIALS:Insulator – Hytrel 4776.MODEL NUMBER CALIBRATION COLOR6372 K Yellow 6559 J Black 6560 E Violet 6561 T BlueRATINGS:Maximum Ambient Temperature - 400°F. (205°C.).Maximum Wire Size – 20AWG (solid), 22 AWG (stranded)ORDERING INFORMATION: Model 6372, 6559, 6560, 6561 Note: For low voltage environments do not exceed 30VAC/60VDC.All dimensions are in inches. Tolerances (except noted): .xx = ±.02” (,51 mm), .xxx = ± .005” (,127 mm). All specifications are to the latest revisions. Specifications are subject to change without notice. Registered trademarks are the property of their respective companies. Made in USA“Do-It-Yourself”ASSEMBLY INSTRUCTIONS1. Using a flat tip screwdriver, remove lid from connector.2. Cut back extension wire jacket (if applicable) 5/8”, strip back individual wires ¼”.3. Remove the elastomer strain relief from the connector. Insert wires into the strain relief until flush with the extensionwire outer jacket (5/8”).4. Loosen the two wire terminal screws (Approximately 3 ½ turns counter clockwise) using a small flat tipscrewdriver.5. Insert the stripped Red* wire under the (-) terminal screw, and the remaining wire under the (+) terminal screw.Tighten down the two terminal screws.6. Install the lid and tighten down the lid screw.*Color may vary outside of the USA.。

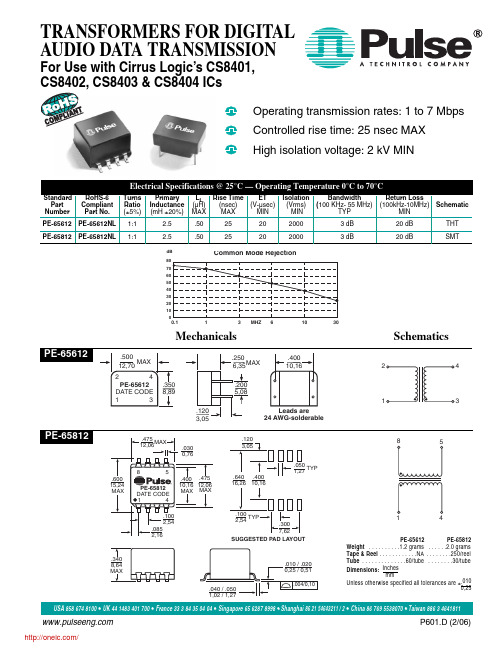

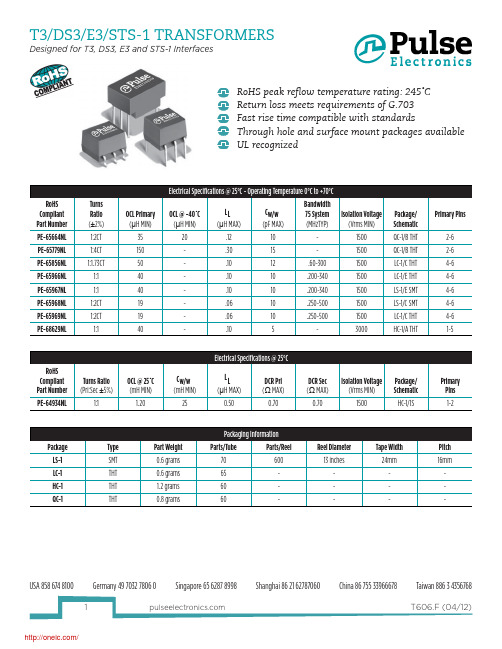

TRANSFORMERS FOR DIGITAL AUDIO DATA TRANSMISSIONFor Use with Cirrus Logic’s CS8401,MechanicalsSchematicsOperating transmission rates: 1 to 7 Mbps Controlled rise time: 25 nsec MAX High isolation voltage: 2 kV MINUSA 858 674 8100•UK 44 1483 401 700•France 33 3 84 35 04 04•Singapore 65 6287 8998•Shanghai 86 21 54643211 / 2•China 86 769 5538070•Taiwan 886 3 4641811P601.D (2/06)/TRANSFORMERS FOR DIGITAL AUDIO DATA TRANSMISSIONFor Use with Cirrus Logic’s CS8401, CS8402, CS8403 & CS8404 ICsThese transformers have been designed for use at the interface between line driver and receiver and the intercon-necting medium in Digital Audio Data Transmission Systems according to AES 3-199X or IEC 958. In such systems,two channels of periodically sampled and uniformly quantized audio signals are transmitted on a single shielded twisted pair.The electrical parameters of the interface are based on those of CCITT V.II or balanced voltage digital circuits which allow signal transmission up to a few hundred meters. The isolation transformers are essential in improving the balance of the transmitter and the receiver circuitry, and reducing common mode noise and EMI.These transformers are recommended for use with the Cirrus Logic CS8401, CS8402, CS8403 and CS8404“Digital Audio Interface Transmit Device.”The schematic below represents an implementation of transmit and receive circuits using isolation transformers at both ends. Equalization in the receiver may permit to increase the length of the interconnecting cable.ApplicationApplicable DocumentsAES 3-1985 (ANSI S4.40-1985), AES 3-199XDraft, IEC 958,CP-340, EBU 3250P601.D (2/06)For More Information:Pulse Worldwide Headquarters12220 World Trade Drive San Diego, CA 92128U.S.A. TEL:858 674 8100FAX:858 674 8262PulseNorthern Europe3 Huxley RoadSurrey Research Park Guildford, Surrey GU2 5RE United KingdomTEL:44 1483 401700FAX:44 1483 401701PulseSouthern EuropeZone Industrielle F-39270Orgelet FranceTEL:33 3 84 35 04 04FAX:33 3 84 25 46 41Pulse South Asia150 Kampong Ampat #07-01/02KA CentreSingapore 368324TEL:65 6287 8998FAX:65 6280 0080Pulse North AsiaNo. 26Kao Ching Road Yang Mei Chen Taoyuan Hsien Taiwan, R. O. C.TEL: 886 3 4641811FAX: 886 3 4641911Pulse China Headquarters No. 1Industrial District Changan, Dongguan ChinaTEL: 86 769 5538070FAX: 86 769 5538870Performance warranty of products offered on this data sheet is limited to the parameters specified. Data is subject to change without notice. Other brand and product names mentioned herein may be trademarks or registered trademarks of their respective owners.© Copyright, 2006. Pulse Engineering, Inc. All rights reserved.Pulse North China Room 1503XinYin BuildingNo. 888 YiShan Road Shanghai 200233ChinaTEL: 86 21 54643211/2FAX: 86 21 54643210/分销商库存信息:PULSEPE-65812NLT PE-65612NL PE-65812NL。

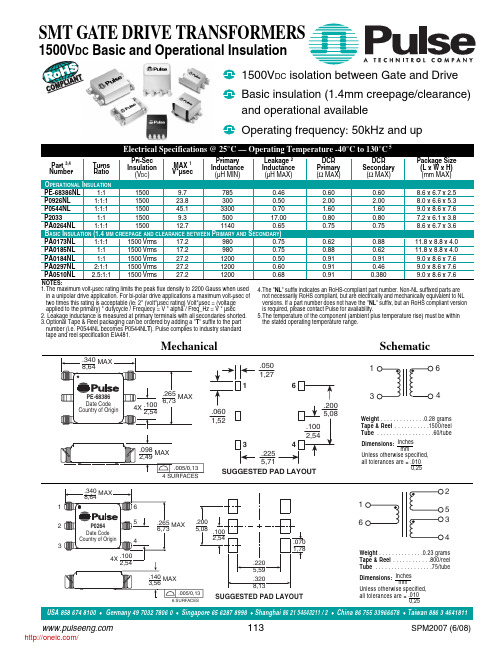

1500V Basic and Operational InsulationElectrical Specifications @ 25°C — Operating Temperature -40°C to 130°C1.The maximum volt-µsec rating limits the peak flux density to 2200 Gauss when usedin a unipolar drive application. For bi-polar drive applications a maximum volt-µsec oftwo times this rating is acceptable (ie: 2* (volt*µsec rating) Volt*µsec = (voltageapplied to the primary) * dutycycle / Frequecy = V * alpha / Freq_Hz = V * µsec2. Leakage inductance is measured at primary terminals with all secondaries shorted.3.Optional Tape & Reel packaging can be ordered by adding a "T" suffix to the partnumber (i.e. P0544NL becomes P0544NL T). Pulse complies to industry standardtape and reel specification EIA481.4.The "NL" suffix indicates an RoHS-compliant part number. Non-NL suffixed parts arenot necessarily RoHS compliant, but are electrically and mechanically equivalent to NLversions. If a part number does not have the "NL" suffix, but an RoHS compliant versionis required, please contact Pulse for availability.5.The temperature of the component (ambient plus temperature rise) must be withinthe stated operating temperature range.1500VBasic insulation (1.4mm creepage/clearance)and operational availableOperating frequency: 50kHz and up16321Dimensions:InchesmmUnless otherwise specified,all tolerances are ±.0100,25Weight . . . . . . . . . . . . . .0.23 gramsTape & Reel . . . . . . . . . . . .800/reelTube . . . . . . . . . . . . . . . . . .75/tubeSUGGESTED PAD LAYOUTWeight . . . . . . . . . . . . . .0.48 grams Tape & Reel . . . . . . . . . . . .900/reel Tube . . . . . . . . . . . . . . . . . .60/tubeSMT GATE DRIVE TRANSFORMERS1500V DC Basic and Operational InsulationMechanicalsSchematics162534Weight . . . . . . . . . . . . . .0.48 grams Tape & Reel . . . . . . . . . . .1000/reel Tube . . . . . . . . . . . . . . . . . .80/tube Dimensions:InchesmmUnless otherwise specified, all tolerances are ±.0100,258147Dimensions:InchesmmUnless otherwise specified,all tolerances are ±.0100,25Weight . . . . . . . . . . . . . .0.29 grams Tape & Reel . . . . . . . . . . .1200/reel Tube . . . . . . . . . . . . . . . . . .80/tube 16PA 0130Dimensions:InchesmmUnless otherwise specified, all tolerances are ±.0100,25分销商库存信息:PULSEPE-68386NLT PA0264NLT PA0185NLT PA0184NLT PE-68386NL P0544NLP0544NLT PA0173NLT P0926NL。

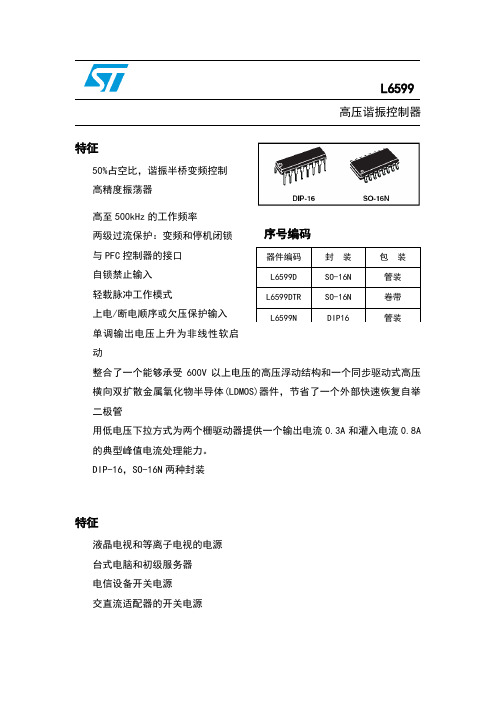

L6599高压谐振控制器特征50%占空比,谐振半桥变频控制 高精度振荡器高至500kHz 的工作频率 两级过流保护:变频和停机闭锁 与PFC 控制器的接口 自锁禁止输入 轻载脉冲工作模式上电/断电顺序或欠压保护输入 单调输出电压上升为非线性软启动整合了一个能够承受600V 以上电压的高压浮动结构和一个同步驱动式高压横向双扩散金属氧化物半导体(LDMOS)器件,节省了一个外部快速恢复自举二极管用低电压下拉方式为两个栅驱动器提供一个输出电流0.3A 和灌入电流0.8A 的典型峰值电流处理能力。

DIP-16,SO-16N 两种封装特征液晶电视和等离子电视的电源 台式电脑和初级服务器 电信设备开关电源 交直流适配器的开关电源序号编码器件编码 封 装 包 装 L6599D SO-16N 管装 L6599DTR SO-16N 卷带 L6599NDIP16管装框图目录1 驱动描述 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42 引脚设置 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5引脚排列 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5引脚功能说明 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53 典型系统框图 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74 电气数据 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7极限参数 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7热相关数据 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85 电气参数 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96 典型的电气性能 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127 应用资料 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15振荡器 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16工作在空载或非常轻的负载状态 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18软启动 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21电流检测,过流保护和过载保护 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23闭锁关机 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26LINE检测功能 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27自举部分 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . .28应用实例 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .298 封装外形尺寸 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 修订记录 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 驱动描述L6599是一个用于谐振半桥拓扑电路的精确的双端控制器。

áçXRT7300E3/DS3/STS-1 LINE INTERFACE UNIT FEBRUARY 2002REV. 1.1.1GENERAL DESCRIPTIONThe XRT7300 DS3/E3/STS-1 Line Interface Unit is designed to be used in DS3, E3 or SONET STS-1 ap-plications and consists of a line transmitter and re-ceiver integrated on a single chip.XRT7300 can be configured to support the E3 (34.368 Mbps), DS3 (44.736 Mbps) or the SONET STS-1 (51.84 Mbps) rates.In the transmit direction, the XRT7300 encodes input data to either B3ZS (for DS3/STS-1 applications) or HDB3 (for E3 applications) format and converts the data into the appropriate pulse shapes for transmis-sion over coaxial cable via a 1:1 transformer.In the receive direction the XRT7300 performs equal-ization on incoming signals, performs Clock Recov-ery, decodes data from either B3ZS or HDB3 format, converts the receive data into TTL/CMOS format, checks for LOS or LOL conditions and detects and declares the occurrence of line code violations.The XRT7300 also contains a 4-Wire Microprocessor Serial Interface for accessing the on-chip Command registers.FEATURES•Meets E3/DS3/STS-1 Jitter T olerance Require-ments•Full Loop-Back Capability•T ransmit and Receive Power Down Modes•Full Redundancy Support•Contains a 4-Wire Microprocessor Serial Interface •Uses Minimum External components•Requires Single +5V Power Supply•-40°C to +85°C Operating T emperature Range •Available in a 44 pin TQFP package APPLICATIONS•Interfaces to E3, DS3 or SONET STS-1 Networks •CSU/DSU Equipment•PCM T est Equipment•Fiber Optic T erminals•MultiplexersN OTE: This Device is Protected by US Patent # 6,157,270F IGURE 1. B LOCK D IAGRAM OF THE XRT7300元器件交易网Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 • XRT7300áçE3/DS3/STS-1 LINE INTERFACE UNITREV. 1.1.12ORDERING INFORMATIONP ART N UMBER P ACKAGE T YPEO PERATING T EMPERATURE R ANGEXRT7300IV44 Pin TQFP (10mm x 10mm)-40°C to +85°CF IGURE 2. P IN O UT OF THE XRT7300 IN THE 44 P IN TQFPáçE3/DS3/STS-1 LINE INTERFACE UNIT XRT7300REV. 1.1.1TABLE OF CONTENTSGeneral description (1)FEATURES (1)APPLICATIONS (1)Figure 1.Block Diagram of the XRT7300 (1)Ordering Information (2)Figure 2.Pin Out of the XRT7300 in the 44 Pin TQFP (2)TABLE OF CONTENTS (I)Pin Description (3)Electrical Characteristics (10)DC ELECTRICAL CHARACTERISTICS (TA = 25°C, VDD = 5.0V + 5%, UNLESS OTHERWISE SPECI-FIED) (10)AC ELECTRICAL CHARACTERISTICS (TA = 25°C, VDD = 5.0V + 5%, UNLESS OTHERWISE SPECI-FIED) (10)Figure 3.Timing Diagram of the Transmit Terminal Input Interface (11)Figure 4.Timing Diagram of the Receive Terminal Output Interface (11)AC ELECTRICAL CHARACTERISTICS (CONTINUED) (TA = 25°C, VDD = 5.0V + 5%, UNLESS OTHER-WISE SPECIFIED) (12)AC ELECTRICAL CHARACTERISTICS (CONTINUED) (TA = 25°C, VDD = 5.0V + 5%, UNLESS OTHER-WISE SPECIFIED) (13)ABSOLUTE MAXIMUM RATINGS (14)Figure 5.Transmit Pulse Amplitude Test Circuit for DS3, E3 and STS-1 Rates (15)Figure 6.ITU-T G.703 Transmit Output Pulse Template for E3 Applications (15)Figure 7.Bellcore GR-499-CORE Transmit Output Pulse Template for DS3 Applications (16)Figure 8.Bellcore GR-253-CORE Transmit Output Pulse Template for SONET STS-1 Applications (16)MICROPROCESSOR SERIAL INTERFACE TIMING (SEE FIGURE9) (17)Figure 9.Timing Diagram for the Microprocessor Serial Interface (17)System Description (18)THE TRANSMIT SECTION (18)THE RECEIVE SECTION (18)THE MICROPROCESSOR SERIAL INTERFACE (18)Table 1:Role of Microprocessor Serial Interface pins when the XRT7300 is operating in the Hardware Mode18 1.0 SELECTING THE DATA RATE (19)Table 2:Selecting the Data Rate for the XRT7300 via the E3 and STS-1/DS3 input pins (Hardware Mode) (19)COMMAND REGISTER CR4 (ADDRESS = 0X04) (19)Table 3:Selecting the Data Rate for the XRT7300 Via the STS-1/DS3 and the E3 Bit-fields Within Command Register CR4 (HOST Mode) (19)2.0 THE TRANSMIT SECTION (20)2.1 T HE T RANSMIT L OGIC B LOCK (20)Figure 10.The Typical Interface for the Transmission of Data in a Dual-Rail Format From the Transmitting Ter-minal Equipment to the Transmit Section of the XRT7300 (20)Figure 11.How the XRT7300 Samples the Data on the TPDATA and TNDATA Input Pins (20)Accepting Single-Rail Data from the Terminal Equipment (21)COMMAND REGISTER CR1 (ADDRESS = 0X01) (21)Figure 12.The Behavior of the TPDATA and TCLK Input Signals While the Transmit Logic Block is Accepting Single-Rail Data From the Terminal Equipment (21)IXRT7300E3/DS3/STS-1 LINE INTERFACE UNITáçREV. 1.1.12.2 T HE T RANSMIT C LOCK D UTY C YCLE A DJUST C IRCUITRY (21)2.3 T HE HDB3/B3ZS E NCODER B LOCK (22)B3ZS Encoding (22)Figure 13.An Example of B3ZS Encoding (22)HDB3 Encoding (22)Figure 14.An Example of HDB3 Encoding (23)Enabling/Disabling the HDB3/B3ZS Encoder (23)2.4 T HE T RANSMIT P ULSE S HAPER C IRCUITRY (23)COMMAND REGISTER CR2 (ADDRESS = 0X02 (23)Enabling the Transmit Line Build-Out Circuit (23)Disabling the Transmit Line Build-Out Circuit (23)COMMAND REGISTER CR1 (ADDRESS = 0X01) (23)Design Guideline for Setting the Transmit Line Build-Out Circuit (24)COMMAND REGISTER CR1 (ADDRESS = 0X01) (24)The Transmit Line Build-Out Circuit and E3 Applications (24)2.5 I NTERFACING THE T RANSMIT S ECTION OF THE XRT7300 TO THE L INE (24)Figure 15.Recommended Schematic for Interfacing the Transmit Section of the XRT7300 to the Line (24)TRANSFORMER RECOMMENDATIONS (25)3.0 THE RECEIVE SECTION (25)3.1 I NTERFACING THE R ECEIVE S ECTION OF THE XRT7300 TO THE L INE (25)Figure 16.Recommended Schematic for Interfacing the Receive Section of the XRT7300 to the Line (Transform-er-Coupling) (26)Figure 17.Recommended Schematic for Interfacing the Receive Section of the XRT7300 to the Line (Capaci-tive-Coupling) (26)3.2 T HE R ECEIVE E QUALIZER B LOCK (26)Figure 18. The Typical Application for the System Installer (27)COMMAND REGISTER CR2 (ADDRESS = 0X02) (28)3.3 P EAK D ETECTOR AND S LICER (28)3.4 C LOCK R ECOVERY PLL (28)3.5 T HE HDB3/B3ZS D ECODER (28)B3ZS Decoding DS3/STS-1 Applications (29)Figure 19.An Example of B3ZS Decoding (29)HDB3 Decoding E3 Applications (29)Figure 20.An Example of HDB3 Decoding (29)Enabling/Disabling the HDB3/B3ZS Decoder (30)3.6 LOS D ECLARATION/C LEARANCE (30)COMMAND REGISTER CR2 (ADDRESS = 0X02) (30)The LOS Declaration/Clearance Criteria for E3 Applications (30)Figure 21.The Signal Levels that the XRT7300 Declares and Clears LOS (E3 Mode Only) (31)Figure 22.The Behavior the LOS Output Indicator In Response to the Loss of Signal and the Restoration of Sig-nal (31)The LOS Declaration/Clearance Criteria for DS3 and STS-1 Applications (32)Table 4:The ALOS Declaration and Clearance Thresholds for a Given Setting of LOSTHR (DS3 and STS-1 Ap-plications) for Equalizer Enabled or Disabled (32)COMMAND REGISTER CR0 (ADDRESS = 0X00) (32)COMMAND REGISTER CR2 (ADDRESS = 0X02) (33)COMMAND REGISTER CR0 (ADDRESS = 0X00) (33)IIáçE3/DS3/STS-1 LINE INTERFACE UNIT XRT7300REV. 1.1.1COMMAND REGISTER CR2 (ADDRESS = 0X02) (33)Muting the Recovered Data while the LOS is being Declared (33)3.7 R OUTING THE R ECOVERED T IMING AND D ATA I NFORMATION TO THE R ECEIVING T ERMINAL E QUIPMENT (33)COMMAND REGISTER CR3 (ADDRESS = 0X03) (33)Figure 23. The Typical Interface for the Transmission of Data in a Dual-Rail Format From the Receive Section of the XRT7300 to the Receiving Terminal Equipment (34)Figure 24. How the XRT7300 Outputs Data on the RPOS and RNEG Output Pins (34)Figure 25.The Behavior of the RPOS, RNEG and RCLK1 Signals When RCLK1 is Inverted (35)Routing Single-Rail Format data (Binary Data Stream) to the Receive Terminal Equipment (35)COMMAND REGISTER CR3 (ADDRESS = 0X03) (35)COMMAND REGISTER CR3 (ADDRESS = 0X03) (35)Figure 26.The Typical Interface for the Transmission of Data in a Single-Rail Format From the Receive Section of the XRT7300 to the Receiving Terminal Equipment (36)Figure 27.The Behavior of the RPOS and RCLK1 Output Signals While the XRT7300 is Transmitting Single-Rail Data to the Receiving Terminal Equipment (36)4.0 DIAGNOSTIC FEATURES OF THE XRT7300 (36)4.1 T HE A NALOG L OCAL L OOP-B ACK M ODE (36)Figure 28.The Analog Local Loop-Back in the XRT7300 (37)COMMAND REGISTER CR4 (ADDRESS = 0X04) (37)4.2 T HE D IGITAL L OCAL L OOP-B ACK M ODE (37)Figure 29.The Digital Local Loop-Back path in the XRT7300 (38)COMMAND REGISTER CR4 (ADDRESS = 0X04) (38)4.3 T HE R EMOTE L OOP-B ACK M ODE (38)Figure 30.The Remote Loop-Back Path in the XRT7300 (39)COMMAND REGISTER CR4 (ADDRESS = 0X04) (39)4.4 TXOFF F EATURES (40)COMMAND REGISTER CR1 (ADDRESS = 0X01) (40)4.5 T HE T RANSMIT D RIVE M ONITOR F EATURES (40)Figure 31.The XRT7300 Employing the Transmit Drive Monitor Features (40)Figure 32. Two LIU’s, Each Monitoring the Transmit Output Signal of the Other LIU IC (41)4.6 T HE TAOS (T RANSMIT A LL O NE S) F EATURE (41)COMMAND REGISTER CR1 (ADDRESS = 0X01) (41)5.0 THE MICROPROCESSOR SERIAL INTERFACE (42)5.1 D ESCRIPTION OF THE C OMMAND R EGISTERS (42)Table 5:Addresses and Bit Formats of XRT7300 Command Registers (42)DESCRIPTION OF BIT-FIELDS FOR EACH COMMAND REGISTER (42)Command Register - CR0 (42)Command Register - CR1 (43)Command Register - CR2 (44)Command Register - CR3 (44)Command Register - CR4 (45)5.2 O PERATING THE M ICROPROCESSOR S ERIAL I NTERFACE (45)Table 6:Loop-Back Modes (45)Figure 33.Microprocessor Serial Interface Data Structure (46)Figure 34. How to Interface the XRT7300 IC to the XRT7234/45 E3/DS3 ATM UNI IC (47)Figure 35.How to Interface the XRT7300 IC to the XRT7250 DS3/E3 Framer IC (48)ORDERING INFORMATION (49)Package Dimensions (49)IIIXRT7300E3/DS3/STS-1 LINE INTERFACE UNITáçREV. 1.1.1REVISION HISTORY (50)IVáçXRT7300E3/DS3/STS-1 LINE INTERFACE UNITREV. 1.1.13PIN DESCRIPTIONPIN DESCRIPTIONP IN#S YMBOLT YPE D ESCRIPTION1TXLEVITransmit Line Build-Out Enable/Disable Select:This input pin is used to enable or disable the T ransmit Line Build-Out circuit in the XRT7300.Setting this pin to “High” disables the Line Build-Out circuit. In this mode, the XRT7300 outputs partially shaped pulses onto the line via the TTIP and TRING output pins.Setting this pin to “Low” enables the Line Build-Out circuit. In this mode, the XRT7300 outputs partially-shaped pulses onto the line via the TTIP and TRING output pins.T o comply with the isolated DSX-3/STSX-1 Pulse T emplate Requirements per Bellcore GR-499-Core or Bellcore GR-253-Core:1. Set this input pin to a "1" if the cable length between the Cross-Connect and the transmit output of the XRT7300 is greater than 225 feet.2. Set this input pin to a "0" if the cable length between the Cross-Connect and the transmit output of the XRT7300 is less than 225 feet.This pin is active only if both of the following are true:(a) The XRT7300 is configured to operate in either the DS3 or SONET STS-1 modes and(b) The XRT7300 is configured to operate in the Hardware Mode.N OTE : This pin should be tied to GND if the XRT7300 is to be operated in the HOST mode.2T AOS ITransmit All Ones Select:A “High” on this pin causes a continuous AMI all “1’s” pattern to be transmitted onto the line. The frequency of this “1’s” pattern is determined by TCLK.N OTES :1.This input pin is ignored if the XRT7300 is operating in the HOST Mode.2.Tie this pin to GND if the XRT7300 is going to be operating in the HOST Mode.3VDD ****Transmit Digital Power Supply4DMOODrive Monitor Output:If no transmitted AMI signal is present on MTIP and MRING input pins for 128±32 TCLK periods, then the DMO pin toggles and remains “High” until the next AMI signal is detected.5GND ****Transmit Digital GND 6GND ****Analog GND (Substrate)7GND****Receive Analog GND8RTIPIReceive TIP Input:This input pin along with RRING is used to receive the line signal from the Remote DS3/E3/STS-1 T erminal.9RRING IReceive RING Input:This input pin along with RTIP is used to receive the line signal from the Remote DS3/E3/STS-1 T erminal.10VDD ****Receive Analog VDDXRT7300áçE3/DS3/STS-1 LINE INTERFACE UNITREV. 1.1.1411REGRESET/(RCLK2INV)IRegister Reset Input pin (Invert RCLK2 Output - Select):The function of this pin depends upon whether the XRT7300 is operating in the HOST Mode or in the Hardware Mode.HOST Mode - Register Reset Input pin:Setting this input pin “Low” causes the XRT7300 to reset the contents of the Command Registers to their default settings and operating configuration. This pin is internally pulled “High”.Hardware Mode - Invert RCLK2 Output Select:Setting this input pin “Low” configures the Receive Section of the XRT7300 to output the recovered data via the RPOS and RNEG output pins on the rising edge of the RCLK2 output signal.Setting this input pin “High” configures the Receive Section to output the recov-ered data on the falling edge of the RCLK2 output signal.12REQDIS IReceive Equalization Disable Input:Setting this input pin “High” disables the Internal Receive Equalizer in the XRT7300. Setting this pin “Low” enables the Internal Receive Equalizer. The guidelines for enabling and disabling the Receive Equalizer are described in Section 3.2.N OTES :1.This input pin is ignored if the XRT7300 is operating in the HOST Mode.2.Tie this pin to GND if the XRT7300 is going to be operating in the HOST Mode.13LOSTHR ILoss of Signal Threshold Control:The voltage forced on this pin controls the input loss of signal (LOS) threshold. T wo settings are provided by forcing this signal to either GND or VDD. N OTE : This pin is only applicable during DS3 or STS-1 operations.14LLB ILocal Loop-Back Select:This input pin along with RLB dictates which Loop-Back mode the XRT7300 is operating in.A “High” on this pin with RLB being set to “Low” configures the XRT7300 to oper-ate in the Analog Local Loop-Back Mode.A “High” on this pin with RLB also being set to “High” configures the XRT7300 to operate in the Digital Local Loop-Back Mode.N OTES :1.This input pin is ignored if the XRT7300 is operating in the HOST Mode.2.Tie this pin to GND if the XRT7300 is going to be operating in the HOST Mode.15RLB IRemote Loop-Back Select:This input pin along with LLB dictates which Loop-Back mode the XRT7300 is be operating in.A “High” on this pin with LLB being set to “Low” configures the XRT7300 to oper-ate in the Remote Loop-Back Mode.A “High” on this pin with LLB also being set to “High” configures the XRT7300 to operate in the Digital Local Loop-Back Mode.N OTES :1.This input pin is ignored if the XRT7300 is operating in the HOST Mode.2.Tie this pin to GND if the XRT7300 is going to be operating in the HOST Mode.PIN DESCRIPTIONP IN#S YMBOL T YPE D ESCRIPTIONáçXRT7300E3/DS3/STS-1 LINE INTERFACE UNITREV. 1.1.1516STS-1/DS3ISTS-1/DS3 Select Input:A “High” on this pin configures the Clock Recovery Phase Locked Loop to set its VCO Center frequency to around 51.84 MHz (optimal for SONET STS-1 opera-tions). A “Low” on this pin configures the Clock Recovery Phase Locked Loop to set its VCO Center frequency to around 44.736 MHz (optimal for DS3 opera-tions).N OTES :1.The XRT7300 ignores this pin if the E3 pin (pin 17) is set to “1”.2.This input pin is ignored if the XRT7300 is operating in the HOST Mode.3.Tie this pin to GND if the XRT7300 is going to be operating in the HOST Mode.17E3IE3 Select Input:A “High” on this pin configures the XRT7300 to operate in the E3 Mode.A “Low” on this pin configures the XRT7300 to check the state of the STS-1/DS3 input pin.N OTES :1.This input pin is ignored if the XRT7300 is operating in the HOST Mode.2.Tie this pin to GND if the XRT7300 is going to be operating in the HOST Mode.18HOST/HW IHOST/HW Mode Select:This input pin is used to enable or disable the Microprocessor Serial Interface (e.g., consisting of the SDI, SDO, SCLK, CS and REGRESET pins).Setting this input pin “High” enables the Microprocessor Serial Interface (e.g. configures the XRT7300 to operate in the HOST Mode). In this mode, theXRT7300 is configured by writing data into the on-chip Command Registers via the Microprocessor Serial Interface. When the XRT7300 is operating in the HOST Mode, it ignores the states of many of the discrete input pins.Setting this input pin “Low” disables the Microprocessor Serial Interface (e.g., configures the XRT7300 to operate in the Hardware Mode). In this mode, many of the external input control pins are functional.19SDI/(LOSMUTEN)ISerial Data Input for the Microprocessor Serial Interface (HOST Mode) or MUTE-upon-LOS Enable Input (Hardware Mode):The function of this input pin depends upon whether the XRT7300 is operating in the HOST or the Hardware Mode.Serial Data Input for the Microprocessor Serial Interface (HOST Mode):This pin is used to read or write data into the Command Registers of the Micro-processor Serial Interface. The Read/Write bit, the Address Values of the Com-mand Registers and Data Value to be written during Write Operations are applied to this pin.This input is sampled on the rising edge of the SCLK pin (pin 21).MUTE-upon-LOS Enable Input (Hardware Mode):When in the Hardware Mode, this input pin is used to configure the XRT7300 to MUTE the recovered data via the RPOS and RNEG output pins whenever it declares an LOS condition.Setting this input pin “High” configures the XRT7300 to automatically pull the RPOS and RNEG output pins to GND whenever it is declaring an LOS condition, thereby MUTing the data being output to the T erminal Equipment.Setting this input pin “Low” configures the XRT7300 to NOT automatically MUTE the recovered data whenever an LOS condition is declared.PIN DESCRIPTIONP IN#S YMBOL T YPE D ESCRIPTIONXRT7300áçE3/DS3/STS-1 LINE INTERFACE UNITREV. 1.1.1620SDO/(LCV)OSerial Data Output from the Controller Port/(Line Code Violation Output (LCV) Indicator.):The function of this input pin depends upon whether the XRT7300 is operating in the HOST or the Hardware Mode.HOST Mode - Microprocessor Serial Interface - Serial Data Output.This pin serially outputs the contents of the specified Command Register during Read Operations. The data on this pin is updated on the falling edge of the SCLK input signal. This pin is tri-stated upon completion of data transfer.Hardware Mode - Line Code Violation Output Indicator.This pin pulses “High” for one bit period any time the Receive Section of the XRT7300 detects a Line Code Violation in the incoming E3, DS3 or STS-1 Data Stream.21SCLK/(ENCO-DIS)IMicroprocessor Serial Interface Clock Signal/Encoder Disable:HOST Mode - Microprocessor Serial Interface Clock SignalThis signal is used to sample the data on the SDI pin on the rising edge of this signal. Additionally, during Read operations the Microprocessor Serial Interface updates the SDO output on the falling edge of this signal.Hardware Mode - B3ZS/HDB3 Encoder DisableSetting this input pin “High” disables the B3ZS/HDB3 Encoder and configures the XRT7300 to transmit the line signal in an AMI Format.Setting this input pin “Low” enables the B3ZS/HDB3 Encoder and configures the XRT7300 to transmit the line signal in the B3ZS format (for DS3/STS-1 opera-tion) or in the HDB3 format (for E3 operation).22CS/(DECODIS)IMicroprocessor Serial Interface - Chip Select/Decoder DisableThe function of this input pin depends upon whether the XRT7300 is operating in the HOST or the Hardware Mode.HOST Mode - Chip Select Input:The Local Microprocessor must assert this pin (e.g., set it to “0”) in order to enable communication with the XRT7300 via the Microprocessor Serial Inter-face.Hardware Mode - (B3ZS/HDB3 Decoder Disable)Setting this input pin “High” disables the B3ZS/HDB3 Decoder. Setting this input pin “Low” enables the B3ZS/HDB3 Decoder.23RLOL OReceive Loss of Lock Output IndicatorThis output pin toggles “High” if the XRT7300 has detected a Loss of Lock Con-dition. The XRT7300 declares an LOL (Loss of Lock) Condition if the recovered clock frequency deviates from the Reference Clock frequency (available at the EXCLK input pin) by more than 0.5%.24RLOS OReceive Loss of Signal Output IndicatorThis output pin toggles “High” if the XRT7300 has detected a Loss of Signal Condition in the incoming line signal.The criteria the XRT7300 uses to declare an LOS Condition depends upon whether the device is operating in the E3 or DS3/STS-1 Mode.25GND ****Digital GND 26VDD****Digital VDDPIN DESCRIPTIONP IN#S YMBOL T YPE D ESCRIPTIONPIN DESCRIPTIONP IN#S YMBOL T YPE D ESCRIPTION27EXCLK I External Reference Clock Input:Apply a 34.368MHz clock signal for E3 applications, a 44.736 MHz clock signalfor DS3 applications or a 51.84 MHz clock signal for SONET STS-1 applications.28GND****Receiver Digital Ground29VDD****Receiver Digital VDD30LCV/(RCLK2)O Line Code Violation Indicator/Receive Clock Output pin 2:The function of this pin depends upon whether the XRT7300 is operating in theHOST Mode, the Hardware Mode or User selection.HOST Mode - Line Code Violation Indicator Output:If the XRT7300 is configured to operate in the HOST Mode, then this pin func-tions as the LCV output pin by default. However, by using the on-chip CommandRegisters, this pin can be configured to function as the second Receive Clocksignal output pin (RCLK2).Hardware Mode - Receive Clock Output pin 2:This output pin is the Recovered Clock signal from the incoming line signal. Thereceive section of the XRT7300 outputs data via the RPOS and RNEG outputpins on the rising edge of this clock signal.N OTE: If the XRT7300 is operating in the HOST Mode and this pin is configuredto function as the additional Receive Clock signal output pin, then the XRT7300can be configured to update the data on the RPOS and RNEG output pins on thefalling edge of this clock signal.31RCLK1O Receive Clock Output pin 1:This output pin is the Recovered Clock signal from the incoming line signal. Thereceive section of the XRT7300 outputs data via the RPOS and RNEG outputpins on the rising edge of this clock signal.N OTE: If the XRT7300 device is operating in the “Host” Mode, then the user canconfigure the device to update the data on the RPOS and RNEG output pins onthe falling edge of this clock signal.32RNEG O Receive Negative Pulse Output:This output pin pulses “High” whenever the XRT7300 has received a NegativePolarity pulse in the incoming line signal at the RTIP/RRING inputs.N OTE: If the B3ZS/HDB3 Decoder is enabled, then the zero suppression pat-terns in the incoming line signal (such as: "00V", "000V", "B0V", "B00V") is notreflected at this output.33RPOS O Receive Positive Pulse Output:This output pin pulses “High” whenever the XRT7300 has received a PositivePolarity pulse in the incoming line signal at the RTIP/RRING inputs.N OTE: If the B3ZS/HDB3 Decoder is enabled, then the zero suppression pat-terns in the incoming line signal (such as: "00V", "000V", "B0V", "B00V") is notreflected at this output.34ICT I In-Circuit Test Input:Setting this pin “Low” causes all digital and analog outputs to go into a high-impedance state to allow for in-circuit testing. This pin is internally pulled “High”.PIN DESCRIPTIONP IN#S YMBOL T YPE D ESCRIPTION35TXOFF I Transmitter OFF Input:Setting this input pin “High” configures the XRT7300 to turn off the T ransmitter inthe device.N OTES:1.This input pin is ignored if the XRT7300 is operating in the HOST Mode.2.Tie this pin to GND if the XRT7300 is going to be operating in the HOSTMode.36TCLK I Transmit Clock Input for TPDATA and TNDATA:This input pin must be driven at 34.368 MHz for E3 applications, 44.736MHz forDS3 applications, or 51.84MHz for SONET STS-1 applications. The XRT7300uses this signal to sample the TPDA T A and TNDA T A input pins. By default, theXRT7300 is configured to sample these two pins on the falling edge of this sig-nal.If the XRT7300 is operating in the HOST Mode, then the device can be config-ured to sample the TPDA T A and TNDA T A input pins on the rising edge of TCLK.37TPDA T A I Transmit Positive Data Input:The XRT73L00 samples this pin on the falling edge of TCLK. If the device sam-ples a “1” at this input pin, then it generates and transmits a positive polaritypulse to the line.N OTES:1.The data should be applied to this input pin if the T ransmit Section isconfigured to accept Single-Rail data from the T erminal Equipment.2.If the XRT73L00 is operating in the HOST Mode, then the XRT73L00can be configured to sample the TPDA T A pin on either the rising or fall-ing edge of TCLK.38TNDA T A I Transmit Negative Data Input:The XRT7300 samples this pin on the falling edge of TCLK. If the device sam-ples a “1” at this input pin, then it generates and transmits a negative polaritypulse to the line.N OTES:1.This input pin is ignored and should be tied to GND if the T ransmit Sec-tion is configured to accept Single-Rail data from the T erminal Equip-ment.2.If the XRT7300 is operating in the HOST Mode, then the XRT7300 canbe configured to sample the TNDA T A pin on either the rising or fallingedge of TCLK.39GND-Transmit Analog Ground40TRING O Transmit TIP Output:The XRT7300 uses this pin, along with TTIP, to transmit a bipolar line signal via a1:1 transformer.41TTIP O Transmit RING Output:The XRT7300 uses this pin, along with TRING, to transmit a bipolar line signalvia a 1:1 transformer.42VDD-Transmit Analog Power SupplyPIN DESCRIPTIONP IN#S YMBOL T YPE D ESCRIPTION43MRING I Monitor Ring Input:The bipolar line output signal from TRING can be connected to this pin via a 270Ω resistor in order to check for line driver failure. This pin is internally pulled“High”.44MTIP I Monitor Tip Input:The bipolar line output signal from TTIP can be connected to this pin via a 270 Ωresistor in order to check for line driver failure. This pin is internally pulled “High”.ELECTRICAL CHARACTERISTICSDC ELECTRICAL CHARACTERISTICS (T A = 25°C, V DD = 5.0V + 5%, UNLESS OTHERWISE SPECIFIED) S YMBOL P ARAMETER M IN.T YP.M AX.U NITS V DDD DC Supply Voltage 4.755 5.25V V DDA DC Supply Voltage 4.755 5.25VI CC Supply Current (Measured while T ransmitting and Receiving all “1’s”)DS-3 Mode167200mASTS-1 Mode180220mA V IL Input Low Voltage0.8V V IH Input High Voltage 2.0VDD V V OL Output Low Voltage, IOUT = -4.0mA00.4V V OH Output High Voltage, IOUT = 4.0mA 2.8VDD VI L Input Leakage Current*±10mA * Not applicable to pins with pull-up/pull-down resistors.AC ELECTRICAL CHARACTERISTICS (T A = 25°C, V DD = 5.0V + 5%, UNLESS OTHERWISE SPECIFIED)S YMBOL P ARAMETER M IN.T YP.M AX.U NITS Terminal Side Timing Parameters (See Figure3 & Figure4)TCLK Clock Duty Cycle (DS3/STS-1)305070%TCLK Clock Duty Cycle (E3)305070%TCLK Frequency (SONET STS-1)51.84MHzTCLK Frequency (DS3)44.736MHzTCLK Frequency (E3)34.368MHz t RTX TCLK Clock Rise Time (10% to 90%)4ns t FTX TCLK Clock Fall Time (90% to 10%)4ns t TSU TPDA T A/TNDA T A to TCLK Falling Set up time3ns t THO TPDA T A/TNDA T A to TCLK Falling Hold time3ns t LCVO RCLK to rising edge of LCV output delay 2.5ns t TDY TTIP/TRING to TCLK Rising Propagation Delay time0.614ns RCLK Clock Duty Cycle455055%RCLK Frequency (SONET STS-1)51.84MHzRCLK Frequency (DS3)44.736MHzRCLK Frequency (E3)34.368MHz。

ASTM D6797中文标准一、概述ASTM D6797是美国材料和试验协会(ASTM)发布的一项关于塑料管材料抗压试验的标准。

该标准规定了使用静态加载机进行塑料管材料的短期和长期抗压性能测试的方法。

本文将对ASTM D6797标准的主要内容进行介绍和解析,希望对相关领域的专业人士和学习者有所帮助。

二、标准概述1. ASTM D6797标准的适用范围,包括了适用于聚乙烯和聚丙烯管材料的试验方法。

这些方法可以用于评估管材料在短期压缩和长期压缩周期下的性能。

2. 该标准规定了两种不同的试验方法,即静态压缩试验和长期压缩试验。

静态压缩试验是在规定的条件下进行单向或双向压缩试验,以确定材料在短期加载下的性能。

长期压缩试验则是在一定的压缩应力下进行长期持续时间的试验,以评估材料在长期加载下的性能。

3. 标准还规定了试验样品的制备、试验设备的选择和校准、试验条件的确定等方面的要求,以确保试验结果的可靠性和准确性。

三、试验方法1. 试验材料的制备根据ASTM D6797标准的要求,试验材料的制备应符合相关规范和标准。

试验样品的制备应包括材料的选择、切割、加工、标记等步骤,以确保试验样品的质量和代表性。

2. 静态压缩试验静态压缩试验是在规定的温度和湿度条件下进行的,可以分为单向和双向压缩试验。

试验过程中需记录材料的变形情况和压缩载荷,以评估材料的抗压性能。

3. 长期压缩试验长期压缩试验是在恒定的压缩应力下进行的,试验时间通常较长。

通过定期记录试验样品的变形情况和应力水平,可以评估材料在长期加载下的性能。

4. 试验结果的分析根据ASTM D6797标准的要求,对试验结果进行必要的处理和分析,包括计算材料的压缩模量、应力-应变曲线、残余变形率等指标,以评估材料的抗压性能。

四、设备和仪器ASTM D6797标准要求使用的设备和仪器应符合相关的标准和规范,包括静态加载机、试验夹具、测力传感器、位移传感器、温湿度控制设备等。