05_Altera_CPLD的资源优化

- 格式:ppt

- 大小:561.00 KB

- 文档页数:38

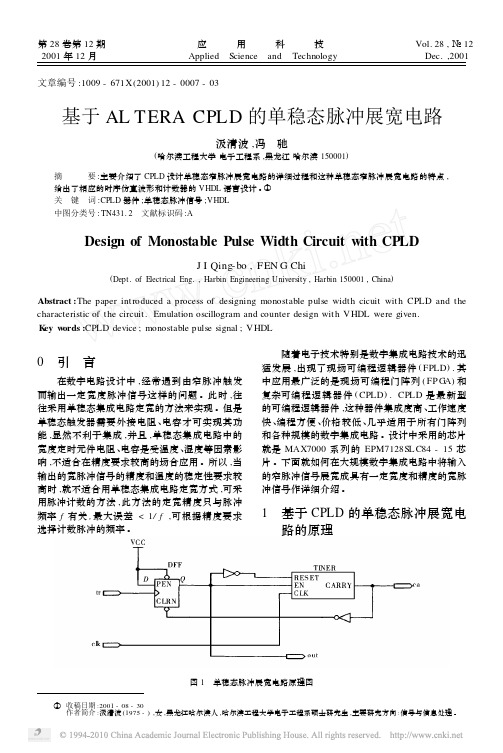

文章编号:1009-671X (2001)12-0007-03基于AL TERA CPLD 的单稳态脉冲展宽电路汲清波,冯 驰(哈尔滨工程大学电子工程系,黑龙江哈尔滨150001)摘 要:主要介绍了CPLD 设计单稳态窄脉冲展宽电路的详细过程和这种单稳态窄脉冲展宽电路的特点,给出了相应的时序仿真波形和计数器的VHDL 语言设计。

①关 键 词:CPLD 器件;单稳态脉冲信号;VHDL 中图分类号:TN431.2 文献标识码:ADesign of Monostable Pulse Width Circuit with CPLDJ I Qing-bo ,FEN G Chi(Dept.of Electrical Eng.,Harbin Engineering University ,Harbin 150001,China )Abstract :The paper introduced a process of designing monostable pulse width cicuit with CPLD and the characteristic of the circuit.Emulation oscillogram and counter design with V HDL were given.K ey w ords :CPLD device ;monostable pulse signal ;V HDL0 引 言在数字电路设计中,经常遇到由窄脉冲触发而输出一定宽度脉冲信号这样的问题。

此时,往往采用单稳态集成电路定宽的方法来实现。

但是单稳态触发器需要外接电阻、电容才可实现其功能,显然不利于集成,并且,单稳态集成电路中的宽度定时元件电阻、电容是受温度、湿度等因素影响,不适合在精度要求较高的场合应用。

所以,当输出的宽脉冲信号的精度和温度的稳定性要求较高时,就不适合用单稳态集成电路定宽方式,可采用脉冲计数的方法,此方法的定宽精度只与脉冲频率f 有关,最大误差<1/f ,可根据精度要求选择计数脉冲的频率。

Altera 公司 2010年12月3010Subscribe© 2010 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at /common/legal.html . Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.101 Innovation DriveSan Jose, CA Altera CPLD 的实时ISP 与ISP 钳位功能本应用笔记介绍了MAX ®II 和MAX V 器件的实时在系统编程(ISP)模式与ISP 钳位编程模式以及它们在Quartus ®II 软件,Jam ™ Standard Test and ProgrammingLanguage (STAPL) Player 和Jam STAPL Byte -Code Player 中的应用。

第21卷 第1期 吉 林 化 工 学 院 学 报Vol.21No.1 2004年3月JOURNAL OF J IL IN INSTITU TE OF CHEMICAL TECHNOLOGYMar. 2004收稿日期:2004-02-07作者简介:翟玉文(1965-),男,吉林市人,吉林化工学院教授,硕士,主要从事自动化仪表及计算机应用方面的研究. 文章编号:100722853(2004)0120082202基于AL TERA 的FP GA/CPLD 下载电路设计翟玉文1,董 萍2,杨 潇1,艾学忠1(1.吉林化工学院自动化系,吉林吉林132022;2.中国石油集团工程设计有限责任公司东北分公司,吉林吉林132002)摘要:介绍了AL TERA CPLD/FPG A 可编程逻辑器件在系统配置方法,给出了AL TERA MAX 和FL EX 系列器件的下载电路.关 键 词:复杂可编程逻辑器件;现场可编程门阵列;在系统配置;下载电路中图分类号:TN 47 文献标识码:A 可编程逻辑器件PLD 是允许用户编程(配置)实现所需逻辑功能的器件.目前大规模可编程逻辑器件已日趋广泛地应用于复杂数字系统的设计中,并以其具有在系统重构ISR 的特点,给设计的修改和系统升级带来极大方便.AL TERA 公司是世界最著名的可编程逻辑器件生产厂家之一,它的EDA 开发工具MAX +PL US II 及其MAX7000S 和FL EL10K 系列器件得到了广泛应用.本文介绍采用J TA G 接口标准模式的MAX 和FL EX 系列器件下载电路设计.1 MAX ,FL EX 系列器件下载电路(1)MAX 系列器件是AL TERA 公司的基于EEPROM 工艺的复杂可编程逻辑器件CPLD ,包括MAX9000、MAX7000A 、MAX7000B 、MAX7000S 、MAX7000、MAX5000、MAX3000A 和Classic 等系列.联合测试活动组织J TA G 开发了IEEE1149.1边界扫描测试BST 技术规范,用J TA G 接口作为下载接口,可以省去专用的编程接口,减少系统的引出线[1,2].图1以MAX7000S 为例给出了MAX 系列可编程逻辑器件的下载电路.J TA G 接口电路中使用了四根信号线:TDI ─—测试数据输入、TDO ─—测试数据输出、TMS ─—测试模式选择、TC K ─—测试时钟信号,对MAX 系列器件而言,TC K 、TMS 、TDI 是输入信号,TDO 是输出信号.利用MAX +PL US II 应用软件,在完成设计项目的编译后,生成的CPLD 下载文件以pof 为扩展名,经仿真正确后,就可通过下载电路对相应的器件进行ISP 在系统编程(下载).MAX 系列器件下载后具有非易失性.图1 MAX 系列器件下载电路(2)FL EX 系列器件是AL TERA 公司的基于SRAM 工艺的现场可编程门阵列FPG A (Field Pro 2grammable G ate Array )型可编程逻辑器件,包括FL EX10K 、FL EX10KE 、FL EX8000和FL EX6000等系列.图2以FL EX10K10为例给出了FL EX 系列可编程逻辑器件的下载电路.J TA G 接口电路中同样使用TC K 、TMS 、TDI 和TDO 四根信号线.基于SRAM 工艺的FP G A 器件由于配置数据存放于SRAM 中,系统掉电后将失去原有的逻辑功能,再次上电时需重新加载配置数据,所以这种下载电路的在系统配置方式适用于系统开发设计阶段.2 J TA G 下载接口与计算机并口的转换电路 J TA G 下载接口与计算机并口之间的转换连接如图3所示.电路采用J TA G 接口标准,通过并图2 FL EX 系列器件下载电路口下载电缆ByteBlaster (MV )采用J TA G 模式进行在系统编程(下载).25针D 型插座与计算机并口相连,10针插座(J TA G 接口)连接到用户下载板上,25针插座与10针插座之间是由74L S244组成的变换电路,用来提高信号驱动能力,将计算机并口送出的信息经缓冲后传送到下载板,同时将器件配置过程中送出的信息送给计算机,以使计算机与被配置的AL TERA 可编程器件之间进行信息交换.该转换电路可制作放置于25针D 型插座盒内.图3 J TA G 下载接口与计算机并口的转换连接3 FP GA 非易失在系统配置方法基于EEPROM 结构的CPLD 器件具有非易失性,配置后其内容长期驻留在芯片内,可直接应用于实际系统中.但由于CPLD 芯片的规模较小(可用门数小于2万门),在复杂的大型数字系统中,基于SRAM 工艺的FP G A 器件具有更广泛的应用前景.对于已经设计完的FP G A 应用系统,如果每次掉电都通过计算机下载配置将很不方便,系统上电后能自动加载配置对FP G A 的应用是必须的.实现自动配置主要有主动串行配置(AS )和被动配置(PS 、PPA 或PPS )方式.AL 2TERA 的串行ROM 型EPC 器件是AS 方式的专用配置器件,包括O TP (一次可编程,如EPC1)和多次可编程(如EPC2)两种.单片机可用于被动配置方式中对FP G A 进行配置.参考文献:[1] 赵曙光,郭万有,杨颂华.可编程逻辑器件原理、开发与应用[J ].西安:西安电子科技大学出版社,2000.[2] 潘松,黄继业.EDA 技术实用教程[J ].北京:科学出版社,2002.[3] 何伟,唐仁圣,张玲.FPG A/CPLD 可编程逻辑器件的在系统配置方法[J ].重庆大学学报,2003,(5):125-128.[4] 杨刚,杨霏.用单片机配置CPLD 器件[J ].电子设计应用,2002,(11):49-51Design of the dow nload circuit based on AL TERA FPGA/CPLDZHA I Yu 2wen 1,DON G Ping 2,YAN G Xiao 1,A I Xue 2zhong 1(1.Dept.of Automation ,Jilin Institute of Chemical Technology ,Jilin City 132022,China ;2.Northeast Branch Company of China Petroleum Engineering Design Co.L TD ,Jilin City 132002,China )Abstract :The method of the In 2System Reconfiguration based on AL TERA CPLD/FP G A is introduced.The download circuit for AL TERA MAX and FL EX is given.K ey w ords :CPLD ;FP G A ;ISR ;download circuit38 第1期翟玉文,等:基于AL TERA 的FPGA/CPLD 下载电路设计 。

ALTERA CPLD器件的配置与下载一、配置方式ALTERA CPLD器件的配置方式主要分为两大类:主动配置方式和被动方式。

主动配置方式由CPLD器件引导配置操作过程,它控制着外部存储器和初始化过程;而被动配置方式由外部计算机或控制器控制配置过程。

根据数据线的多少又可以将CPLD器件配置方式分为并行配置和串行配置两类。

经过不同组合就得到四种配置方式:主动串行配置(AS)、被动串行(PS)、被动并行同步(PPS)、被动并行异步(PPA)。

我们没有必要对每一种配置方式都进行讲述,而是详细地来讲讲我们实验室中经常使用的方式:被动串行配置方式(PS)。

以FLEX10K器件为例,我们首先对PS方式中使用到的引脚有个了解,它的主要配置引脚如下:MSEL1、MSEL0:输入;接地。

nSTATUS:双向漏极开路;命令状态下器件的状态输出。

加电后,FLEX10K立即驱动该引脚到低电位,然后在100ms内释放掉它,nSTATUS必须经过1.0k电阻上拉到Vcc,如果配置中发生错误,FLEX10K将其拉低。

nCONFIG:输入;配置控制输入。

低电位使FLEX10K器件复位,在由低到高的跳变过程中启动配置。

CONF_DONE:双向漏极开路;状态输出。

在配置期间,FLEX10K将其驱动为低。

所有配置数据无误差接收后,FLEX10K将其置为三态,由于有上拉电阻,所以将变为高电平,表示配置成功。

状态输入。

输入高电位引导器件执行初始化过程并进入用户状态。

CONF_DONE 必须经过1.0k电阻上拉到Vcc,而且可以将外电路驱动为低以延时FLEX10K初始化过程。

DCLK:输入;为外部数据源提供时钟。

nCE:输入;FLEX10K器件使能输入,nCE为低时使能配置过程,而且为单片配置时,nCE必须始终为低。

nCEO:输出(专用于多片器件);FLEX10K配置完成后,输出为低。

在多片级联配置时,驱动下一片的nCE端。

DATA0:输入;数据输入,在DATA0引脚上的一位配置数据。

《Altera FPGA/CPLD设计(高级篇)(第2版)》:Altera公司推荐FPGA/CPLD 培训教材。

目录第1章可编程逻辑设计指导原则1.1 可编程逻辑基本设计原则1.1.1 面积和速度的平衡与互换原则1.1.2 硬件原则1.1.3 系统原则1.1.4 同步设计原则1.2 可编程逻辑常用设计思想与技巧1.2.1 乒乓操作1.2.2 串并转换1.2.3 流水线操作1.2.4 异步时钟域数据同步1.3 altera推荐的coding style1.3.1 coding style的含义1.3.2 结构层次化编码(hierarchical coding)1.3.3 模块划分的技巧(design partitioning)1.3.4 组合逻辑的注意事项1.3.5 时钟设计的注意事项1.3.6 全局异步复位资源1.3.7 判断比较语句case和if...else的优先级1.3.8 使用pipelining技术优化时序1.3.9 模块复用与resource sharing1.3.10 逻辑复制1.3.11 香农扩展运算1.3.12 信号敏感表1.3.13 状态机设计的一般原则1.3.14 altera megafunction资源的使用1.3.15 三态信号的设计1.3.16 加法树的设计1.4 小结1.5 问题与思考第2章altera器件高级特性与应用2.1 时钟管理2.1.1 时序问题2.1.2 锁相环应用2.2 片内存储器2.2.1 ram的普通用法2.2.2 ram用做移位寄存器2.2.3 ram实现固定系数乘法2.3 数字信号处理2.3.1 dsp块资源2.3.2 工具支持2.3.3 典型应用2.4 片外高速存储器2.4.1 存储器简介2.4.2 zbt sram接口设计2.4.3 ddr sdram接口设计2.4.4 qdr sram接口设计2.4.5 ddr3、qdr ii+和rldram ii+2.4.6 软件支持和应用实例2.5 高速差分接口和dpa2.5.1 高速差分接口的需求2.5.2 器件的专用资源2.5.3 动态相位调整电路(dpa)2.5.4 软件支持和应用实例2.6 高速串行收发器2.7 小结2.8 问题与思考第3章logiclock设计方法3.1 logiclock设计方法简介3.1.1 logiclock设计方法的目标3.1.2 logiclock设计流程3.1.3 logiclock设计方法支持的器件族3.2 logiclock区域3.2.1 region的类型与常用属性值3.2.2 region的创建方法3.2.3 region的层次结构3.2.4 指定region的逻辑内容3.3 logiclock的约束注意事项3.3.1 约束优先级3.3.2 规划logiclock区域3.3.3 向logiclock区域中布置器件特性3.3.4 虚拟引脚(virtual pins)3.4 反标注布线信息3.4.1 导出反标注布线信息3.4.2 导入反标注布线信息3.5 logiclock设计方法支持的tcl scripts 3.6 quartus ii基于模块化的设计流程3.7 小结3.8 问题与思考第4章时序约束与时序分析4.1 时序约束与时序分析基础4.1.1 周期与最高频率4.1.2 利用quartus ii工具分析设计4.1.3 时钟建立时间4.1.4 时钟保持时间4.1.5 时钟输出延时4.1.6 引脚到引脚的延迟4.1.7 slack4.1.8 时钟偏斜4.1.9 quartus ii时序分析工具和优化向导4.2 设置时序约束的常用方法4.2.1 指定全局时序约束4.2.2 指定个别时钟约束4.3 高级时序分析4.3.1 时钟偏斜4.3.2 多时钟域4.3.3 多周期约束4.3.4 伪路径4.3.5 修正保持时间违例4.3.6 异步时钟域时序分析4.4 最小化时序分析4.5 使用tcl工具进行高级时序分析4.6 timequest简介4.7 小结4.8 问题与思考第5章设计优化5.1 解读设计5.1.1 内部时钟域5.1.2 多周期路径和伪路径5.1.3 i/o接口的时序要求5.1.4 平衡资源的使用5.2 设计优化的基本流程和首次编译5.2.1 设计优化基本流程5.2.2 首次编译的约束和设置5.2.3 查看编译报告5.3 资源利用优化5.3.1 设计代码优化5.3.2 资源重新分配5.3.3 解决互连资源紧张的问题5.3.4 逻辑综合面积优化5.3.5 网表面积优化5.3.6 寄存器打包5.3.7 quartus ii中的资源优化顾问5.4 i/o时序优化5.4.1 执行时序驱动的编译5.4.2 使用ioe中的触发器5.4.3 可编程输入/输出延时5.4.4 使用锁相环对时钟移相5.4.5 其他i/o时序优化方法5.5 最高时钟频率优化5.5.1 设计代码优化5.5.2 逻辑综合速度优化5.5.3 布局布线器设置5.5.4 网表优化和物理综合5.5.5 使用logiclock对局部进行优化5.5.6 位置约束、手动布局和反标注5.5.7 quartus ii中的时序优化顾问5.6 使用dse工具优化设计5.6.1 为什么需要dse5.6.2 什么是dse,如何使用5.7 如何减少编译时间5.8 设计优化实例5.9 小结5.10 问题与思考第6章altera其他高级工具6.1 命令行与tcl脚本6.1.1 命令行脚本6.1.2 tcl脚本6.1.3 使用命令行和tcl脚本6.2 hardcopy流程6.2.1 结构化asic6.2.2 hardcopy器件6.2.3 hardcopy设计流程6.3 基于nios ii处理器的嵌入式系统设计6.3.1 nios ii处理器系统6.3.2 avalon交换结构6.3.3 使用sopc builder构建系统硬件6.3.4 nios ii ide集成开发环境6.3.5 nios ii系统典型应用6.4 dsp builder工具6.4.1 dsp builder设计流程6.4.2 与sopc builder一起构建系统6.5 小结6.6 问题与思考第7章fpga系统级设计技术7.1 信号完整性及常用i/o电平标准7.1.1 信号完整性7.1.2 单端标准7.1.3 差分标准7.1.4 伪差分标准7.1.5 片上终端电阻7.2 电源完整性设计7.2.1 电源完整性7.2.2 同步翻转噪声7.2.3 非理想回路7.2.4 低阻抗电源分配系统7.3 功耗分析和热设计7.3.1 功耗的挑战7.3.2 fpga的功耗7.3.3 热设计7.4 serdes与高速系统设计7.4.1 serdes的基本概念7.4.2 altera stratix ivgx中serdes的基本结构7.4.3 典型高速系统应用框图举例7.4.4 高速pcb设计注意事项7.5 小结7.6 问题与思考。

Altera 公司 2010年12月2810Subscribe© 2010 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at /common/legal.html . Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.101 Innovation DriveSan Jose, CA 95134 使用Agilent 3070测试仪实现Altera CPLD 的在系统编程本应用笔记介绍了如何使用Agilent 3070测试系统来实现Altera ® MAX ® II 和MAX V器件的快速编程时间,并分别介绍了使用以及未使用Agilent Technologies 可编程逻辑器件(PLD)在系统编程(ISP)软件的Agilent 3070测试仪的开发流程。

FPGA\CPLD设计学习笔记题记:这个笔记不是特权同学自己整理的,特权同学只是对这个笔记做了一下完善,也忘了是从那DOWNLOAD来的,首先对整理者表示感谢。

这些知识点确实都很实用,这些设计思想或者也可以说是经验吧,是很值得每一个有志于FPGA/CPLD方面发展的工程师学习的。

1、硬件设计基本原则(1)、速度与面积平衡和互换原则:一个设计如果时序余量较大,所能跑的频率远高于设计要求,能可以通过模块复用来减少整个设计消耗的芯片面积,这就是用速度优势换面积的节约;反之,如果一个设计的时序要求很高,普通方法达不到设计频率,那么可以通过数据流串并转换,并行复制多个操作模块,对整个设计采用“乒乓操作”和“串并转换”的思想进行处理,在芯片输出模块处再对数据进行“并串转换”。

从而实现了用面积复制换取速度的提高。

(2)、硬件原则:理解HDL本质(3)、系统原则:整体把握(4)、同步设计原则:设计时序稳定的基本原则2、Verilog作为一种HDL语言,对系统行为的建模方式是分层次的。

比较重要的层次有系统级(system)、算法级(Algorithm)、寄存器传输级(RTL)、逻辑级(Logic)、门级(Gate)、电路开关级(Switch)。

3、实际工作中,除了描述仿真测试激励(Testbench)时使用for循环语句外,极少在RTL级编码中使用for循环,这是因为for循环会被综合器展开为所有变量情况的执行语句,每个变量独立占用寄存器资源,不能有效的复用硬件逻辑资源,造成巨大的浪费。

一般常用case语句代替。

4、if…else…和case在嵌套描述时是有很大区别的,if…else…是有优先级的,一般来说,第一个if的优先级最高,最后一个else的优先级最低。

而case语句是平行语句,它是没有优先级的,而建立优先级结构需要耗费大量的逻辑资源,所以能用case的地方就不要用if…else…语句。

补充:1.也可以用if…; if…; if…;描述不带优先级的“平行”语句。

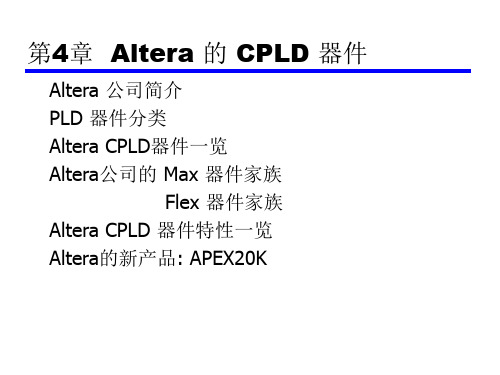

Altera公司是一家知名的半导体公司,致力于生产和销售可编程逻辑器件(PLD)和现场可编程门阵列(FPGA)等产品。

下面将列举Altera公司旗下的CPLD和FPGA产品,帮助大家更好地了解这家公司的产品线。

一、CPLD产品线1. MAX 7000系列MAX 7000系列是Altera公司推出的一款CPLD产品,具有低功耗、高性能和可编程性强的特点。

该系列产品广泛应用于通信、工业控制、汽车电子等领域,为客户提供了稳定可靠的解决方案。

2. MAX 9000系列MAX 9000系列是Altera公司的另一款CPLD产品,采用了先进的CMOS工艺和可编程逻辑单元,具有高密度、可靠性高的特点。

该系列产品在航空航天、国防安全、医疗设备等领域有着广泛的应用。

二、FPGA产品线1. Stratix系列Stratix系列是Altera公司旗下最为知名的FPGA产品之一,拥有高速、高密度、低功耗等特点,适用于需要大规模数据处理和高性能计算的应用场景。

该系列产品常用于人工智能、云计算、数据中心等领域。

2. Cyclone系列Cyclone系列是Altera公司针对中小规模应用市场推出的FPGA产品,具有低成本、低功耗、高性能等特点。

该系列产品在嵌入式系统、工业自动化、网络通信等领域有着广泛的应用。

3. Arria系列Arria系列是Altera公司旗下的高性能FPGA产品,具有高速、低功耗、灵活性强等特点,适用于需要高性能和灵活性的应用场景。

该系列产品在无线通信、高性能计算、高清视频等领域有着广泛的应用。

通过以上列举,我们可以看到Altera公司在CPLD和FPGA领域拥有丰富的产品线,为不同领域的客户提供了多样化的解决方案。

期待Altera在未来能够持续推出更多高性能、低功耗的PLD和FPGA产品,满足客户不断增长的需求。

Altera公司作为半导体行业的领军企业,一直以来致力于为全球各行业提供高性能、低功耗的可编程逻辑器件(PLD)和现场可编程门阵列(FPGA)产品。

eda技术实用教程-veriloghdl答案【篇一:eda技术与vhdl程序开发基础教程课后答案】eda的英文全称是electronic design automation2.eda系统设计自动化eda阶段三个发展阶段3. eda技术的应用可概括为4.目前比较流行的主流厂家的eda软件有、5.常用的设计输入方式有原理图输入、文本输入、状态机输入6.常用的硬件描述语言有7.逻辑综合后生成的网表文件为 edif8.布局布线主要完成9.10.常用的第三方eda工具软件有synplify/synplify pro、leonardo spectrum1.8.2选择1.eda技术发展历程的正确描述为(a)a cad-cae-edab eda-cad-caec eda-cae-cadd cae-cad-eda2.altera的第四代eda集成开发环境为(c)a modelsimb mux+plus iic quartus iid ise3.下列eda工具中,支持状态图输入方式的是(b)a quartus iib isec ispdesignexpertd syplify pro4.下列几种仿真中考虑了物理模型参数的仿真是(a)a 时序仿真b 功能仿真c 行为仿真d 逻辑仿真5.下列描述eda工程设计流程正确的是(c)a输入-综合-布线-下载-仿真b布线-仿真-下载-输入-综合c输入-综合-布线-仿真-下载d输入-仿真-综合-布线-下载6.下列编程语言中不属于硬件描述语言的是(d)a vhdlb verilogc abeld php1.8.3问答1.结合本章学习的知识,简述什么是eda技术?谈谈自己对eda技术的认识?答:eda(electronic design automation)工程是现代电子信息工程领域中一门发展迅速的新技术。

2.简要介绍eda技术的发展历程?答:现代eda技术是20世纪90年代初从计算机辅助设计、辅助制造和辅助测试等工程概念发展而来的。

FPGA设计中的资源优化策略

在FPGA(现场可编程门阵列)设计中,资源优化策略是非常重要的。

在设计过程中,经常会遇到资源不足的问题,因此需要采取一些策略来优化资源的利用,以实现设计的最佳性能和效率。

首先,对于FPGA设计中资源的优化,需要考虑到逻辑资源、存储资源和时序资源。

逻辑资源是指FPGA中可用的逻辑单元,存储资源是指FPGA中可用的存储单元,时序资源是指设计在FPGA中的时钟周期。

在优化逻辑资源方面,可以采取逻辑综合和优化编码的方法,减少逻辑门数量,简化逻辑电路结构,从而节省FPGA中的逻辑资源。

其次,针对存储资源的优化,可以采取存储资源共享和优化存储器的方法。

存储资源共享是指多个模块共享同一个存储器,减少存储器的使用,从而节省存储资源。

优化存储器是指采取合适的存储器类型,如RAM、ROM等,以及设计有效的存储器结构,提高FPGA中存储资源的利用率。

最后,在时序资源的优化方面,可以采取时序约束和时序优化的方法。

时序约束是指给出设计中各个时序参数的限制,如时钟频率、时钟间隔等,保证设计在FPGA中能够满足时序要求。

时序优化是指通过合理的时序设计,减小时序路径的延迟,提高FPGA中时序资源的利用率。

总的来说,对于FPGA设计中的资源优化策略,需要综合考虑逻辑资源、存储资源和时序资源的优化方法,合理设计电路结构和时序约束,以提高FPGA设计的性能和效率。

通过有效的资源优化策略,可以充分利用FPGA中的资源,实现设计的最佳性能和效率。

希望以上介绍对您有所帮助,如有任何疑问,请随时与我联系。

CPLD 实验系统用户手册单片机爱好者网站荣誉出品Altera CPLD 实验系统是针对CPLD初、中级学习者设计,帮助用户降低学习成本和加快用户快速进入可编程逻辑器件设计开发领域,提供一个帮助用户快速开始可编程逻辑器件学习之旅的硬件平台。

可以作为数字电路的试验平台,做几乎所有的数字电路试验,不需一根导线和数字电路IC.第一章系统安装Altera CPLD 实验系统由CPLD 实验主板、Altera CPLD子板、Altera CPLD下载线、直流电源等组成首先进行软件的安装:实验系统的软件平台是Altera Quartus II 专用设计软件,完成程序的编辑、编译,以及软件模拟运行。

Altera 的EPM7128由于只可以重复烧写100次,不适合实验,实验板采用一颗atmel ATF1508-PLCC84,ATF15XX 系列CPLD芯片提供了替代ALTERA公司 EPM7000 和 EPM3000系列芯片的引脚完全一致,结构完全包容的器件。

ATF15XX系列芯片可实现ALTERA 公司芯片的完全替换!!!!不存在任何性能和设计上的不同;可重复编程10000次,可放心做实验。

安装atmel ISP编程软件,运行配套光盘中的安装程序,按程序的提示,一步步安装即可。

安装atmel 的pof2ed 编程软件,将Quartus II生成的POF文件转换成atmel ISP编程软件使用的jed文件,用于烧写ATF1508芯片下一步进行硬件安装:1、将5V直流电源的输出插头插入实验板的电源插座—J7;2、将Altera CPLD下载线的并口电缆插入计算机的并行口,将Altera CPLD下载线的10芯电缆插座插入的实验板的CPLD JTAG下载插座---J8;3、将5V直流电源插入交流220V插座,实验板的电源指示LED会亮,说明实验板已进入工作状态,硬件安装完成。

至此实验系统安装完毕,可以实验。

第二 章 实验板的具体功能介绍电源本板需外接5V电源(插头内正外负),用本机随带的5V /1A专用开关电源为电路板供电。

ALTERA CPLD 使用教程版权所有 2005-12______________________________________________________________________________目录第1章软件安装 (3)1.1 开始安装 (3)1.2 安装向导 (3)1.3 接受协议 (4)1.4 使用信息 (5)1.5 完全安装 (5)1.6 安装目录 (6)1.7 安装程序组 (6)1.8 安装完成 (7)第2章编程器驱动安装 (7)2.1 搜索硬件 (7)2.2 硬件连接 (8)2.3 添加新的硬件设备 (9)2.4 手动选择硬件 (9)2.5 选择硬件类型 (10)2.6 选择硬件驱动程序 (10)2.7 选择硬件型号 (11)2.8 安装完成 (11)2.9 硬件设置 (12)第3章MAX+plus II 10.2 使用 (13)3.1 新建工程 (13)3.2 添加文件 (13)3.3 器件选择 (14)3.4 引脚定义 (14)3.5 开始编译 (15)3.6 编译完成 (15)3.7 下载配置 (15)3.8 开始下载 (16)______________________________________________________________________________第1章软件安装AL TERA公司一直都处于可编程芯片系统(SOPC)领域的前沿和领先地位,为业界提供最先进的可编程逻辑器件、相关的软件工具、IP软件模块以及优秀的设计服务。

第三代PLD开发系统,使用MAX+PLUSII的设计者不需精通器件内部的复杂结构。

设计者可以用自己熟悉的设计工具(如原理图输入或硬件描述语言)建立设计,MAX+PLUSII 把这些设计转自动换成最终所需的格式。

其设计速度非常快。

对于一般几千门的电路设计,使用MAX+PLUSII,从设计输入到器件编程完毕,用户拿到设计好的逻辑电路,大约只需几小时。

Altera CPLD的简介Altera在近十五年CPLD经验基础上,推出了成本很低的CPLD――MAX II系列。

MAX II器件的成本是相竞争CPLD的一半,它采用了新的查找表(LUT)体系,因此每个I/O管脚的成本很低,而且开创了CPLD体系的新纪元。

这种即用的非易失器件系列面向通用的小容量逻辑应用,从而设计者能够发挥CPLD器件的优势,替代小型ASIC和ASSP。

MAX II器件采用了成本优化的六层金属0.18微米Flash工艺,其功耗大约是前一代MAX器件的十分之一。

它们的容量从240至2,210个逻辑单元(LE)(192至1,700个等效宏单元),多达272个用户I/O管脚。

表1是MAX II器件的主要特性,表2是可提供的封装。

MAX II的特性MAX II器件包括一些能够充分发挥技术创新的新特性,这也是Altera的传统。

该器件系列是专为降低新老CPLD应用成本而设计的。

重要的MAX II特性包括:功耗是前一代CPLD系列的十分之一――MAX II器件的动态功耗很低,所以运行功耗较低。

MAX II 系列功耗是低成本MAX 3000A系列的十分之一。

容量翻两番――器件容量等效于大约192至1700个宏单元。

这是Altera以往系列的四倍。

性能翻倍――由于MAX II器件系列布线体系、软件算法和工艺技术的改进,性能平均比MAX 7000AE快两倍。

用户Flash存储器――Altera据称是首家在可编程逻辑器件(PLD)内提供用户Flash存储器的可编程逻辑供应商。

因此,MAX II器件系列能够省去常用的串行或并行EEPROM,它们的批量价格通常在50美分至2美元之间,从而进一步降低了终端系统的成本。

整个系列每个器件的存储容量为8K比特。

实时在系统可编程性(ISP)――用于能够在不中断功能的情况下实时地重新配置MAX II器件。

这允许客户为运行中的客户系统增加功能或灵活性。

有关MAX II器件特性的完整说明,请浏览Altera网站/max2。