CHM2179A中文资料

- 格式:pdf

- 大小:84.37 KB

- 文档页数:6

特性 ▪ ▪ ▪ ▪ ▪ ▪ ▪ ▪ ▪ ▪ ▪ ▪ ▪ 应用SOP14CMT2159A带微能量收集FSK/OOK 编码发射器术语本文所用到的术语描述如下:AN 应用笔记PA 功率放大器BOM 物料清单PC 个人计算机BSC 中心基本距离PCB 印刷电路板BW 带宽PLL 锁相环DC 直流PN 相位噪声EEPROM电可擦除可编程只读存储器RBW 分辨带宽ESD 静电释放RCLK 参考时钟ESR 等效串联电阻RF 射频GUI 图形用户界面RFPDK RF产品开发套件IC 集成电路RoHS 危害物质限用指令LDO 低压差稳压器RSSI 接收信号强度指示器Max 最大Rx 接收,接收器MCU 微控制器单元SOP 小外形封装Min 最小Tx 发射,发射器MOQ 最小起订量Typ 典型NP0 具有温度补偿特性XOSC 晶体振荡器OBW 占用带宽XTAL/Xtal 晶体OOK 开关键控目录1.电气特性 (4)1.1推荐运行条件 (4)1.2绝对最大额定值 (4)1.3发射器规格 (5)1.4晶体振荡器 (6)1.5DC-DC特性 (6)2.管脚描述 (7)3.典型性能 (8)4.典型应用 (9)5.功能描述 (11)5.1概述 (11)5.2调制,频率及数据率 (12)5.3RFPDK及内建EEPROM (12)5.4功率放大器 (13)5.5Ramping (13)5.6运行状态 (14)5.7编码器 (15)5.7.11920编码结构 (15)5.7.21527编码结构 (16)5.7.32262编码结构 (17)5.8LED发射指示 (18)6.订购信息 (19)7.封装外形 (20)8.顶部丝印 (21)9.其它文档 (22)10.文档变更记录表 (23)11.联系方式 (24)1. 电气特性V1接5V,T OP= 25 °C,F RF = 433.92 MHz,输出功率是+10 dBm,匹配与50 Ω阻抗,除非另行声明,所有结果是在CMT2159A-EM V1.0上测试得到。

EVERLIGHT ELECTRONICS CO.,LTD.Technical Data Sheet 0603 Package Chip LED(0.4mm Height)19-217/G7C-AL1M2B/3TFeatures․Package in 8mm tape on 7〞diameter reel. ․Compatible with automatic placement equipment. ․Compatible with infrared and vapor phase reflow solder process. ․Mono-color type. ․Pb-free. ․The product itself will remain within RoHS complaint versionDescriptions․The 19-217 SMD Taping is much smaller than lead frame type components, thus enable smaller board size, higher packing density, reduced storage space and finally smaller equipment to be obtained. ․ Besides, lightweight makes them ideal for miniature applications. etc.Applications․Backlighting in dashboard and switch. ․Telecommunication: indicator and backlighting in telephone and fax. ․Flat backlight for LCD, switch and symbol. ․General use.Device Selection GuidePart No. 19-217/G7C-AL1M2B/3T Chip Material AlGaInP Emitted Color Brilliant Yellow Green Lens Color Water ClearEverlight Electronics Co., Ltd. Device No:SZDSE-197-G01 Prepared date: 17-10-2006Rev. 2Page: 1 of 10Prepared by: Bian ChangYou/EVERLIGHT ELECTRONICS CO.,LTD.19-217/G7C-AL1M2B/3TPackage Outline DimensionsNote: The tolerances unless mentioned is ±0.1mm ,UnitEverlight Electronics Co., Ltd. Device No:SZDSE-197-G01 Prepared date: 17-10-2006Rev. 2Page: 2 of 10Prepared by: Bian ChangYou/EVERLIGHT ELECTRONICS CO.,LTD.19-217/G7C-AL1M2B/3TAbsolute Maximum Ratings (Ta=25℃)Parameter Reverse Voltage Forward Current Peak Forward Current (Duty 1/10 @1KHz) Power Dissipation Electrostatic Discharge(HBM) Operating Temperature Storage Temperature Soldering Temperature Symbol VR IF IFP Pd ESD Topr Tstg Tsol Rating 5 25 60 60 2000 -40 ~ +85 -40 ~ +90 Unit V mA mA mW V ℃ ℃Reflow Soldering : 260 ℃ for 10 sec. Hand Soldering : 350 ℃ for 3 sec.Electro-Optical Characteristics (Ta=25℃)Parameter Luminous Intensity Viewing Angle Peak Wavelength Dominant Wavelength Spectrum Radiation Bandwidth Forward Voltage Reverse Current Symbol Iv 2θ1/2 λp λd △λ VF IR Min. 11.5 --------569.5 ----1.75 ----Typ. ----120 575 ----20 --------Max. 28.5 --------577.5 ----2.35 10 Unit mcd deg nm nm nm V μA VR=5V IF=20mA ConditionNotes:1.Tolerance of Luminous Intensity ±10% 2.Tolerance of Dominant Wavelength ±1nm 3.Tolerance of Forward Voltage ±0.1VEverlight Electronics Co., Ltd. Device No:SZDSE-197-G01 Prepared date: 17-10-2006Rev. 2Page: 3 of 10Prepared by: Bian ChangYou/EVERLIGHT ELECTRONICS CO.,LTD.19-217/G7C-AL1M2B/3TBin Range Of Dom. WavelengthGroup Bin C16 A C17 C18 C19 Bin L1 L2 M1 M2 Group Bin 0 B 1 2 Min 11.5 14.5 18.0 22.5 Min 1.75 1.95 2.15 Min 569.5 571.5 573.5 575.5 Max 571.5 573.5 575.5 577.5 Max 14.5 18.0 22.5 28.5 Max 1.95 2.15 2.35 V IF=20mA Unit Condition mcd IF=20mA Unit Condition nm IF=20mA Unit ConditionBin Range Of Luminous IntensityBin Range Of Forward VoltageNotes:1.ToleLance of Luminous Intensity ±10% 2.ToleLance of Dominant Wavelength ±1nm 3.ToleLance of FoLwaLd Voltage ±0.1VEverlight Electronics Co., Ltd. Device No:SZDSE-197-G01 Prepared date: 17-10-2006Rev. 2Page: 4 of 10Prepared by: Bian ChangYou/EVERLIGHT ELECTRONICS CO.,LTD.19-217/G7C-AL1M2B/3TTypical ElectLo-Optical ChaLacteListics CuLvesEverlight Electronics Co., Ltd. Device No:SZDSE-197-G01 Prepared date: 17-10-2006Rev. 2Page: 5 of 10Prepared by: Bian ChangYou/EVERLIGHT ELECTRONICS CO.,LTD.19-217/G7C-AL1M2B/3TLabel explanationCAT: Luminous Intensity Lank HUE: Dom. Wavelength Lank LEF: FoLwaLd Voltage Lankxxxxxx xxxxxxRoHSxxxxxxxxxxxx xxxx xxxxxxxxLeel DimensionsNote: The toleLances unless mentioned is ±0.1mm ,Unit = mmEverlight Electronics Co., Ltd. Device No:SZDSE-197-G01 Prepared date: 17-10-2006Rev. 2Page: 6 of 10Prepared by: Bian ChangYou/EVERLIGHT ELECTRONICS CO.,LTD.19-217/G7C-AL1M2B/3TCaLLieL Tape Dimensions: Loaded quantity 3000 PCS peL LeelNote: The toleLances unless mentioned is ±0.1mm ,Unit = mmMoistuLe Lesistant PackagingLabelAluminum moistue-proof bagDesiccantLabelEverlight Electronics Co., Ltd. Device No:SZDSE-197-G01 Prepared date: 17-10-2006Rev. 2Page: 7 of 10Prepared by: Bian ChangYou/EVERLIGHT ELECTRONICS CO.,LTD.19-217/G7C-AL1M2B/3TLeliability Test Items And ConditionsThe Leliability of pLoducts shall be satisfied with items listed below. Confidence level:90% LTPD:10%No. 1 2Items Leflow SoldeLing TempeLatuLe CycleTest Condition Temp. : 260℃±5℃ Min. 5sec. H : +100℃ 15min ∫ 5 min L : -40℃ 15min H : +100℃ 5min ∫ 10 sec L : -10℃ 5min Temp. : 100℃ Temp. : -40℃ IF = 20 mA 85℃/ 85%RHTest Sample HouLs/Cycle Size s 6 Min. 300 Cycles 22 PCS. 22 PCS.Ac/Le 0/1 0/13 4 5 6 7TheLmal Shock High TempeLatuLe StoLage Low TempeLatuLe StoLage DC OpeLating Life High TempeLatuLe / High Humidity300 Cycles 1000 HLs. 1000 HLs. 1000 HLs. 1000 HLs.22 PCS. 22 PCS. 22 PCS. 22 PCS. 22 PCS.0/1 0/1 0/1 0/1 0/1Everlight Electronics Co., Ltd. Device No:SZDSE-197-G01 Prepared date: 17-10-2006Rev. 2Page: 8 of 10Prepared by: Bian ChangYou/EVERLIGHT ELECTRONICS CO.,LTD.19-217/G7C-AL1M2B/3TPLecautions FoL Use1. Over-current-proof Customer must apply resistors for protection, otherwise slight voltage shift will cause big current change ( Burn out will happen ). 2. Storage 2.1 Do not open moisture proof bag before the products are ready to use. 2.2 Before opening the package: The LEDs should be kept at 30℃ or less and 90%RH or less. 2.3 After opening the package: The LED's floor life is 1 year under 30℃ or less and 60% RH or less. If unused LEDs remain, it should be stored in moisture proof packages. 2.4 If the moisture absorbent material (silica gel) has faded away or the LEDs have exceeded the storage time, baking treatment should be performed using the following conditions. Baking treatment : 60±5℃ for 24 hours. 3. Soldering Condition 3.1 Pb-free solder temperature profile3.2 Reflow soldering should not be done more than two times. 3.3 When soldering, do not put stress on the LEDs during heating. 3.4 After soldering, do not warp the circuit board.Everlight Electronics Co., Ltd. Device No:SZDSE-197-G01 Prepared date: 17-10-2006Rev. 2Page: 9 of 10Prepared by: Bian ChangYou/EVERLIGHT ELECTRONICS CO.,LTD.19-217/G7C-AL1M2B/3T4.Soldering Iron Each terminal is to go to the tip of soldering iron temperature less than 350℃ for 3 seconds within once in less than the soldering iron capacity 25W. Leave two seconds and more intervals, and do soldering of each terminal. Be careful because the damage of the product is often started at the time of the hand solder. 5.Repairing Repair should not be done after the LEDs have been soldered. When repairing is unavoidable, a double-head soldering iron should be used (as below figure). It should be confirmed beforehand whether the characteristics of the LEDs will or will not be damaged by repairing.EVERLIGHT ELECTRONICS CO., LTD. Office: No 25, Lane 76, Sec 3, Chung Yang Rd, Leliability Test Items AndR.O.C Conditions Tucheng, Taipei 236, Taiwan,The Leliability of pLoducts shall be satisfied with items listed below.Tel: 886-2-2267-2000, 2267-9936 Fax: 886-2267-6244, 2267-6189, 2267-6306 Everlight Electronics Co., Ltd. Device No:SZDSE-197-G01 Prepared date: 17-10-2006Rev. 2Page: 10 of 10Prepared by: Bian ChangYou/分销商库存信息: EVERLIGHT19-217/G7C-AL1M2B/3T。

Axial Lead and Cartridge Fuses409w w w.l i t t e l f u s e.c o mDesigned to IEC Standard• Designed to International (IEC) Standards for use globally.• Meets the IEC 60127-2, Sheet 2 specification for Fast-Acting Fuses.• Available in Cartridge and Axial Lead Form.• Available in ratings of 0.032 to 15 amperes.ELECTRICAL CHARACTERISTICS:% of AmpereAmpere Opening RatingRating Time150%.032–6.360 minutes, Min imum 8-1530 minutes, Min imum 210%.032-1530 minutes, Max imum275%.032–.1000.01 sec., Min.;.5 sec.Max..125–150.05 sec., Min.;2 sec.Max.400%.032–.100.003 sec., Min.;0.1 sec.Max..125–6.3.01 sec., Min.;0.3 sec.Max.8 - 15.01 sec., Min.;0.4 sec.Max.1000%.032–6.3.02 second, Max imum 8-15.04 second, Max imumINTERRUPTING RATING:35 amperes or 10 x rated current;(whichever is greater) to a maximum 100 amperes @ 250VAC, unity Power Factor.ORDERING INFORMATION:Cartridge Nominal Nominal Catalog Ampere Voltage Resistance Melting I 2t Number Rating Rating Cold Ohms A 2Sec.217.032.032250262.20.000060217.040.040250183.20.000085217.050.05025015.200.000190217.063.06325010.450.000550217.080.0802507.8900.000828217.100.100250 5.6970.00450217.125.125250 3.8200.00477217.160.160250 2.5250.010217.200.200250 1.7000.024217.250.250250 1.2330.042217.315.3152500.8800.112217.400.4002500.2770.127217.500.5002500.2070.219217.600.6002500.2000.390217.630.6302500.1900.409217.800.8002500.1200.847217001.12500.096 1.0422171.25 1.252500.070 2.23021701.5 1.52500.056 4.38221701.6 1.62500.053 4.616217002.22500.042 5.72621702.5 2.52500.0339.460217003. 3.02500.02417.0412173.15 3.152500.02217.722217004.42500.01629.164217005.52500.01442.79621706.3 6.32500.00962.466217008.8*2500.007198.158217010.10*2500.006217.633217015.15*2500.004607.133ENVIRONMENTAL SPECIFICATIONS:Operating temperature:-55˚C to 125˚CThermal Shock:MIL-STD-202F Method 107G, Test Condition B:(5cycles –65°C to +125°C)Vibration:MIL-STD-202F Method 201AHumidity:MIL-STD-202F Method 103B, T est Condition A.high relative humidity (95%) and elevated temperature (40°C) for 240 hours.Salt Spray:MIL-STD-202F Method 101D, T est Condition BPHYSICAL SPECIFICATIONS:Material:Body:GlassCap:Nickel Plated Brass Leads:Tin Plated CopperTerminal Strength :MIL-STD-202F Method 211A,T est Condition ASolderability:Reference IEC 60127 Second Edition 2003-01 Annex A T erminal strength:MIL-STD-202F Method 211A, T est Condition A Product Marking:Cap 1:current and voltage rating.Cap 2:Agency approval markings.Packaging:Available in Bulk (v=5, H=100, M=1000 pcs/pkg) or on Tape/Reel (MRET1=1000 pcs/reel).1Axial Lead and Cartridge Fuses410w w w.l i t t e l f u s e.c o mDesigned to IEC StandardAgency ApprovalsNote:600mA, 1.5A and 3A ratings are available with UL recognition and CSA acceptance only.8A and 10A are under consideration by IEC(125V).。

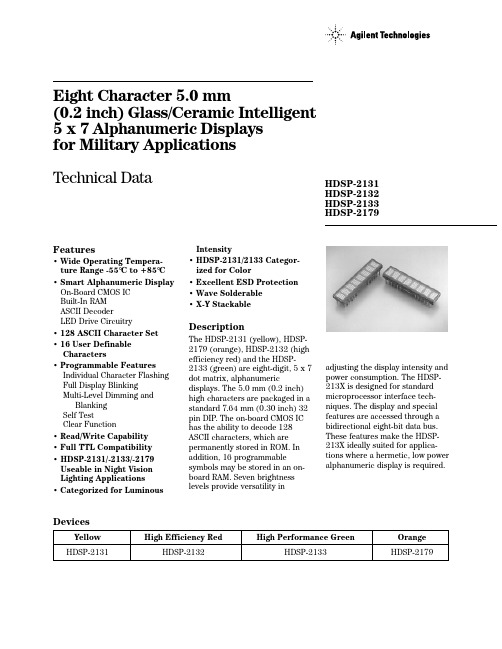

Intensity• HDSP-2131/2133 Categor-ized for Color• Excellent ESD Protection • Wave Solderable • X-Y StackableDescriptionThe HDSP-2131 (yellow), HDSP-2179 (orange), HDSP-2132 (high efficiency red) and the HDSP-2133 (green) are eight-digit, 5 x 7dot matrix, alphanumericdisplays. The 5.0 mm (0.2 inch)high characters are packaged in a standard 7.64 mm (0.30 inch) 32pin DIP. The on-board CMOS IC has the ability to decode 128ASCII characters, which are permanently stored in ROM. In addition, 16 programmablesymbols may be stored in an on-board RAM. Seven brightness levels provide versatility inFeatures• Wide Operating Tempera-ture Range -55°C to +85°C • Smart Alphanumeric Display On-Board CMOS IC Built-In RAM ASCII DecoderLED Drive Circuitry• 128 ASCII Character Set • 16 User Definable Characters• Programmable Features Individual Character Flashing Full Display Blinking Multi-Level Dimming and Blanking Self TestClear Function• Read/Write Capability • Full TTL Compatibility • HDSP-2131/-2133/-2179Useable in Night Vision Lighting Applications• Categorized for LuminousEight Character 5.0 mm(0.2 inch) Glass/Ceramic Intelligent 5x 7 Alphanumeric Displays for Military Applications Technical DataHDSP-2131HDSP-2132HDSP-2133HDSP-2179DevicesYellow High Efficiency RedHigh Performance GreenOrange HDSP-2131HDSP-2132HDSP-2133HDSP-2179adjusting the display intensity and power consumption. The HDSP-213X is designed for standard microprocessor interface tech-niques. The display and special features are accessed through a bidirectional eight-bit data bus.These features make the HDSP-213X ideally suited for applica-tions where a hermetic, low power alphanumeric display is required.元器件交易网2Package DimensionsESD WARNING: STANDARD CMOS HANDLING PRECAUTIONS SHOULD BE OBSERVED WITH THE HDSP-2131, HDSP-2132, HDSP-2133, AND HDSP-2179.Absolute Maximum RatingsSupply Voltage, V DD to Ground [1]........................................-0.3 to 7.0 V Operating Voltage, V DD to Ground [2].............................................5.5 V Input Voltage, Any Pin to Ground..............................-0.3 to V DD +0.3 V Free Air Operating Temperature Range, T A ....................-55°C to +85°C Storage Temperature, T S ..............................................-55°C to +100°C CMOS IC Junction Temperature, T J (IC)....................................+150°C Wave Solder Temperature,1.59 mm (0.063 in.) below Body...............................250°C for 3 secs ESD Protection @ 1.5 k Ω, 100 pF.........................V Z = 4 kV (each pin)Notes:1. Maximum voltage is with no LEDs illuminated.2. 20 dots ON in all locations at full brightness.Note:1. All dimensions are in mm (inches).2. Unless otherwse specified tolerance is ±0.30 mm (±0.015).3. For green and yellow devices only.4. Leads are copper alloy, solder dipped.HDSP-213X/2179元器件交易网3 Character SetRecommended Operating ConditionsParameter Symbol Minimum Nominal Maximum Units Supply Voltage V DD 4.5 5.0 5.5VElectrical Characteristics over Operating Temperature Range4.5 < V DD <5.5 V (unless otherwise specified)25°C25°CParameter Symbol Min.Typ.[1]Max.[1]Max.[2]Units Test Conditions Input Leakage I I-10.0+10.0µA V IN = 0 to V DD, (Input without pullup)pins CLK, D0-D7,A0-A4Input Current I IP-30.0111830µA V IN = 0 to V DD, (Input with pullup)pins RST, CLS, WR,RD, CE, FLI DD Blank I DD (BLK)0.5 1.5 2.0mA V IN = V DDI DD 8 digits I DD(V)200255330mA"V" on in all 812 dots/character[3]locationsI DD 8 digits I DD(#)300370430mA"#" on in all 820 dots/character[3]locationsInput Voltage High V IH 2.0V DD V V DD = 5.5 V+0.3Input Voltage Low V IL GND0.8V V DD = 4.5 V-0.3 VOutput V oltage High V OH 2.4V V DD = 4.5 V,I OH = -40 µA Output Voltage Low V OL0.4V V DD = 4.5 V,D0-D7I OL = 1.6 mA Output Voltage Low0.4V V DD = 4.5 V,CLK I OL = 40 µA Thermal Resistance RθJ-PIN11°C/WIC Junction-to-PINNotes:1.V DD = 5.0 V.2.Maximum I DD occurs at -55°C.3.Average I DD measured at full brightness. See Table 2 in Control Word Section for I DD at lower brightness levels. PeakI DD = 28/15 x Average I DD (#).Optical Characteristics at 25°C[4]= 5.0 V at Full BrightnessVDDHigh Efficiency Red HDSP-2132Description Symbol Minimum Typical Units2.57.5mcdLuminous Intensity Character Average (#)IVPeak Wavelengthλ635nmPEAK626nm Dominant WavelengthλdOrange HDSP-2179Description Symbol Minimum Typical Units2.57.5mcdLuminous Intensity Character Average (#)IVPeak Wavelengthλ600nmPEAK602nm Dominant WavelengthλdYellow HDSP-2131Description Symbol Minimum Typical Units2.57.5mcdLuminous Intensity Character Average (#)IV583nm Peak WavelengthλPEAK585nm Dominant WavelengthλdHigh Performance Green HDSP-2133Description Symbol Minimum Typical Units Luminous Intensity Character Average (#)I2.57.5mcdV568nm Peak WavelengthλPEAKDominant Wavelengthλ574nmdNote:4.Refers to the initial case temperature of the device immediately prior to the light measurement.AC Timing Characteristics over Temperature RangeV DD = 4.5 to 5.5 V unless otherwise specified.ReferenceNumber Symbol Description Min.[1]Units1t ACC Display Access TimeWrite210Read230ns 2t ACS Address Setup Time to Chip Enable10ns3t CE Chip Enable Active Time[2, 3]Write140Read160ns 4t ACH Address Hold Time to Chip Enable20ns 5t CER Chip Enable Recovery Time60ns6t CES Chip Enable Active Prior to Rising Edge of[1,2]Write140Read160ns7t CEH Chip Enable Hold Time to Rising Edge ofRead/Write Signal[2, 3]0ns 8t W Write Active Time[2,3]100ns 9t WD Data Valid Prior to Rising Edge of Write Signal50ns 10t DH Data Write Hold Time20ns 11t R Chip Enable Active Prior to Valid Data160ns 12t RD Read Active Prior to Valid Data75ns 13t DF Read Data Float Delay10ns t RC Reset Active Time[4]300ns Notes:1. Worst case values occur at an IC junction temperature of 150°C.2. For designers who do not need to read from the display, the Read line can be tied to V DD and the Write and Chip Enable lines can betied together.3. Changing the logic levels of the Address lines when CE = “0” may cause erroneous data to be entered into the Character RAM,4. The display must not be accessed until after 3 clock pulses (110 µs min. using the internal refresh clock) after the rising edge of thereset line.AC Timing Characteristics over Temperature RangeV DD = 4.5 to 5.5 V unless otherwise specified.Symbol Description25°C Typical Minimum[1]UnitsF OSC Oscillator Frequency5728kHzF RF[5]Display Refresh Rate256128HzF FL[6]Character Flash Rate21Hzt ST[7]Self Test Cycle Time 4.69.2Sec Notes:5.F RF = F OSC/224.6.F FL = F OSC/28,672.7.t ST = 262,144/F OSC.Write Cycle Timing DiagramINPUT PULSE LEVELS WITH 0.6 V TO 2.4 VINPUT PULSE LEVELS: 0.6 V TO 2.4 V8Read Cycle Timing DiagramCharacter Font Relative Luminous Intensity vs.TemperatureElectrical DescriptionPin FunctionRESET (RST, pin 5)Reset initializes the display.FLASH (FL, pin 27)FL low indicates an access to the Flash RAM and is unaffected by thestate of address lines A3-A4.ADDRESS INPUTS Each location in memory has a distinct address. Address inputs (A0-A2)(A0-A4, pins 28-32)select a specific location in the Character RAM, the Flash RAM or aparticular row in the UDC (User-Defined Character) RAM. A3-A4 areused to select which section of memory is accessed. Table 1 shows thelogic levels needed to access each section of memory.Table 1. Logic Levels to Access MemoryFL A4 A3Section of Memory A2A1A00X X Flash RAM Character Address10 0UDC Address Register Don't Care10 1UDC RAM Row Address11 0Control Word Register Don't Care11 1Character RAM Character Address CLOCK SELECT This input is used to select either an internal (CLS = 1) or external (CLS = 0) (CLS, pin 1)clock source.CLOCK INPUT/OUTPUT Outputs the master clock (CLS = 1) or inputs a clock (CLS = 0) for slave (CLK, pin 2)displays.WRITE (WR, pin 3)Data is written into the display when the WR input is low and theCE input is low.CHIP ENABLE (CE, pin 4)This input must be at a logic low to read or write data to the display andmust go high between each read and write cycle.input is low.DATA Bus (D0-D7,The Data bus is used to read from or write to the display.pins 11-14, 19-22)GND(SUPPLY) (pin 17)This is the analog ground for the LED drivers.GND(LOGIC) (pin 18)This is the digital ground for internal logic.V DD(POWER) (pin 16)This is the positive power supply input.driving of eight 5 x 7 dot matrix characters. The major useraccessible portions of the display are listed below:Flash RAM, a 128 character ASCII decoder, a 16 character UDC RAM, a UDC Address Register, a Control Word Register, and the refresh circuitry necessary to synchronize the decoding andCharacter RamFigure 2 shows the logic levels needed to access theHDSP-213X Character RAM.During a normal access the CE ="0" and either RD = "0" or WR ="0". However, erroneous data may be written into the Character RAM if the Address lines are unstable when CE = "0" regardless of the Address lines A 0-A 2 are used to select the location in the Charac-ter RAM. Two types of data can be stored in each Character RAM location: an ASCII code or a UDC RAM address. Data bit D 7 is used to differentiate between an ASCII character and a UDC RAMaddress. D 7 = 0 enables the ASCII decoder and D 7 = 1 enables the UDC RAM. D 0-D 6 are used to input ASCII data and D 0-D 3 are used to input a UDC address.Figure 2. Logic Levels to Access the Character RAM.Character RAM This RAM stores either ASCII character data or a UDC RAM address.Flash RAMThis is a 1 x 8 RAM which stores Flash data.User-Defined Character This RAM stores the dot pattern for custom characters.RAM (UDC RAM)User-defined Character This register is used to provide the address to the UDC RAM when Address Registerthe user is writing or reading a custom character.(UDC Address Register)Control Word RegisterThis register allows the user to adjust the display brightness, flash individual characters, blink, self test or clear the display.Display Internal Block DiagramFigure 1 shows the internal block diagram of the HDSP-213X/-2179display. The CMOS IC consists of an 8 byte Character RAM, an 8 bitUDC RAM and UDC Address RegisterFigure 3 shows the logic levels needed to access the UDC RAM and the UDC Address Register. The UDC Address Register is eight bits wide. The lower four bits (D0-D3) are used to select one of the 16 UDC locations. The upper four bits (D4-D7) are not used. Once the UDC address has been stored in the UDC Address Register, the UDC RAM can be accessed.To completely specify a 5 x 7 character requires eight write cycles. One cycle is used to store the UDC RAM address in the UDC Address Register. Seven cycles are used to store dot data in the UDC RAM. Data is entered by rows. One cycle is needed to access each row. Figure 4 shows the organization of a UDC character assuming the symbol to be stored is an “F.” A0-A2 are used to select the row to be accessed and D0-D4 are used to transmit the row dot data. The upper three bits (D5-D7) are ignored. D0 (least significant bit) corresponds to the right most column of the 5 x 7 matrix and D4 (most significant bit) corresponds to the left most column of the 5 x 7 matrix.Flash RAMFigure 5 shows the logic levels needed to access the Flash RAM. The Flash RAM has one bit associated with each location of the Character RAM. The Flash input is used to select the Flash RAM. Address lines A3-A4 are ignored. Address lines A0-A2 are used to select the location in theFlash RAM to store the attribute. D0 is used to store or remove the flash attribute. D0 = “1” stores the attribute and D0 = “0”removes the attribute.When the attribute is enabledthrough bit 3 of the Control Wordand a "1" is stored in the FlashRAM, the corresponding characterwill flash at approximately 2 Hz.The actual rate is dependent onthe clock frequency. For anexternal clock the flash rate canbe calculated by dividing theclock frequency by 28,672.Figure 4. Data to Load “F” into the UDC RAM.Control Word RegisterFigure 6 shows how to access the Control Word Register. This is an eight bit register which performs five functions. They are Bright-ness control, Flash RAM control,Blinking, Self Test and Clear.Each function is independent of the others. However, all bits are updated during each Control Word write cycle.Brightness (Bits 0-2)Bits 0-2 of the Control Word adjust the brightness of the display. Bits 0-2 are interpreted as a three bit binary code with code (000) corresponding to maximum brightness and code (111) corresponding to a blanked display. In addition to varying the display brightness, bits 0-2 also vary the average value of I DD . I DD can be calculated at any brightness level by multiplying the percent bright-ness level by the value of I DD at the 100% brightness level.These values of I DD are shown in Table 2.Flash Function (Bit 3)Bit 3 determines whether the flashing character attribute is on or off. When bit 3 is a “1,” the output of the Flash RAM is checked. If the content of alocation in the Flash RAM is a “1,”the associated digit will flash atapproximately 2 Hz. For anexternal clock, the blink rate can be calculated by driving the clock frequency by 28,672. If the flash enable bit of the Control Word is a “0,” the content of the Flash RAM is ignored. To use this function with multiple display systems see the Reset section.Blink Function (Bit 4)Bit 4 of the Control Word is used to synchronize blinking of alleight digits of the display. When this bit is a “1” all eight digits of the display will blink at approxi-mately 2 Hz. The actual rate is dependent on the clock frequency.For an external clock, the blink rate can be calculated by dividing the clock frequency by 28,672.This function will override the Flash function when it is active.To use this function with multiple display systems see the Reset section.Figure 5. Logic Levels to Access the Flash RAM.Table 2. Current Requirements at Different Brightness Levels%25°C SymbolD 2D 1D 0BrightnessTypical Units I DD (V)000100200mA 00180160mA 01053106mA 0114080mA 1002754mA 1012040mA 111326mAFigure 6. Logic Levels to Access the Control Word RegisterSelf Test Function (Bits 5, 6) Bit 6 of the Control Word Register is used to initiate the self test function. Results of the internal self test are stored in bit 5 of the Control Word. Bit 5 is a read only bit where bit 5 = “1” indicates a passed self test and bit 5 = “0”indicates a failed self test.Setting bit 6 to a logic 1 will start the self test function. The built-in self test function of the IC consists of two internal routines which exercises major portions of the IC and illuminates all of the LEDs. The first routine cycles the ASCII decoder ROM through all states and performs a checksum on the output. If the checksum agrees with the correct value, bit 5 is set to “1.” The second routine provides a visual test of the LEDs using the drive circuitry. This is accomplished by writing checkered and inverse checkered patterns to the display. Each pattern is displayed for approxi-mately 2 seconds.During the self test function the display must not be accessed. The time needed to execute the self test function is calculated by multiplying the clock period by 262,144. For example, assume a clock frequency of 58 KHz, then the time to execute the self test function frequency is equal to (262,144/58,000) = 4.5 second duration.At the end of the self test function, the Character RAM is loaded with blanks, the Control Word Register is set to zeros except for bit 5, and the Flash RAM is cleared and the UDC Address Register is set to all ones.Clear Function (Bit 7)Bit 7 of the Control Word willclear the Character RAM and theFlash RAM. Setting bit 7 to a "1"will start the clear function. Threeclock cycles (110 µs min. usingthe internal refresh clock) arerequired to complete the clearfunction. The display must not beaccessed while the display isbeing cleared. When the clearfunction has been completed, bit7 will be reset to a “0.” The ASCIIcharacter code for a space (20H)will be loaded into the CharacterRAM to blank the display and theFlash RAM will be loaded with“0”s. The UDC RAM, UDC AddressRegister, and the remainder of theControl Word are unaffected.Display ResetFigure 7 shows the logic levelsneeded to Reset the display. Thedisplay should be Reset on Power-up. The external Reset clears theCharacter RAM, Flash RAM,Control Word and resets theinternal counters. After the risingedge of the Reset signal, threeclock cycles (110 µs min. usingthe internal refresh clock) arerequired to complete the resetsequence. The display must not beaccessed while the display isbeing reset. The ASCII Charactercode for a space (20H) will beloaded into the Character RAM toblank the display. The Flash RAMand Control Word Register areloaded with all "0"s. The UDCRAM and UDC Address Registerare unaffected. All displays whichoperate with the same clocksource must be simultaneouslyreset to synchronize the Flashingand Blinking functions.Mechanical and ElectricalConsiderationsThe HDSP-213X/-2179 is a 32 pindual-in-line package with 24external pins, which can bestacked horizontally and verticallyto create arrays of any size. TheHDSP-213X/-2179 is designed tooperate continuously from -55°Cto +85°C with a maximum of 20dots ON per character. Illuminat-ing all thirty-five dots at fullbrightness is not recommended.The HDSP-213X/-2179 isassembled by die attaching andwire bonding 280 LED chips anda CMOS IC to a ceramicsubstrate. A glass window isplaced over the ceramic substratecreating an air gap over the LEDwire bonds. A second glasswindow creates an air gap overthe CMOS IC. This packageconstruction makes the displayhighly tolerant to temperaturecycling and allows wave solderingand visual inspection of the IC.Figure 7. Logic Levels to Reset theDisplay.Figure 8. Maximum Power Dissipationvs. Ambient Temperature DeratingBased on TJMAX = 125°C.ESD SusceptibilityThese displays have ESD sus-ceptibility ratings of CLASS 3 per DOD-STD-1686 and CLASS B per MIL-STD-883C.Soldering and Post Solder Cleaning Instructions for the HDSP-213X/-2179The HDSP-213X/-2179 may be hand soldered or wave soldered with SN63 solder. When hand soldering it is recommended that an electronically temperature con-trolled and securely grounded soldering iron be used. For best results, the iron tip temperature should be set at 315°C (600°F).For wave soldering, a rosin-based RMA flux can be used. The solder wave temperature should be set at 245°C ± 5°C (473°F ± 9°F), and dwell in the wave should be set between 11/2 to 3 seconds for optimum soldering. The preheat temperature should not exceed 105°C (221°F) as measured on the solder side of the PC board.For further information on soldering and post soldercleaning, see Application Note 1027, Soldering LED Components.Contrast EnhancementWhen used with the proper con-trast enhancement filters, theHCMS-213X/-2179 series displays are readable daylight ambients.Refer to Application Note 1029Luminous Contrast and Sun-light Readability of the HDSP-235X Series Alphanumeric Displays for Military Applica-tions for information on contrast enhancement for daylightThe inputs to the CMOS IC are protected against static discharge and input current latchup. How-ever, for best results standard CMOS handling precautions should be used. Prior to use, the HDSP-213X should be stored in antistatic packages or conductive material. During assembly, a grounded conductive work area should be used, and assembly personnel should wear conductive wrist straps. Lab coats made of synthetic material should be avoided since they are prone to static charge buildup. Input current latchup is caused when the CMOS inputs are subjected to either a voltage below ground (V IN < ground) or to a voltage higher than V DD (V IN > V DD ) and when a high current is forced into the input. To prevent input cur-rent latchup and ESD damage,unused inputs should beconnected either to ground or to V DD . Voltages should not beapplied to the inputs until V DD has been applied to the display. Tran-sient input voltages should be eliminated.Thermal ConsiderationsThe HDSP-213X/-2179 has been designed to provide a low ther-mal resistance path from theCMOS IC to the 24 package pins.This heat is then typicallyconducted through the traces of the user’s printed circuit board to free air. For most applications no additional heatsinking is required.The maximum operating IC junction temperature is 150°C.The maximum IC junction tem-perature can be calculated using the following equation:T J (IC) MAX = T A+ (P D MAX) (R θJ-PIN + R θPIN-A )WhereP D MAX = (V DD MAX) (I DD MAX)I DD MAX = 370 mA with 20 dots ON in eight character locations at 25°C ambient. This value is from the Electrical Characteristics table.P D MAX = (5.5 V) (0.370 A)= 2.04 WGround ConnectionsTwo ground pins are provided to keep the internal IC logic ground clean. The designer can, when necessary, route the analog ground for the LED drivers sep-arately from the logic ground until an appropriate ground plane is available. On long interconnects between the display and the host system, the designer can keep voltage drops on the analogground from affecting the display logic levels by isolating the two grounds.The logic ground should be con-nected to the same ground poten-tial as the logic interface circuitry.The analog ground and the logic ground should be connected at a common ground which canwithstand the current introduced by the switching LED drivers.When separate ground connec-tions are used, the analog ground can vary from -0.3 V to +0.3 V with respect to the logic ground.Voltage below -0.3 V can cause all dots to be on. Voltage above +0.3V can cause dimming and dot mismatch.ambients. Refer to Application Note 1015 Contrast Enhance-ment Techniques for LEDDisplays for information on con-trast enhancement in moderate ambients.Night Vision LightingWhen used with the proper NVG/DV filters, theHDSP-2131, HDSP-2179 and HDSP-2133 may be used in nightvision lighting applications. The HDSP-2131 (yellow), HDSP-2179(orange) displays are used as master caution and warningindicators. The HDSP-2133 (high performance green) displays are used for general instrumentation.For a list of NVG/DV filters and a discussion on night vision lighting technology, refer to Application Note 1030 LED Displays and Indicators and Night VisionImaging System Lighting. An external dimming circuit must be used to dim these displays tonight vision lighting levels to meet NVIS radiance requirements.Refer to AN 1039 Dimming HDSP-213X Displays to Meet Night Vision Lighting Levels.Note:Test conditions as specified in Optical Characteristic table.Note:Test conditions as specified in Optical Characteristic table.Color Bin Limits/semiconductorsFor product information and a complete list ofdistributors, please go to our web site.For technical assistance call:Americas/Canada: +1 (800) 235-0312 or (916) 788-6763Europe: +49 (0) 6441 92460China: 10800 650 0017Hong Kong: (+65) 6756 2394India, Australia, New Zealand: (+65) 6755 1939Japan: (+81 3) 3335-8152 (Domestic/Interna-tional), or 0120-61-1280 (Domestic Only)Korea: (+65) 6755 1989Singapore, Malaysia, Vietnam, Thailand,Philippines, Indonesia: (+65) 6755 2044Taiwan: (+65) 6755 1843Data subject to change.Copyright © 2004 Agilent Technologies, Inc.Obsoletes 5988-2258EN July 19, 20045988-4667EN元器件交易网。

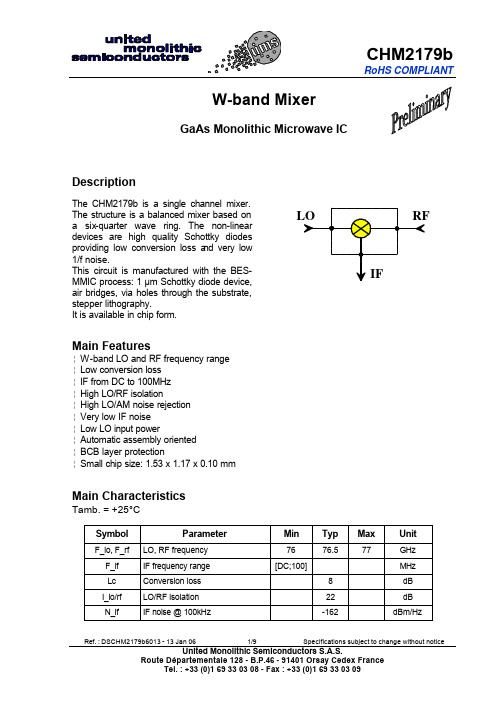

¦ IF from DC to 100MHz¦ High LO/RF isolation¦ High LO/AM noise rejection¦ Very low IF noise¦ Low LO input power¦ Automatic assembly oriented¦ BCB layer protection¦ Small chip size: 1.53 x 1.17 x 0.10 mmMain CharacteristicsTamb. = +25°CSymbol Parameter Min Typ Max UnitF_lo, F_rf LO, RF frequency 76 76.5 77 GHz F_if IF frequency range [DC;100] MHzLc Conversion loss 8 dBI_lo/rf LO/RF isolation 22 dBN_if IF noise @ 100kHz -162 dBm/Hz Ref. : DSCHM2179b6013 - 13 Jan 06 1/9 Specifications subject to change without noticeUnited Monolithic Semiconductors S.A.S.Route Départementale 128 - B.P.46 - 91401 Orsay Cedex FranceTel. : +33 (0)1 69 33 03 08 - Fax : +33 (0)1 69 33 03 09CHM2179b W-band Mixer ESD Protection : Electrostatic discharge sensitive device. Observe handling precautions !Full operating temperature range, used according to section “Typical assembly and bias configuration”Symbol Parameter Min Typ Max Unit F_lo, F_rf LO, RF frequency 76 77 GHz F_if IF frequency range [DC;100] MHz Lc Conversion loss 5 8 10 dB P_lo LO input power 3 5.5 8 dBm P_RF_1dB RF input power at 1 dB -3 0 dBm VSWR_lo LO port VSWR (50Ω) 2:1 2.5:1VSWR_rf RF port VSWR (50Ω) 2:1 2.5:1IMP_if IF load impedance (1) 200 ΩI_lo/rf LO/RF isolation 16 22 dB R_lo_am LO AM noise rejection (SSB) 20 27 dB NFNoise figure for IF=1kHz (2) 35 40 dBNoise figure for IF=10kHz (2) 29 34 dBNoise figure for IF=100kHz (2) 21.5 26.5 dBNoise figure for IF=200kHz (2) 18 23 dB +V Positive supply voltage (3) 4.5 V+I Positive supply current (3) 1.5 2.5 mA Top Operating temperature range -40 +100 °C (1) The IF optimum load for conversion loss is 200Ω. For minimum noise figure this load can be lower, the best results have been obtained on 50Ω.(2) Measured on 200Ω IF impedance.(3) An external resistor controls the bias current (see section “Typical Assembly and Bias Configuration”) Absolute Maximum Ratings (1)Symbol Parameter Values Unit +V Supply voltage 6 V+I Supply current 2.5 mA P_lo Maximum peak input power overdrive at LO port (2) 10 dBmP_rf_cw Maximum input power at RF port (3) 3 dBm Tstg Storage temperature range -55 to +125 °C(1) Operation of this device above anyone of these parameters may cause permanent damage.(2) Duration < 1sCHM2179b W-band Mixer (3) Continuous wave mode.W-band MixerCHM2179bChip Mechanical Data and Pin ReferencesUnit = µmExternal chip size = 1530 x 1170 Chip thickness = 100 +/- 10HF Pads (2,5) = 105 X 86 (BCB opening) DC/IF Pads = 86 x 83 (BCB opening)Pin number Pin nameDescription1,3,4,6 Ground: should not be bonded. If required,please ask for more information.2 LO LO input 5 RF RF input7 GND Ground (optional) 8 Not Connected9 IF IF output 10 C_ext Bias decoupling 11 +V Positive supply voltageSeveral external configurations are possible for bias and IF. The objective is to give flexibility for the integration.As this component is mainly dedicated to low IF use, there are several possibilities for interfacing with low noise IF amplifier. The optimum IF load for conversion loss is 200Ω, however depending on the IF amplifier noise characteristic this load can be modified in order to optimise the noise figure. A series capacitor, between IF output and the load is recommended. Due to high sensitivity to electrical discharges an integrated resistance is used and two ports are available for biasing. One is for the connection of a decoupling capacitor (C_ext) and the other one is for the supply voltage connection through an external series resistance (+V port). However, in order to keep the compatibility with the CHM2179, only the “C_ext” port can beNotes::1. R_bias = R_bias1 + 1kΩ when “+V” port is used, otherwize R_bias = R_bias22. R_bias can be adjusted if necessary; This allows to optimise the performances when someparameters are different from recommended ones (Supply voltage, LO power …). However maximum ratings for the current have to be taken into account.3. A series capacitor at IF outputs is recommended for DC decoupling.In order to use acceptable wire bonding length, compatible with automatic pick and place and wire bonding equipment, an external matching network is proposed on low dielectric constant substrate.CHM2179b W-band Mixer Unit =µmW-band Mixer CHM2179bOrdering InformationChip form : CHM2179b98F/00Information furnished is believed to be accurate and reliable. However United Monolithic Semiconductors S.A.S. assumes no responsability for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of United Monolithic Semiconductors S.A.S.. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. United Monolithic Semiconductors S.A.S. products are not authorised for use as critical components in life support devices or systems without express written approval from United Monolithic Semiconductors S.A.S.。

LOW VOLTAGE HEADPHONE AMPLIFIER for PORTABLE AUDIO s GENERAL DESCRIPTION s PACKAGE OUTLINEThe NJM2171A is a low voltage headphone amplifierdesigned for portable audio items.The NJM2171A operates directly for battery supply. It includes mute and standby circuit which require few external components and realize low current consumption and very low turn-noise at standby mode.It is suitable for portable Mini-Disc, portable Compact-Disc, and other headphone amplifier application.s FEATURESq Operating Voltage V+1=1.8 to 4.5VV+2=0.9 to 4.5Vq Operating Current 450µA typ. @V+1=2.3V700µA typ. @V+2=1.2Vq Supply Current in Power Down Mode10µA typ. @V+1=2.3V25µA typ. @V+2=1.2Vq Output Power Exceeds 5mW R L=16Ω@THD=10% q Fixed Voltage Gain 11.5dB typ.q Package Outline VSP10q Bipolar Technologys PIN CONFIGURATIONNJM2171AR PIN FUNCTION1.V+22.OUT13.IN14.STBY5.V+16.V REF7.MUTE8.IN29.OUT210.GNDs ABSOLUTE MAXIMUM RATINGS(Ta=25°C)PARAMETER SYMBOL RATINGS UNITSupply Voltage V+5VPower Dissipation P D (VSP8) 320mWOperating Temperature Range Topr-20 to +75°CStorage Temperature Range Tstg-40 to +125°Cs RECOMMENDED OPERATING CONDITIONS (Ta=25°C)PARAMETER SYMBOL MIN.TYP.MAX.UNITOperating Voltage Range1V+1 1.8 2.3 4.5VOperating Voltage Range2V+20.9 1.2 4.5Vs ELECTRICAL CHARACTERISTICS (V+1=2.3V,V+2=1.2V,Rg=600Ω,R L=16Ω,f=1kHz,Ta=25°C) PARAMEETER SYMBOL TEST CONDITION MIN.TYP.MAX.UNITI CC0V+1=0V(1pin)--1I CC1STANDBY ON,MUTE ON(1pin)-2540I CC2STANDBY ON,MUTE ON(5pin)-1015µAI CC3No signal(1pin)-7001200 Operating CurrentI CC4No signal(5pin)-450700I CC5P O=0.5mW+0.5mW(1pin)- 5.5-mAI CC6P O=0.5mW+0.5mW(5pin)-0.8-Reference Voltage V REF No signal0.550.600.65V Closed Loop Gain G V V IN=-30dBV10.511.512.5dBP O1THD=10% 5.08.5-mW Output PowerP O2V+1=1.8V,V+2=0.9V,THD=10% 2.0 4.0-THD1Po=1mW,R L=16Ω-0.150.3% Total Harmonic DistortionTED2Po=5mW,R L=16Ω-0.40.6Output Noise Voltage V NO A-Weighted--100-96dBV Crosstalk CT V IN=-30dBV--80-70dBV Mute Level MUTE MUTE-ON,V IN=-30dBV,A-Weighted--95-80dBVSVR1V+1=1.8V+0.1Vrms, V+2=0.9V6070-Supply Voltage RejectiondB Ratio SVR2V+1=1.8V, V+2=0.9V+0.1Vrms6070-s CONTROL TERMINAL CHARACTERISTICSPARAMETER SYMBOL TEST CONDITION MIN.TYP.MAX.UNIT High Level Input Voltage V IH STBY(4pin), MUTE(7pin) 1.2-V +1V Low Level Input Voltage V IL STBY(4pin), MUTE(7pin)0-0.3Vs CONTROL TERMINAL EXPLANATION •STBY (4Pin)PARAMETER CONTROL SIGNAL STATUS STANDBY ON H IC is non-active.STANDBY OFF L IC is active.•MUTE (7Pin)PARAMETER CONTROL SIGNAL STATUS MUTE ON H IC doesn’t output the signal.MUTE OFF L IC output the signal.s APPLICATION CIRCUITV +2OUT1IN1OUT2IN2V +1。

General DescriptionThe MAX6921/MAX6931 are 20-output, 76V, vacuum-fluorescent display (VFD) tube drivers that interface a multiplexed VFD tube to a VFD controller, such as the MAX6850–MAX6853, or to a microcontroller. The MAX6921/MAX6931 are also ideal for driving static VFD tubes or telecom relays.Data is input using an industry standard 4-wire serial interface (CLOCK, DATA, LOAD, BLANK), compatibile with either Maxim’s or industry-standard VFD driver and controller.For easy display control, the active-high BLANK input forces all driver outputs low, turning the display off, and automatically puts the MAX6921/MAX6931 into shut-down mode. Display intensity can also be controlled by directly pulse-width modulating the BLANK input.The MAX6921 has a serial interface data output, DOUT,allowing any number of devices to be cascaded on the same serial interface.The MAX6931 has a negative supply voltage input, V SS ,allowing the drivers’ output swing to be made bipolar to simplify filament biasing in many applications.The MAX6921 is available in 28-pin TSSOP, SO, and PLCC packages. The MAX6931 is available in a 28-pin TSSOP package.Maxim also offers 12-output VFD drivers (MAX6920) and 32-output VFD drivers (MAX6922/MAX6932).ApplicationsWhite Goods Industrial Weighing Gaming Machines Security Automotive Telecom Avionics VFD Modules InstrumentationIndustrial ControlFeatureso 5MHz Industry-Standard 4-Wire Serial Interface o 3V to 5.5V Logic Supply Rangeo 8V to 76V Grid/Anode Supply Rangeo -11V to 0V Filament Bias Supply (MAX6931 Only)o Push-Pull CMOS High-Voltage Outputs o Outputs can Source 40mA, Sink 4mA Continuously o Outputs can Source 75mA Repetitive Pulseso Outputs can be Paralleled for Higher Current Drive o Any Output can be Used as a Grid or an Anode Drivero Blank Input Simplifies PWM Intensity Control o Small 28-Pin TSSOP Packageo -40°C to +125°C Temperature RangeMAX6921/MAX693120-Output, 76V , Serial-InterfacedVFD Tube Drivers________________________________________________________________Maxim Integrated Products1Ordering Information19-3020; Rev 1; 4/10For pricing, delivery, and ordering information,please contact Maxim Direct at 1-888-629-4642,or visit Maxim’s website at .Typical Operating CircuitPin Configurations appear at end of data sheet./V denotes an automotive qualified part.M A X 6921/M A X 693120-Output, 76V , Serial-Interfaced VFD Tube Drivers 2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSELECTRICAL CHARACTERISTICS(Typical Operating Circuit , V BB = 8V to 76V, V CC = 3V to 5.5V, V SS = -11V to 0V, V BB - V SS ≤76V, T A = T MIN to T MAX , unless other-Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Voltage (with respect to GND)V BB .........................................................................-0.3V to +80V V CC ...........................................................................-0.3V to +6V V SS (MAX6931 only)...............................................-12V to +0.3V V BB - V SS (MAX6931 only).....................................-0.3V to +80V OUT_ (MAX6921 only)..................(GND - -0.3V) to (V BB + 0.3V)OUT_ (MAX6931 only)....................(V SS - -0.3V) to (V BB + 0.3V)All Other Pins..............................................-0.3V to (V CC + 0.3V)OUT_ Continuous Source Current ....................................-45mA OUT_ Pulsed (1ms max, 1/4 max duty) Source Current ...-80mA Total OUT_ Continuous Source Current .........................-540mA Total OUT_ Continuous Sink Current .................................90mA Total OUT_ Pulsed (1ms max, 1/4 max duty)Source Current ...........................................................-960mA OUT_ Sink Current .............................................................15mA CLK, DIN, LOAD, BLANK, DOUT Current .......................±10mAContinuous Power Dissipation (T A = +70°C)28-Pin TSSOP (derate 12.8mW/°Cover +70°C)................................................................1025mW 28-Pin Wide SO (derate 12.5mW/°Cover +70°C)................................................................1000mW 28-Pin PLCC (derate 10.5mW/°Cover +70°C)..................................................................842mW Operating Temperature Range(T MIN to T MAX )...............................................-40°C to +125°C Junction Temperature......................................................+150°C Storage Temperature Range.............................-65°C to +150°C Lead Temperature (soldering, 10s).................................+300°C Soldering Temperature (reflow)Wide SO, TSSOP lead(Pb)-free...................................+260°C PLCC lead(Pb)-free......................................................+245°CMAX6921/MAX693120-Output, 76V , Serial-InterfacedVFD Tube Drivers_______________________________________________________________________________________3ELECTRICAL CHARACTERISTICS (continued)(Typical Operating Circuit , V BB = 8V to 76V, V CC = 3V to 5.5V, V SS = -11V to 0V, V BB - V SS ≤76V, T A = T MIN to T MAX , unless other-wise noted.) (Note 1)Typical Operating Characteristics(V CC = 5.0V, V BB = 76V, and T A = +25°C, unless otherwise noted.)M A X 6921/M A X 693120-Output, 76V , Serial-Interfaced VFD Tube Drivers 4_______________________________________________________________________________________ELECTRICAL CHARACTERISTICS (continued)(Typical Operating Circuit , V BB = 8V to 76V, V CC = 3V to 5.5V, V SS = -11V to 0V, V BB - V SS ≤76V, T A = T MIN to T MAX , unless other-wise noted.) (Note 1)Note 2:Guaranteed by design.Note 3:Delay measured from control edge to when output OUT_ changes by 1V.TUBE SUPPLY CURRENT (I BB)vs. TEMPERATURE (OUTPUTS LOW)TEMPERATURE (°C)S U P P L Y C U R R E N T (m A )100804060020-200.20.40.60.81.01.21.41.61.82.00-40120TUBE SUPPLY CURRENT (I BB )vs. TEMPERATURE (OUTPUTS HIGH)TEMPERATURE (°C)S U P P L Y C U R R E N T (m A )100804060020-200.20.40.60.81.01.21.41.61.82.00-40120LOGIC SUPPLY CURRENT (I CC )vs. TEMPERATURE (OUTPUTS LOW)TEMPERATURE (°C)S U P P L Y C U R R E N T (µA )10080406020-2050100150200250300350400-40120MAX6921/MAX693120-Output, 76V , Serial-InterfacedVFD Tube DriversOUTPUT RISE AND FALL WAVEFORMMAX6921/31 toc071µs/divBLANK 2V/divOUT_20V/divTypical Operating Characteristics (continued)(V CC = 5.0V, V BB = 76V, and T A = +25°C, unless otherwise noted.)LOGIC SUPPLY CURRENT (I CC )vs. TEMPERATURE (OUTPUTS HIGH)TEMPERATURE (°C)S U P P L Y C U R R E N T (µA )10080406020-20450500550600650700750800400-40120OUTPUT VOLTAGE (V BB - V H )vs. TEMPERATURE (OUTPUT HIGH)TEMPERATURE (°C)O U T P U T V O L T A G E (V )100804060020-200.51.01.52.02.53.03.5-40120OUTPUT VOLTAGEvs. TEMPERATURE (OUTPUT LOW)TEMPERATURE (°C)O U T P U T V O L T A G E (V )10080406020-2024681012140-40120M A X 6921/M A X 693120-Output, 76V , Serial-Interfaced VFD Tube Drivers 6_______________________________________________________________________________________Figure 1. MAX6921/MAX6931 Functional DiagramDetailed DescriptionThe MAX6921/MAX6931 are VFD tube drivers compris-ing a 4-wire serial interface driving 20 high-voltage rail-to-rail output ports. The driver is suitable for both static and multiplexed displays.The output ports feature high current-sourcing capabili-ty to drive current into grids and anodes of static or multiplex VFDs. The ports also have active current sink-ing for fast discharge of capacitive display electrodes in multiplexing applications.The 4-wire serial interface comprises a 20-bit shift reg-ister and a 20-bit transparent latch. The shift register is written through a clock input CLK and a data input DIN.For the MAX6921, the data propagates to a data output DOUT. The data output allows multiple drivers to be cascaded and operated together. The output latch is transparent to the shift register outputs when LOAD is high, and latches the current state on the falling edge of LOAD.Each driver output is a slew-rated controlled CMOS push-pull switch driving between V BB and G ND (MAX6921) or V SS (MAX6931). The output rise time is always slower than the output fall time to avoid shoot-through currents during output transitions. The output slew rates are slow enough to minimize EMI, yet are fast enough so as not to impact the typical 100µs digit multiplex period and affect the display intensity.Initial Power-Up and OperationAn internal reset circuit clears the internal registers of the MAX6921/MAX6931 on power-up. All outputs OUT0to OUT19 and the interface output DOUT (MAX6921only) initialize low regardless of the initial logic levels of the CLK, DIN, BLANK, and LOAD inputs.4-Wire Serial InterfaceThe MAX6921/MAX6931 use 4-wire serial interface with three inputs (DIN, CLK, LOAD) and a data output (DOUT, MAX6921 only). This interface is used to write output data to the MAX6921/MAX6931 (Figure 4) (Table 1). The serial interface data word length is 20 bits,D0–D19.The functions of the four serial interface pins are:•CLK input is the interface clock, which shifts data into the MAX6921/MAX6931s’ 20-bit shift register on its rising edge.•LOAD input passes data from the MAX6921/MAX6931s’ 20-bit shift register to the 20-bit output latch when LOAD is high (transparent latch), and latches the data on LOAD’s falling edge •DIN is the interface data input, and must be stable when it is sampled on the rising edge of CLK.•DOUT is the interface data output, which shifts data out from the MAX6921’s 20-bit shift register on the rising edge of CLK. Data at DIN is propagated through the shift register and appears at DOUT (20CLK cycles + t DO ) later.A fifth input, BLANK, can be taken high to force outputs OUT0 to OUT19 low, without altering the contents of the output latches. When the BLANK input is low, outputs OUT0 to OUT19 follow the state of the output latches. A common use of the BLANK input is PWM intensity control.The BLANK input’s function is independent of the oper-ation of the serial interface. Data can be shifted into the serial interface shift register and latched regardless of the state of BLANK.MAX6921/MAX693120-Output, 76V , Serial-InterfacedVFD Tube Drivers_______________________________________________________________________________________7Figure 2. MAX6921 CMOS Output Driver StructureFigure 3. MAX6931 CMOS Output Driver StructureM A X 6921/M A X 6931Writing Device Registers Using the4-Wire Serial InterfaceThe MAX6921/MAX6931 are normally written using the following sequence:1)Take CLK low.2)Clock 20 bits of data in order D19 first to D0 lastinto DIN, observing the data setup and hold times.3)Load the 20 output latches with a falling edgeon LOAD.LOAD can be high or low during a transmission. If LOAD is high, then the data shifted into the shift regis-ter at DIN appear at the OUT0 to OUT19 outputs.CLK and DIN can be used to transmit data to other peripherals. Activity on CLK always shifts data into the MAX6921/MAX6931s’ shift register. However, the MAX6921/MAX6931 only update their output latch on the rising edge of LOAD, and the last 20 bits of data are loaded. Therefore, multiple devices can share CLK and DIN, as long as they have unique LOAD controls.Determining Driver Output Voltage DropThe outputs are CMOS drivers, and have a resistive characteristic. The typical and maximum sink and source output resistances can be calculated from the V H and V L electrical characteristics. Use this calculated resistance to determine the output voltage drop at dif-ferent output currents.20-Output, 76V , Serial-Interfaced VFD Tube Drivers 8_______________________________________________________________________________________Figure 4. 4-Wire Serial Interface Timing DiagramOutput Current RatingsThe continuous current-source capability is 40mA per output. Outputs can drive up to 75mA as a repetitive peak current, subject to the on-time (output high) being no longer than 1ms, and the duty cycle being such that the output power dissipation is no more than the dissipa-tion for the continuous case. The repetitive peak rating allows outputs to drive a higher current in multiplex grid driver applications, where only one grid is on at a time,and the multiplex time per grid is no more than 1ms.Since dissipation is proportional to current squared, the maximum current that can be delivered for a given mul-tiplex ratio is given by:I PEAK = (grids x 1600)1/2mAwhere grids is the number of grids in a multiplexed display.This means that a duplex application (two grids) can use a repetitive peak current of 56.5mA, a triplex (three grids)application can use a repetitive peak current of 69.2mA,and higher multiplex ratios are limited to 75mA.Paralleling OutputsAny number of outputs within the same package can be paralleled in order to raise the current drive or reduce the output resistance. Only parallel outputs directly (by shorting outputs together) if the interface control can be guaranteed to set the outputs to the same level. Although the sink output is relatively weak (typically 750Ω), that resistance is low enough to dissi-pate 530mW when shorted to an opposite level output at a V BB voltage of only 20V. A safe way to parallel out-puts is to use diodes to prevent the outputs from sink-ing current (Figure 5). Because the outputs cannot sink current from the VFD tube, an external discharge resis-tor, R, is required. For static tubes, R can be a large value such as 100k Ω. For multiplexed tubes, the valueof the resistor can be determined by the load capaci-tance and timing characteristics required. Resistor R discharges tube capacitance C to 10% of the initial voltage in 2.3 x RC seconds. So, for example, a 15k Ωvalue for R discharges 100pF tube grid or anode from 40V to 4V in 3.5µs, but draws an additional 2.7mA from the driver when either output is high.Power DissipationTake care to ensure that the maximum package dissi-pation ratings for the chosen package are not exceed-ed. Over-dissipation is unlikely to be an issue when driving static tubes, but the peak currents are usually higher for multiplexed tubes. When using multiple dri-ver devices, try to share the average dissipation evenly between the drivers.Determine the power dissipation (P D ) for the MAX6921/MAX6931 for static tube drivers with the fol-lowing equation:P D = (V CC x I CC ) + (V BB x I BB ) + ((V BB - V H )x I ANODE x A)where:A = number of anodes driven (the MAX6921/MAX6931can drive a maximum of 20).I ANODE = maximum anode current.(V BB - V H ) is the output voltage drop at the given maxi-mum anode current I OUT .A static tube dissipation example follows:V CC = 5V ±5%, V BB = 10V to 18V, A = 20, I OUT = 2mAP D = (5.25V x 1mA)+ (18V x 1.4mA) + ((2.5V x 2mA/25mA) x 2mA x 20) = 38mWDetermine the power dissipation (P D ) for the MAX6921/MAX6931 for multiplex tube drivers with the following equation:P D = (V CC x I CC ) + (V BB x I BB ) + ((V BB - V H )x I ANODE x A) + ((V BB - V H ) x I GRID )where:A = number of anodes driven.G = number of grids driven.I ANODE = maximum anode current.I GRID = maximum grid current.The calculation presumes all anodes are on, but only one grid is on. The calculated P D is the worst case,presuming one digit is always being driven with all its anodes lit. Actual P D can be estimated by multiplying this P D figure by the actual tube drive duty cycle, taking into account interdigit blanking and any PWM intensity control.MAX6921/MAX693120-Output, 76V , Serial-InterfacedVFD Tube Drivers_______________________________________________________________________________________9Figure 5. Paralleling OutputsM A X 6921/M A X 6931A multiplexed tube dissipation example follows:V CC = 5V ±5%, V BB = 36V to 42V, A = 12, G = 8,I ANODE = 0.4mA, I GRID = 24mAP D = (5.25V x 1mA)+ (42V x 1.4mA)+ ((2.5V x 0.4mA/25mA) x 0.4mA x 12) + ((2.5V x 24mA/25mA) x 24mA) = 122mWThus, for a 28-pin wide TSSOP package (T JA = 1 / 0.0128= 78.125°C/W from Absolute Maximum Ratings ), the maximum allowed ambient temperature T A is given by:T J(MAX) = T A + (P D x T JA ) = 150°C = T A + (0.122x 78.125°C/W)So T A = +140.5°C.This means that the driver can be operated in this application up to the MAX6921/MAX6931s’ +125°C maximum operating temperature.Power-Supply ConsiderationsThe MAX6921/MAX6931 operate with multiple power-supply voltages. Bypass the V CC , V BB , and V SS (MAX6931 only) power-supply pins to GND with 0.1µF capacitors close to the device. The MAX6931 can be operated with V SS connected to GND if a negative bias supply is not required. For multiplex applications, it may be necessary to add an additional bulk electrolytic capacitor of 1µF or greater to the V BB supply.Power-Supply SequencingThe order of the power-supply sequencing is not impor-tant. The MAX6921/MAX6931 will not be damaged if any combination of V CC , V BB , and V SS (MAX6931 only)is grounded while the other supply or supplies are maintained up to their maximum ratings. However, as with any CMOS device, do not drive the MAX6921/MAX6931s’ logic inputs if the logic supply V CC is not operational because the input protection diodes clamp the signals.Cascading Drivers (MAX6921 Only)Multiple MAX6921s can be cascaded, as shown in the Typical Application Circuit , by connecting each driver’s DOUT to DIN of the next drivers. Devices can be cas-caded at the full 5MHz CLK speed when V CC ≥4.5V.When V CC <4.5V, the longer propagation delay (t DO )limits the maximum cascaded CLK to 4MHz.20-Output, 76V , Serial-Interfaced VFD Tube Drivers 10______________________________________________________________________________________分销商库存信息:MAXIMMAX6921AQI+T MAX6921AUI+T MAX6921AQI+ MAX6921AUI+MAX6922AQH+D MAX6921AWI+T MAX6931AUI+MAX6931AUI+T MAX6922AQH+TD MAX6921AWI+。

This document was generated on 08/13/2012PLEASE CHECK FOR LATEST PART INFORMATIONPart Number:19039-0017Status:ActiveDescription:Avikrimp™ Snap Plug Receptacle for 18-22 AWG Wire, Nylon, Fits Male Plug Diameter 4.57mm, Mylar Tape CarrierDocuments:Drawing (PDF)Product Specification PS-19902-015 (PDF)Product Specification PS-19902-011 (PDF)RoHS Certificate of Compliance (PDF)Agency CertificationCSA LR18689ULE152602GeneralProduct Family Quick Disconnects Series19039CommentsFits Male Plug Dia. 4.57mm Crimp Quality Equipment YesProduct Name Avikrimp™Type Snap Receptacle UPC800755958539PhysicalBarrel Type Closed Color - Resin Natural Flammability 94V-2GenderFemale Glow-Wire Compliant NoInsulationNylon (PA)Lock to Mating Part None Material - MetalBrass Material - Plating MatingTin Material - Plating Termination Tin Material - Resin Nylon Net Weight 1.312/g OrientationStraightPackaging Type Adhesive Tape on Reel Plating min - Mating2.540µm Plating min - Termination 2.540µm Tab Thickness N/A Tab WidthN/ATemperature Range - Operating -40°C to +105°CTermination Interface: Style Crimp or Compression Wire Insulation Diameter 3.25mm max.Wire Size AWG 18, 20, 22Wire Size mm²0.25 - 1.50ElectricalVoltage - Maximum600V Material InfoOld Part NumberBRA-8180NTReference - Drawing NumbersProduct Specification PS-19902-011, PS-19902-015Sales DrawingSD-19039-001Seriesimage - Reference onlyEU RoHSChina RoHSELV and RoHS Compliant REACH SVHC Not ReviewedLow-Halogen Status Not ReviewedNeed more information on product environmental compliance?Email productcompliance@For a multiple part number RoHS Certificate of Compliance, click herePlease visit the Contact Us section for any non-product compliance questions.Search Parts in this Series 19039SeriesApplication Tooling | FAQTooling specifications and manuals are found by selecting the products below.Crimp Height Specifications are then contained in the Application Tooling Specification document.GlobalDescription Product #Mini-Mac™Applicator 0638853600Crimp Dies for MTA-100 Tape Applicator used in 3BF Press, MTA-105Tape Applicator used in TM-2000™ Press,and ATP-301 Air Crimping Press for Mylar Tape Mounted Terminals0192880033This document was generated on 08/13/2012PLEASE CHECK FOR LATEST PART INFORMATION分销商库存信息: MOLEX 0190390017。

a217wc1化学成分摘要:1.化学成分概述2.元素组成3.功能特性4.应用领域5.总结正文:【1】化学成分概述a217wc1是一种合金材料,其化学成分主要包括铁、碳、镍、钼、铬等元素。

在这些元素的共同作用下,a217wc1合金具有优异的性能。

【2】元素组成1.铁:作为基体元素,铁为a217wc1提供了良好的强度和韧性。

2.碳:碳元素可以提高a217wc1的硬度和耐磨性。

3.镍:镍元素有助于提高a217wc1的抗腐蚀性能。

4.钼:钼元素可以提高a217wc1的耐磨性和耐热性。

5.铬:铬元素赋予了a217wc1优良的耐腐蚀性和抗氧化性。

【3】功能特性1.优异的抗腐蚀性能:a217wc1合金在腐蚀环境下具有较高的抗腐蚀能力,使其在化工、海洋工程等领域具有广泛的应用。

2.良好的耐磨性能:a217wc1合金的高硬度和耐磨性使其在磨损环境下具有较长的使用寿命。

3.较高的强度和韧性:a217wc1合金在承受较大应力时仍具有较好的抗断裂能力。

4.良好的焊接性能:a217wc1合金易于焊接,有利于提高工程应用中的施工效率。

【4】应用领域1.化工设备:a217wc1合金的抗腐蚀性能使其在化工设备的制造中具有广泛应用。

2.海洋工程:在海洋环境下,a217wc1合金的高抗腐蚀性能使其成为理想的选择。

3.能源领域:a217wc1合金在核电站、石油化工等高温、高压环境的设备制造中具有重要作用。

4.航空航天:a217wc1合金的高强度和韧性使其在航空航天领域的结构件制造中具有优势。

【5】总结a217wc1化学成分的合金材料在工业领域具有广泛的应用,其优异的抗腐蚀、耐磨、强度和韧性等性能使其成为众多行业的首选材料。