VHDL数字电子钟的设计与实现_论文

- 格式:doc

- 大小:532.00 KB

- 文档页数:14

课程设计报告设计题目:用VHDL语言实现数字钟的设计班级:电子 0901学号: XXXXXXXX姓名:XXXXXXXXX指导教师:XXXXXXXXX设计时间:现代电子设计技术的核心已转向基于计算机的电子设计自动化技术,即EDA (Electronic Design Automation)技术。

EDA技术就是依赖计算机,在EDA工具软件平台上,对以硬件描述语言HDL(Hardware Description Language)为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、分割、综合、布局布线以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

EDA技术使得设计者的工作仅限于利用软件的方式,即利用硬件描述语言和EDA软件来完成对系统硬件功能的实现。

硬件描述语言是EDA技术的重要组成部分,常见的HDL语言有VHDL、Verilog、HDL、ABLE、AHDL、System Verilog和System C。

其中VHDL、Verilog在现在的EDA设计中使用最多,也拥有几乎所有主流EDA工具的支持。

VHDL语言具有很强的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,从而大大简化硬件设计任务,提高了设计效率和可靠性。

在这次设计中,主要使用VHDL语言输入。

此次设计很好地完成了数字钟的定时、切换显示年月日和时分秒的功能,完成了小型FPGA的设计开发,锻炼了动手实践能力,达到了课程设计的目的。

关键词:EDA技术硬件描述语言VHDL 设计数字电子钟摘要 (2)1、课程设计目的 (4)2、课程设计内容及要求 (4)2.1 设计内容 (4)2.2 设计要求 (4)3、VHDL程序设计 (5)3.1 方案论证 (5)3.2 设计思路与方法 (6)3.2.1 设计思路 (6)3.2.2 设计方法 (7)4、仿真与分析 (7)5、器件编程下载及设计结果 (9)6、课程设计总结 (10)7、参考文献 (10)8、程序清单 (11)8.1 顶层模块 (11)8.2 秒脉冲模块 (13)8.3 数码管显示模块 (14)8.4 时分秒模块 (15)8.4.1 分秒模块 (16)8.4.2 小时模块 (18)8.5 年月日模块 (19)8.5.1 日期模块 (21)8.5.2 月份模块 (24)8.5.3 年份模块 (25)1、课程设计目的EDA技术课程设计在课程结束以后进行,在实践中验证理论知识,不仅是为了巩固课堂上所学知识,更是为了加深我们对EDA技术和VHDL语言的理解;为了让我们自己动手完成从设计输入、逻辑综合、功能仿真、设计实现到实现编程、时序仿真,一直到器件的下载测试的整个过程,真切感受利用EDA技术对FPGA进行设计开发的过程,锻炼和提高我们对器件的编程调试能力。

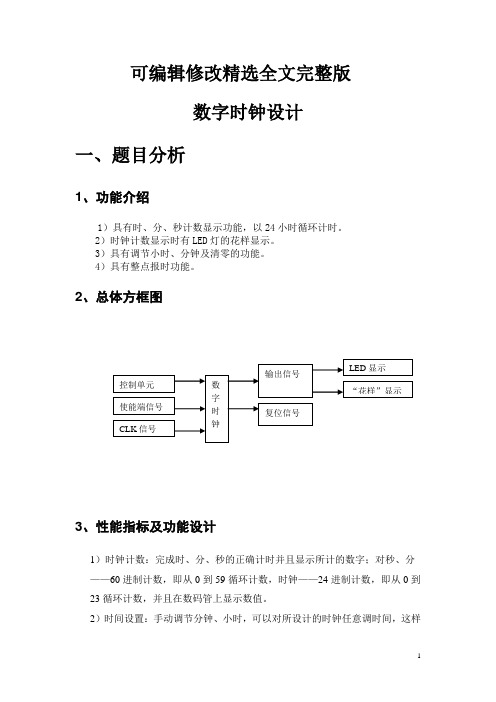

可编辑修改精选全文完整版数字时钟设计一、题目分析1、功能介绍1)具有时、分、秒计数显示功能,以24小时循环计时。

2)时钟计数显示时有LED灯的花样显示。

3)具有调节小时、分钟及清零的功能。

4)具有整点报时功能。

2、总体方框图3、性能指标及功能设计1)时钟计数:完成时、分、秒的正确计时并且显示所计的数字;对秒、分——60进制计数,即从0到59循环计数,时钟——24进制计数,即从0到23循环计数,并且在数码管上显示数值。

2)时间设置:手动调节分钟、小时,可以对所设计的时钟任意调时间,这样使数字钟真正具有使用功能。

我们可以通过实验板上的键7和键4进行任意的调整,因为我们用的时钟信号均是1HZ的,所以每LED灯变化一次就来一个脉冲,即计数一次。

3)清零功能:reset为复位键,低电平时实现清零功能,高电平时正常计数。

可以根据我们自己任意时间的复位。

4)蜂鸣器在整点时有报时信号产生,蜂鸣器报警。

产生“滴答.滴答”的报警声音。

5)LED灯在时钟显示时有花样显示信号产生。

即根据进位情况,LED不停的闪烁,从而产生“花样”信号。

二、选择方案1、方案选择方案一:根据总体方框图及各部分分配的功能可知,本系统可以由秒计数器、分钟计数器、小时计数器、整点报时、分的调整以及小时的调整和一个顶层文件构成。

采用自顶向下的设计方法,子模块利用VHDL语言设计,顶层文件用原理图的设计方法。

显示:小时采用24进制,而分钟均是采用6进制和10进制的组合。

方案二:根据总体方框图及各部分分配的功能可知,本系统可以由秒计数器、分钟计数器、小时计数器、整点报时、分的调整以及小时的调整和一个顶层文件构成。

采用自顶向下的设计方法,子模块利用VHDL语言设计,顶层文件用原理图的设计方法。

显示:小时采用24进制,而分钟和秒均60进制。

终上所述,考虑到试验时的简单性,故我选择了方案二。

三、细化框图根据自顶向下的方法以及各功能模块的的功能实现上述设计方案应系统细化框图:四、编写程序、仿真和分析1、秒计数器1)VHDL 语言描述程序见附录 2)秒计数器的仿真波形图3)波形分析数字时钟控制单元 时调整 分调整使能端信号 CLK 信号时显示 分显示 秒显示24进制 60进制 60进制LED 显示整点报花样显利用60进制计数器完成00到59的循环计数功能,当秒计数至59时,再来一个时钟脉冲则产生进位输出,即enmin=1;reset作为复位信号低电平有效,即高电平时正常循环计数,低电平清零。

VHDL电子时钟的设计VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,用于设计和模拟数字电路和系统。

在这篇文章中,我们将探讨VHDL电子时钟的设计。

设计一个VHDL电子时钟需要考虑以下几个方面:时钟的显示方式、时钟的时钟源以及时钟的控制逻辑。

首先,我们需要确定时钟的显示方式。

常见的电子时钟显示方式有7段LED显示和LCD显示。

在这里,我们选择使用7段LED显示。

7段LED 显示由7个LED灯组成,可以显示0到9的数字。

此外,还需要考虑到显示小时和分钟的两个时钟。

接下来,我们需要确定时钟的时钟源。

时钟源决定了时钟的精度和稳定性。

在VHDL设计中,常用的时钟源有晶体振荡器和时钟发生器。

晶体振荡器由晶体和振荡电路组成,可以提供非常精确和稳定的时钟信号。

时钟发生器则基于计数器和除频器的原理产生时钟信号。

根据实际需求选择合适的时钟源。

最后,我们需要设计时钟的控制逻辑。

控制逻辑决定了时钟的功能和操作方式。

在这里,我们将设计一个简单的时钟,包括设置时间、调节时间、显示时间和闹钟功能。

我们可以使用按钮和开关控制时钟的功能。

下面是一个VHDL电子时钟的示例设计代码:```vhdl--时钟显示模块entity ClockDisplay isportclk : in std_logic;reset : in std_logic;hours : in integer range 0 to 23;minutes : in integer range 0 to 59;alarm : in std_logic;seg7 : out std_logic_vector(6 downto 0) end entity ClockDisplay;architecture Behavioral of ClockDisplay is signal count : integer := 0;signal sec : integer := 0;signal disp_hours : integer := 0;signal disp_minutes : integer := 0;beginprocess (clk, reset)beginif reset = '1' thencount <= 0;sec <= 0;disp_hours <= 0;disp_minutes <= 0;elsif rising_edge(clk) thencount <= 0;sec <= sec + 1;elsecount <= count + 1;end if;end if;end process;process (sec, reset, hours, minutes, alarm)beginif reset = '1' thendisp_hours <= 0;disp_minutes <= 0;elsif rising_edge(sec) thenif alarm = '1' and hours = disp_hours and minutes = disp_minutes then--闹钟触发逻辑elsif sec = 59 thenif minutes = 59 thenif hours = 23 thendisp_hours <= 0;disp_minutes <= 0;elsedisp_hours <= hours + 1; disp_minutes <= 0;end if;elsedisp_hours <= hours;disp_minutes <= minutes + 1; end if;elsedisp_hours <= hours;disp_minutes <= minutes;end if;end if;end process;process (disp_hours, disp_minutes)begincase disp_hours is...end case;case disp_minutes is...end case;end process;end architecture Behavioral;```这个代码中,我们使用了两个进程来处理时钟的计时和显示逻辑。

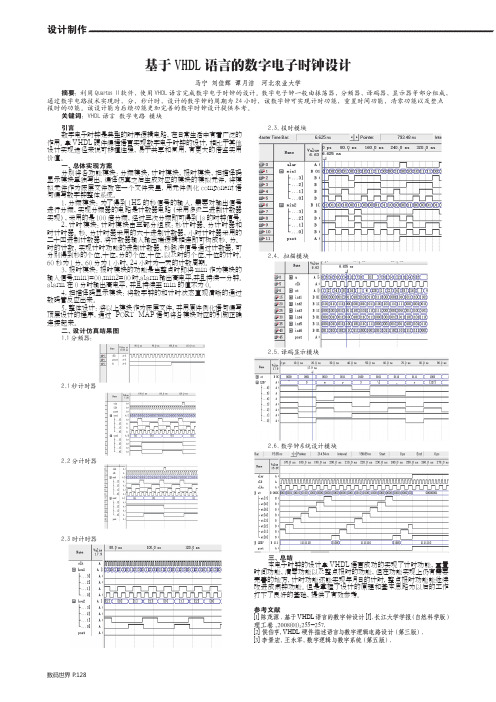

设计制作数码世界 P.128基于VHDL语言的数字电子时钟设计马宁 刘佳辉 谭月洁 河北农业大学摘要:利用QuartusⅡ软件,使用VHDL语言完成数字电子时钟的设计。

数字电子钟一般由振荡器,分频器,译码器,显示器等部分组成,通过数字电路技术实现时,分,秒计时,设计的数字钟的周期为24小时,该数字钟可实现计时功能,重置时间功能,清零功能以及整点报时的功能。

该设计能为后续功能更加完善的数字时钟设计提供参考。

关键词:VHDL语言 数字电路 模块引言数字电子时钟是典型的时序逻辑电路,在日常生活中有着广泛的作用。

拿VHDL硬件编程语言实现数字电子时钟的设计,相比于其他设计实现途径来说可移植性强,易于共享和复用,有更大的借鉴实用价值。

一、总体实现方案分别将各功能模块:分频模块,计时模块,报时模块,扫描译码显示模块单独写出,编译仿真之后生成对应的模块的模拟元件,将模拟元件作为底层文件放在一个文件夹里,用元件例化component语句编写数字钟整体系统。

1.分频模块:为了得到1HZ的秒信号的输入,需要对输出信号进行分频,实现分频器的电路是计数器电路(采用多级二进制计数器实现),采用的是100倍分频,经过三次分频即可得到1s的时钟信号。

2.计时模块:计时模块由三部分组成:秒计时器、分计时器和时计时器。

秒、分计时器采用的六十进制计数器,小时计时器采用的二十四进制计数器,将计数器输入输出端逻辑相连即可构成秒、分、时的计数,实现计时功能的进制计数器。

秒脉冲信号通过计数器,可分别得到秒的个位、十位,分的个位、十位,以及时的个位、十位的计时。

60秒为1分,60分为1小时,24小时为一天的计数周期。

3.报时模块:报时模块的功能是当整点时即将min作为模块的输入信号,min1=00,min2=00时,alarm输出高电平,并且持续一分钟。

alarm在0分时输出高电平,并且持续至min的值不为0。

4.扫描译码显示模块:将数字钟的和计时状态直观清晰的通过数码管反应出来。

课程设计报告设计题目:用VHDL语言实现数字钟的设计班级:学号:姓名:指导老师:设计时间:摘要本设计是基于VHDL语言的数字钟,硬件平台是Xilinx的Virtex2系列FPGA 开发板。

该数字钟具备预置年月日时分秒的功能,通过按键还可以改变数字钟显示的内容和进入不同的设置状态,并通过加减按键调整系统时间。

在整个VHDl数字电路系统中,采用层次化设计方法,自顶向下进行设计。

设计中根据系统的功能要求合理划分出层次,进行分级设计和仿真验证,将较为复杂的数字系统逻辑简化为基本的模型从而降低实现的难度。

工程中底层实体实现了年月日、时分秒的双向计数器功能,另外还单独设计了系统的时钟模块,用来生成周期为125Hz的按键扫描时钟和周期为1Hz单位脉冲时钟。

为了消除按键的抖动,为此设计了按键消抖模块,采用了状态机来对按键进行消抖。

为了实现根据年份和月份对当前月的天数的判断逻辑,采用了函数对该逻辑进行分析,给出正确的判断结果。

为了提高利用率,在工程中建立了一个包集文件,对底层实体进行了统一封装,方便顶层的调用。

底层的所有实体系统的顶层主要完成了底层的元件例化,主控状态机对系统的状态转换进行控制,按键响应和时钟重新分配电路则完成了整个系统的控制逻辑。

关键词:层次化设计,元件例化,函数,状态机目录摘要 (2)一、课程设计目的 (4)二、课程设计内容及其要求 (4)三、VHDL程序设计 (5)1.设计方案论证 (5)2.设计思路与方法 (6)3.VHDL源代码及其仿真结果 (7)1、六进制可逆计数器 (7)2、十进制可逆计数器, (9)3、十二进制可逆计数器, (11)4、二十四进制可逆计数器 (13)5、天数计数器 (16)6、判断闰年和月份 (18)7、时钟分频模块 (22)8、按键消抖模块 (24)9、程序包 (27)10、顶层实体(主控状态机) (29)四、编程下载 (38)五、课程设计总结 (38)六、参考文献 (38)一、课程设计目的诞生于1983年的VHDL语言,在1987年被美国国防部和IEEE指定为标准硬件描述语言。

基于VHDL数字电子钟的设计与实现摘要:本课程设计完成了数字电子钟的设计,数字电子钟是一种用数字显示秒、分、时的计时装置,由于数字集成电路技术的发展和采用了先进的石英技术,它使数字钟具有走时准确、性能稳定、携带方便等优点。

数字钟已成为人们日常生活中必不可少的必需品,广泛用于个人家庭以及办公室等公共场所,给人们的生活带来极大的方便。

在这里我们将已学过的比较零散的数字电路的知识有机的、系统的联系起来用于实际,来培养我们的综合分析和设计电路的能力。

关键词:电子钟;门电路及单次按键;琴键开关目录第一章引言----------------------------------------------------------------11.1 课题的背景、目的------------------------------------------11.2 课程设计的内容------------------------------------------1 第二章EDA与VHDL简介--------------------------------------------------22.1 EDA的介绍---------------------------------------------22.2 VHDL的介绍--------------------------------------------32.2.1 VHDL的用途与优点-----------------------------------------------------------------32.2.2 VHDL的主要特点----------------------------------------------------------------------2.2.3 用VHDL语言开发的流程------------------------------------------------------------ 第三章数字电子钟的设计方案------------------------------------------63.1秒脉冲发生器--------------------------------------------73.2可调时钟模块--------------------------------------------83.3校正电路------------------------------------------------83.4闹铃功能------------------------------------------------103.5日历系统------------------------------------------------11 第四章结束语---------------------------------------------------------------134.1致谢----------------------------------------------------144.2参考文献------------------------------------------------151引言随着科学技术的不断发展,人们对时间计量的精度要求越来越高。

1 引言随着科学技术的不断发展,人们对时间计量的精度要求越来越高。

相对机械钟而言,数字钟能实现准确计时,并显示时,分,秒,而且可以方便,准确的对时间进行调节。

在此基础上,还可以实现整点报时的功能。

因此,数字钟的应用十分广泛。

所谓数字时钟,是指利用电子电路构成的计时器。

1.1课题的背景、目的电子技术是一门应用很广,发展极为迅速的科学技术,尤其由于数字电子技术具有高抗干扰能力、更高的可靠性和便于计算机处理等特点,近年来得到更加迅速的发展,数字通讯设备、数字电视、数字照相机、数字摄象机等数字化产品近年如雨后春笋般大量涌现,数字电子技术已经成为今后电子技术发展的主要方向。

现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。

诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、定时启闭电路、定时开关烘箱、通断动力设备,甚至各种定时电气的自动启用等,所有这些,都是以钟表数字化为基础的。

因此,研究数字钟及扩大其应用,有着非常现实的意义。

通过数字时钟的设计,巩固计算机组成原理课程,理论联系实际,提高分析、解决计算机技术的实际问题的独立工作能力;掌握用VHDL语言编制简单的小型模块,学会数字钟的设计方法,熟悉集成电路的使用方法,初步掌握电子钟的设计方法并实现时间的显示和校对,以及报时的功能,并能对数字电子钟进行扩展。

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。

1.2 课程设计的内容本课程设计实现一个数字时钟,具有按秒走时功能,能够分别显示小时(2位24小时)、分钟(2位)、秒(2位)。

具有整点报时、时间调整功能,且能够对计时系统的小时、分钟进行调整。

基于 VHDL 数字电子钟的设计与实现学生:范新钧 080307039指导老师:唐飞VHDL 与单片机的关系摘要:本课程设计完成了数字电子钟的设计,数字电子钟是一种用数字显示秒、分、时的计时装置, 由于数字集成电路技术的发展和采用了先进的石英技术, 它使数字钟具有走时准确、性能稳定、携带方便等优点。

数字钟已成为人们日常生活中必不可少的必需品, 广泛用于个人家庭以及办公室等公共场所, 给人们的生活带来极大的方便。

在这里我们将已学过的比较零散的数字电路的知识有机的、系统的联系起来用于实际,来培养我们的综合分析和设计电路的能力。

关键词:电子钟;门电路及单次按键;琴键开关一 . 引言20纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高, 同时也使现代电子产品性能进一步提高, 产品更新换代的节奏也越来越快。

时间对人们来说总是那么宝贵,工作的忙碌性和繁杂性容易使人忘记当前的时间。

忘记了要做的事情, 当事情不是很重要的时候, 这种遗忘无伤大雅。

但是, 一旦重要事情, 一时的耽误可能酿成大祸。

所以, 要制作一个定时系统。

随时提醒这些容易忘记时间的人。

钟表的数字化给人们生产生活带来了极大的方便, 而且大大地扩展了钟表原先的报时功能。

诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、定时启闭电路、定时开关烘箱、通断动力设备,甚至各种定时电气的自动启用等,所有这些,都是以钟表数字化为基础的。

因此,研究数字钟及扩大其应用,有着非常现实的意义。

通过数字电子钟的设计,巩固计算机组成原理课程, 理论联系实际,提高分析、解决计算机技术的实际问题的独立工作能力;掌握用 VHDL 语言编制简单的小型模块,学会数字钟的设计方法 , 熟悉集成电路的使用方法 , 初步掌握电子钟的设计方法并实现时间的显示和校对,以及报时的功能,并能对数字电子钟进行扩展。

集成电路软件设计基于VHDL的数字电子钟系统设计学院信息工程学院班级电科1112姓名闭应明学号 2011850057 成绩指导老师卫雅芬2013 年 12 月 10 日目录一、摘要 (1)二、关键词 ............................................. 错误!未定义书签。

三、引言................................................ 错误!未定义书签。

四、设计要求........................................... 错误!未定义书签。

五、技术指标 (1)六、设计思想 (1)七、设计原理 (2)八、设计方案 (2)九、设计各个模块的功能 (3)十、各个模块的波形仿真结果 (1)十一、各个电路模块的DV综合的网标和电路模型 (12)十二、设计结果分析 (19)十三、论文结论 (20)十四、参考文献 (20)十五、附录 (21)十六、致谢 (50)一、摘要:本设计采用层次化设计方法,自顶向下进行设计。

设计中根据系统的功能要求合理划分出层次,进行分级设计和仿真验证,将较为复杂的数字系统逻辑简化为基本的模型从而降低实现的难度。

突出了其作为硬件描述语言的良好的可读性、可移植性和易理解等优点,并通过ModelSim SE 6.1完成综合、仿真。

二、关键词:Modelsim VHDL 硬件描述语言设计数字钟三、引言:硬件描述语言HDL(Hardware Description Language)是一种用形式化方法来描述数字电路和系统的语言。

目前.电子系统向集成化、大规模和高速度等方向发展,以硬件描述语言和逻辑综合为基础的自顶向下的电路设计方法在业界得到迅猛发展,VHDL在这种形势下显示出了巨大的优势,展望将来VHDL在硬件设计领域的地位将与c语言和c++在软件设计领域的地位一样,在大规模数字系统的设计中,它将逐步取代传统的逻辑状态表和逻辑电路图等硬件描述方法,而成为主要的硬件描述工具。

基于VHDL的数字电子钟系统设计数字电子钟是一种用数字电路实现的时钟系统,在现代社会逐渐普及。

在这篇文档中,我们将会讨论使用VHDL(可编程硬件描述语言) 设计数字电子钟系统的过程及其原理。

第一步是需求分析。

我们需要决定所设计的数字电子钟系统需要具备哪些功能,例如显示小时、分钟、秒数、日期、星期、闹钟等功能。

同时,还需考虑设计的电子钟具备哪些功能是其他电子钟所没有的,以增强该款电子钟的市场竞争力。

第二步是架构设计。

经过需求分析后,我们需要设计电子钟系统所需的硬件结构。

常见的电子钟由振荡器、时钟、存储器、显示器和控制接口组成。

其中,振荡器用来处理系统时基;时钟用来计时,提供系统时间;存储器负责存储显示数据和助记代码;显示器用来显示时间和日期;而控制接口则提供交互方式,如按键、通讯口等。

第三步是模块设计。

使用VHDL 可以将架构设计分解成更小的模块,进行编写和测试。

这些模块可以包括时钟模块、计数器模块、闹钟模块、数据显示模块等。

其中,时钟模块需要使用振荡器生成时钟信号,计数器模块必须进行计时,生成秒数和毫秒数的输出信号;然后,使用数码管显示模块将这些输出信号转换成可读的时间、日期和闹钟信息;再添加按键输入模块,以便用户操作和控制该电子钟系统。

第四步是系统测试。

在VHDL 设计结束后,需要对数字电子钟系统进行实际测试。

首先,系统测试需要用到仿真软件对整个系统进行验证。

同时,需要将程序下载到FPGA 芯片上,并通过硬件测试验证设计的电子钟系统是否符合需求和规范。

综上所述,设计数字电子钟系统需要遵循一定的流程,包括需求分析、架构设计和模块设计,在这个过程中也需要注重各个模块之间的兼容性和整体性。

这篇文档给大家介绍了使用VHDL 搭建数字电子钟系统的方法,希望广大读者可以从中获得借鉴。

实验名称:基于FPGA的具有闹钟和校时功能的数字钟设计一、设计内容和要求实验要求使用 VHDL进行多功能时钟的设计具体要求如下:1.能将基本的小时、分钟、及秒钟显示在数码管上。

2.能利用拨码开关进行时间的校正。

3.具有整点报时和闹钟的功能。

二、 FPGA简介以硬件描述语言(Verilog或VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至 FPGA 上进行测试,是现代 IC设计验证的技术主流。

这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。

在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块。

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配臵逻辑模块CLB(Configurable Logic Block)、输入输出模块IOB (Input Output Block)和内部连线(Interconnect)三个部分。

现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD 器件)相比,FPGA具有不同的结构。

FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。

FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

FPGA基本特点采用FPGA设计ASIC电路(专用集成电路),用户不需要投片生产,就能得到合用的芯片。

基于VHDL语言实现数字电子钟的设计一.设计要求:1、设计容选用适宜的可编程逻辑器件及外围电子元器件,设计一个数字电子钟,利用EDA软件〔QUARTUS Ⅱ〕进展编译及仿真,设计输入可采用VHDL硬件描述语言输入法〕和原理图输入法,并下载到EDA实验开发系统,连接外围电路,完成实际测试。

2、设计要求〔1〕具有时、分、秒计数显示功能。

〔2〕具有清零的功能,且能够对计时系统的小时、分钟进展调整。

〔3〕小时为十二小时制。

二.实验目的:1.通过这次EDA设计中,提高手动能力。

2.深入了解时事时钟的工作原理,以及时事时钟外围硬件设备的组成。

3.掌握多位计数器相连的设计方法。

4.掌握十进制,六进制,二十四进制计数器的设计方法。

5.继续稳固多位共阴极扫描显示数码管的驱动,及编码。

6.掌握扬声器的驱动。

7.LED灯的把戏显示。

8.掌握CPLD技术的层次化设计方法三.实验方案:数字系统的设计采用自顶向下、由粗到细, 逐步分解的设计方法, 最顶层电路是指系统的整体要求, 最下层是具体的逻辑电路的实现。

自顶向下的设计方法将一个复杂的系统逐渐分解成假设干功能模块, 从而进展设计描述, 并且应用EDA 软件平台自动完成各功能模块的逻辑综合与优化, 门级电路的布局, 再下载到硬件中实现设计。

因此对于数字钟来说首先是时分秒的计数功能,然后能显示,附带功能是清零、调整时分。

通过参考EDA 课程设计指导书,现有以下方案:1.作为顶层文件有输入端口:时钟信号,清零按键,调时按键,调分按键;输出端口有:用于接数码管的八段码输出口,扫描用于显示的六个数码管的输出口。

2.底层文件分为:〔1〕时间计数模块。

分秒计数模块计数为60计数,时计数模块为12计数。

〔2〕显示模块。

显示模块由一个六进制计数器模块和一个七段译码器组成。

进制计数器为六选一选择器的选择判断端提供输入信号, 六选一选择器的选择输出端分别接秒个位、秒十位、分个位、分十位和时个位、时十位的选通位用来完成动态扫描显示,同时依次输出秒个位、秒十位、分个位、分十位和时个位、时十位数向给译码模块。

基于vhdl的电子闹钟设计基于VHDL的电子闹钟设计电子闹钟是我们日常生活中常用的物品之一,在我们每天的生活中起着非常重要的作用。

现在,大量人们自己亲手打造自己的电子闹钟,这已经成为一种流行的风潮。

其中一种制作闹钟的方法就是使用VHDL语言进行设计,在这里我们将介绍基于VHDL的电子闹钟的设计。

VHDL的定义VHDL是“可综合的硬件描述语言”的缩写,其对于电子器件的设计和工程制造具有极大的重要性。

VHDL可以直接描述数字电路,然后通过其编译器和模拟器生成对应的硬件电路。

它是在20世纪80年代产生的,在当时风靡一时,并且现在仍然是电路仿真和设计过程中的重要工具。

闹钟设计一块基于FPGA开发板上的闹钟的设计步骤从以下几个方面进行:模块划分根据闹钟的功能划分模块,这些模块可以包括:时钟模块(时钟、分钟、秒钟、时令),轮询模块(轮询时钟模块,测量按键状态),SDRAM芯片(用来存储当前时间和闹钟时间),闹铃模块(识别达到设定时间的闹钟)。

时钟模块时钟模块是一个非常重要的模块。

时钟的频率由外部电源提供,频率通常为50Hz,可以通过PLL进行锁相放大处理来获取1秒的时钟信号。

时钟信号用于计算当前时间和闹钟时间。

模块中还必须包括一个开关,在程序中用来控制时钟的启停,以及计时和控制亮度的显示屏。

轮询模块轮询模块用来轮询时钟模块和按键状态。

通过轮询时钟模块,我们可以获取当前时间,并存储在SDRAM芯片中。

同时,我们也可以通过轮询按键状态来检测用户是否更改了设置,如设定时间、闹钟时间和亮度等。

SDRAMSDRAM芯片的作用是用来存储当前时间和闹钟时间。

需要的RAM空间相当小,只需要一些字节就足够了。

因此,常用的8位RAM芯片足以实现此目的。

闹铃模块闹铃模块用于识别设定时间是否和当前时间相同,并在正确的时间触发闹钟响铃。

当闹钟时间到来时,闹铃模块会向用户发出闹钟信号,通过控制LED灯来让用户知道是闹钟响了。

要注意的是,该模块必须在程序运行时轮询保持警醒状态。

摘要摘要随着EDA技术的发展和应用领域的扩大与深入,EDA技术在电子信息、通信、自动控制及计算机应用领域的重要性日益突出。

EDA技术就是依赖功能强大的计算机,在EDA工具软件平台上,对以硬件描述语言VHDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

本文介绍了基于VHDL硬件描述语言设计的多功能数字闹钟的思路和技巧。

在Quartus 11开发环境中编译和仿真了所设计的程序,并逐一调试验证程序的运行状况。

仿真和验证的结果表明,该设计方法切实可行,该数字闹钟可以实现调时定时闹钟播放音乐功能具有一定的实际应用性。

关键词:闹钟 FPGA VHDL目录目录摘要............................................................................................................................. I 目录.......................................................................................................................... III 第一章选题背景.. (1)1.1选题研究内容 (1)1.2课题研究功能 (1)1.3课题相关技术应用 (1)第二章FPGA 简介 (3)2.1FPGA概述 (3)2.1.1 FPGA基本结构 (3)2.2FPGA编程原理 (3)2.3FPGA设计流程 (4)第三章数字闹钟整体方案设计 (7)3.1数字闹钟整体设计 (7)3.1.1数字闹钟各部分作用 (7)3.2数字钟的工作原理 (7)第四章模块电路设计 (9)4.1模块电路图设计 (9)4.2各模块电路设计 (9)第五章实验结果 (16)5.1实验概述 (16)5.2实验仿真结果 (16)第六章总结与展望 (18)研究结论 (18)研究展望 (18)致谢 (20)参考文献 (22)附录1 部分模块代码 (24)附录2 动态扫描模块程序 (33)目录第一章选题背景第一章选题背景1.1选题研究内容设计一个24小时的闹钟,该闹钟由显示屏、数字键、TIME键、ALARM键、扬声器组成。

二、试验项目名称:基于vhdl语言的数码管时钟设计三、实验目的:利用FPGA开发板上的数码管,晶振等资源设计出能够显示时、分、秒的时钟。

四、实验内容及原理:(一)、综述本实验目标是利用FPGA逻辑资源,编程设计实现一个数字电子时钟。

实验环境为fpga开发板。

电路设计采用VHDL硬件描述语言编程实现,开发软件为ise7.1i。

(二)、模块框架设计计数时钟由模为60的秒计数器模块、模为60的分计数模块、模为24的小时计数器模块、此外还有最后的数码管显示模块。

1.综合计时模块包括计时及进位两个进程,实现时钟逻辑功能。

2.显示模块将时钟的每次变化所对应的时间及时输出到数码管上。

实质为数码管译码器。

(三)、VHDL编程与仿真:1、各个进程模块以下三个process分别为分频,进位以及计时进程。

分频进程用于统计CLK输入信号输出完整的1秒。

进位进程控制60进制,60进制和24进制的进位关系。

计时进程用于实现电子时钟的基本计时功能,即每秒均变化。

---------------------分频部分-----------------process(clk,reset)beginif(reset='0')thencnt<=0;elsif(clk'event and clk='1')thencnt<=cnt+1;if(cnt=50000000)then ----开发板晶振50M,统计到此时为1S cnt<=0;end if;end if;end process;------------------------------------------------进位共包括秒个位向秒十位进位,秒十位向分个位进位,分个位向分十位进位,分十位向时个位进位,时个位向时十位进位。

根据进位规则则可以实现从0时0分0秒到23时59分59秒之间任意时刻的显示。

-------------各位的进位标志--------------------------process(clk,reset)beginif reset='0'thenjinwei<="000000";elsif clk'event and clk='1'thenif dataout_buf(0)=9 thenjinwei(0)<='1'; -----9S时向秒十位进位------elsejinwei(0)<='0';end if;if(jinwei(0)='1'and dataout_buf(1)=5)thenjinwei(1)<='1'; ------59S时向分个位进位------- elsejinwei(1)<='0';end if;if(jinwei(1)='1' and dataout_buf(3)=9)thenjinwei(2)<='1'; -----9分且秒十位进位时向分十位进位elsejinwei(2)<='0';end if;if(jinwei(2)='1' and dataout_buf(4)=5)thenjinwei(3)<='1'; -----分十位为5且分个位进位时向时个位进位elsejinwei(3)<='0';end if;if(jinwei(3)='1' and dataout_buf(6)=9)thenjinwei(4)<='1'; ----时个位为9且分十位进位时向时十位进位elsejinwei(4)<='0';end if;if(jinwei(4)='1' and dataout_buf(6)=2 and dataout_buf(7)=1)then jinwei(5)<='1'; ----到12时且时个位进位时标记最高标记位elsejinwei(5)<='0';end if;end if;end process;---------------------------------------------------计数进程,其进程逻辑上受分频输出与进位控制,当分频输出变化(即每秒),秒个位自加,当满足进位条件时,调用进位规则,进行时间的跳转。

第2期气象水文海洋仪器N o .22008年6月M eteoro log ica,l H ydro l og ical and M ar i ne Instru m entsJ une 2008收稿日期:2007-11-12.作者简介:张子刚(1974-),男,硕士,讲师.主要研究方向:电子设计自动化.基于VHDL 的数字时钟的设计张子刚1,卢 戈2,田 鹏1(11装甲兵技术学院,长春130117;2165043部队,吉林132011)摘 要:随着EDA 技术的发展和应用领域的扩大与深入,EDA 技术在电子信息、通信、自动控制及计算机应用领域的重要性日益突出。

EDA 技术就是依赖功能强大的计算机,在EDA 工具软件平台上,对以硬件描述语言VHDL 为系统逻辑描述手段完成的设计文件,自动地完成逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

本文介绍了基于VHDL 硬件描述语言设计的多功能数字时钟的思路和技巧。

在Quartus Ò开发环境中编译和仿真了所设计的程序,并逐一调试验证程序的运行状况。

仿真和验证的结果表明,该设计方法切实可行,该数字时钟具有一定的实际应用性。

关键词:数字时钟;VH DL ;Quartus Ò中图分类号:TN 702 文献标识码:A 文章编号:1006-009X(2008)02-0010-05D esign of digital cl ock based on VHDLZhang Z-i gang 1,Lu Ge 2,T ian Peng1(11A rmor T echnique Instit ute of PLA 1,Changchu 130117,China ;2165043T roop J ilin 132011,China )Abst ract :W ith t h e deve l o p m ent o fEDA techno logy and expansi o n and deepen of app li c ation ,EDA techno logy has beco m e m ore and m ore i m portant i n electronic i n for m ation ,co mmunicati o ns ,auto m ati c contro l and co m puter app licati o ns .EDA techno logy depends on po w erf u l co m puters ,co m plete l o g ic opti m izati o n and si m ulation tests of desi g n docum ents by m eans o fm ak i n g har dw are descripti o n language VHDL as the syste m log ic descr i p tion au to m aticall y i n EDA tools so ft w are platfor m ,until it has ach ieved t h e f u ncti o n o f established electr onic circu its syste m.I n th is paper ,w e have i n troduced i d eas and crafts m anship ofm ult-i function dig ita l clock desi g n based on VHDL hardw are descri p tion l a nguage .Co mp ile and si m u late desi g ned procedures i n Quartus Òdeve l o pm ent env ironm ent and debug and verify each o f t h e operation of prog ra m.Si m u lation and ver ify results sho w that th i s desi g n is wo r kable and this d i g ital clock is practica.l K ey w ords :d i g ital clock ;VHDL;Quart u s Ò 随着电子设计自动化(EDA )的高速发展,电子系统的设计技术和工具发生了深刻的变化。

vhdl设计实例VHDL设计实例:数字电子钟引言:数字电子钟是一种常见的电子设备,用于显示当前时间。

本文将介绍如何使用VHDL设计一个简单的数字电子钟。

一、设计概述数字电子钟由时钟模块、数码管显示模块和控制模块组成。

时钟模块用于生成计时脉冲,数码管显示模块用于将时钟模块输出的计时脉冲转换为对应的数字显示,控制模块用于调整时钟和设置时间。

二、时钟模块设计时钟模块是整个电子钟的核心,它需要能够精确地生成计时脉冲。

使用VHDL语言,可以使用计数器和时钟分频器实现时钟模块。

计数器用于计数,时钟分频器用于将计数器的输出分频为1秒钟一次的脉冲。

三、数码管显示模块设计数码管显示模块用于将时钟模块输出的计时脉冲转换为数字显示。

在数码管显示模块中,每个数码管对应一个数字显示,通过切换不同的数码管,可以实现显示小时、分钟和秒钟。

使用VHDL语言,可以使用多路复用器和BCD转换器实现数码管显示模块。

四、控制模块设计控制模块用于调整时钟和设置时间。

通过增加按钮和减少按钮,可以实现调整时钟的功能。

通过设置按钮,可以进入设置时间的模式,并通过增加按钮和减少按钮设置小时、分钟和秒钟。

使用VHDL语言,可以使用状态机实现控制模块。

五、测试与验证在设计完成后,需要进行测试和验证。

可以使用仿真工具对设计的各个模块进行仿真,验证其功能是否正常。

同时,还可以将设计烧录到FPGA开发板上进行实际测试,确保数字电子钟能够正常工作。

六、总结本文以VHDL设计实例为题,详细介绍了数字电子钟的设计过程。

通过时钟模块、数码管显示模块和控制模块的设计,实现了一个简单的数字电子钟。

通过测试和验证,确保了设计的正确性和可靠性。

希望本文对读者理解VHDL设计实例并进行创作有所帮助。

通过自己的实践和研究,不断探索和创新,可以设计出更多实用的数字电子设备。

让我们一起努力,推动数字电子技术的发展!。

基于VHDL的数字电子钟设计摘要:在简要介绍了EDA技术特点的基础上,用EDA技术作为开发手段,采用了顶层图形设计思想,基于硬件描述语言,以可编程器件为核心,实现计时24小时的电子时钟的设计。

关键字:EDA 电子时钟 CPLD VHDL引言:现代电子技术的核心是EDA(Electronic Design Automation)技术。

EDA技术就是依靠功能强大的电子计算机,在EDA工具软件平台上,对硬件描述语言HDL(Hardware Description Language)为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、分割、综合、优化、仿真,直到下载到可编程逻辑器件CPLD/FPGA或专用集成电路ASIC(Application Specific Integrated Circuit)芯片中,实现既定的电子电路设计功能。

EDA技术使得电子电路设计者的工作仅限于利用硬件描述语言和EDA软件平台来完成对系统硬件功能的实现,极大地提高了设计效率,缩短了设计周期,节省了设计成本。

EDA是在20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

一般把EDA 技术的发展分为CAD、CAE和EDA这三个阶段。

20世纪90年代以来,微电子工艺有了惊人的发展,2006年工艺水平已经达到了60nm,目前正向45nm迈进。

大容量的可编程逻辑器件陆续面世,对电子设计的工具提出了更高的要求,提供了广阔的发展空间,促进了EDA技术的新成。

特别重要的是,世界各EDA公司致力推出兼容各种硬件实现方案和支持标准硬件描述语言的EDA工具软件,有效地将EDA技术推向成熟。

一般情况下EDA软件我们使用Quartus II或Max+plux II,它们的设计流程为:1)编辑设计图形文件2)编译设计文件3)仿真设计文件4)编程下载设计文件一.设计要求设计一个电子钟,要求可以显示时、分、秒,用户可以设置时间.二.实验目的1. 掌握多位计数器相连的设计方法。

目录之答禄夫天创作1 概述数字钟电路的基本结构由两个60进制计数器和一个24进制计数器组成,分别对秒、分、小时进行计时,当计时到23时59分59秒时,再来一个计数脉冲,则计数器清零,重新开始计时。

秒计数器的计数时钟CLK为1Hz的尺度信号,可以由晶振发生的50MHz信号通过分频得到。

当数字钟处于计时状态时,秒计数器的进位输出信号作为分钟计数器的计数信号,分钟计数器的进位输出信号又作为小时计数器的计数信号,每一秒钟发出一个中断给CPU,CPU 采取NIOS,它响应中断,并读出小时、分、秒等信息。

CPU对读出的数据译码,使之动态显示在数码管上。

1.2 设计任务设计一个基于VHDL的数字时钟,具体功能要求如下:1.在七段数码管上具有时--分--秒的依次显示。

2.时、分、秒的个位记满十向高位进一,分、秒的十位记满五向高位进一,小时按24进制计数,分、秒按60进制计数。

3.整点报时,当计数到整点时扬声器发出响声。

4.时间设置:可以通过按键手动调节秒和分的数值。

此功能中可通过按键实现整体清零和暂停的功能。

5.LED灯循环显示:在时钟正常计数下,LED灯被依次循环点亮。

2 系统总体方案设计设计一个基于VHDL的数字时钟,我采取自顶向下分模块的设计。

底层为实现个弄能的模块,各模块由vhdl语言编程实现:顶层采取原理图形式调用。

其中底层模块包含秒、分、时三个计数器模块、按键去抖动模块、按键控制模块、时钟分频模块、数码管显示模块共7个模块。

设计框图如下:由图可以清晰的看到数字钟系统设计中各功能模块间连接关系。

系统时钟50MHZ经过分频后发生1秒的时钟信号,1秒的时钟信号作为秒计数模块的输入信号,秒计数模块发生的进位信号作为分计数模块的输入信号,分计数模块的进位信号作为时计数模块的输入信号。

秒计数模块、分计数模块、时计数模块的计数输出分别送到显示模块。

由于设计中要使用按键进行调节时间,而按键的动作过程中存在发生得脉冲的不稳定问题,所以就牵扯到按键去抖动的问题,对此系统中设置了按键去抖动模块,按键去抖动模块发生稳定的脉冲信号送入按键控制模块,按键控制模块根据按键的动作对秒、分、时进行调节。

基于VHDL数字电子钟的设计与实现学生:范新钧080307039指导老师:唐飞VHDL 与单片机的关系摘要:本课程设计完成了数字电子钟的设计,数字电子钟是一种用数字显示秒、分、时的计时装置,由于数字集成电路技术的发展和采用了先进的石英技术,它使数字钟具有走时准确、性能稳定、携带方便等优点。

数字钟已成为人们日常生活中必不可少的必需品,广泛用于个人家庭以及办公室等公共场所,给人们的生活带来极大的方便。

在这里我们将已学过的比较零散的数字电路的知识有机的、系统的联系起来用于实际,来培养我们的综合分析和设计电路的能力。

关键词:电子钟;门电路及单次按键;琴键开关一. 引言20纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

时间对人们来说总是那么宝贵,工作的忙碌性和繁杂性容易使人忘记当前的时间。

忘记了要做的事情,当事情不是很重要的时候,这种遗忘无伤大雅。

但是,一旦重要事情,一时的耽误可能酿成大祸。

所以,要制作一个定时系统。

随时提醒这些容易忘记时间的人。

钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。

诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、定时启闭电路、定时开关烘箱、通断动力设备,甚至各种定时电气的自动启用等,所有这些,都是以钟表数字化为基础的。

因此,研究数字钟及扩大其应用,有着非常现实的意义。

通过数字电子钟的设计,巩固计算机组成原理课程,理论联系实际,提高分析、解决计算机技术的实际问题的独立工作能力;掌握用VHDL语言编制简单的小型模块,学会数字钟的设计方法,熟悉集成电路的使用方法,初步掌握电子钟的设计方法并实现时间的显示和校对,以及报时的功能,并能对数字电子钟进行扩展。

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。

数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

因此,此次设计与制作数字钟就是为了了解数字钟的原理,从而学会制作数字钟.而且通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法.且由于数字钟包括组合逻辑电路和时叙电路.通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法1.2 课程设计的内容本次设计以数字电子为主,实现对时、分、秒、星期数字显示的计时装置,周期为243要采用中规模CMOS 集成电路.本系统的设计电路由脉冲逻辑电路模块、时钟脉冲模块、电源模块、时钟译码显示电路模块、整点报时模块、校时模块、星期模块等几部分组成。

采用电池作电源,采用低功耗的CMOS芯片及液晶显示器,发生器使用晶体振荡、计数振荡器CD4060及双JK触发器CD4027,将标准秒信号送入“秒计数器”;计数器采用“可予制四位二进制异步清除”计数器来实现,分别组成两个六十进制(秒、分)、一个二十四进制(时)的计数器;整电报时电路以门电路、触发器及扬声器构成,要求在离整点差5秒时,每1秒钟鸣叫一次,共响5次,前四次为低音512Hz,最后一声为高音1024Hz;星期计数器是用四个D触发器组成;校时电路是由与非门构成的双稳态触发器,用来对“星期”、“时”、“分”、“秒”显示数字进行调整的;译码显示电路选用BCD-7段锁存译码/驱动器CC4511构成,再经过设计一个电子钟,具有时、分、秒显示功能,在计时过程中具有报时功能,同时能对时、分进行校对,在使用74LS290输入脉冲时能够显示一周的星期,具有一分钟闹铃功能.实验仪器: 74LS161(7片),74LS48(BCD_7段译码器), 74LS29(4片),门电路及单次按键,琴键开关2.VHDL的介绍1)VHDL语言超高速集成电路硬件描述语(VHSIC Hardware Deseription Language,简称VHDL),是IEEE的一项标准设计语言。

它源于美国国防部提出的超高速集成电路(Very High Speed Integrated Circuit,简称VHSIC)计划,是ASIC设计和PLD设计的一种主要输入工具。

1987年底,VHDL被IEEE和美国国防部确认为标准硬件描述语言。

自IEEE公布了VHDL的标准版本,IEEE-1076(简称87版)之后,各EDA公司相继推出了自己的VHDL设计环境,或宣布自己的设计工具可以和VHDL接口。

此后VHDL在电子设计领域得到了广泛的接受,并逐步取代了原有的非标准的硬件描述语言。

1993年,IEEE对VHDL进行了修订,从更高的抽象层次和系统描述能力上扩展VHDL 的内容,公布了新版本的VHDL,即IEEE标准的1076-1993版本,(简称93版)。

现在,VHDL和Verilog 作为IEEE的工业标准硬件描述语言,又得到众多EDA公司的支持,在电子工程领域,已成为事实上的通用硬件描述语言。

有专家认为,在新的世纪中,VHDL于Verilog语言将承担起大部分的数字系统设计任务。

2.2.1 VHDL的用途与优点VHDL主要用于描述数字系统的结构,行为,功能和接口。

VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可是部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。

在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。

这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。

应用VHDL进行工程设计的优点是多方面的。

(1)与其他的硬件描述语言相比,VHDL具有更强的行为描述能力,从而决定了他成为系统设计领域最佳的硬件描述语言。

强大的行为描述能力是避开具体的器件结构,从逻辑行为上描述和设计大规模电子系统的重要保证。

(2)VHDL丰富的仿真语句和库函数,使得在任何大系统的设计早期就能查验设计系统的功能可行性,随时可对设计进行仿真模拟。

(3)VHDL语句的行为描述能力和程序结构决定了他具有支持大规模设计的分解和已有设计的再利用功能。

符合市场需求的大规模系统高效、高速的完成必须有多人甚至多个代发组共同并行工作才能实现。

(4)对于用VHDL完成的一个确定的设计,可以利用EDA工具进行逻辑综合和优化,并自动的把VHDL 描述设计转变成门级网表。

(5)VHDL对设计的描述具有相对独立性,设计者可以不懂硬件的结构,也不必管理最终设计实现的目标器件是什么,而进行独立的设计。

2)VHDL语言开发的流程(1)文本编辑:用任何文本编辑器都可以进行,也可以用专用的HDL编辑环境。

通常VHDL文件保存为.vhd文件。

(2)功能仿真:将文件调入HDL仿真软件进行功能仿真,检查逻辑功能是否正确(也叫前仿真,对简单的设计可以跳过这一步,只在布线完成以后,进行时序仿真)。

(3)逻辑综合:将源文件调入逻辑综合软件进行综合,即把语言综合成最简的布尔表达式和信号的连接关系。

逻辑综合软件会生成.edf(edif)的EDA工业标准文件。

(4)布局布线:将.edf文件调入PLD厂家提供的软件中进行布线,即把设计好的逻辑安放到PLD/FPGA内。

(5)编程下载:确认仿真无误后,将文件下载到芯片中。

3.数字电子时钟的设计方案3.1设计规划系统的工作原理:振荡器产生稳定的分频脉冲信号,作为数字钟的时间基准,然后经过分频器输出标准秒脉冲。

秒计数器满60分向分计数器进位,分计数器满60后向小时计数器进位,小时计数器按照“24翻1”规律计数。

计数器的输出分别由译码器送显示器显示。

计时出现误差时,可以用校时电路校时、校分。

数字电子钟的电路组成方框图片如下:图3.1 数字电子钟的电路组成方框图硬件电路的设计:如图3.1所示,以74LS161作为控制部件。

47LS161被接成十进制计数器,其置数输入端A、B、C、D(3脚4脚5脚6脚)接低电平,LD、EP、ET(9脚10脚7脚)接高电平,秒脉冲由CP(2脚)端输入。

计数器的输出端QA、QB、QC、QD(14脚13脚12脚11脚)接译码电路CD4511的输入端D、C、B、A。

用74LS290做一个七进制的加法计数器,将时的十位的进位脉冲接到显示星期的74LS290的输入脉冲就可以了。

硬件电路图如下:图3.2 硬件电路图软件电路的设计:考虑到实用性,在该电子钟的设计中修改定时或调整时间时采用了闪烁。

在编程上,首先进行了初始化定义了程序的入口地址以及中断的入口地址,在主程序的开始定义了一组固定单元用来存储计数的秒,分,时等。

在显示程序段中主要进行了闪烁的处理,采用定时器中断置标志位,再与位选相互结合的方法来控制调时或定时中的闪烁。

时、分、秒的显示则是用了软件译码 (查表 )的方式,再用了一段固定的程序段进行进制转化。

初始化之后,用中断方式对其计数,计数的同时采用了定时器比较的方法,比较当前计数时间与定时时间是否相等,若相等则将闹铃标志位置数。

为了避免响铃影响显示定时,选时或调时程序段。

对当前时间或定时时间修改后又返回到最初的显示程序段,如此循环下去。

程序流程图如图所示。

74LS48时钟基准74LS29晶体振荡器LED 数码管74LS161图3.3 程序流程图3.2 各模块原理及程序3. 2.1秒脉冲发生器秒脉冲发生器是数字钟的重要部分,它的精度稳定度决定了数字钟的质量,通常用晶体振荡器发生的脉冲经过整形、分频获得1Hz 的秒脉冲。

如晶振为32768Hz ,通过15次二分频后可获得1Hz 的脉冲输出。

(本实验中实验箱上已经有1hz 脉冲)。

按键由琴键或拨码开关发出脉冲或电平信号,控制整个系统工作。

原理图如下:响铃结束显示初始化TF 读键有无闹钟?是否为调时、定时?开始TT定时FF调时TF调时?是否修改?其程序代码如下:ORG 0000HAJMP MAINORG 000BHAJMP TIMEORG 0300HMAIN:mov 20h,#00hMOV 21H,#00HMOV 22H,#00HMOV 23H,#00HMOV IP,#02H ;IP,IE初始化MOV IE,#82HMOV TMOD,#01H ;设定定时器工作方式?MOV TL0,#0B0HMOV TH0,#3CHSETB TR0 ;启动定时?MOV SP,#40H ;重设堆栈指针NEXT: LCALL DISP ;调用显示子程序?LCALL KEY ;调用按键检测子程序JZ NEXT ;LCALL ANKEY ;调用按键处理子程序SJMP NEXT ;重新循环NOPNOPNOP3.2.2可调时钟模块有了时间标准“秒”信号后,就可以根据60秒为1分、60分为1小时、24小时为1天的计数周期,分别组成两个六十进制(秒、分)、一个二十四进制(时)的计数器。