Six-Pole_Bandpassfilter_with_Single_Cross-Coupling

- 格式:pdf

- 大小:801.13 KB

- 文档页数:12

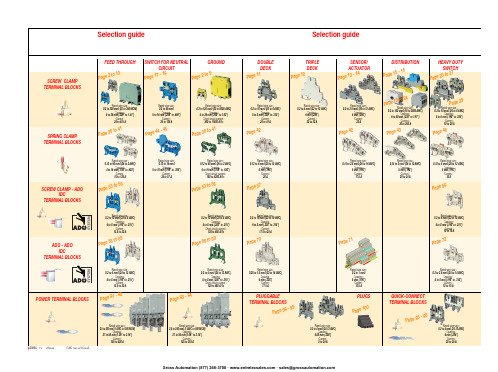

ABB EntrelecSommaireBU0402061SNC 160 003 C0205SummarySelection guide ....................................................................................page 1Screw clamp ........................................................................................page 2Feed through and ground terminal blocks .......................................................page 2 - 5 to 10Single pole, multiclamp terminal blocks..........................................................................page 4Feed through terminal blocks - Double-deck................................................................page 11Feed through terminal blocks - Triple-deck...................................................................page 12Three level sensor, terminal blocks without ground connection...................................page 13Three level sensor, terminal blocks with ground connection ........................................page 14Terminal blocks for distribution boxes, double deck + protection .......................page 15 - 16Interruptible terminal blocks for neutral circuit......................................................page 17 - 18Distribution : phase, ground terminal blocks .......................................................page 19 to 21Single pole or four pole distribution blocks..........................................................page 22 to 24Heavy duty switch terminal blocks with blade......................................................page 25 - 26Heavy duty switch terminal blocks with push-turn knob..............................................page 26Heavy duty switch terminal blocks with contact control pull lever...............................page 29Heavy duty switch terminal blocks with blade - Double-deck .....................................page 27Fuse holder terminal blocks for 5x20 mm (.197x.787 in.) and 5x25 mm (.197x.984 in.)or 6.35x25.4 mm (1/4x1 in.) and 6.35x32 mm (1/4x11/4 in.) fuse s.........................................page 28 - 29Fuse holder terminal blocks for 5x20 mm (.197x.787 in.) and 5x25 mm (.197x.984 in.) fuses -Double-dec k.....................................................................................................................page 27Terminal blocks for test circuits with sliding bridge ......................................................page 30Terminal blocks for metering circuits.............................................................................page 31ESSAILEC terminal blocks.............................................................................................page 32Safety connection terminal blocks ................................................................................page 33Miniblocks for EN 50045 (DIN 46277/2) rail ..........................................................page 34 - 35Spring clamp ......................................................................................page 36Angled terminal blocks - Feed through and ground .....................................................page 36Feed through and ground terminal blocks ...........................................................page 37 to 41Feed through terminal blocks - Double deck ................................................................page 42Terminal blocks for sensors / actuators ........................................................................page 42Terminal blocks for distribution boxes...........................................................................page 43Switch terminal blocks for neutral conductor........................................................page 44 - 45Heavy duty switch terminal blocks with blade..............................................................page 46Fuse holder terminal blocks for 5x20 mm (.197x.787 in.) and 5x25 mm (.197x.984 in.) fuse s....page 47Miniblocks Spring clamp ......................................................................................page 48 to 52ADO - Screw clamp ...........................................................................page 53Feed through and ground terminal blocks ...........................................................page 53 to 56Feed through and ground terminal blocks - Double-deck............................................page 57Heavy duty switch terminal blocks with blade..............................................................page 58Fuse holder terminal blocks for 5x20 mm (.197x.787 in.) and 5x25 mm (.197x.984 in.) fuse s ......page 59 - 60Miniblocks ADO - Screw clamp............................................................................page 61 to 65ADO - ADO .........................................................................................page 66Feed through and ground terminal blocks ...........................................................page 66 to 69Feed through and ground terminal blocks - Double-deck............................................page 70Terminal blocks for sensors / actuators ........................................................................page 71Heavy duty switch terminal blocks with blade..............................................................page 72Fuse holder terminal blocks for 5x20 mm (.197x.787 in.) and 5x25 mm (.197x.984 in.) fuse s ......page 73 - 74Miniblocks ADO - ADO .........................................................................................page 75 to 79Accessories ADO ...........................................................................................................page 80Power terminal blocks .............................................................page 81 to 84Quick-connect terminal blocks .................................................page 85 - 86Terminal blocks for railway applications ................................page 87 to 97Pluggable terminal blocks .....................................................page 98 to 100Accessories......................................................................................page 101Marking..................................................................................page 102 to 104GrossAutomation(877)268-3700··*************************PR30PR3.Z2PR3.G2PR5PR4PR1.Z2Rated wire size :Rated wire size :Rated wire size :Rated wire size :Mounting railsShield terminals forcollector barMarking tableHorizontal Rated wire size :0.5 to 16 mm² (22 to 8 AWG)Rated wire size :Rated wire size :Rated wire size :P a g e t o 29e30 t o 32ag e e3P a ge 8 t o 60a g e6t o 6574P a ge 7 t o 79P a ge 9P a g P a gGrossAutomation(877)268-3700··*************************2ABB Entrelecd010830402051SNC 160 003 C0205MA 2,5/5 - 2.5 mm² blocks - 5 mm .200" spacingAccessoriesGrossAutomation(877)268-3700··*************************3ABB Entrelec D010740402051SNC 160 003 C0205M 4/6 - 4 mm² blocks - 6 mm .238" spacingAccessoriesGrossAutomation(877)268-3700··*************************4ABB EntrelecD011030402051SNC 160 003 C0205M 4/6.3A - 4 mm² blocks - 6 mm .238" spacingM 4/6.4A - 4 mm² blocks - 6 mm .238" spacingGrossAutomation(877)268-3700··*************************5ABB Entrelec D010840402051SNC 160 003 C0205M 6/8 - 6 mm² blocks - 8 mm .315" spacingAccessoriesGrossAutomation(877)268-3700··*************************6ABB EntrelecD010850402051SNC 160 003 C0205M 10/10 - 10 mm² blocks - 10 mm .394" spacingAccessoriesGrossAutomation(877)268-3700··*************************7ABB Entrelec D010860402051SNC 160 003 C0205M 16/12 - 16 mm² blocks - 12 mm .473" spacingAccessoriesGrossAutomation(877)268-3700··*************************8ABB EntrelecD010870402051SNC 160 003 C0205M 35/16 - 35 mm² blocks - 16 mm .630" spacingGrossAutomation(877)268-3700··*************************M 95/26 - 95 mm² blocks - 26 mm 1.02" spacingM 70/22.P - 70 mm² ground block with rail contact - 22 mm .630" spacingSelection35 mm / 1.37"12 mm / 0.47"14-30 Nm / 124-260 Ib.in 1.2-1.4 Nm / 10.6-12.3 Ib.in1000600600415400400577070240 mm 2500 MCM 500 MCM 10 mm 2 6 AWG 6 AWG IEC UL CSANFC DIN0.5 - 160.5 - 100 AWG-600 MCM 2 AWG-500 MCM 50 - 30035 - 24018-6 AWGD 150/31.D10 - 150 mm² blocks - 31 mm 1.22" spacingCharacteristicsD 240/36.D10 - 240 mm² blocks - 36 mm 1.41" spacingSelectionWire size main circuit mm² / AWG VoltageV Current main circuit A Current outputARated wire size main circuit mm² / AWG Rated wire size outputmm² / AWG Wire stripping length main circuit mm / inches Wire stripping length output mm / inches Recommended torque main circuit Nm / Ib.in Recommended torque outputNm / Ib.inSolid Stranded Solid Stranded Wire size output mm² / AWG9.5 mm / .37"0.5-0.8 Nm / 4.4-7.1 Ib.in5003003003220204 mm 212 AWG12 AWG0.2 - 422-12 AWG 22-12 AWG 0.22 - 4IEC ULCSANFC DINCharacteristicsWire size mm² / AWGSolid Stranded D 4/6.T3 - 4 mm² blocks - 6 mm .238" spacingSelectionVoltage V CurrentARated wire sizemm² / AWG Wire stripping length mm / inches Recommended torqueNm / Ib.inM 4/6.T3.P - 4 mm² block - 6 mm .238" spacingD 2,5/6.D - 2.5 mm² blocks - 6 mm .238" spacingD 2,5/6.DL - 2.5 mm² blocks - 6 mm .238" spacingD 2,5/6.DPA1 - 2.5 mm² blocks - 6 mm .238" spacingD 2,5/6.DPAL1 - 2.5 mm² blocks - 6 mm .238" spacingD 4/6... - 4 mm² blocks - 6 mm .238" spacingD 4/6.LNTP - 4 mm² closed blocks - 17.8 mm .700" spacingMA 2,5/5.NT- 2.5 mm² block - 5 mm .200" spacingAccessories**SFB2 : 16 to 35 mm² 6 to 2 AWG H= 3 mm/.12"M 10/10.NT- 10 mm² block - 10 mm .394" spacingAccessories(1) Except for M 35/16 NT (closed block)*SFB1 : 0.5 to 35 mm² 18 to 2 AWG H= 7 mm/.28"**SFB2 : 16 to 35 mm² 6 to 2 AWG H= 3 mm/.12"MB 4/6... - 4 mm² blocks - 6 mm .238" spacingMB 6/8... - 6 mm² blocks - 8 mm .315" spacingMB 10/10... - 10 mm² blocks - 10 mm .394" spacingBRU 125 A - 35 mm² block - 27 mm 1.063" spacingBRU 160 A - 70 mm² block - 35.2 mm 1.388" spacingBRU 250 A - 120 mm² blocks - 44.5 mm 1.752" spacingBRU 400 A - 185 mm² block - 44.5 mm 1.752" spacingAccessoriesAccessoriesBRT 80 A - 16 mm² block - 48 mm 1.89" spacingBRT 125 A - 35 mm² block - 48 mm 1.89" spacingBRT 160 A - 50 mm² block - 50 mm 1.97" spacing9.5 mm / .37"0.5-0.6 Nm / 4.4-5.3 Ib.in4003003002010104 mm 210 AWG 12 AWG 0.5 - 422-10 AWG20-12 AWG0.5 - 2.5IEC ULCSANFC DINMA 2,5/5.SNB - 2.5 mm² blocks - 5 mm .200" spacingCharacteristicsM 4/6.SNB - 4 mm² blocks - 6 mm .238" spacingSelectionWire size mm² / AWGVoltage V CurrentARated wire sizemm² / AWG Wire stripping length mm / inches Recommended torqueNm / Ib.inSolid StrandedM 6/8.SNB - 6 mm² blocks - 8 mm .315" spacing - blade switchingSelectionAccessoriesM 4/8.D2.SF - for fuses 5x20 mm .197x.787 in. and 5x25 mm .197x.984 in. -4 mm² blocks - 8 mm .315" spacingM 4/6.D2.SNBT - 4 mm² blocks - 6 mm .238" spacing - blade switchM 4/8.SF- 4 mm² blocks - 8 mm .315" spacingM 4/8.SFL - 4 mm² blocks - 8 mm .315" spacing12 mm / .472"1.2-1.4 Nm / 10.6-12.3 Ib.in800(1)60060016252510 mm 210 AWG8 AWG0.5 - 1622-10 AWG 22-8 AWG 0.5 - 10IEC ULCSANFC DINCBD2SML 10/13.SF - for fuses 6.35x25.4 mm 1/4x1 in. and 6.35x32 mm 1/4x11/4 in. -10 mm² blocks - 13 mm .512" spacingSelectionAccessoriesCharacteristicsWire size mm² / AWGVoltage V CurrentARated wire sizemm² / AWG Wire stripping length mm / inches Recommended torqueNm / Ib.inSolid Stranded (1) Insulation voltage of terminal block - operating voltage : according to fuse.M 4/6.D2.2S2... - 4 mm² blocks - 6 mm .238" spacing11 mm / .43"0.8-1 Nm / 7.1-8.9 Ib.in50060030306 mm 28 AWG0.5 - 1022-8 AWG0.5 - 6IECULCSANFC DINM 6/8.ST... - 6 mm² blocks - 8 mm .315" spacingCharacteristicsWire size mm² / AWGVoltage V CurrentARated wire sizemm² / AWG Wire stripping length mm / inches Recommended torqueNm / Ib.inSolid Stranded M 6/8.STA - 6 mm² blocks - 8 mm .315" spacing(3)Only for M 6/8.STAM 4/6.ST- 4 mm² blocks - 6 mm .236" spacingBNT...PC...(2) Only for M10/10.ST-SnThe PREM IUM solution for testing the secondary circuits of current or voltage transformers.ESSAILEC, approved by the major electricity utilities, remains the premium choice for the energy market.Implemented in the transformers secondary circuits, ESSAILEC thanks to its intelligent “make before break” design eases and secures any intervention. Cutting the energy supply is avoided with zero risk for the operator.The plug and socket connection cuts cost installation as well as in-situ wiring errors. ESSAILEC is ideal for the wiring of sub-assemblies in the secondary circuits.ESSAILEC terminal blocksProtection relays,Protection relays,Testing :The ESSAILEC socket supplies energy to the protection or counting devices. The insertion of the test plug, which is connected to the measurement equipment, allows the testing of the devices, without perturbing the circuit.ESSAILEC blocks are well adapted to current or voltage measurement :-Current sockets with make before break contacts and pre-wired test plug for current measures-Voltage sockets with open contacts and pre-wired test plug for voltage measures-Up to 4 ammeters or 4 voltmeters connected to the test plugDistributing :The ESSAILEC plug is continuously mounted on the socket to supply current or voltage to secondary circuits sub assemblies.ESSAILEC blocks extreme versatility allow :-Safe current distribution with current socket with mobile contacts since the secondary circuit is not cut when plug is removed-Voltage or polarity distribution with dedicated voltage or polarity socket with closed contactESSAILEC is designed to offer :Great flexibility :-Connection multi contacts « plug and play »-Panel, rail, rack fixed mounting or stand-alone connector -Two wiring technologies, up to 10 mm²Extreme reliability :-Non symmetric blocks -Coding accessories -IP20 design -Locking system -Sealed coverR S T NFor technical characteristics and complete part numbers list, please ask for the ESSAILEC catalog10005006003225254 mm 21.65 mm²12 AWG 13 mm / .51"IECB.SCSANFC DINTS 50-180.5 - 0.8 Nm /4.4 - 7.1 Ib.in0.2 - 422-12 AWG0.22 - 40.5 - 1.50.28 - 1.6580050060041252562.512 AWG 13 mm / .51"0.8 - 1 Nm / 7.1 - 8.9 Ib.inIECB.S CSANFC DINTS 50-180.5 - 1020-12 AWG0.5 - 60.28 - 2.590050060046406510 mm 26 mm² 6 AWG 14 mm / .55"IECB.S UL/CSANFC DINTS 50-181.2 - 1.4 Nm / 10.6 - 12.3 Ib.in0.5 - 1620 - 6 AWG0.5 - 100.28 - 6M 4/6.RS - 4 mm² blocks - 6 mm .238" spacingCharacteristicsWire size mm² / AWGVoltage V CurrentARated wire sizemm² / AWG Wire stripping lengthmm / inches Recommended torque (screw)Nm / Ib.inSolid wire Stranded wire Solid wire Stranded wire Screw clampLugsM 6/8.RS - 6 mm² blocks - 8 mm .315" spacingCharacteristicsWire size mm² / AWGVoltage V CurrentARated wire sizemm² / AWG Wire stripping lengthmm / inches Recommended torque (screw)Nm / Ib.inSolid wire Stranded wire Solid wire Stranded wire Screw clampLugspending M 10/10.RS - 10 mm² blocks - 10 mm .394" spacingCharacteristicsWire size mm² / AWGVoltage V CurrentARated wire sizemm² / AWG Wire stripping lengthmm / inches Recommended torque (screw)Nm / Ib.inSolid wire Stranded wire Solid wire Stranded wire Screw clampLugspending SelectionAccessories(1) Only for block M 4/6.RS (4) For blocks M 4/6.RS and M 6/8.RS(2) Only for block M 6/8.RS(3) Only for block M 10/10.RSDR 1,5/4 - 1.5 mm² blocks - 4 mm .157" spacingDR 1,5/5... - 1.5 mm² blocks - 5 mm .200" spacing。

NCS36000Passive Infrared (PIR)Detector ControllerThe NCS36000 is a fully integrated mixed−signal CMOS device designed for low−cost passive infrared controlling applications. The device integrates two low−noise amplifiers and a LDO regulator to drive the sensor. The output of the amplifiers goes to a window comparator that uses internal voltage references from the regulator.The digital control circuit processes the output from the window comparator and provides the output to the OUT and LED pin.Features•3.0 − 5.75 V Operation •−40 to 85°C•14 Pin SOIC Package•Integrated 2−Stage Amplifier •Internal LDO to Drive Sensor•Internal Oscillator with External RC •Single or Dual Pulse Detection •Direct Drive of LED and OUT •This is a Pb−Free DeviceTypical Applications•Automatic Lighting (Residential and Commercial)•Automation of Doors•Motion Triggered Events (Animal photography)VREF OP1_P OP1_N OP1_O OP2_N OP2_O VSS VDDOSC OUTLED xLED_ENMODE Figure 1. Simplified Block Diagram14SOIC−14D SUFFIXCASE 751A1See detailed ordering and shipping information in the package dimensions section on page 7 of this data sheet.ORDERING INFORMATIONPIN CONNECTIONS(Top View)A = Assembly Location WL = Wafer Lot Y = YearWW = Work WeekG= Pb−Free PackageMARKING DIAGRAMOP2_O OP2_N OP1_O OP1_N OP1_P VREF VSSVDD OSC MODE NC xLED_EN LED OUTPIN FUNCTION DESCRIPTIONPin No.Pin Name Description1OP2_O Output of second amplifier2OP2_N Inverting input of second amplifier3OP1_O Output of first amplifier4OP1_N Inverting input of first amplifier5OP1_P Non−inverting input of first amplifier6VREF Regulated voltage reference to drive sensor7VSS Analog ground reference.8OUT CMOS output (10 mA Max)9LED CMOS output to drive LED (10mA Max)10xLED_EN Active low LED enable input11NC No Connect12MODE Pin used to select pulse count mode13OSC External oscillator to control clock frequency14VDD Analog power supplyABSOLUTE MAXIMUM RATINGSRating Symbol Value Unit Input Voltage Range (Note 1)V in−0.3 to 6.0V Output Voltage Range V out−0.3 to 6.0 V or (V in + 0.3),whichever is lowerV Maximum Junction Temperature T J(max)140°C Storage Temperature Range T STG−65 to 150°C ESD Capability, Human Body Model (Note 2)ESD HBM2kV ESD Capability, Machine Model (Note 2)ESD MM200V Lead Temperature SolderingReflow (SMD Styles Only), Pb−Free Versions (Note 3)T SLD260°CStresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.1.Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.2.This device series incorporates ESD protection and is tested by the following methods:ESD Human Body Model tested per AEC−Q100−002 (EIA/JESD22−A114)ESD Machine Model tested per AEC−Q100−003 (EIA/JESD22−A115)Latchup Current Maximum Rating: v150 mA per JEDEC standard: JESD783.For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/DTHERMAL CHARACTERISTICSRating Symbol Value Unit Thermal Characteristics, DFN6, 3x3.3 mm (Note 4)Thermal Resistance, Junction−to−Air (Note 5) Thermal Reference, Junction−to−Lead2 (Note 5)R q JAR Y JLWill be Completed oncepackage and powerconsumption is finalized°C/WThermal Characteristics, TSOP−5 (Note 4)Thermal Resistance, Junction−to−Air (Note 5)R q JA See note above.°C/W4.Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.5.Values based on copper area of 645 mm2 (or 1 in2) of 1 oz copper thickness and FR4 PCB substrate.OPERATING RANGES (Note 6)Rating Symbol Min Typ Max Unit Analog Power Supply V DD 3.0 5.0 5.75V Analog Ground Reference V SS0.00.1V Supply Current (Standby, No Loads)I DD170m ADigital Inputs (MODE)V ih0.7 *V DD V DD V DD +0.3VV il VSS V DD *0.28Digital Output (OUT, LED)Push−Pull Output (10 mA Load)V oh0.67 *V DDV DD VV ol VSS V DD *0.3OP1_P (Sensor Input) (Note 7)AMP 1 IN0.1V DD −1.1V Ambient Temperature T A−4085°C6.Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.7.Guaranteed By Design (Non−tested parameter).ELECTRICAL CHARACTERISTICS V in = 1 V, C in = 100 nF, C out = 100 nF, for typical values T A = 25°C; unless otherwise noted.Parameter Test Conditions Symbol Min Typ Max Unit LDO Voltage ReferenceOutput Voltage V DD = 3.0 V to 5.75 V VREF 2.6 2.7 2.8V Supply Current V DD = 3.0 V to 5.75V IREF2050m A Comparator High Trip Level V h 2.413 2.5 2.588V Comparator Low Trip Level V l 1.641 1.7 1.760V Reference voltage for non−inverting input ofsecond amplifierV m 2.007 2.1 2.174V System OscillatorOscillator Frequency V DD = 5.0 VR3 = 220 k WC2 = 100 nFOSC62.5HzWindow ComparatorLower Trip Threshold See Vl aboveHigher Trip Threshold See Vh aboveDifferential Amplifiers (Amplifier Circuit)DC Gain V DD = 5.0 V (Note 8)Av80dB Common−mode Input Range V DD = 5.0 V (Note 8)CMIR0.1V DD −1.1V Power Supply Rejection Ratio V DD = 5.0 V (Note 8)PSRR60dB Output Drive Current V DD = 5.0 V (Note 8)I out125m A PORPOR Release Voltage V POR 1.35 2.85V 8.Guaranteed By Design (Non−tested parameter).APPLICATIONS INFORMATIONOscillatorThe oscillator uses an external resistor and capacitor to set the system clock frequency. Multiple clock frequencies can be selected using different combinations of resistors and capacitors. Figure 2 shows a simplifier block diagram for the system oscillator.Figure 2. Block Diagram of System Oscillator Circuit LDO RegulatorThe LDO regulator provides the reference voltage for the sensor and all other analog blocks within the system. The nominal voltage reference for the sensor is 2.7 V ±5%. An external capacitor is needed on the VREF pin to guarantee stability of the regulator.Differential AmplifiersThe two differential amplifiers can be configured as a bandpass filter to condition the PIR sensor signal for the post digital signal processing. The cutoff frequencies and passband gain are set by the external components. See Figure 5.101010Figure 3. Plot Showing Typical Magnitude Responseof Differential Amplifiers When Configured as aBandpass FilterWindow ComparatorThe window comparator compares the voltage from thesecond differential amplifier to two reference voltages fromthe LDO regulator. COMP_P triggers if OP2_O is greaterthan the Vh voltage and COMP_N triggers if OP2_O islower than the Vl voltage. See Figures 4 and 5.VhVlVssVssVmFigure 4. Plot Showing Functionality of Window Comparator for an Analog Input OP2_OVmVhVl Figure 5. Figure Showing Simplified Block Diagram of Analog Conditioning StagesDigital Signal Processing Block (all times assume a 62.5 Hz system oscillator frequency)The digital signaling processing block performs three major functions.The first function is that the device toggles LED during the start−up sequencing at approximately two hertz regardless of the state of the XLED_EN pin. The startup sequence lasts for thirty seconds. During that time the OUT pin is held low regardless of the state of OP2_O.The second function of the digital signal processing block is to insure a certain glitch width is seen before OUT is toggled. The digital signal processing block is synchronous with the system oscillator frequency and therefore the deglitch time is related to when the comparators toggle within the oscillator period. A signal width less than two clock period is guaranteed to be deglitched as a zero. A signal width of greater than three clock cycles is guaranteed to be de−glitched. It should be noted that down−sampling can occur if sufficient anti−aliasing is not performed at the input of the circuit (OPI_P) or if noise is injected into the amplifiers, an example would be a noisy power supply.The third function of the digital signal processing block is to recognize different pulse signatures coming from the window comparator block. The device is equipped with two pulse recognition routines. Single pulse mode (MODE tied to VSS) will trigger the OUT pin if either comparator toggles and the deglitch time is of the appropriate length. (See Figure 6). Dual pulse mode (MODE tied to V DD) requires two pulses with each pulse coming from the opposite comparator to occur within a timeout window of five seconds or 312 clock cycles (See Figure 7). If the adjacent pulses occur outside the timeout window then the digital processing block will restart the pulse recognition routine. xLED_EN PinThe xLED_EN pin enables the LED output driver when motion has been detected. If xLED_EN is tied high the LED pin will not toggle after motion is detected. If the xLED_EN is tied low the LED pin will toggle when motion is detected. During start-up the LED pin will toggle irrespective of how the xLED_EN pin is tied. (See Figure 6).V H V L V MFigure 7. Timing Diagram for Dual−Pulse Mode DetectionV H V L V MC1C2Figure 8. Typical Application Diagram Using NCS36000R1 = 10 k W C1 = 33 m F J1 (Jumper for xLED_EN)R2 = 560 k W C2 = 10 nF J2 (Jumper for Mode Select)R3 = 10 k W C3 = 33 m F D1 (LED)R4 = 560 k W C4 = 10 nF R5 = 43 k W C5 = 100 nF R6 = 1 k W C6 = 100 nF R7 = 220 k WC7 = 100 nF9.R1, C1, R2, C2, R3, C3, R4, C4 setup bandpass filter characteristics. With components as shown above the passband gain is approximately 70 dB with the 3 dB cutoff frequency of the filter at approximately 700 mHz and 20 Hz.10.R4 can be replaced by a potentiometer to adjust sensitivity of system. Note dynamically changing R4 will also change the pole location for the second amplifier.11.R5 and C5 are sensor dependant components and R6 may need to be adjusted to guarantee the AMP 1 IN parameter outlined within the Operating Ranges section of this document.12.R7 and C7 may be adjusted to change the oscillator frequency. R7 may not be smaller than 50 k W .ORDERING INFORMATIONDevice Package Shipping†55 Units / RailNCS36000DG SOIC−14(Pb−Free)NCS36000DRG SOIC−143000 / Tape & Reel(Pb−Free)†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.PACKAGE DIMENSIONSSOIC−14D SUFFIX CASE 751A−03NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127(0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.SBM0.25 (0.010)AST SEATING PLANEDIM MIN MAX MIN MAX INCHESMILLIMETERS A 8.558.750.3370.344B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2280.244R0.250.500.0100.019____DIMENSIONS: MILLIMETERS*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks,copyrights, trade secrets, and other intellectual property. A listing of SCILLC’s product/patent coverage may be accessed at /site/pdf/Patent−Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly,any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

Table of Contents1 Introduction (4)2 Modes of operation (5)3 Installing the device (8)3.1 Power supply (8)3.2 Serial connector (8)3.3 The antenna connector (10)3.4 Signaling lights (10)3.5 Jumpers (11)4 AT command set (12)4.1 Setup of the serial interface parameters (14)4.2 Setup of the radio interface (15)4.3 Command mode setup (16)4.4 Reduced power consumption mode setup (16)5 Firmware update (18)5.1 The procedure for writing the new firmware (18)6 Technical specifications (19)Radio modem PRM4 868MHz /User's manual V1.6 / 24.05.201121IntroductionDecode PRM4 modem is used for data transmission in UHF ISM 868MHz band. Through the use of radio interface it procures networking of devices and systems. Easy to use,the PRM4provides secure method of connecting computers,PLC devices, measuring devices and SCADA systems.The device transports the asynchronous serial data between two or more PRM4 devices in point-to-point or point-to-multipoint configuration. The RS-232/485/422 connection enables the implementation of the device into the existing systems without the need for additional equipment.PRM4 DeviceThe standard delivery contains the PRM4 device, network power supply adapter for 230V, mini omni-directional antenna for ISM 868MHz band, DB9 M-F serial cable and CD with this manual and necessary software.Radio modem PRM4 868MHz /User's manual V1.6 / 24.05.201142Modes of operationDecode PRM4 device can operate in one of the two modes of operation.When powered, the device will automatically enter the default,data transfer mode. When the device is in the data transfer mode, it will listen and receive all the packets intended for it, whereas the transmitter will turn-on only occasionally to send the data acquired from the wire connection.The mode and parameters of operation are set through the use of AT commands using the command mode of operation. The transfer into the command mode and the set of supported AT commands is described in chapter 4.The PRM 4 device supports an addressing scheme. All modems intended for data exchange in a radio network must be set to the same frequency and must have the same network address(NA). The NA can be set to any value from the 0 – 65535 range. Each device has its source address (SA) used to identify the device inside a network. The SA can take values between 0 and 255 inclusive. Note that the SA must be set uniquely inside a network. If a point-to-multipoint connection is required (e.g. for master-slave protocols used with SCADA software or PLC devices)the destination address (DA) masking is used. This way it is possible to mask a number of bits when comparing the DA and SA and, consequently, the packet with one destination address can be sent to multiple devices having the unmasked parts of their SA match the unmasked parts of DA.For example, if assumed that the radio frequency and the NA are the same for all the devices in the following figure, the device with the SA equal to 100 will send its packets to the remaining three devices, whereas the devices with the SA 1,2 and 3 will send data only to the SA 100 device. This is because the Address Masks(AM) on devices with SA 1,2 and 3 have been set to 252 (binary 11111100) so that they match the higher (unmasked) six bits of the DA (binary 000000).Radio modem PRM4 868MHz /User's manual V1.6 / 24.05.20115Point-to-multipoint connectionThe below figure illustrates the point-to-point connection. The AM is set to 255 so all the bits are compared and only the exact match of the SA and DA would lead to receipt of the packets. The NAs as well as the radio frequencies are set as with the previous example.Point-to-point connectionThe PRM 4 device receives over the serial interface and buffers the data that needs to be sent until the condition for sending the data is met. The data is sent when there are no new data for a specified time interval after the last data has been received on the serial interface. This time interval can be set by using the AT commands and it is referred to as the packetization timeout. The default value of this parameter is set to 5ms. In other words, if communicating on 9600bps, a 5 character pause will induce the modem to send the entire memory content within one packet. The transmit data buffer size is 512 bytes.The following figure shows the example of three-character packet generation and sending on 9600bps with default packetization timeout.Radio modem PRM4 868MHz /User's manual V1.6 / 24.05.20116Packet generation and sendingIn cases when there is a need for low power consumption of the device (i.e. solar or battery power) the device can be set into one of the three reduced power consumption modes by using the ATSM command.When in the reduced power consumption mode, the receiver is not constantly turned on. It is turned on and off 8 times per second. Therefore, when using this mode, waiting for all the receivers to become active may induce the additional transport delay. By using the ATSM command the reduced power consumption mode of operation can be adjusted to fit the various field configurations.If the devices with the reduced power consumption are communicating only with a device in a normal mode, the first group of devices is set to ATSM2 whereas the device operating in normal mode is set with ATSM1. On the other hand, if all the devices are operating in low power consumption mode, they ought to be set with ATSM3.Important note:When calculating the power budget for the reduced power consumption mode, the RS232 signal lines should not be omitted. It is recommended that, in these cases, the transmit/receive signals of the RS232 interface should be switched off when not actively communicating.Radio modem PRM4 868MHz /User's manual V1.6 / 24.05.20117PRM4 back plateThe connection of a serial interface is achieved by 9-pin female connector (DB9F). Depending on the position of the jumpers located on the circuit board, the device can be connected with the following interfaces: RS-232C, RS-422 and RS-485. If the jumpers are set for RS-232C, the signal layout matches the DCE side. The following table shows the DB9F connector signal layout for different serial connections.RS-232 signals RS-422 signalsDCD outputRD output-TX TD input-RX DTR inputGND-GND DSR outputRTS input+RX CTS output+TX RI(1)output(1)(1)By altering the J7 jumper state it is possible to change the function of this pit to the powersupply input.(2)On some devices with RS485/422 connection, the signals have been denoted as A and B. Inthat case, the A signals should be connected to the + signals of the modem. Vice verse, the B signals should be connected to the – signals of the modem.Radio modem PRM4 868MHz /User's manual V1.6 / 24.05.20119PRM4 front plateSignaling lightsThe above figure illustrates the layout of the LED signaling lights. The LED functions are shown in the following table.Colour DescriptionGreen Constantly on when the power supplyconnected,the device's processorand if the reduced power consumption modeis set to 0 or 2. If this parameter is set to 1 or3 this indicator flashes with the frequency of8Hz.Red On when the device is in special modes.Green On when receiving data.Red On when sending data.The layout of the jumpers on the printed circuit board Radio modem PRM4 868MHz /User's manual V1.6 / 24.05.20115Firmware updateThe following is needed to load the new version of the firmware into the PRM4 device:∙MSPFET software – Can be located on the CD that is included in the PRM4 product pack. Otherwise, the latest software version can be downloaded from http://kurt.on.ufanet.ru/files/MspFet_16007_devel.zip∙RS232 cable for programming the PRM 4 device, and∙File containing the new firmware.5.1The procedure for writing the new firmware∙Open the casing of the device and take out the printed circuit board.∙Connect the serial port of the PC to RS232 port of the modem via DB9 cable and programming cable. The adapter for PRM 4 is DB9 female to DB9 male cable with the following pin connections:DB9 female DB9 malepin 2 ------------------- pin 8pin 3 ------------------- pin 7pin 4 ------------------- pin 4pin 5 ------------------- pin 5pin 7 ------------------- pin 3∙Set the J1 and J2 into the 1-2 state. The rest of the jumpers should be in a state corresponding for RS-232C serial connection according to the aforementioned table.∙Connect the power supply.∙Start the MSPFET, load the prm4xxx.hex, using the setup of the program adjust the BSL and serial port to which the device is connected. Press AUTO.Confirm that the modem's microcontroller has been programmed and verified.∙Disconnect the power supply.∙Set the J1 and J2 into the 2-3 state.∙Return the circuit board into the casing and close it.∙Check the modem operation with the new firmware.Radio modem PRM4 868MHz /User's manual V1.6 / 24.05.2011186Technical specificationsFrequency range ISM 868MHz, according to EN 300 220Channel range and number25kHz, 80 channelsTransmit power+13dBm, 20mWModulation2FSK with Gaussian filtrationDeviation±4kHzOccupied bandwidth25kHzFrequency control synthesizerFrequency stability±2 ppm, -10ºC to +60ºCTx – Rx transition time≤1msError detection CRC16Radio signaling rate9600bpsReceiver sensitivity better than -115dBm for 10-3 BERChannel occupation time less than 1%Range up to 2km with rod antenna, 16km with high gainantennaAntenna connector SMA femaleAntenna impedance50ΩSerial interface8 data, None parity, 1 stop bit1200, 2400, 4800, 9600, 19200, 38400, 57600,115200Serial connector DB9 DCE RS-232: Tx, Rx, RTS, CTS, DTR, DSR, DCD, RI,GNDRS-422: Tx+, Tx-, Rx+, Rx-, GND (2W/4Wselectable)RS-485: Tx+, Tx-, Rx+, Rx-, GND (2W/4Wselectable)Termination 120 Ohm for RS-422 and RS-485selectableSettings through AT command setAddressing scheme65536 network addresses, 256 source addresses Network configuration Point-to-point, point-to-multipointPower supply8-32Vdc, 2W or battery option 3.3-12VdcPower consumption<50mALED indications power supply, receive, transmit, error in channel Temperature range-20°C to +75°C, 0 to 95% RH (non condensing) Protection IP50Dimensions86 x 57 x 26 mmWeight110gMounting desktop or optional mounting for 35mm DIN rail Radio modem PRM4 868MHz /User's manual V1.6 / 24.05.201119。

数据表NI 920616个AI 差分/32个AI 单端,±200 mV ~±10 V, 16位,250 kS/s 多路综合,燃料电池测量•弹簧端子连接•保护性后壳•600 VDC (US )/400 VDC (EU ), CAT I ,通道对地隔离NI 9206 C 系列模块可与任意CompactDAQ 或CompactRIO 系统配合使用,具有16个差分模拟输入、16位分辨率以及250 kS/s 最大采样率。

每个通道的可编程范围包括±200 mV 、±1 V 、±5 V 及±10 V 。

为防止信号瞬变,NI 9206在输入通道和公共端(COM )之间包含±30 V 的过压保护。

此外,NI 9206还具有通道对地双重隔离屏障,以确保安全、抗噪性及高共模电压范围。

NI 9206额定具有1,000 Vrms 瞬间过压保护。

NI 9206提供高达600 VDC (欧洲为400 VDC )的通道对地隔离,使其非常适合精确监控大型燃料电池和电池组。

虽然每组被测电池对地可高达600 V ,但NI 9206的每个通道必须保持在模块COM 的10 V 范围内。

• NI 9206• NI 9206入门指南• NI 9940 Backshell Kit (779567-01) 套件内容附件• NI 9974弹簧接线盒(196740-01)• NI 9941后壳套件(779568-01)NI C系列概述NI 提供超过100种C 系列模块,用于测量、控制以及通信应用程序。

C 系列模块可连接任意传感器或总线,并允许进行高精度测量,以满足高级数据采集及控制应用程序的需求。

•与测量相关的信号调理,可连接一组传感器和信号•隔离选项包括组间、通道间以及通道对地•温度范围为-40 °C ~70 °C ,满足各种应用程序和环境需要•热插拔2 | | NI 9206数据表CompactRIO和CompactDAQ平台同时支持大部分C系列模块,用户无需修改就可将模块在两个平台间转换。

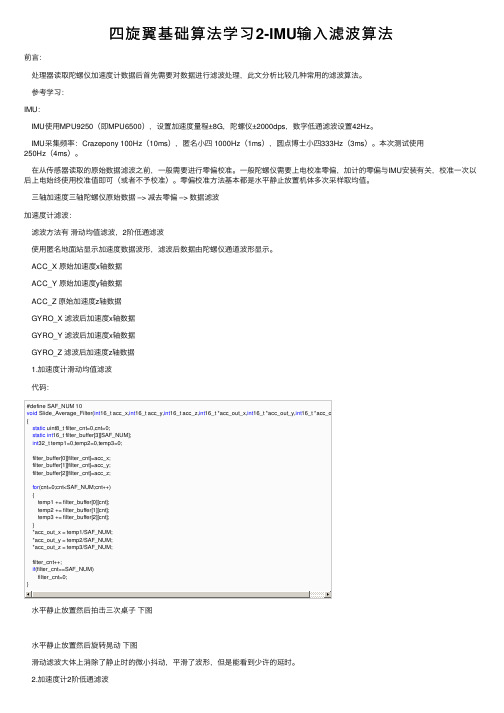

文章编号:2095-6835(2020)13-0043-03面向极低功耗收发器的分数锁相环架构设计何昊晨(武汉理工大学自动化学院,湖北武汉430070)摘要:分数锁相环的毛刺是噪声耦合到带内的原因之一,导致收发器使用更高的功率实现等同的灵敏度。

针对该问题,提出一种基于可变幅度电荷泵(Variable Amplitude Charge Pump,VACP)和固定脉冲、可变周期信号发生器(Fixed Pulse Variable Period Signal Generator,FPVPSG)的低毛刺分数锁相环架构。

在FPVPSG的驱动下,VACP的输出电流脉冲不仅有固定位置、固定宽度、可变幅度,而且有可变周期,用于根除参考毛刺和分数毛刺。

基于Spectre的仿真结果表明,当参考频率f REF为20MHz,小数分频为120.13,且瞬态和锁定时的周期分别为1/f REF 和27/f REF时,20MHz及其整数倍的参考毛刺被根除,10MHz的分数毛刺较已有方案小19.67dB,且其他分数毛刺均远小于已有方案。

该结果表明推荐的分数锁相环架构可用于极低功耗收发器,在移动物联网和边缘计算领域有一定的应用前景。

关键词:极低功耗收发器;交调干扰;噪声;分数锁相环架构中图分类号:TN74文献标识码:A DOI:10.15913/ki.kjycx.2020.13.0161引言在移动物联网和边缘计算等领域,大部分收发器布局在户外或其他较难维护的场景,开发者应设计高性能的器件,用于尽可能降低收发器的功耗,使其具有较长的使用寿命。

分数锁相环(Fractional Phase-Locked Loop,FPLL)为收发器提供本振信号,将基带信号上变频到射频或者将接收信号下变频到基带,它的毛刺将恶化收发器的信噪比,导致发射器使用更高的发射功率实现等同的灵敏度,不利于节省收发器的功耗。

因此,研究更低毛刺的FPLL架构对实现极低功耗的收发器具有重要的意义,一直为学术界和工业界关注的研究热点。

Preliminary Product InformationThis document contains information for a new product.Cirrus Logic reserves the right to modify this product without notice.3.3V Stereo Audio DAC with 2V RMS Line OutputFeaturesMulti-bit Delta-Sigma Modulator 106dB A-wt Dynamic Range -93dB THD+NSingle-ended Ground Centered AnalogArchitecture–No DC-blocking Capacitors Required–Integrated Step-up/Inverting Charge Pump –Filtered Line-level Outputs–Selectable 1 or 2V RMS Full-scale OutputLow Clock-jitter Sensitivity Low-latency Digital FilteringSupports Sample Rates up to 192kHz 24-bit Resolution+3.3V Charge Pump and Core Logic, +3.3VAnalog, and +0.9 to 3.3V Interface Power SuppliesLow Power Consumption24-pin QFN, Lead-free AssemblyDescriptionThe CS4353 is a complete stereo digital-to-analog sys-tem including digital interpolation, fifth-order multi-bit delta-sigma digital-to-analog conversion, digital de-em-phasis, analog filtering, and on-chip 2V RMS line-level driver from a 3.3V supply.The advantages of this architecture include ideal differ-ential linearity, no distortion mechanisms due to resistor matching errors, no linearity drift over time and temper-ature, high tolerance to clock jitter, and a minimal set of external components.The CS4353 is available in a 24-pin QFN package in both Automotive (-40°C to +105°C) and Commercial (-40°C to +85°C) grades. The CDB4353 Customer Demonstration Board is also available for device evalu-ation and implementation suggestions. Please see “Ordering Information” on page 26 for complete details.These features are ideal for cost-sensitive, 2-channel audio systems including video game consoles, DVD players and recorders, A/V receivers, set-top boxes,digital TVs, mini-component systems, and mixing consoles.CS4353TABLE OF CONTENTS1. PIN DESCRIPTIONS (4)2. CHARACTERISTICS AND SPECIFICATIONS (6)RECOMMENDED OPERATING CONDITIONS (6)ABSOLUTE MAXIMUM RATINGS (6)DAC ANALOG CHARACTERISTICS (COMMERCIAL - CNZ) (7)DAC ANALOG CHARACTERISTICS (AUTOMOTIVE - DNZ) (8)COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE (9)SWITCHING SPECIFICATIONS - SERIAL AUDIO INTERFACE (10)DIGITAL INTERFACE CHARACTERISTICS (11)INTERNAL POWER-ON RESET THRESHOLD VOLTAGES (11)DC ELECTRICAL CHARACTERISTICS (12)3. TYPICAL CONNECTION DIAGRAM (13)4. APPLICATIONS (14)4.1.1 Ground-Centered Outputs (14)4.1.2 Full-Scale Output Amplitude Control (14)4.1.3 Pseudo-Differential Outputs (14)4.8.1 Power-Up Sequences (20)4.8.1.1 External RESET Power-Up Sequence (20)4.8.1.2 Internal Power-On Reset Power-Up Sequence (20)4.8.2 Power-Down Sequences (20)4.8.2.1 External RESET Power-Down Sequence (20)4.8.2.2 Internal Power-On Reset Power-Down Sequence (20)4.9.1 Capacitor Placement (21)5. DIGITAL FILTER RESPONSE PLOTS (22)6. PARAMETER DEFINITIONS (24)7. PACKAGE DIMENSIONS (25)8. ORDERING INFORMATION (26)9. REVISION HISTORY (27)LIST OF FIGURESFigure 1.Serial Input Timing (10)Figure 2.Power-On Reset Threshold Sequence (11)Figure 3.Typical Connection Diagram (13)Figure 4.Stereo Pseudo-Differential Output (14)Figure 5.I²S, up to 24-Bit Data (16)Figure 6.Left-Justified up to 24-Bit Data (16)Figure 7.De-Emphasis Curve, Fs = 44.1 kHz (17)Figure 8.Internal Power-On Reset Circuit (17)Figure 9.Initialization and Power-Down Sequence Diagram (19)Figure 10.Single-Speed Stopband Rejection (22)Figure 11.Single-Speed Transition Band (22)Figure 12.Single-Speed Transition Band (detail) (22)Figure 13.Single-Speed Passband Ripple (22)Figure 14.Double-Speed Stopband Rejection (22)Figure 15.Double-Speed Transition Band (22)Figure 16.Double-Speed Transition Band (detail) (23)Figure 17.Double-Speed Passband Ripple (23)Figure 18.Quad-Speed Stopband Rejection (23)Figure 19.Quad-Speed Transition Band (23)Figure 20.Quad-Speed Transition Band (detail) (23)Figure 21.Quad-Speed Passband Ripple (23)LIST OF TABLESTable 1. Power-On Reset Threshold Voltages (11)Table 2. Digital I/O Pin Characteristics (12)Table 3. CS4353 Operational Mode Auto-Detect (15)Table 4. Single-Speed Mode Standard Frequencies (15)Table 5. Double-Speed Mode Standard Frequencies (15)Table 6. Quad-Speed Mode Standard Frequencies (15)Table 7. Digital Interface Format (16)1. PIN DESCRIPTIONSPin Name Pin #Pin DescriptionSCLK 1Serial Clock (Input ) - Serial clock for the serial audio interface.MCLK 2Master Clock (Input ) - Clock source for the delta-sigma modulator and digital filters. VL 3Serial Audio Interface Power (Input ) - Positive power for the serial audio interface DGND 4Digital Ground (Input ) - Ground reference for the digital section.FLYP+FLYP-75Step-Up Charge Pump Cap Positive/Negative Nodes (Output) - Positive and Negative nodes for the step-up charge pump’s flying capacitor.VCP 6Charge Pump and Digital Core Logic Power (Input ) - Positive power supply for the step-up and invert-ing charge pumps as well as the digital core logic sections.VFILT+8Step-Up Charge Pump Filter Connection (Output) - Power supply from the step-up charge pump that provides the positive rail for the output amplifiersFLYN+FLYN-911Inverting Charge Pump Cap Positive/Negative Nodes (Output) - Positive and Negative nodes for the inverting charge pump’s flying capacitor.CPGND 10Charge Pump Ground (Input ) - Ground reference for the Charge Pump section.VFILT-12Inverting Charge Pump Filter Connection (Output) - Power supply from the inverting charge pump that provides the negative rail for the output amplifiers.AOUTB AOUTA 1315Analog Outputs (Output ) - The full-scale analog line output level is specified in the Analog Characteris-tics table.AOUT_REF 14Pseudo Diff. Analog Output Reference (Input ) - Ground reference for the analog output amplifiers. This pin must be at the same nominal DC voltage as the AGND pin.AGND16Analog Ground (Input ) - Ground reference for the low voltage analog section.S D I NL R C KI ²S /L JD E M1_2V R M SR E S E TF L Y P +V F I L T +F L Y N +C P G N DF L Y N -SCLK MCLKVL DGND FLYP-VBIAS VA AGND AOUT_REF AOUTBVCPV F I L T -AOUTAVA17Low Voltage Analog Power (Input) - Positive power supply for the analog section. VBIAS18Positive Voltage Reference (Output) - Positive reference voltage for the internal DAC.RESET19Reset (Input) - Optional connection for an external reset control. The device enters a powered-down state when this pin is set low (GND) OR when the VCP supply falls below the V off threshold (see Table1). This pin should be set high (VL) during normal operation.1_2VRMS201 or 2V RMS Select (Input) - Selects the analog output full-scale voltage. Setting this pin low (GND) selects 1V RMS, while setting it high (VL) selects 2V RMS.DEM21De-emphasis (Input) - Selects the standard 50µs/15µs digital de-emphasis filter response for 44.1 kHz sample rates when enabled.I²S/LJ22Digital Interface Format (Input) - Selects the serial audio interface format. Setting this pin low (GND) selects I²S, while setting it high (VL) selects Left-Justified.LRCK23Left / Right Clock (Input) - Determines which channel, Left or Right, is currently active on the serial audio data line.SDIN24Serial Audio Data Input (Input) - Input for two’s complement serial audio data.Thermal Pad-Thermal Relief Pad - This pad may be soldered to the board, however it MUST be electrically isolated from all board connections.2.CHARACTERISTICS AND SPECIFICATIONS RECOMMENDED OPERATING CONDITIONSAGND = DNGD = CPGND = 0V; all voltages with respect to ground.Notes:1.VCP and VA must be supplied with the same nominal voltage. Additional current draw will occur if the sup-ply voltages applied to VCP and VA differ by more than 0.5V.ABSOLUTE MAXIMUM RATINGSAGND = DNGD = CPGND = 0V; all voltages with respect to ground.WARNING:Operation at or beyond these limits may result in permanent damage to the device. Normal operationis not guaranteed at these extremes.ParametersSymbol Min TypMaxUnitsDC Power SupplyCharge Pump and Digital Core power (Note 1)Low Voltage Analog power (Note 1)Interface powerVCP VA VL 3.133.130.85 3.33.30.9 to 3.33.473.473.47V V V Ambient Operating Temperature (Power Applied)-CNZ-DNZT A T A-40-40--+85+105°C °CParametersSymbolMinMaxUnitsDC Power SupplyCharge Pump and Digital Core Logic PowerLow Voltage Analog Power Supply Voltage DifferenceInterface PowerVCP VA |VCP - VA|VL -0.3-0.3--0.3 3.633.630.53.63V V V V Input Current, Any Pin Except Supplies I in -±10mA Digital Input Voltage Digital Interface V IN-L -0.3V L + 0.4V Analog Input Voltage AOUT_REF V IN-A -0.30.5V Ambient Operating Temperature (Power Applied)T A -55+125°C Storage Temperature T stg-65+150°CTest conditions (unless otherwise specified): T A = 25°C; VCP =VA =3.3V; AOUT_REF =AGND = DGND =CPGND = 0V; VBIAS, +/-VFILT, and FLYP/N+/- capacitors as shown in Figure 3 on page 13; input test signal is a 997Hz sine wave at 0dBFS; measurement bandwidth 10Hz to 20kHz.Notes:2.Measured between the AOUTx and AOUT_REF pins.3.One-half LSB of triangular PDF dither is added to data.4.Measured with the specified minimum AC-Load Resistance present on the AOUTx pins. Additional im-pedance between the AOUTx pin and the load will lower the voltage delivered to the load.5.V PP is the controlling specification. V RMS specification valid for sine wave signals only.Note that for sine wave signals:6.Measured with AOUT_REF connected directly to ground. Additional impedance between AOUT_REFand ground will lower the AOUT_REF rejection.7.SDIN =0. AOUT_REF input test signal is a 60Hz, 50mVpp sine wave. Measured by applying the testsignal into the AOUT_REF pin and measuring the resulting output amplitude on the AOUTx pin. Spec-ification calculated by: 1_2VRMS =01_2VRMS =1ParameterSymbol MinTypMaxMinTypMaxUnitDynamic Performance, Fs = 48, 96, and 192kHz (Notes 2, 3)Dynamic Range24-bit A-Weightedunweighted 16-bit A-Weightedunweighted9491--100979289----10097--1061039895----dB dB dB dB Total Harmonic Distortion + Noise24-bit 0dB-20dB-60dB 16-bit 0dB-20dB-60dB THD+N--------93-77-37-93-75-29-87-71-31-----------93-83-43-93-75-35-87-77-37---dB dB dB dB dB dB Idle Channel Noise / Signal-to-Noise Ratio (A-wt)-100--106-dB Interchannel Isolation(1kHz)-115--115-dB Analog Output (Note 2)Full Scale AOUTx Output Voltage (Notes 4, 5)0.98 1.05 1.12 1.96 2.10 2.25V RMS 2.772.973.17 5.54 5.94 6.36V pp Max Current Draw from an AOUTx Pin I OUTmax-575--575-µA Interchannel Gain Mismatch -0.1--0.1-dB Output Offset -±5±8-±5±8mV Gain Drift-100--100-ppm/°C Output Impedance Z OUT -100--100-ΩAC-Load Resistance R L 5--5--k ΩLoad Capacitance C L --1000--1000pF AOUT_REF Rejection (Notes 6, 7)AOR-40--40-dB Analog Reference Input AOUT_REF Input Voltage(Note 8)--0.2--0.2VppV RMS V pp22---------=AOR dB 20log 10AOUT _REFAOUT _REF AOUTx–---------------------------------------------------------⎝⎠⎛⎞⋅=Test conditions (unless otherwise specified): TA = -40 to +85°C; VCP =VA =3.13V to 3.47V; AOUT_REF = AGND = DGND =CPGND = 0V; VBIAS, +/-VFILT, and FLYP/N+/- capacitors as shown in Figure 3 on page 13; input test signal is a 997Hz sine wave at 0dBFS; measurement bandwidth 10Hz to 20kHz.8.Applying a DC voltage on the AOUT_REF pin will cause a DC offset on the DAC output. See Section4.1.3 for more information.1_2VRMS =01_2VRMS =1ParameterSymbol MinTypMaxMinTypMaxUnitDynamic Performance, Fs = 48, 96, and 192kHz (Notes 2, 3)Dynamic Range24-bit A-Weightedunweighted 16-bit A-Weightedunweighted9491--100979289----10097--1061039895----dB dB dB dB Total Harmonic Distortion + Noise24-bit 0dB-20dB-60dB 16-bit 0dB-20dB-60dB THD+N--------93-77-37-93-75-29-87-71-31-----------93-83-43-93-75-35-87-77-37---dB dB dB dB dB dB Idle Channel Noise / Signal-to-Noise Ratio (A-wt)-100--106-dB Interchannel Isolation(1kHz)-115--115-dB Analog Output (Note 2)Full Scale AOUTx Output Voltage (Notes 4, 5)0.98 1.05 1.12 1.96 2.10 2.25V RMS 2.772.973.17 5.54 5.94 6.36V pp Max Current Draw from an AOUTx Pin I OUTmax-575--575-µA Interchannel Gain Mismatch -0.1--0.1-dB Output Offset -±5±8-±5±8mV Gain Drift-100--100-ppm/°C Output Impedance Z OUT -100--100-ΩAC-Load Resistance R L 5--5--k ΩLoad Capacitance C L --1000--1000pF AOUT_REF Rejection (Notes 6, 7)AOR-40--40-dB Analog Reference Input AOUT_REF Input Voltage(Note 8)--0.2--0.2VppCOMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSEThe filter characteristics have been normalized to the sample rate (Fs) and can be referenced to the desired sam-ple rate by multiplying the given characteristic by Fs. Notes:9.Response is clock-dependent and will scale with Fs.10.For Single- and Double-Speed Mode, the Measurement Bandwidth is from stopband to 3 Fs.For Quad-Speed Mode, the Measurement Bandwidth is from stopband to 1.34 Fs.11.De-emphasis is available only in Single-Speed Mode.12.Amplitude vs. Frequency plots of this data are available in “Digital Filter Response Plots” on page 22.ParameterMin TypMaxUnitSingle-Speed Mode - 48kHzPassband (Note 9)to -0.01dB corner to -3dB corner00--.454.499Fs Fs Frequency Response 10Hz to 20kHz -0.01-+0.01dB StopBand0.547--Fs StopBand Attenuation(Note 10)102--dB Total Group Delay (Fs = Sample Rate)-9.4/Fs -s Intra-channel Phase Deviation --±0.56/Fss Inter-channel Phase Deviation--0s De-emphasis Error (Note 11)(Relative to 1kHz)Fs = 44.1 kHz --±0.14dB Double-Speed Mode - 96kHzPassband (Note 9)to -0.01dB corner to -3dB corner00--.430.499Fs Fs Frequency Response 10Hz to 20kHz -0.01-0.01dB StopBand.583--Fs StopBand Attenuation(Note 10)80--dB Total Group Delay (Fs = Sample Rate)- 4.6/Fs -s Intra-channel Phase Deviation --±0.03/Fss Inter-channel Phase Deviation--0s Quad-Speed Mode - 192kHzPassband (Note 9)to -0.01 dB cornerto -3dB corner00--.105.490Fs Fs Frequency Response 10Hz to 20kHz -0.01-0.01dB StopBand.635--Fs StopBand Attenuation(Note 10)90--dB Total Group Delay (Fs = Sample Rate)- 4.7/Fs-sSWITCHING SPECIFICATIONS - SERIAL AUDIO INTERFACEParametersSymbol MinMaxUnitsMCLK Frequency 2.04851.2MHz MCLK Duty Cycle4555%Input Sample Rate (Auto selection)Single-Speed Mode Double-Speed Mode Quad-Speed ModeFs Fs Fs 88417054108216kHz kHz kHz LRCK Duty Cycle 4060%SCLK Pulse Width Low t sclkl 20-ns SCLK Pulse Width High t sclkh20-ns SCLK PeriodSingle-Speed Mode -s Double-Speed Mode -s Quad-Speed Mode-s SCLK rising to LRCK edge delay t slrd 20-ns SCLK rising to LRCK edge setup time t slrs 20-ns SDIN valid to SCLK rising setup time tsdlrs 20-ns SCLK rising to SDIN hold timet sdh20-nsFigure 1. Serial Input Timing1128()Fs ---------------------164()Fs ------------------164()Fs ------------------DIGITAL INTERFACE CHARACTERISTICSTest conditions (unless otherwise specified): AGND = DGND = CPGND = 0V; all voltages with respect to ground.INTERNAL POWER-ON RESET THRESHOLD VOLTAGESTest conditions (unless otherwise specified): AGND = DGND = CPGND = 0V; all voltages with respect to ground.Table 1. Power-On Reset Threshold VoltagesFigure 2. Power-On Reset Threshold SequenceParametersSymbolMin TypMaxUnitsHigh-Level Input Voltage 1.2V < VL ≤ 3.3V 0.9V ≤ VL ≤ 1.2V V IH V IH 0.7xVL 0.9xVL ----V V Low-Level Input Voltage 1.2V < VL ≤ 3.3V 0.9V ≤ VL ≤ 1.2VV IL V IL ----0.3xVL 0.1xVL V V Input Leakage Current I in--±10µA Input Capacitance-8-pFParametersSymbolMin Typ Max Units Internal Reset Asserted at Power-On V on1- 1.00-V Internal Reset Released at Power-On V on2- 2.14-V Internal Reset Asserted at Power-OffV off-2.00-VDC ELECTRICAL CHARACTERISTICSTest conditions (unless otherwise specified): VCP =VA =VL =3.3V; AGND = DGND = CPGND = 0V; SDIN =0; all voltages with respect to ground.Notes:13.Current consumption increases with increasing sample rate and increasing MCLK frequency. Typicalvalues are based on Fs =48kHz and MCLK =12.288MHz. Maximum values are based on highest sample rate and highest MCLK frequency; see Switching Specifications - Serial Audio Interface . Vari-ance between speed modes is small.14.Power-down is defined as RESET pin = Low with all clock and data lines held static low. All digital inputshave a weak pull-down (approximately 50k Ω) which is only present during reset. Opposing this pull-down will slightly increase the power-down current.15.Valid with the recommended capacitor value on VBIAS as shown in the typical connection diagram inSection 3.16.Typical voltage shown for “Initialization State”, see Section 4.7. Typical voltage may be up to 1.5V lowerduring normal operation.2.1Digital I/O Pin CharacteristicsInput and output levels and associated power supply voltage are shown in Table 2. Logic levels should not exceed the corresponding power supply voltage.Table 2. Digital I/O Pin CharacteristicsParametersSymbol Min Typ Max UnitsPower SuppliesPower Supply Current (Note 13)Normal OperationPower-Down, All Supplies (Note 14)I VCPI VA I VL I PD----362.40.1654330.2-mA mA mA µA Power Dissipation (All Supplies)Normal Operation, 1_2VRMS =0(Note 13)Power-Down (Note 14)--1271152-mW mW Power Supply Rejection Ratio (Note 15) (1 kHz)(60 Hz)PSRR --6060--dB dB DC Output VoltagesPin VoltageFLYP+ to FLYP-VFILT+ to GND (Note 16)FLYN+ to FLYN-GND to VFILT- (Note 16)VA to VBIAS-----3.36.66.66.62.1-----V V V V VPin Name Power SupplyI/O Driver ReceiverRESET VLInput -0.9V - 3.3V, with HysteresisMCLK Input -0.9V - 3.3V LRCK Input -0.9V - 3.3V SCLK Input -0.9V - 3.3V SDIN Input -0.9V - 3.3V DEM Input -0.9V - 3.3V I²S/LJ Input -0.9V - 3.3V 1_2VRMSInput-0.9V - 3.3V3.TYPICAL CONNECTION DIAGRAMFigure 3. Typical Connection Diagram4.APPLICATIONS4.1Line Outputs4.1.1Ground-Centered OutputsAn on-chip charge pump creates both positive and negative high-voltage supplies, which allows the full-scale output swing to be centered around ground. This eliminates the need for large DC-blocking capac-itors which create audible pops at power-on, allows the CS4353 to deliver a larger full-scale output at low-er supply voltages, and provides improved bandwidth frequency response.4.1.2Full-Scale Output Amplitude ControlThe full-scale output voltage amplitude is selected via the 1_2VRMS pin. When the pin is connected to VL, the full-scale output voltage at the AOUTx pins is approximately 2V RMS. When the pin is connected to GND, the full-scale output voltage at the AOUTx pins is approximately 1V RMS. Additional impedance between the AOUTx pin and the load will lower the voltage delivered to the load. See the DAC Analog Characteristics (Commercial - CNZ) or DAC Analog Characteristics (Automotive - DNZ) table for the com-plete specifications of the full-scale output voltage.4.1.3Pseudo-Differential OutputsThe CS4353 implements a pseudo-differential output stage. The AOUT_REF input is intended to be used as a pseudo-differential reference signal. This feature provides common mode noise rejection with single-ended signals. Figure4 shows a basic diagram outlining the internal implementation of the pseudo-differ-ential output stage, including a recommended stereo pseudo-differential output topology. If pseudo-differ-ential output functionality is not required, simply connect the AOUT_REF pin to ground next to the CS4353. If a split-ground design is used, the AOUT_REF pin should be connected to AGND. See the Ab-solute Maximum Ratings table for the maximum allowable voltage on the AOUT_REF pin. Applying a DC voltage on the AOUT_REF pin will cause a DC offset on the DAC output.Figure 4. Stereo Pseudo-Differential Output4.2Sample Rate Range/Operational Mode DetectThe CS4353 operates in one of three operational modes. The device will auto-detect the correct mode when the input sample rate (Fs), defined by the LRCK frequency, falls within one of the ranges illustrated in Table 3. Sample rates outside the specified range for each mode are not supported. In addition to a valid LRCK frequency, a valid serial clock (SCLK) and master clock (MCLK) must also be applied to the device for speed mode auto-detection; see Figure 9.Table 3. CS4353 Operational Mode Auto-Detect4.3System ClockingThe device requires external generation of the master (MCLK), left/right (LRCK) and serial (SCLK) clocks.The left/right clock, defined also as the input sample rate (Fs), must be synchronously derived from the MCLK signal according to specified ratios. The specified ratios of MCLK to LRCK, along with several stan-dard audio sample rates and the required MCLK frequency, are illustrated in Tables 4-6.Refer to Section 4.4 for the required SCLK timing associated with the selected Digital Interface Format and to “Switching Specifications - Serial Audio Interface” on page 10 for the maximum allowed clock frequen-cies.Table 4. Single-Speed Mode Standard FrequenciesTable 5. Double-Speed Mode Standard FrequenciesTable 6. Quad-Speed Mode Standard FrequenciesInput Sample Rate (Fs)Mode8 kHz - 54 kHz Single-Speed Mode 84 kHz - 108 kHz Double-Speed Mode 170 kHz - 216 kHzQuad-Speed ModeSample Rate(kHz)MCLK (MHz)256x384x512x768x1024x328.192012.288016.384024.576032.768044.111.289616.934422.579233.868845.15844812.288018.432024.576036.864049.1520Sample Rate(kHz)MCLK (MHz)128x192x256x384x512x88.211.289616.934422.579233.868845.15849612.288018.432024.576036.864049.1520Sample Rate(kHz)MCLK (MHz)128x192x256x176.422.579233.868845.158419224.576036.864049.15204.4Digital Interface FormatThe device will accept audio samples in either I²S or Left-Justified digital interface formats, as illustrated in Table 7.The desired format is selected via the I²S/LJ pin. For an illustration of the required relationship between the LRCK, SCLK and SDIN, see Figures 5-6. For all formats, SDIN is valid on the rising edge of SCLK. Also,SCLK must have at least 32 cycles per LRCK period in the Left-Justified format.For more information about serial audio formats, refer to Cirrus Logic Application Note AN282: The 2-Chan-nel Serial Audio Interface: A Tutorial , available at .Table 7. Digital Interface FormatFigure 5. I²S, up to 24-Bit DataFigure 6. Left-Justified up to 24-Bit DataI²S/LJDescriptionFigure0I²S, up to 24-bit Data51Left-Justified, up to 24-bit Data64.5De-Emphasis ControlThe device includes on-chip digital de-emphasis. Figure 7 shows the de-emphasis curve for Fs equal to 44.1kHz. The frequency response of the de-emphasis curve scales with changes in the sample rate, Fs.The de-emphasis error will increase for sample rates other than 44.1kHz.When the DEM pin is connected to VL, the 44.1kHz de-emphasis filter is activated. When the DEM pin is connected to GND, the de-emphasis filter is turned off.Note: De-emphasis is only available in Single-Speed Mode.4.6Internal Power-On ResetThe CS4353 features an internal power-on reset (POR) circuit. The POR circuit allows the RESET pin to be connected to VL during power-up and power-down sequences if the external reset function is not needed.This circuit monitors the VCP supply and automatically asserts or releases an internal reset of the DAC’s digital circuitry when the supply reaches defined thresholds (see “Internal Power-On Reset Threshold Volt-ages” on page 11). No external clocks are required for the POR circuit to function.Figure 8. Internal Power-On Reset CircuitWhen power is first applied, the POR circuit monitors the VCP supply voltage to determine when it reaches a defined threshold, V on1. At this time, the POR circuit asserts the internal reset low, resetting all of the digital circuitry. Once the VCP supply reaches the secondary threshold, V on2, the POR circuit releases the internal reset.Figure 7. De-Emphasis Curve, Fs = 44.1 kHzNote:For correct operation of the internal POR circuit, the voltage on VL must rise before or simulta-neously with VCP.When power is removed and the VCP voltage reaches a defined threshold, V off, the POR circuit asserts the internal reset low, resetting all of the digital circuitry.4.7InitializationWhen power is first applied, the DAC enters a reset (low power) state at the beginning of the initialization sequence. In this state, the AOUTx pins are weakly pulled to ground and VBIAS is connected to VA.The device will remain in the reset state until the RESET pin is brought high. Once the RESET pin is high, the internal digital circuitry is reset and the DAC enters a power-down state until MCLK is applied. Alterna-tively, if no external reset control is required, the internal power-on reset can be used by tying the RESET pin to VL (see Section 4.6).Once MCLK is valid, the device enters an initialization state in which the charge pump powers up and charg-es the capacitors for both the positive and negative high-voltage supplies.Once LRCK and SCLK are valid, the number of MCLK cycles is counted relative to the LRCK period to de-termine the MCLK/LRCK frequency ratio. Next, the device enters the power-up state in which the interpo-lation and decimation filters and delta-sigma modulators are turned on, the internal voltage reference, VBIAS, powers up to normal operation, the analog output pull-down resistors are removed, and power is applied to the output amplifiers.After this power-up state sequence is complete, normal operation begins and analog output is generated.If valid MCLK, LRCK, and SCLK are applied to the DAC before RESET is set high, the total time from RE-SET being set high to the analog audio output from AOUTx is less than 50ms.See Figure9 for a diagram of the device’s states and transition conditions.Figure 9. Initialization and Power-Down Sequence Diagram4.8Recommended Power-Up and Power-Down Sequences4.8.1Power-Up Sequences4.8.1.1External RESET Power-Up SequenceFollow the power-up sequence below if the external RESET pin is used:1.Hold RESET low while the power supplies are turned on.2.Set the I²S/LJ, 1_2VRMS, and DEM configuration pins to the desired state.3.Provide the correct MCLK, LRCK, and SCLK signals locked to the appropriate frequencies asdiscussed in Section 4.3.4.After the power supplies, configuration pins, and clock signals are stable, bring RESET high. Thedevice will initiate the power-up sequence seen in Figure9. The sequence will complete and audiowill be output from AOUTx within 50ms after RESET is set high.4.8.1.2Internal Power-On Reset Power-Up SequenceFollow the power-up sequence below if the internal power-on reset is used:1.Hold RESET high (connected to VL) while the power supplies are turned on. The power-on resetcircuitry will function as described in Section 4.6.2.Set the I²S/LJ, 1_2VRMS, and DEM configuration pins to the desired state.3.After the power supplies and configuration pins are stable, provide the correct MCLK, LRCK, andSCLK signals to progress from the ‘Power-Down State’ in the power-up sequence seen in Figure9.The sequence will complete and audio will be output from the AOUTx pins within 50ms after validclocks are applied.4.8.2Power-Down Sequences4.8.2.1External RESET Power-Down SequenceFollow the power-down sequence below if the external RESET pin is used:1.For minimal pops, set the input digital data to zero for at least 8192 consecutive samples.2.Bring RESET low.3.Remove the power supply voltages.4.8.2.2Internal Power-On Reset Power-Down SequenceFollow the power-down sequence below if the internal power-on reset is used:1.For minimal pops, set the input digital data to zero for at least 8192 consecutive samples.2.Remove the MCLK signal without applying any glitched pulses to the MCLK pin.3.Remove the power supply voltages.Note: A glitched pulse is any pulse that is shorter than the period defined by the minimum/maximum MCLK signal duty cycle specification and the nominal frequency of the input MCLK signal. A transient may occur on the analog outputs if the MCLK signal duty cycle specification is violated when the MCLK signal is removed during normal operation; see “Switching Specifications - Serial Audio Interface” on page10.。

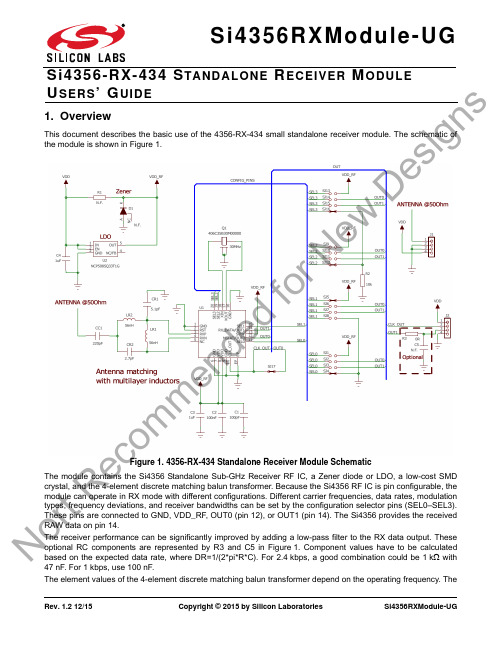

Rev. 1.2 12/15Copyright © 2015 by Silicon LaboratoriesSi4356RXModule-UGU SERS ’ G UIDE1. OverviewThis document describes the basic use of the 4356-RX-434 small standalone receiver module. The schematic of the module is shown in Figure 1.Figure 1.4356-RX-434 Standalone Receiver Module SchematicThe module contains the Si4356 Standalone Sub-GHz Receiver RF IC, a Zener diode or LDO, a low-cost SMD crystal, and the 4-element discrete matching balun transformer. Because the Si4356 RF IC is pin configurable, the module can operate in RX mode with different configurations. Different carrier frequencies, data rates, modulation types, frequency deviations, and receiver bandwidths can be set by the configuration selector pins (SEL0–SEL3).These pins are connected to GND, VDD_RF, OUT0 (pin 12), or OUT1 (pin 14). The Si4356 provides the received RAW data on pin 14.The receiver performance can be significantly improved by adding a low-pass filter to the RX data output. These optional RC components are represented by R3 and C5 in Figure 1. Component values have to be calculated based on the expected data rate, where DR=1/(2*pi*R*C). For 2.4kbps, a good combination could be 1k with 47nF. For 1kbps, use 100nF.The element values of the 4-element discrete matching balun transformer depend on the operating frequency. TheN o r t Re co m m e nd edf or Ne w De si g n sSi4356RXModule-UGelement values can be found in the Si4356 data sheet and are detailed in “AN643: Si446x/Si4362 RX LNA Matching”.The module is +5V compatible; therefore, supply voltages up to +5V can be connected to the VDD. Meanwhile,the Si4356 RF IC does not tolerate voltages above +3.6V (VDD_RF). This voltage conversion between the VDD and VDD_RF (see Figure 1) is ensured by a Zener diode or an LDO; one of them should be mounted simultaneously. Do not directly connect +5V to the pins of the Si4356 RF IC! The default and typical supply voltage for the VDD is +5V while using an LDO to drive 3.3V for the Si4356 RF IC (VDD_RF). If using a Zener diode, the R1 resistor value must be determined according to the Zener diode and the supply voltages.The RST pin of the Si4356 RF IC on the small RX module is directly connected to the GND, which means that it is not possible to reset the radio chip externally. For this reason, it is strongly recommended to ensure the exact VDD requirements for the radio chip for a proper power-on-reset (POR), as documented in the Si4356 data sheet.If the documented radio VDD requirements are not carefully followed for a proper POR, and if the VDD_RF is not stable, then it is recommended to place some very large valued capacitors (100 of µF range) on the VDD and VDD_RF lines in order to avoid any unintentional "reset" due to the unstable VDD_RF (and the lack of the proper POR) that could get the radio chip into an undefined state.N o r t Re co m m e nd edf or Ne w De si g n sSi4356RXModule-UG2. Module LayoutThe layout of the module is shown in Figure 2. The PCB is approximately 11x45mm.Figure 2.Top and Bottom Layout of 4356-RX-434 Standalone Receiver ModuleThe module has two 4-pin connectors (see J1 and J2 in Figure 2), and the pin assignments are listed in Table 1.Table 1. Standalone Receiver Module Pin AssignmentsJ1J2150 point, antenna can be con-nected through this pin1Supply voltage2Ground 2Not connected (default) or CLK3Ground 3Received Data4Supply voltage4GroundN o r t Re co m m e nd edf or Ne w De si g n sSi4356RXModule-UGAs the VDD is pulled up to +5V, the module starts to work in RX mode, and all detectable signals at the selected frequency are demodulated and passed to the system MCU via the RX Data (pin 3 of J2).The module has a 50Ω input point (pin 1 of J1) where a monopole type antenna can be connected through pin 1 of the J1 connector.Notes:1. A 15MHz microcontroller clock output is available on pin 10 of the Si4356. This clock signal can be used to drive anexternal MCU and avoid the need for additional oscillators in the application. If this clock signal is not used, it can be turned off by connecting pin 10 to pin 12. By default, this clock signal is turned off; to make it available on pin 2 of J2, the SJ17 solderable jumper should be cut.2. Each of the configuration selector pins (SEL0–SEL3) are connected to four solderable jumpers connected to GND,VDD_RF, OUT0, and OUT1. With these solderable jumpers (zoomed in Figure 3), the desired configuration can be set.Figure 3 shows the solderable jumper connections.Figure 3.Top- and Bottom-Layer Configuration Selector Pin Solderable Jumper ConnectionsPlease refer to the data sheet of the Si4356 RF IC for information on how these solderable jumpers should be connected for all available configurations. The default configuration of the module is as follows:1.Frequency: 433.92MHz2.Modulation Type: OOK3.Data rate: 0.5–5kbps4.RX Bandwidth: 206kHzThe manufacturing pack, including the CAD, CAM, BOM, and PDF files of the module, can be found on the Silicon Labs home page: . More detailed information about the Si4356 RF IC can be found in the data sheet.*Note: These pins of the solderable jumpers are connected to GND through the R2 resistor (10k Ω) to avoid excess currentN o r t Re co m m e nd edf or Ne w De si g n sSi4356RXModule-UGN OTES :N o r t Re co m m e nd edf or Ne w De si g n sDisclaimerSilicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.Trademark InformationSilicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world’s most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.Silicon Laboratories Inc.400 West Cesar Chavez Austin, TX 78701USASmart.Connected.Energy-FriendlyProducts/productsQuality/qualitySupport and CommunityN o r t Re co m m e nd edf or Ne w De si g n s。

Six-Pole Bandpassfilter with Single Cross-Coupling

coupled-resonator filter is performed in this article by using the group delay response of the input reflection coefficient of sequentially tuned resonators containing all the information necessary to design and tune filters. To achieve high losses a single transmission zero is introduced producing a pair of finite frequency poles. CST (CST MWS) is used to optimize and/or tune the bandpass filter resonse in a complete model by applying the new, fast MOR-Frequency Domain Solver. To speed-up the tuning process the entire model is split up into several sections and recombined in CST DESIGN STUDIO™ (CST DS) to get the overall filter response

The example presented here is a 6-pole folded combline bandpassfilter with a center frequency = 1793 MHz, a bandwidth = 170 MHz, a return loss of VSWR= 1.2 (equivalent to -21dB) and an out-of-band rejection for frequencies 1920 MHz of less

Figure 1:Final geometry. Note, that the capacitive cross-coupling is made inactive by minimizing its length

Figure 2:Typical Chebyshev- response after completion of the tuning process

Instead of performing the optimization with the complete filter, the model was split up into several sub-sections. wWaveguide ports considering a sufficiently large number of modes are assigned at the intersections . CST MWS is used to compute the required S-parameters. Since the number of meshcells of the submodels is small compared to a complete model the runtimes are extremely short, thus the meshdensity can be increased to achieve higher accuracy. Since frequencies below cutoff are considered it is advisable to use the Frequency Domain solver within CST MWS: here the Model order Reduction

Figure 3:Definition of the sub-models: At the common interfaces between the sub-models waveguide ports are assigned (not shown here)

The sub-models are loaded into CST DS and linked together. The local sub-model parameters can be accessed and assigned to a global CST DS parameter. These parameters can be used in an optimization process. CST

scheme in order to avoid numerous recomputations of S-parameters for individual setups required by the optimizer.

Figure 4:CST MWS submodels and their connections via modes. Note the link to global CST DS parameters

Figure 5:S-Parameter view of CST DS results

In a next step, the length of the capacitive cross-coupling stub is enlarged to increase the coupling bandwidth for a quadruplet type behaviour described in [3] and [4].

Figure 6:Enlarging the length of the stub reinforces the coupling bandwidth

Figure 7:The transmission zeros are still in the upper stopband indicating that the coupling is too small. Shown here is also a comparison between a complete model and a sub-model result using CST DS

Finally, the cross-coupling is further increased, resulting in a symmetric location of the transmission zeros above and below the passband. The next two figures show the geometry and the respective S-parameters.

Figure 8:Further enlargement of the cross coupling stub

Figure 9:Results of the CST DS model: Two transmission zeros appear above and below passband. Adding a diagonally positioned coupling would allow a more symmetric rejection shape

References:

[1] John B. Ness: "A Unified Approach to the Design, Measurement, and Tuning of Coupled-Resonator Filters", IEEE Trans. on MW Theor. and Tech., Vol 46, No 4, April 1998

simply be described by low-pass prototype LC elements and by coupling coefficients of the inverter coupled filter. Approximation techniques can be used to get good initial values of the lumped elements [4] to find an optimal consecutive optimization loop. The cross-couplings requires slight changes of the theoretical Chebychev values resulting in very small geometrical modifications. A The next figure shows the equivalent network including also a cross-coupling admittance inverter with a negative C across the nodes 2 and 5.

Figure 10:Circuit elements for inverter coupled filter structures

Figure 11:Optimized filter response of the bandpass filter within CST DS Figure 12:Parameter list of optimized LC lumped element values。