HD74AC273FPEL中文资料

- 格式:pdf

- 大小:122.28 KB

- 文档页数:8

HD74AC365/HD74ACT365Hex Buffer/Driver with 3-State OutputFeatures• 3-State Outputs Drive Bus Lines or Buffer Memory Address Registers• Outputs Source/Sink 24 mA• HD74ACT365 has TTL-Compatible InputsPin ArrangementHD74AC365/HD74ACT3652Logic SymbolPin NamesOE 1, OE 23-State Output: Enable Input (Active Low)I Inputs OOutputsTruth TableInputs Output OE 1OE 2I O L L L L L L H H X H X Z H XXZH :High Voltage Level L :Low Voltage Level X :ImmaterialZ:High ImpedanceDC Characteristics (unless otherwise specified)ItemSymbol Max Unit ConditionMaximum quiescent supply current I CC 80µA V IN = V CC or ground, V CC = 5.5 V,Ta = Worst caseMaximum quiescent supply current I CC 8.0µA V IN = V CC or ground, V CC = 5.5 V,Ta = 25°CMaximum I CC /input (HD74ACT365)I CCT1.5mAV IN = V CC – 2.1 V, V CC = 5.5 V,Ta = Worst caseHD74AC365/HD74ACT3653AC Characteristics: HD74AC365Ta = +25°C C L = 50 pFTa = –40°C to +85°C C L = 50 pF ItemSymbol V CC (V)*1Min Typ Max Min Max Unit Propagation delay t PLH 3.3 1.07.09.0 1.010.0ns5.0 1.0 5.07.0 1.07.5Propagation delay t PHL 3.3 1.07.09.0 1.010.0ns 5.0 1.0 5.07.0 1.07.5Enable time t PZH 3.3 1.09.012.5 1.013.0ns 5.0 1.07.09.0 1.09.5Enable time t PZL 3.3 1.010.012.5 1.013.5ns 5.0 1.08.010.0 1.010.5Disable time t PHZ 3.3 1.09.512.0 1.012.5ns 5.0 1.07.510.0 1.010.5Disable time t PLZ3.3 1.09.012.5 1.013.5ns 5.01.07.010.01.010.5Note:1.Voltage Range 3.3 is 3.3 V ± 0.3 VVoltage Range 5.0 is 5.0 V ± 0.5 VAC Characteristics: HD74ACT365Ta = +25°C C L = 50 pFTa = –40°C to +85°C C L = 50 pF ItemSymbol V CC (V)*1Min Typ Max Min Max Unit Propagation delay t PLH 5.0 1.0 6.59.0 1.010.0ns Propagation delay t PHL 5.0 1.0 6.59.0 1.010.0ns Enable time t PZH 5.0 1.08.010.5 1.011.0ns Enable time t PZL 5.0 1.09.512.0 1.013.0ns Disable time t PHZ 5.0 1.09.512.0 1.013.0ns Disable time t PLZ5.01.08.010.51.011.5nsNote:1.Voltage Range 5.0 is 5.0 V ± 0.5 VCapacitanceItemSymbol Typ Unit Condition Input capacitanceC IN 4.5pF V CC = 5.5 V Power dissipation capacitanceC PD45.0pFV CC = 5.0 VHitachi CodeJEDECEIAJWeight (reference value)DP-16 Conforms Conforms 1.07 gHitachi Code JEDEC EIAJWeight (reference value)FP-16DA —Conforms 0.24 g*Dimension including the plating thicknessBase material dimension° – 8°Hitachi CodeJEDECEIAJWeight (reference value)FP-16DN Conforms Conforms 0.15 g*Dimension including the plating thickness Base material dimension° – 8°Hitachi CodeJEDECEIAJWeight (reference value)TTP-16DA ——0.05 g*Dimension including the plating thickness Base material dimensionCautions1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, includingintellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Hitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright ' Hitachi, Ltd., 1999. All rights reserved. Printed in Japan.Hitachi Asia Pte. Ltd.16 Collyer Quay #20-00Hitachi TowerSingapore 049318Tel: 535-2100Fax: 535-1533URLNorthAmerica : http:/Europe : /hel/ecg Asia (Singapore): .sg/grp3/sicd/index.htm Asia (Taiwan): /E/Product/SICD_Frame.htm Asia (HongKong): /eng/bo/grp3/index.htm Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.Taipei Branch Office3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105)Tel: <886> (2) 2718-3666Fax: <886> (2) 2718-8180Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components)7/F., North Tower, World Finance Centre,Harbour City, Canton Road, Tsim Sha Tsui,Kowloon, Hong Kong Tel: <852> (2) 735 9218Fax: <852> (2) 730 0281 Telex: 40815 HITEC HXHitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 778322Hitachi Europe GmbHElectronic components Group Dornacher Stra§e 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:。

1/11April 2001s HIGH SPEED:s f MAX = 250MHz (TYP.) at V CC = 5V sLOW POWER DISSIPATION:I CC = 8µA(MAX.) at T A =25°C sHIGH NOISE IMMUNITY:V NIH = V NIL = 28 % V CC (MIN.)s50Ω TRANSMISSION LINE DRIVING CAPABILITYsSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 24mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsOPERATING VOLTAGE RANGE:V CC (OPR) = 2V to 6VsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 273sIMPROVED LATCH-UP IMMUNITYDESCRIPTIONThe 74AC273 is an advanced high-speed CMOS OCTAL D-TYPE FLIP FLOP WITH CLEAR fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology. Information signals applied to D inputs aretransfered to the Q output on the positive goingedge of the clock pulse.When the CLEAR input is held low, the Q outputs are held low independentely of the other inputs. All inputs and outputs are equipped with protection circuits against static discharge, giving them 2KV ESD immunity and transient excess voltage.74AC273OCTAL D-TYPE FLIP FLOP WITH CLEARPIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODESPACKAGE TUBE T & RDIP 74AC273B SOP 74AC273M74AC273MTRTSSOP74AC273TTRs l c )d u c t () -O bs o e t eP r od u t (s74AC2732/11INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLELOGIC DIAGRAMThis logic diagram has not be used to estimate propagation delaysPIN No SYMBOL NAME AND FUNCTION 1CLEAR Asyncronous Master Reset (Active LOW)2, 5, 6, 9, 12, 15, 16,19Q0 to Q7Flip-Flop Outputs 3, 4, 7, 8, 13, 14, 17, 18D0 to D7Data Inputs11CLOCK Clock Input (LOW-to-HIGH Edge Triggered)10GND Ground (0V)20V CCPositive Supply Voltagel s l u )Ob so e t ePr od u c t () -O bs o e t eP r od c t(s74AC2733/11ABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.RECOMMENDED OPERATING CONDITIONS1) V IN from 30% to 70% of V CCSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7V V I DC Input Voltage -0.5 to V CC + 0.5V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current ± 20mA I OK DC Output Diode Current ± 20mA I O DC Output Current ± 50mA I CC or I GND DC V CC or Ground Current± 400mA T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValue UnitV CC Supply Voltage 2 to 6V V I Input Voltage 0 to V CCV V O Output Voltage 0 to V CCV T op Operating Temperature-55 to 125°Cdt/dvInput Rise and Fall Time V CC = 3.0, 4.5 or 5.5V (note 1)8ns/Vl s e c )Ob so e t ePr od u c t () -O bs o l t eP r od u t (s74AC2734/11DC SPECIFICATIONS2) Incident wave switching is guaranteed on transmission lines with impedances as low as 50ΩSymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage3.0V O = 0.1 V or V CC -0.1V 2.1 1.5 2.1 2.1V4.5 3.15 2.25 3.15 3.155.5 3.852.753.853.85V ILLow Level Input Voltage3.0V O = 0.1 V or V CC -0.1V 1.50.90.90.9V4.5 2.25 1.35 1.35 1.355.5 2.75 1.651.651.65V OHHigh Level Output Voltage3.0I O =-50 µA 2.9 2.99 2.9 2.9V4.5I O =-50 µA 4.4 4.49 4.4 4.45.5I O =-50 µA 5.4 5.495.4 5.43.0I O =-12 mA 2.56 2.46 2.44.5I O =-24 mA 3.86 3.76 3.75.5I O =-24 mA 4.864.764.7V OLLow Level Output Voltage3.0I O =50 µA 0.0020.10.10.1V4.5I O =50 µA 0.0010.10.10.15.5I O =50 µA 0.0010.10.10.13.0I O =12 mA 0.360.440.54.5I O =24 mA 0.360.440.55.5I O =24 mA 0.360.440.5I I Input Leakage Current5.5V I = V CC or GND ± 0.1± 1± 1µA I CC Quiescent Supply Current5.5V I = V CC or GND880160µA I OLD Dynamic Output Current (note 1, 2)5.5V OLD = 1.65 V max 7550mA I OHDV OHD = 3.85 V min-75-50mAl t l c )Ob so e t ePr od u c (s ) -O bs o e t eP r od u t (s74AC2735/11AC ELECTRICAL CHARACTERISTICS (C L = 50 pF, R L = 500 Ω, Input t r = t f = 3ns)(*) Voltage range is 3.3V ± 0.3V (**) Voltage range is 5.0V ± 0.5VCAPACITIVE CHARACTERISTICSPD load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /8 (per circuit)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t PLH t PHL Propagation Delay TimeCLOCK to Q3.3(*)4.07.512.5 3.014.0 3.016.0ns5.0(**) 3.0 5.09.0 2.510.0 2.511.0t PHL Propagation Delay TimeCLEAR to Q3.3(*)4.08.513.0 3.014.0 3.016.0ns5.0(**) 3.06.510.02.511.02.512.0t W CLEAR Pulse Width, LOW3.3(*)5.56.0 6.0ns 5.0(**)4.0 4.5 4.5t W CLOCK Pulse Width3.3(*) 5.5 6.0 6.0ns5.0(**)4.0 4.5 4.5t s Setup Time D to CLOCK, HIGH orLOW3.3(*) 5.5 6.0 6.0ns5.0(**) 4.0 4.5 4.5t h Hold Time D toCLOCK, HIGH or LOW3.3(*) 1.5 1.5 1.5ns5.0(**) 1.5 1.51.5t REM Recovery Time CLEAR to CLOCK 3.3(*) 4.0 4.5 4.5ns 5.0(**) 3.0 3.0 3.0f MAXMaximum Clock Frequency3.3(*)907575MHz5.0(**)140250125125Symbol ParameterTest ConditionValueUnitV CC(V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance5.04pF C PDPower DissipationCapacitance (note 1)5.0f IN = 10MHz32pFc u t 74AC2736/11TEST CIRCUITC L = 50pF or equivalent (includes jig and probe capacitance)R L = R 1 = 500Ω or equivalentR T = Z OUT of pulse generator (typically 50Ω)WAVEFORM 1: PROPAGATION DELAYS, SETUP AND HOLD TIMES (f=1MHz; 50% duty cycle)74AC273 WAVEFORM 2: PROPAGATION DELAYS (f=1MHz; 50% duty cycle)WAVEFORM 3: RECOVERY TIME (f=1MHz; 50% duty cycle)7/11l slc)O b s oe t eP ro du ct()-O bs oe t eP ro dut(s74AC273Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2001 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - MoroccoSingapore - Spain - Sweden - Switzerland - United Kingdom© 11/11芯天下--/。

元器件交易网Hitachi CodeJEDECEIAJWeight (reference value)DP-14ConformsConforms0.97 gUnit: mm元器件交易网Hitachi CodeJEDECEIAJWeight (reference value)FP-14DA —Conforms 0.23 g*Dimension including the plating thickness Base material dimension° – 8°Hitachi CodeJEDEC EIAJWeight (reference value)FP-14DN Conforms Conforms 0.13 g° – 8°*Pd platingCautions1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, includingintellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Hitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright ' Hitachi, Ltd., 1999. All rights reserved. Printed in Japan.Hitachi Asia Pte. Ltd.16 Collyer Quay #20-00Hitachi TowerSingapore 049318Tel: 535-2100Fax: 535-1533URLNorthAmerica : http:/Europe : /hel/ecg Asia (Singapore): .sg/grp3/sicd/index.htm Asia (Taiwan): /E/Product/SICD_Frame.htm Asia (HongKong): /eng/bo/grp3/index.htm Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.Taipei Branch Office3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105)Tel: <886> (2) 2718-3666Fax: <886> (2) 2718-8180Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components)7/F., North Tower, World Finance Centre,Harbour City, Canton Road, Tsim Sha Tsui,Kowloon, Hong Kong Tel: <852> (2) 735 9218Fax: <852> (2) 730 0281 Telex: 40815 HITEC HXHitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 778322Hitachi Europe GmbHElectronic components Group Dornacher Stra§e 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:。

HD74HC14Hex InvertersREJ03D0540-0200(Previous ADE-205-412)Rev.2.00Oct 06, 2005 Features• High Speed Operation: t pd = 10.5 ns typ (C L = 50 pF)• High Output Current: Fanout of 10 LSTTL Loads• Wide Operating Voltage: V CC = 2 to 6 V• Low Input Current: 1 µA max• Low Quiescent Supply Current: I CC (static) = 1 µA max (Ta = 25°C)• Ordering InformationPart Name Package TypePackage Code(Previous Code)PackageAbbreviationTaping Abbreviation(Quantity)HD74HC14P DILP-14pin PRDP0014AB-B(DP-14AV)P —HD74HC14FPEL SOP-14 pin (JEITA) PRSP0014DF-B(FP-14DAV)FP EL (2,000 pcs/reel)HD74HC14RPEL SOP-14 pin (JEDEC) PRSP0014DE-A(FP-14DNV)RP EL (2,500 pcs/reel)HD74HC14TELL TSSOP-14pin PTSP0014JA-B(TTP-14DV)T ELL(2,000pcs/reel)Note: Please consult the sales office for the above package availability.Function TableInput OutputA YL HH L H : High levelL : Low levelPin ArrangementAbsolute Maximum RatingsItem Symbol Ratings UnitSupply voltage range V CC –0.5 to 7.0 V Input / Output voltage Vin, Vout –0.5 to V CC +0.5VInput / Output diode current I IK , I OK ±20 mAOutput current I O±25 mAV CC , GND current I CC or I GND ±50 mAPower dissipationP T 500 mWStorage temperature Tstg –65 to +150 °CNote: The absolute maximum ratings are values, which must not individually be exceeded, and furthermore, no two ofwhich may be realized at the same time.Recommended Operating ConditionsItem Symbol Ratings Unit ConditionsSupply voltage V CC 2 to 6 V Input / Output voltage V IN , V OUT 0 to V CC V Operating temperature Ta –40 to 85 °C 0 to unlimited V CC = 2.0 V 0 to unlimitedV CC = 4.5 V Input rise / fall time *1t r , t f0 to unlimitednsV CC = 6.0 VNote: 1. This item guarantees maximum limit when one input switches. Waveform: Refer to test circuit of switching characteristics.Electrical CharacteristicsTa = 25°CTa = –40 to+85°CItem Symbol V CC (V) Min Typ Max Min Max UnitTest Conditions2.0 — — 1.5 — 1.5 4.5 — —3.15 — 3.15V T +6.0 — — 4.2 — 4.2V2.0 0.3 — — 0.3 — 4.5 0.9 — — 0.9 — Threshold voltage V T -6.0 1.2 — — 1.2 —V 2.0 0.2 — 1.2 0.2 1.2 4.5 0.4 — 2.25 0.4 2.25 Hysteresis voltage V H6.0 0.6 — 3.0 0.6 3.0V 2.0 1.9 2.0 — 1.9 — 4.5 4.4 4.5 — 4.4 — 6.0 5.9 6.0 — 5.9 — I OH = –20 µA 4.5 4.18 — — 4.13 —I OH = –4 mAV OH6.0 5.68 — — 5.63 — V Vin = V IH or V IL I OH = –5.2 mA 2.0 — 0.0 0.1 — 0.1 4.5 — 0.0 0.1 — 0.1 6.0 — 0.0 0.1 — 0.1 I OL = 20 µA 4.5 — — 0.26 — 0.33 I OL = 4 mAOutput voltage V OL6.0 — — 0.26 — 0.33V Vin = V IH or V IL I OL = 5.2 mAInput currentIin 6.0 — — ±0.1 — ±1.0 µA Vin = V CC or GND Quiescent supply current I CC 6.0 — — 1.0 — 10 µA Vin = V CC or GND, Iout = 0 µASwitching Characteristics (C L = 50 pF, Input t r = t f = 6 ns)Ta = 25°C Ta = –40 to +85°CItem Symbol V CC (V) Min Typ Max Min Max UnitTest Conditions2.0 — — 125 — 155 4.5 — 10 25 — 31 t PLH6.0 — — 21 — 26 ns 2.0 — — 125 — 155 4.5 — 11 25 — 31 Propagation delaytimet PHL6.0 — — 21 — 26ns 2.0 — — 75 — 95 4.5 — 5 15 — 19 Output rise timet TLH6.0 — — 13 — 16ns 2.0 — — 75 — 95 4.5 — 5 15 — 19 Output fall time t THL6.0 — — 13 — 16ns Input capacitance Cin——510—10pFTest CircuitWaveformsPackage Dimensions RENESAS SALES OFFICESRefer to "/en/network" for the latest and detailed information.Renesas Technology America, Inc.450 Holger Way, San Jose, CA 95134-1368, U.S.ATel: <1> (408) 382-7500, Fax: <1> (408) 382-7501Renesas Technology Europe LimitedDukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900Renesas Technology Hong Kong Ltd.7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong KongTel: <852> 2265-6688, Fax: <852> 2730-6071Renesas Technology Taiwan Co., Ltd.10th Floor, No.99, Fushing North Road, Taipei, TaiwanTel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999Renesas Technology (Shanghai) Co., Ltd.Unit2607 Ruijing Building, No.205 Maoming Road (S), Shanghai 200020, ChinaTel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952Renesas Technology Singapore Pte. Ltd.1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632Tel: <65> 6213-0200, Fax: <65> 6278-8001Renesas Technology Korea Co., Ltd.Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, KoreaTel: <82> 2-796-3115, Fax: <82> 2-796-2145Renesas Technology Malaysia Sdn. Bhd.Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, MalaysiaTel: <603> 7955-9390, Fax: <603> 7955-9510。

HD74BC374AOctal D Type Flip Flops With 3 State OutputsREJ03D0284–0300Z(Previous ADE-205-010A (Z))Rev.3.00Jul.16.2004 DescriptionThe HD74BC374A provides high drivability and operation equal to or better than high speed bipolar standard logic IC by using Bi-CMOS process. The device features low power dissipation that is about 1/5 of high speed bipolar logic IC, when the frequency is 10 MHz. The device has eight edge triger D type flip flop with three state outputs in a 20 pin package. Data at the D inputs meeting set up reguirements, are transferred to the Q outputs on positive going transitions of the clock input. When the latch enable goes low, data at the D inputs will be retained at the outputs until latch enable returns high again. When a high logic level is applied to the output control input, all outputs go to a high impedance state, regardless of what signals are present at the other inputs and the state of the storage elements.Features•Input/Output are at high impedance state when power supply is off.•Built in input pull up circuit can make input pins be open, when not used.•TTL level input•Wide operating temperature rangeTa = –40 to + 85°C•Ordering InformationPart Name Package Type Package Code PackageAbbreviation Taping Abbreviation(Quantity)HD74BC374AFPEL SOP-20 pin (JEITA)FP-20DAV FP EL (2,000 pcs/reel) Function TableL:Low levelX:ImmaterialZ:High impedance:Low to high transitionPin ArrangementAbsolute Maximum RatingsItemSymbolRatingUnitSupply voltage V CC –0.5 to +7.0V Input diode current I IK ±30mA Input voltage V IN –0.5 to +7.5V Output voltage V OUT –0.5 to +7.5V Off state output voltage V OUT(off)–0.5 to +5.5V Storage temperature Tstg–65 to +150°CNote:1.The absolute maximum ratings are values which must not individually be exceeded, and furthermore, no twoof which may be realized at the same time.Recommended Operating ConditionsItemSymbolMinTypMaxUnitSupply voltage V CC 4.5 5.0 5.5V Input voltageV IN 0—V CC V Output voltageV OUT 0—V CC V Operating temperatureTopr–40—85°C Input rise/fall time *1t r , t f 0—8ns/VNote: 1.This item guarantees maximum limit when one input switches.Waveform: Refer to test circuit of switching characteristics.Logic DiaglamElectrical Characteristics (Ta = –40°C to +85°C)ItemSymbol V CC (V)Min Max UnitTest ConditionsInput voltage V IH 2.0—V V IL —0.8V Output voltageV OH 4.5 2.4—V I OH = –3 mA 4.5 2.0—V I OH = –15 mA V OL4.5—0.4V I OL = 24 mA 4.5—0.5V I OL = 48 mA Input diode voltage V IK 4.5—–1.2V I IN = –18 mA Input currentI I5.5— 1.0µA V IN = 5.5 V 5.5—–250µA V IN = 0 V 5.5—100µA V IN = 7.0 V Short circuit output current *1I OS 5.5–100–225mA V IN = 0 or 5.5 V Off state output current I OZH 5.5—50µA V O = 2.7 V I OZL 5.5—–50µA V O = 0.5 VSupply currentI CCL 5.5—29.5mA V IN = 0 or 5.5 V All output is “L”I CCH 5.5— 2.5mA V IN = 0 or 5.5 V All output is “H”I CCZ5.5—2.5mAV IN = 0 or 5.5 V All output is “Z”I CCT *2 5.5— 1.5mA V IN = 3.4 or 0.5 VNotes :1.Not more than one output should be shorted at a time and duration of the short circuit should not exceed onesecond.2.When input by the TTL level, it shows I CC increase at per one input pin.Switching Test Method (C L = 50 pF)Ta = 25°C V CC = 5.0 VTa = –40 to 85°C V CC = 5.0 V ±10%ItemSymbol Min Max Min Max Unit Test Conditions Propagation CK →Q t PLH 3.08.0 3.010.0ns See under figure delay timet PHL 3.08.0 3.010.0Output enable time t ZH 3.09.0 3.011.0ns t ZL 3.09.0 3.011.0Output disable time t HZ 3.08.0 3.010.0ns t LZ 3.08.0 3.010.0Setup time t s (H) 2.0— 2.0—ns t s (L) 2.0— 2.0—Hold time t h (H) 2.0— 2.0—ns t h (L) 2.0— 2.0—Pulse width t w (H) 6.0—6.0—nst w (L) 6.0—6.0—Input capacitance C IN 3.0(Typ)—pF V IN = V CC or GND Output capacitanceC O15.0(Typ)—pFV O = V CC or GNDTest CircuitWaveforms-2Package Dimensions RENESAS SALES OFFICESRenesas Technology America, Inc.450 Holger Way, San Jose, CA 95134-1368, U.S.ATel: <1> (408) 382-7500 Fax: <1> (408) 382-7501Renesas Technology Europe Limited.Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, United KingdomTel: <44> (1628) 585 100, Fax: <44> (1628) 585 900Renesas Technology Europe GmbHDornacher Str. 3, D-85622 Feldkirchen, GermanyTel: <49> (89) 380 70 0, Fax: <49> (89) 929 30 11Renesas Technology Hong Kong Ltd.7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Hong KongTel: <852> 2265-6688, Fax: <852> 2375-6836Renesas Technology Taiwan Co., Ltd.FL 10, #99, Fu-Hsing N. Rd., Taipei, TaiwanTel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999Renesas Technology (Shanghai) Co., Ltd.26/F., Ruijin Building, No.205 Maoming Road (S), Shanghai 200020, ChinaTel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952Renesas Technology Singapore Pte. Ltd.1, Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632Tel: <65> 6213-0200, Fax: <65> 6278-8001© 2004. Renesas Technology Corp., All rights reserved. Printed in Japan.Colophon .1.0。

HD74LV123ADual Retriggerable Monostable MultivibratorsREJ03D0314–0600Z(Previous ADE-205-258D (Z))Rev.6.00Jun. 02, 2004 DescriptionThe HD74LV123A features output pulse-duration control by three methods. In the first method, the A input is low and the B input goes high. In the second method, the B input is high and the A input goes low. In the third method, the A input is low, the B input is high, and the clear (CLR) input goes high.The basic pulse duration is programmed by selecting external resistance and capacitance values.The external timing capacitor must be connected between Cext and Rext/Cext (positive) and an external resistor connected between Rext/Cext and VccTo obtain variable pulse durations, connect an external variable resistance between Rext/Cext and Vcc.Once triggered, the basic pulse duration can be extended by retriggering the gated low-level-active (A) or high-level-active (B) input. Pulse duration can be reduced by taking CLR low.Features•V CC = 2.0 V to 5.5 V operation•All inputs V IH (Max.) = 5.5 V (@V CC = 0 V to 5.5 V)•All outputs V O (Max.) = 5.5 V (@V CC = 0 V)•Output current ±6 mA (@V CC = 3.0 V to 3.6 V), ±12 mA (@V CC = 4.5 V to 5.5 V)•Ordering InformationPart Name Package Type Package Code PackageAbbreviation Taping Abbreviation (Quantity)HD74LV123AFPEL SOP–16 pin(JEITA)FP–16DAV FP EL (2,000 pcs/reel) HD74LV123ARPEL SOP–16 pin(JEDEC)FP–16DNV RP EL (2,500 pcs/reel) HD74LV123ATELL TSSOP–16 pin TTP–16DAV T ELL (2,000 pcs/reel) Note: Please consult the sales office for the above package availability.Function TableInputs OutputsCLR A B Q Q L X X L H H H X L HL:Low levelX:Immaterial↑:Low to high transition↓:High to low transition:High level pulse:Low level pulsePin ArrangementAbsolute Maximum RatingsItemSymbol Ratings Unit ConditionsSupply voltage range V CC –0.5 to 7.0V Input voltage range*V I –0.5 to 7.0V –0.5 to V CC + 0.5Output: H or L Output voltage range*V O–0.5 to 7.0V V CC : OFF Input clamp current I IK –20mA V I < 0Output clamp currentI OK ±50mA V O < 0 or V O > V CC Continuous output current I O±25mA V O = 0 to V CCContinuous current through V CC or GNDI CC or I GND ±50mA 785SOP Maximum power dissipation at Ta = 25°C (in still air)*3P T 500mW TSSOPStorage temperatureTstg–65 to 150°CNotes:The absolute maximum ratings are values, which must not individually be exceeded, and furthermore, no two ofwhich may be realized at the same time.1.The input and output voltage ratings may be exceeded if the input and output clamp-current ratings areobserved.2.This value is limited to 5.5 V maximum.3.The maximum package power dissipation was calculated using a junction temperature of 150°C.Recommended Operating ConditionsItemSymbol Min Typ Max Unit ConditionsSupply voltage range V CC 2.0— 5.5V Input voltage range V I 0— 5.5V Output voltage range V O 0—V CC V ——–50µA V CC = 2.0 V——–2V CC = 2.3 to 2.7 V ——–6V CC = 3.0 to 3.6 V I OH——–12mAV CC = 4.5 to 5.5 V ——50µA V CC = 2.0 V——2V CC = 2.3 to 2.7 V ——6V CC = 3.0 to 3.6 V Output currentI OL——12mAV CC = 4.5 to 5.5 V 0—200V CC = 2.3 to 2.7 V 0—100V CC = 3.0 to 3.6 V Input transition rise or fall rate ∆t /∆v 0—20ns/VV CC = 4.5 to 5.5 V 5——V CC = 2.0 V External timing resistance Rext 1——k ΩV CC ≥ 2.3 VExternal timing capacitance Cext —Unlimited —F Power-up ramp rate∆t /∆V CC 1——ms/V Operating free-air temperatureTa–40—85°CNote:Unused or floating inputs must be held high or low.Logic DiagramDC Electrical CharacteristicsTa = –40 to 85°CItem Symbol V CC (V)*Min Typ Max Unit Test Conditions2.01.5——2.3 to 2.7V CC × 0.7——3.0 to 3.6V CC × 0.7——V IH4.5 to5.5V CC × 0.7——2.0——0.52.3 to 2.7——V CC × 0.33.0 to 3.6——V CC × 0.3Input voltageV IL4.5 to5.5——V CC × 0.3VMin to Max V CC – 0.1——I OH = –50 µA 2.3 2.0——I OH = –2 mA 3.0 2.48——I OH = –6 mA V OH 4.53.8——I OH = –12 mA Min to Max ——0.1I OL = 50 µA 2.3——0.4I OL = 2 mA 3.0——0.44I OL = 6 mA Output voltage V OL4.5——0.55VI OL = 12 mAInput current I IN 0 to 5.5——±1µA V IN = 5.5 V or GND Input current Rext / Cext I IN 5.5——±2.5µA V IN = V CC or GND Quiescent supply currentI CC 5.5——20µA V IN = V CC or GND, I O = 02.3——2203.0——2804.5——650Active state supply current (per circuit)∆I CC5.5——975µAV IN = V CC or GND Rext/Cext = 0.5 V CCOutput leakage currentI OFF 0——5µA V I or V O = 0 V to 5.5 V Input capacitanceC IN3.3—4.0—pFV I = V CC or GNDNote:For conditions shown as Min or Max, use the appropriate values under recommended operating conditions.Switching CharacteristicsV CC = 2.5 ± 0.2 VTa = 25°CTa = –40 to 85°C Item Symbol Min Typ Max Min Max Unit TestConditionsFROM (Input)TO(Output)—13.531.4 1.037.0C L = 15 pF —16.036.0 1.042.0C L = 50 pF A or B Q or Q —11.025.0 1.029.5C L = 15 pF —13.032.8 1.034.5C L = 50 pF —14.033.4 1.039.0C L = 15 pF Propagation delay timet PLH t PHL—16.038.0 1.044.0nsC L = 50 pFCLR (Trigger)Q or Q—170260—320ns C L = 50 pF, Cext = 28 pF, Rext = 2 k Ω9010011090110µs C L = 50 pF,Cext = 0.01 µF, Rext = 10 k Ωt wQ0.91.0 1.10.9 1.1ms C L = 50 pF,Cext = 0.1 µF, Rext = 10 k ΩOutput pulse width∆t wQ —±1———%C L = 50 pF Pulse width t w 6.0—— 6.5—ns A , B or CLR—40———ns A , or B(Rext = 1 k Ω, Cext = 100 pF)Retrigger timet rr—1.5———µsA , or B(Rext = 1 k Ω, Cext = 0.01 µF)V CC = 3.3 ± 0.3 VTa = 25°CTa = –40 to 85°C Item Symbol Min Typ Max Min Max Unit TestConditions FROM (Input)TO(Output)—9.720.6 1.024.0C L = 15 pF —11.524.1 1.027.5C L = 50 pF A or B Q or Q —8.015.8 1.018.5C L = 15 pF —9.519.3 1.022.0C L = 50 pF CLR Q or Q —9.922.4 1.026.0C L = 15 pF Propagation delay timet PLH t PHL—11.525.9 1.029.5nsC L = 50 pF(Trigger)Q or Q—150240—300ns C L = 50 pF, Cext = 28 pF, Rext = 2 k Ω9010011090110µs C L = 50 pF,Cext = 0.01 µF, Rext = 10 k Ωt wQ0.91.0 1.10.9 1.1ms C L = 50 pF,Cext = 0.1 µF, Rext = 10 k ΩOutput pulse width∆t wQ —±1———%C L = 50 pF Pulse width t w 5.0—— 5.0—ns A , B or CLR—30———ns A , or B(Rext = 1 k Ω, Cext = 100 pF)Retrigger timet rr—1.2———µsA , or B(Rext = 1 k Ω, Cext = 0.01 µF)Switching Characteristics (cont)V CC = 5.0 ± 0.5 VTa = 25°CTa = –40 to 85°C Item Symbol Min Typ Max Min Max Unit TestConditionsFROM (Input)TO(Output)—7.312.0 1.014.0C L = 15 pF —8.514.0 1.016.0C L = 50 pF A or B Q or Q — 5.99.4 1.011.0C L = 15 pF —7.511.4 1.013.0C L = 50 pF —7.312.9 1.015.0C L = 15 pF Propagation delay timet PLH t PHL—8.714.9 1.017.0nsC L = 50 pFCLR (Trigger)Q or Q—140200—240ns C L = 50 pF, Cext = 28 pF, Rext = 2 k Ω9010011090110µs C L = 50 pF,Cext = 0.01 µF, Rext = 10 k Ωt wQ0.91.0 1.10.9 1.1ms C L = 50 pF,Cext = 0.1 µF, Rext = 10 k ΩOutput pulse width∆t wQ —±1———%C L = 50 pF Pulse width t w 5.0—— 5.0—ns A , B or CLR—20———ns A , or B(Rext = 1 k Ω, Cext = 100 pF)Retrigger timet rr—0.95———µsA , or B(Rext = 1 k Ω, Cext = 0.01 µF)Operating CharacteristicsC L = 50 pFTa = 25°CItemSymbol V CC (V)Min Typ Max Unit Test Conditions 3.3—74.0—Power dissipation capacitanceC PD5.0—86.0—pFf = 10 MHzTest CircuitTiming diagramApplication DataPackage Dimensions RENESAS SALES OFFICESRenesas Technology America, Inc.450 Holger Way, San Jose, CA 95134-1368, U.S.ATel: <1> (408) 382-7500 Fax: <1> (408) 382-7501Renesas Technology Europe Limited.Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, United KingdomTel: <44> (1628) 585 100, Fax: <44> (1628) 585 900Renesas Technology Europe GmbHDornacher Str. 3, D-85622 Feldkirchen, GermanyTel: <49> (89) 380 70 0, Fax: <49> (89) 929 30 11Renesas Technology Hong Kong Ltd.7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Hong KongTel: <852> 2265-6688, Fax: <852> 2375-6836Renesas Technology Taiwan Co., Ltd.FL 10, #99, Fu-Hsing N. Rd., Taipei, TaiwanTel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999Renesas Technology (Shanghai) Co., Ltd.26/F., Ruijin Building, No.205 Maoming Road (S), Shanghai 200020, ChinaTel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952Renesas Technology Singapore Pte. Ltd.1, Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632Tel: <65> 6213-0200, Fax: <65> 6278-8001Colophon .1.0。

HD74AC273Octal D-Type Flip-FlopADE-205-386 (Z)1st. EditionSep. 2000 DescriptionThe HD74AC273 has eight edge-triggered D-type flip-flops with individual D inputs and Q outputs. The common buffered Clock (CP) and Master Reset (MR) inputs load and reset (clear) all flip-flops simultaneously.The register is fully edge-triggered. The state of each D input, one setup time before the Low-to-High clock transition, is transferred to the corresponding flip-flops’s Q outputAll outputs will be forced Low independently of Clock or Data inputs by a Low voltage level on the MR input. The device is useful for applications where the true output only is required and the Clock and Master Reset are common to all storage elements.Features• Ideal Buffer for MOS Microprocessor or Memory• Eight Edge-Triggered D Flip-Flops• Buffered Common Clock• Buffered, Asynchronous Master Reset• See HD74AC373 for Transparent Latch Version• See HD74AC374 for 3-State Version• Outputs Source/Sink 24 mAHD74AC2732Pin ArrangementLogic SymbolPin NamesD 0 – D 7Data Inputs MR Master Reset CP Clock Pulse Input Q 0 – Q 7Data OutputsHD74AC2733Logic DiagramMode Select-Truth TableInputsOutputs Operating Mode MR CP D n Q n Reset (Clear)L XX L L :Low Voltage Level X :Immaterial:Low-to-High Clock TransitionDC Characteristics (unless otherwise specified)ItemSymbol Max Unit ConditionMaximum quiescent supply current I CC 80µA V IN = V CC or ground, V CC = 5.5 V,Ta = Worst caseMaximum quiescent supply currentI CC8.0µAV IN = V CC or ground, V CC = 5.5 V,Ta = 25°CHD74AC2734AC Characteristics: HD74AC273Ta = +25°C C L = 50 pFTa = –40°C to +85°C C L = 50 pF ItemSymbol V CC (V)*1Min Typ Max Min Max Unit Maximum clock f max3.390125—75—MHzfrequency 5.0140175—125—Propagation delay t PLH 3.3 1.07.012.5 1.014.0ns Clock to output 5.0 1.0 5.59.0 1.010.0Propagation delay t PHL 3.3 1.07.013.0 1.014.5ns Clock to output 5.0 1.0 5.010.0 1.011.0Propagation delay t PHL 3.3 1.07.013.0 1.014.0ns MR to output 5.01.05.010.01.010.5Note:1.Voltage Range 3.3 is 3.3 V ± 0.3 VVoltage Range 5.0 is 5.0 V ± 0.5 VAC Operating Requirements: HD74AC273Ta = +25°C C L = 50 pFTa = –40°C to +85°C C L = 50 pFItemSymbol V CC (V)*1Typ Guaranteed MinimumUnit Setup time, HIGH or LOW t su3.3 3.5 5.5 6.0nsData to CP5.0 2.5 4.0 4.5Hold time, HIGH or LOW t h3.3–2.00.00.0ns Data to CP 5.0–1.0 1.0 1.0Clock pulse width t w 3.3 3.5 5.5 6.0ns HIGH or LOW 5.0 2.54.0 4.5MR Pulse width t w 3.3 2.05.56.0ns HIGH or LOW 5.0 1.5 4.0 4.5Recovery time t rec 3.3 1.5 3.5 4.5ns MR to CP 5.01.02.03.0Note:1.Voltage Range 3.3 is 3.3 V ± 0.3 VVoltage Range 5.0 is 5.0 V ± 0.5 VHD74AC2735CapacitanceItemSymbol Typ Unit Condition Input capacitanceC IN 4.5pF V CC = 5.5 V Power dissipation capacitanceC PD50.0pFV CC = 5.0 VHD74AC273 Package Dimensions6HD74AC2737HD74AC2738Cautions1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, includingintellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Hitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright © Hitachi, Ltd., 2000. All rights reserved. Printed in Japan.Hitachi Asia Ltd. Hitachi Tower16 Collyer Quay #20-00, Singapore 049318Tel : <65>-538-6533/538-8577 Fax : <65>-538-6933/538-3877URL : .sg URLNorthAmerica : /Europe : /hel/ecg Asia : Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.(Taipei Branch Office)4/F, No. 167, Tun Hwa North Road, Hung-Kuo Building, Taipei (105), Taiwan Tel : <886>-(2)-2718-3666 Fax : <886>-(2)-2718-8180 Telex : 23222 HAS-TPURL : Hitachi Asia (Hong Kong) Ltd. Group III (Electronic Components) 7/F., North Tower, World Finance Centre,Harbour City, Canton Road Tsim Sha Tsui, Kowloon, Hong KongTel : <852>-(2)-735-9218 Fax : <852>-(2)-730-0281URL : Hitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 585160Hitachi Europe GmbHElectronic Components Group Dornacher Stra βe 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:Colophon 2.0。

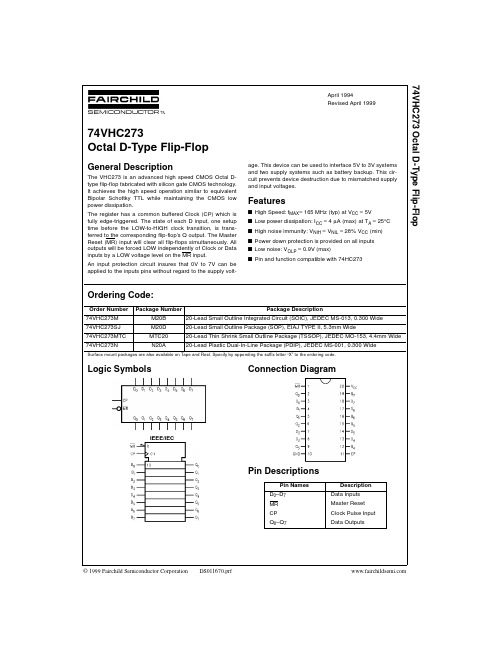

April 1994Revised April 199974VHC273 Octal D-Type Flip-Flop © 1999 Fairchild Semiconductor Corporation DS011670.prf 74VHC273Octal D-Type Flip-FlopGeneral DescriptionThe VHC273 is an advanced high speed CMOS Octal D-type flip-flop fabricated with silicon gate CMOS technology.It achieves the high speed operation similar to equivalentBipolar Schottky TTL while maintaining the CMOS lowpower dissipation.The register has a common buffered Clock (CP) which isfully edge-triggered. The state of each D input, one setuptime before the LOW-to-HIGH clock transition, is trans-ferred to the corresponding flip-flop’s Q output. The MasterReset (MR) input will clear all flip-flops simultaneously. Alloutputs will be forced LOW independently of Clock or Datainputs by a LOW voltage level on the MR input.An input protection circuit insures that 0V to 7V can beapplied to the inputs pins without regard to the supply volt-age. This device can be used to interface 5V to 3V systemsand two supply systems such as battery backup. This cir-cuit prevents device destruction due to mismatched supplyand input voltages.Featuress High Speed: f MAX= 165 MHz (typ) at V CC= 5Vs Low power dissipation: I CC= 4 µA (max) at T A= 25°Cs High noise immunity: V NIH= V NIL= 28% V CC (min)s Power down protection is provided on all inputss Low noise: V OLP= 0.9V (max)s Pin and function compatible with 74HC273Ordering Code:Surface mount packages are also available on Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.Logic SymbolsIEEE/IECConnection DiagramPin DescriptionsOrder Number Package Number Package Description74VHC273M M20B20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide74VHC273SJ M20D20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide74VHC273MTC MTC2020-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide74VHC273N N20A20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePin Names DescriptionD0–D7Data InputsMR Master ResetCP Clock Pulse InputQ0–Q7Data Outputs 274V H C 273Function TableH = HIGH Voltage Level L = LOW Voltage Level X = Immaterial= LOW-to-HIGH TransitionLogic DiagramPlease note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.Operating ModeInputs Outputs MRCP D n Q n Reset (Clear)L XX L Load ’1’H H H Load ’0’HLL74VHC273Absolute Maximum Ratings (Note 1)Recommended Operating Conditions (Note 2)Note 1: Absolute Maximum Ratings are values beyond which the device may be damaged or have its useful life impaired. The databook specifica-tions should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading vari-ables. Fairchild does not recommend operation outside databook specifica-tions.Note 2: Unused inputs must be held HIGH or LOW. They may not float.DC Electrical CharacteristicsNoise CharacteristicsNote 3: Parameter guaranteed by design.Supply Voltage (V CC )−0.5V to +7.0V DC Input Voltage (V IN )−0.5V to +7.0V DC Output Voltage (V OUT )−0.5V to V CC + 0.5VInput Diode Current (I IK )−20 mA Output Diode Current (I OK )±20 mA DC Output Current (I OUT )±25 mA DC V CC /GND Current (I CC )±75 mAStorage Temperature (T STG )−65°C to +150°CLead Temperature (T L )(Soldering, 10 seconds)260°CSupply Voltage (V CC ) 2.0Vto +5.5V Input Voltage (V IN )0V to+5.5V Output Voltage (V OUT )0V to V CCOperating Temperature (T OPR )−40°C to +85°CInput Rise and Fall Time (t r , t f )V CC = 3.3V ± 0.3V 0 ns/V ∼ 100 ns/V V CC = 5.0V ± 0.5V0 ns/V ∼ 20 ns/V Symbol ParameterV CC (V)T A = 25°CT A = −40°C to +85°C Units ConditionsMin TypMaxMin MaxV IH HIGH Level Input 2.0 1.50 1.50V Voltage3.0 − 5.50.7 V CC0.7 V CCV IL LOW Level Input 2.00.500.50VVoltage3.0 − 5.50.3 V CC0.3 V CC V OHHIGH Level Output 2.0 1.9 2.0 1.9VV IN = V IH I OH = −50 µAVoltage3.0 2.9 3.0 2.9or V IL4.5 4.4 4.5 4.43.0 2.58 2.48VI OH = −4 mA 4.53.943.80I OH = −8 mA V OLLOW Level Output 2.00.00.10.1V V IN = VIH IOL= 50 µAVoltage3.00.00.10.1or V IL4.50.00.10.13.00.360.44V I OL = 4 mA 4.50.360.44I OL = 8 mAI IN Input Leakage 0 − 5.5±0.1±1.0µA V IN = 5.5V or GND CurrentI CCQuiescent Supply 5.54.040.0µAV IN = V CC or GNDCurrentSymbol ParameterV CC(V)T A = 25°C Units Conditions Typ Limits V OLP Quiet Output Maximum Dynamic V OL 5.00.60.9V C L = 50 pF (Note 3) V OLV Quiet Output Minimum Dynamic V OL5.0−0.6−0.9V C L = 50 pF (Note 3) V IHD Minimum HIGH Level Dynamic Input Voltage 5.0 3.5V C L = 50 pF (Note 3) V ILD Maximum LOW Level Dynamic Input Voltage5.01.5VC L = 50 pF(Note 3) 474V H C 273AC Electrical CharacteristicsNote 4: Parameter guaranteed by design t OSLH = |t PLH max − t PLH min|; t OSHL = |t PHL max − t PHL min|.Note 5: C PD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load. Average operating current can be obtained from the equation: I CC (opr.) = C PD * V CC * f IN + I CC /8 (per F/F). The total C PD when n pieces of the Flip Flop operates can be calculated by the equation: C PD (total) = 22 + 9n.AC Operating RequirementsNote 6: V CC is 3.3 ± 0.3V or 5.0 ± 0.5VSymbol ParameterV CC (V)T A = 25°CT A = −40°C to +85°C Units ConditionsMin Typ MaxMin Maxf MAXMaximum Clock 3.3 ± 0.37512065MHz C L = 15 pF Frequency507545C L = 50 pF 5.0 ± 0.5120165100MHz C L = 15 pF 8011070C L = 50 pF t PLH Propagation Delay 3.3 ± 0.38.713.6 1.016.0ns C L = 15 pF t PHLTime (CK - Q)11.217.1 1.019.5C L = 50 pF 5.0 ± 0.55.89.0 1.010.5ns C L = 15 pF 7.311.0 1.012.5C L = 50 pF t PHLPropagation Delay 3.3 ± 0.38.913.6 1.016.0ns C L = 15 pF Time (MR - Q)11.417.1 1.019.5C L = 50 pF 5.0 ± 0.55.28.5 1.010.0ns C L = 15 pF6.710.5 1.012.0C L = 50 pFt OSLH Output to 3.3 ± 0.3 1.5 1.5ns (Note 4)C L = 50 pF t OSHL Output Skew 5.0 ± 0.51.01.0C L = 50 pFC IN Input Capacitance 41010pF V CC = Open C PDPower Dissipation 31pF(Note 5)CapacitanceSymbol ParameterV CC (V)(Note 6)T A = 25°C T A = −40°C to +85°CUnitsTypGuaranteed Minimum t W (L)Minimum Pulse Width (CK)3.3 5.5 6.5ns t W (H) 5.0 5.0 5.0t W (L)Minimum Pulse Width (MR) 3.3 5.0 6.0ns 5.0 5.0 5.0t S Minimum Setup Time 3.3 5.5 6.5ns 5.04.5 4.5t H Minimum Hold Time3.3 1.0 1.0ns 5.0 1.0 1.0t RECMinimum Removal Time (MR)3.3 2.5 2.5ns5.02.02.074VHC273Physical Dimensions inches (millimeters) unless otherwise noted20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 WidePackage Number M20B20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage Number M20D 674V H C 273Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.74VHC273 Octal D-Type Flip-FlopLIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into thebody, or (b) support or sustain life, and (c) whose failureto perform when properly used in accordance withinstructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or Physical Dimensions inches (millimeters) unless otherwise noted (Continued)20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePackage Number N20A。

Data sheet acquired from Harris SemiconductorSCHS249AFeatures•Buffered Inputs•Typical Propagation Delay- 6.5ns at V CC = 5V , T A = 25o C, C L = 50pF•Exceeds 2kV ESD Protection MIL-STD-883, Method 3015•SCR-Latchup-Resistant CMOS Process and Circuit Design •Speed of Bipolar FAST™/AS/S with Significantly Reduced Power Consumption •Balanced Propagation Delays•AC Types Feature 1.5V to 5.5V Operation and Balanced Noise Immunity at 30% of the Supply •±24mA Output Drive Current -Fanout to 15 FAST™ ICs-Drives 50Ω Transmission LinesPinoutCD54AC273, CD54ACT273(CDIP)CD74AC273, CD74ACT273(PDIP , SOIC)TOP VIEWDescriptionThe ’AC273and ’ACT273devices are octal D-type flip-flops with reset that utilize advanced CMOS logic rmation at the D input is transferred to the Q output on the positive-going edge of the clock pulse.All eight flip-flops are controlled by a common clock (CP)and a common reset (MR).Resetting is accomplished by a low voltage level independent of the clock.1112131415161718201910987654321MR Q0D0D1Q1Q2D3D2Q3GND V CC D7D6Q6Q7Q5D5D4Q4CPOrdering InformationPART NUMBER TEMPERATURERANGE PACKAGE CD74AC273E -40o C to 85o C 20 Ld PDIP CD54AC273F3A -55o C to 125o C 20 Ld CDIP CD74ACT273E -40o C to 85o C 20 Ld PDIP CD54ACT273F3A -55o C to 125o C 20 Ld CDIP CD74AC273M -40o C to 85o C 20 Ld SOIC CD74ACT273M-40o C to 85o C20 Ld SOICNOTES:1.When ordering,use the entire part number.Add the suffix 96to obtain the variant in the tape and reel.2.Wafer and die for this part number is available which meets allelectrical specifications.Please contact your local sales office for ordering information.August 1998 - Revised April 2000CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.CD54AC273, CD74AC273CD54ACT273, CD74ACT273Octal D Flip-Flop with ResetFunctional DiagramTRUTH TABLE INPUTSOUTPUTSRESET (MR)CLOCK CP DATA Dn Qn L X X L H ↑H H H ↑L L HLXQ0H =High level (steady state),L =Low level (steady state),X =Irrel-evant,↑=Transition from Low to High level,Q0=The level of Q before the indicated steady-state input conditions were estab-lished.Q0Q1Q2Q3Q4Q5Q6Q7RESET MRD0D1D2D3D4D5D6D7CLOCKCPDATA INPUTSDATAOUTPUTSAbsolute Maximum Ratings Thermal InformationDC Supply Voltage, V CC. . . . . . . . . . . . . . . . . . . . . . . .-0.5V to 6V DC Input Diode Current, I IKFor V I < -0.5V or V I > V CC + 0.5V. . . . . . . . . . . . . . . . . . . . . .±20mA DC Output Diode Current, I OKFor V O < -0.5V or V O > V CC + 0.5V . . . . . . . . . . . . . . . . . . . .±50mA DC Output Source or Sink Current per Output Pin, I OFor V O > -0.5V or V O < V CC + 0.5V . . . . . . . . . . . . . . . . . . . .±50mA DC V CC or Ground Current, I CC or I GND (Note 3) . . . . . . . . .±100mA Operating ConditionsTemperature Range, T ACD54AC273, CD54ACT273 . . . . . . . . . . . . . . . . .-55o C to 125o C CD74AC273, CD74ACT273 . . . . . . . . . . . . . . . . . .-40o C to 85o C Supply Voltage Range, V CC (Note 4)AC T ypes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1.5V to 5.5V ACT T ypes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V DC Input or Output Voltage, V I, V O . . . . . . . . . . . . . . . . .0V to V CC Input Rise and Fall Slew Rate, dt/dvAC T ypes, 1.5V to 3V . . . . . . . . . . . . . . . . . . . . . . . . .50ns (Max) AC T ypes, 3.6V to 5.5V. . . . . . . . . . . . . . . . . . . . . . . .20ns (Max) ACT T ypes, 4.5V to 5.5V. . . . . . . . . . . . . . . . . . . . . . .10ns (Max)Thermal Resistance,θJA(Typical, Note 5)E Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69o C/W M Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58o C/W Maximum Junction T emperature (Plastic Package) . . . . . . . . . .150o C Maximum Storage Temperature Range . . . . . . . . . .-65o C to 150o C Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . .300o CCAUTION:Stresses above those listed in“Absolute Maximum Ratings”may cause permanent damage to the device.This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.NOTES:3.For up to 4 outputs per device, add±25mA for each additional output.4.Unless otherwise specified, all voltages are referenced to ground.5.The package thermal impedance is calculated in accordance with JESD 51.DC Electrical SpecificationsPARAMETER SYMBOLTESTCONDITIONS VCC(V)25o C-40o C TO85o C-55o C TO125o CUNITS V I(V)I O(mA)MIN MAX MIN MAX MIN MAXAC TYPESHigh Level Input Voltage V IH-- 1.5 1.2- 1.2- 1.2-V3 2.1- 2.1- 2.1-V5.5 3.85- 3.85- 3.85-V Low Level Input Voltage V IL-- 1.5-0.3-0.3-0.3V3-0.9-0.9-0.9V5.5- 1.65- 1.65- 1.65V High Level Output Voltage V OH V IH or V IL-0.05 1.5 1.4- 1.4- 1.4-V-0.053 2.9- 2.9- 2.9-V-0.05 4.5 4.4- 4.4- 4.4-V-43 2.58- 2.48- 2.4-V-24 4.5 3.94- 3.8- 3.7-V-75(Note 6, 7)5.5-- 3.85---V-50(Note 6, 7)5.5---- 3.85-VLow Level Output VoltageV OLV IH or V IL0.05 1.5-0.1-0.1-0.1V 0.053-0.1-0.1-0.1V 0.05 4.5-0.1-0.1-0.1V 123-0.36-0.44-0.5V 24 4.5-0.36-0.44-0.5V 75(Note 6, 7) 5.5--- 1.65--V 50(Note 6, 7)5.5----- 1.65V Input Leakage Current I I V CC or GND - 5.5-±0.1-±1-±1µA Quiescent Supply Current MSI I CCV CC or GND5.5-8-80-160µAACT TYPESHigh Level Input Voltage V IH -- 4.5 to 5.52-2-2-V Low Level Input Voltage V IL -- 4.5 to 5.5-0.8-0.8-0.8V High Level Output VoltageV OHV IH or V IL-0.05 4.5 4.4- 4.4- 4.4-V -24 4.5 3.94- 3.8- 3.7-V -75(Note 6, 7) 5.5-- 3.85---V -50(Note 6, 7)5.5---- 3.85-V Low Level Output VoltageV OLV IH or V IL0.05 4.5-0.1-0.1-0.1V 24 4.5-0.36-0.44-0.5V 75(Note 6, 7) 5.5--- 1.65--V 50(Note 6, 7)5.5----- 1.65V Input Leakage Current I I V CC or GND - 5.5-±0.1-±1-±1µA Quiescent Supply Current MSII CC V CC or GND 0 5.5-8-80-160µA Additional Supply Current per Input Pin TTL Inputs High 1 Unit Load ∆I CCV CC -2.1- 4.5 to 5.5- 2.4- 2.8-3mANOTES:6.Test one output at a time for a 1-second maximum duration.Measurement is made by forcing current and measuring voltage to minimize power dissipation.7.Test verifies a minimum 50Ω transmission-line-drive capability at 85o C, 75Ω at 125o C.ACT Input Load TableINPUT UNIT LOADDn 0.5MR 0.57CP1NOTE:Unit load is ∆I CC limit specified in DC Electrical Specifications T able, e.g., 2.4mA max at 25o C.DC Electrical Specifications(Continued)PARAMETERSYMBOL TEST CONDITIONSV CC (V)25o C -40o C TO 85o C -55o C TO 125o C UNITS V I (V)I O (mA)MIN MAX MIN MAX MIN MAXPrerequisite For Switching FunctionPARAMETER SYMBOL V CC (V)-40o C TO 85o C-55o C TO 125o CUNITS MIN MAX MIN MAXAC TYPESData to CP Set-Up Time t SU 1.52-2-ns3.3(Note 9)2-2-ns5(Note 10)2-2-ns Hold Time t H 1.52-2-ns3.32-2-ns52-2-ns Removal Time,MR to CP t REM 1.52-2-ns3.32-2-ns52-2-ns MR Pulse Width t W 1.555-63-ns3.3 6.1-7-ns5 4.4-5-ns CP Pulse Width t W 1.555-63-ns3.3 6.1-7-ns5 4.4-5-ns CP Frequency f MAX 1.59-8-MHz3.381-71-MHz5114-100-MHz ACT TYPESData to CP Set-Up Time t SU5(Note 10)2-2-ns Hold Time t H52-2-ns Removal Time MR to CP t REM52-2-ns MR Pulse Width t W5 4.4-5-ns CP Pulse Width t W5 5.3-6-ns CP Frequency f MAX597-85-MHz Switching Specifications Input t r, t f = 3ns, C L= 50pF (Worst Case)PARAMETER SYMBOL V CC (V)-40o C TO 85o C-55o C TO 125o CUNITS MIN TYP MAX MIN TYP MAXAC TYPESPropagation Delay, CP to Qn t PLH, t PHL 1.5--154--169ns3.3(Note 9)4.9-17.2 4.7-18.9ns5(Note 10)3.5-12.3 3.4-13.5nsPropagation Delay,MR to Qnt PLH , t PHL1.5--154--169ns 3.3 4.9-17.2 4.7-18.9ns 53.5-12.3 3.4-13.5ns Input CapacitanceC I ---10--10pF Power Dissipation Capacitance C PD (Note 11)--45--45-pFACT TYPES Propagation Delay,CP to Qnt PLH , t PHL 5(Note 10)3.5-12.3 3.4-13.5ns Propagation Delay,MR to Qn t PLH , t PHL5 3.5-12.3 3.4-13.5ns Input CapacitanceC I ---10--10pF Power Dissipation Capacitance C PD (Note 11)--45--45-pFNOTES:8.Limits tested 100%.9.3.3V Min is at 3.6V, Max is at 3V.10.5V Min is at 5.5V, Max is at 4.5V.11.C PD is used to determine the dynamic power consumption per flip-flop.AC: P D = C PD V CC 2 f i =∑ (C L V CC 2 f o )ACT:P D =C PD V CC 2f i +∑(C L V CC 2f o )+V CC ∆I CC where f i =input frequency,f o =output frequency,C L =output load capacitance,V CC = supply voltage.FIGURE 1.PROPAGATION DELAY TIMES AND CLOCKPULSE WIDTH FIGURE 2.PREREQUISITE AND PROPAGATION DELAYTIMES FOR MASTER RESETSwitching Specifications Input t r , t f = 3ns, C L = 50pF (Worst Case)(Continued)PARAMETERSYMBOL V CC (V)-40o C TO 85o C-55o C TO 125o CUNITS MIN TYP MAX MIN TYP MAX 90%t f t r V SV S V SV SV St PLHt PHLt W 10%10%CP INPUT LEVEL QMR CPINPUT LEVELV SQV St REMV SV St PLHt WGNDINPUT(Q)FIGURE 3.PREREQUISITE FOR CLOCKDV S V S V SV S V S V St H (H)t SU (L)t H (L)t SU (H)CPOUTPUT LEVELDUT OUTPUTR L (NOTE)OUTPUT LOAD500ΩC L 50pFNOTE:For AC Series Only: When V CC = 1.5V , R L = 1k Ω.FIGURE 4.PROPAGATION DELAY TIMESACACT Input LevelV CC 3V Input Switching Voltage, V S 0.5 V CC 1.5V Output Switching Voltage, V S0.5 V CC0.5 V CCIMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.Customers are responsible for their applications using TI components.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 2000, Texas Instruments Incorporated。

TECHNICAL DATA376Octal D Flip-Flop with Common Clock and ResetHigh-Speed Silicon-Gate CMOSThe IN74AC273 is identical in pinout to the LS/ALS273,HC/HCT273. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LS/ALS outputs.This device consists of eight D flip-flops with common Clock and Reset inputs. Each flip-flop is loaded with a low-to-high transition of the Clock input. Reset is asynchronous and active low.• Outputs Directly Interface to CMOS, NMOS, and TTL • Operating Voltage Range: 2.0 to 6.0 V• Low Input Current: 1.0 µA; 0.1 µA @ 25°C• High Noise Immunity Characteristic of CMOS Devices • Outputs Source/Sink 24 mAIN74AC273FUNCTION TABLEX = don’t careLOGIC DIAGRAMPIN 20=V CC PIN 10 = GNDPIN ASSIGNMENTIN74AC273377MAXIMUM RATINGS *Symbol ParameterValue Unit V CC DC Supply Voltage (Referenced to GND)-0.5 to +7.0V V IN DC Input Voltage (Referenced to GND)-0.5 to V CC +0.5V V OUT DC Output Voltage (Referenced to GND)-0.5 to V CC +0.5V I IN DC Input Current, per Pin±20mA I OUT DC Output Sink/Source Current, per Pin ±50mA I CC DC Supply Current, V CC and GND Pins ±50mA P D Power Dissipation in Still Air, Plastic DIP+ SOIC Package+750500mW Tstg Storage Temperature-65 to +150°C T LLead Temperature, 1 mm from Case for 10 Seconds (Plastic DIP or SOIC Package)260°C*Maximum Ratings are those values beyond which damage to the device may occur.Functional operation should be restricted to the Recommended Operating Conditions.+Derating - Plastic DIP: - 10 mW/°C from 65° to 125°CSOIC Package: : - 7 mW/°C from 65° to 125°CRECOMMENDED OPERATING CONDITIONSSymbol ParameterMin Max Unit V CC DC Supply Voltage (Referenced to GND)2.0 6.0V V IN , V OUTDC Input Voltage, Output Voltage (Referenced to GND)0V CC V T J Junction Temperature (PDIP)140°C T A Operating Temperature, All Package Types -40+85°C I OH Output Current - High -24mA I OL Output Current - Low 24mA t r , t fInput Rise and Fall Time *(except Schmitt Inputs)V CC =3.0 V V CC =4.5 V V CC =5.5 V0001504025ns/V*V IN from 30% to 70% V CCThis device contains protection circuitry to guard against damage due to high static voltages or electricfields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation, V IN and V OUT should be constrained to the range GND ≤(V IN or V OUT )≤V CC .Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or V CC ).Unused outputs must be left open.IN74AC273378DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)V CCGuaranteed Limits Symbol Parameter Test Conditions V 25 °C -40°C to 85°C Unit V IHMinimum High-Level Input Voltage V OUT =0.1 V or V CC -0.1 V3.04.55.5 2.13.153.85 2.13.153.85VV IL Maximum Low -Level Input Voltage V OUT =0.1 V or V CC -0.1 V 3.04.55.50.91.351.650.91.351.65VV OH Minimum High-Level Output VoltageI OUT ≤ -50 µA3.04.55.5 2.94.45.4 2.94.45.4V*V IN =V IH or V IL I OH =-12 mA I OH =-24 mA I OH =-24 mA3.04.55.5 2.563.864.86 2.463.764.76V OLMaximum Low-Level Output VoltageI OUT ≤ 50 µA3.04.55.50.10.10.10.10.10.1V *V IN =V IH or V IL I OL =12 mA I OL =24 mA I OL =24 mA3.04.55.50.360.360.360.440.440.44I IN Maximum Input Leakage Current V IN =V CC or GND 5.5±0.1±1.0µA I OLD +Minimum Dynamic Output Current V OLD =1.65 V Max 5.575mA I OHD +Minimum Dynamic Output Current V OHD =3.85 V Min 5.5-75mA I CCMaximum Quiescent Supply Current (per Package)V IN =V CC or GND5.58.080µA *All outputs loaded; thresholds on input associated with output under test.+Maximum test duration 2.0 ms, one output loaded at a time.Note: I IN and I CC @ 3.0 V are guaranteed to be less than or equal to the respective limit @ 5.5 V V CCIN74AC273379AC ELECTRICAL CHARACTERISTICS (C L =50pF, Input t r =t f =3.0 ns)V CC *Guaranteed Limits SymbolParameterV25 °C -40°C to 85°C UnitMinMaxMin Maxf max Maximum Clock Frequency (Figure 1) 3.35.0901*******MHz t PLH Propagation Delay, Clock to Q (Figure 1) 3.35.0 4.03.012.59.0 3.02.514.010.0ns t PHL Propagation Delay, Clock to Q (Figure 1) 3.35.0 4.03.013.010.0 3.52.514.511.0ns t PHL Propagation Delay, Reset to Q (Figure 2) 3.35.0 4.03.013.010.0 3.52.514.010.5ns C INMaximum Input Capacitance5.04.54.5pF Typical @25°C,V CC =5.0 VC PDPower Dissipation Capacitance 50pF*Voltage Range 3.3 V is 3.3 V ±0.3 V Voltage Range 5.0 V is 5.0 V ±0.5 VTIMING REQUIREMENTS (C L =50pF, Input t r =t f =3.0 ns)V CC *Guaranteed Limits Symbol ParameterV 25 °C -40°C to 85°C Unit t su Minimum Setup Time, Data to Clock (Figure 3)3.35.0 5.54.0 6.04.5ns t h Minimum Hold Time, Data to Clock (Figure 3)3.35.001.001.0ns t w Minimum Pulse Width, Clock (Figure 1) 3.35.0 5.54.0 6.04.5ns t w Minimum Pulse Width, Reset (Figure 2) 3.35.0 5.54.06.04.5ns t recMinimum Recovery Time, Reset to Clock (Figure 2)3.35.03.52.04.53.0ns*Voltage Range 3.3 V is 3.3 V ±0.3 V Voltage Range 5.0 V is 5.0 V ±0.5 VIN74AC273380Figure 1. Switching Waveforms Figure 2. Switching WaveformsFigure 3. Switching WaveformsEXPANDED LOGIC DIAGRAM。

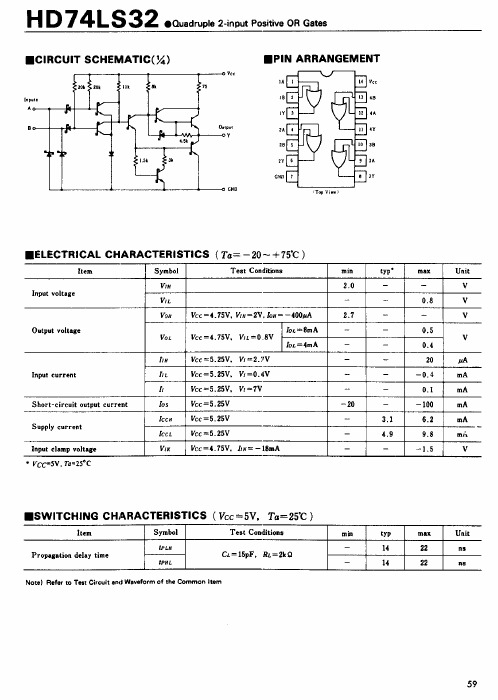

HD74LS273Octal D-type Positive-edge-triggered Flip-Flops (with Clear)REJ03D0473–0300Rev.3.00 Jul.15.2005The HD74LS273, positive-edge-triggered flip-flops utilize LS TTL circuitry to implement D-type flip-flop logic with a direct clear input.Information at the D inputs meeting the setup time requirements is transferred to the Q outputs on the positive-going edge of the clock pulse.When the clock input is at either the high or low level, the D input signal has no effect at the output.Features• Ordering InformationPart NamePackage TypePackage Code (Previous Code) PackageAbbreviationTaping Abbreviation (Quantity)HD74LS273P DILP-20 pin PRDP0020AC-B (DP-20NEV) P — HD74LS273FPEL SOP-20 pin (JEITA) PRSP0020DD-B (FP-20DAV)FPEL (2,000 pcs/reel) HD74LS273RPEL SOP-20 pin (JEDEC)PRSP0020DC-A(FP-20DBV)RPEL (1,000 pcs/reel)Note: Please consult the sales office for the above package availability.Pin ArrangementFunction TableInputs Output Clear Clock D QL X X LH ↑ H HH ↑ L LH L X Q0Notes: H; high level, L; low level, X; irrelevant↑; transition from low to high levelQ0; level of Q before the indicated steady-state input conditions were established.Block DiagramAbsolute Maximum RatingsUnitRatingsItem SymbolSupply voltage V CC 7 VInput voltage V IN 7 VPower dissipation P T 400 mWStorage temperature Tstg –65 to +150 °CNote: Voltage value, unless otherwise noted, are with respect to network ground terminal.Recommended Operating ConditionsMaxTypUnitMinItem SymbolSupply voltage V CC 4.75 5.00 5.25 VI OH — — –400 µAOutput currentI OL — — 8 mA°C75Operating temperature Topr25–20Clock frequency ƒclock 0 — 30 MHzClock pulse width t w (clock) 20 — — nsClear pulse width t w (clear) 20 — — nsData setup time t su (data) 20↑ — — nsClear (inactive-state) setup time t su (clear) 25↑ — — nsData hold time t h (data)5↑ — — nsElectrical Characteristics(Ta = –20 to +75 °C)Item Symbol min. typ.* max. UnitConditionV IH 2.0 — — VInput voltageV IL — — 0.8 VV OH 2.7 — — VV CC = 4.75 V, V IH = 2 V, V IL = 0.8 V,I OH = –400 µA— — 0.5 I OL = 8 mA Output voltageV OL — — 0.4 VI OL = 4 mA V CC = 4.75 V, V IH = 2 V,V IL = 0.8 VI IH — 20 µA V CC = 5.25 V, V I = 2.7 V I IL — –0.4 mA V CC = 5.25 V, V I = 0.4 VInput currentI I —0.1 mA V CC = 5.25 V, V I = 7 V Short-circuit output currentI OS –20 — –100 mA V CC = 5.25 V Supply currentI CC ** — 17 27 mA V CC = 5.25 V Input clamp voltage VIK — — –1.5 V V CC = 4.75 V, I IN = –18 mANotes: * V CC = 5 V, Ta = 25°C ** With all outputs open and 4.5 V applied to all data and clear inputs, I CC is measured after a momentaryground, then 4.5 V is applied to clock.Switching Characteristics(V CC = 5 V, Ta = 25°C)Item Symbol Inputs min. typ. max. Unit ConditionMaximum clock frequency ƒmax Clock 30 40 — MHzt PHL Clear — 18 27t PLH — 17 27Propagation delay time t PHL Clock— 18 27 ns C L = 15 pF, R L = 2 k ΩTesting MethodTest CircuitWaveforms 1Waveforms 2Package Dimensions RENESAS SALES OFFICESRefer to "/en/network" for the latest and detailed information.Renesas Technology America, Inc.450 Holger Way, San Jose, CA 95134-1368, U.S.ATel: <1> (408) 382-7500, Fax: <1> (408) 382-7501Renesas Technology Europe LimitedDukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900Renesas Technology Hong Kong Ltd.7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong KongTel: <852> 2265-6688, Fax: <852> 2730-6071Renesas Technology Taiwan Co., Ltd.10th Floor, No.99, Fushing North Road, Taipei, TaiwanTel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999Renesas Technology (Shanghai) Co., Ltd.Unit2607 Ruijing Building, No.205 Maoming Road (S), Shanghai 200020, ChinaTel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952Renesas Technology Singapore Pte. Ltd.1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632Tel: <65> 6213-0200, Fax: <65> 6278-8001Renesas Technology Korea Co., Ltd.Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, KoreaTel: <82> 2-796-3115, Fax: <82> 2-796-2145Renesas Technology Malaysia Sdn. Bhd.Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, MalaysiaTel: <603> 7955-9390, Fax: <603> 7955-9510。

74AC273, 74ACT273 — Octal D-Type Flip-FlopOctal D-Type Flip-FlopFeatures■ Ideal buffer for microprocessor or memory ■ Eight edge-triggered D-type flip-flops ■ Buffered common clock■ Buffered, asynchronous master reset ■ See 377 for clock enable version ■ See 373 for transparent latch version ■ See 374 for 3-STATE version ■ Outputs source/sink 24mA■ 74ACT273 has TTL-compatible inputsGeneral DescriptionThe AC273 and ACT273 have eight edge-triggered D-type flip-flops with individual D-type inputs and Q outputs. The common buffered Clock (CP) and Master Reset (MR) input load and reset (clear) all flip-flops simultaneously.The register is fully edge-triggered. The state of each D-type input, one setup time before the LOW-to-HIGH clock transition, is transferred to the corresponding flip-flop's Q output.All outputs will be forced LOW independently of Clock or Data inputs by a LOW voltage level on the MR input. The device is useful for applications where the true output only is required and the Clock and Master Reset are common to all storage elements.Ordering InformationDevice also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering number.All packages are lead free per JEDEC: J-STD-020B standard.Order NumberPackage NumberPackage Description74AC273SC M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide 74AC273SJ M20D 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide74AC273MTC MTC2020-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide74AC273PC N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide 74ACT273SC M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide 74ACT273SJ M20D 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide74ACT273MTCMTC2020-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide元器件交易网74AC273, 74ACT273 — Octal D-Type Flip-FlopPin DescriptionIEEE/IECMode Select-Function TableH = HIGH Voltage Level L = LOW Voltage Level X = Immaterial= LOW-to-HIGH TransitionLogic DiagramPin NamesDescriptionD 0 –D 7 Data Inputs MR Master Reset CP Clock Pulse Input Q 0 –Q 7Data OutputsOperating ModeInputsOutputs MRCPD nQ nReset (Clear)L XX L Load ‘1'H H H Load ‘0'HLL元器件交易网74AC273, 74ACT273 — Octal D-Type Flip-FlopRecommended Operating ConditionsThe Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.V CC Supply Voltage –0.5V to +7.0VI IKDC Input Diode Current V I = –0.5V –20mA V I = V CC + 0.5+20mAV I DC Input Voltage –0.5V to V CC + 0.5VI OKDC Output Diode Current V O = –0.5V –20mA V O = V CC + 0.5V+20mAV O DC Output Voltage–0.5V to V CC + 0.5VI O DC Output Source or Sink Current ±50mA I CC or I GND DC V CC or Ground Current per Output Pin±50mAT STG Storage Temperature –65°C to +150°CT JJunction Temperature140°CSymbol ParameterRatingV CCSupply Voltage AC 2.0V to 6.0V ACT4.5V to5.5V V I Input Voltage 0V to V CC V O Output Voltage 0V to V CCT A Operating Temperature–40°C to +85°C∆ V / ∆ t Minimum Input Edge Rate, AC Devices:V IN from 30% to 70% of V CC , V CC @ 3.3V , 4.5V , 5.5V 125mV/ns ∆ V / ∆ tMinimum Input Edge Rate, ACT Devices: V IN from 0.8V to 2.0V , V CC@ 4.5V , 5.5V125mV/ns元器件交易网74AC273, 74ACT273 — Octal D-Type Flip-FlopNotes:1.All outputs loaded; thresholds on input associated with output under test.2.I IN and I CC @3.0V are guaranteed to be less than or equal to the respective limit @ 5.5V V CC .3.Maximum test duration 2.0ms, one output loaded at a time.5.5 2.75 3.85 3.85V ILMaximum LOW Level Input Voltage3.0V OUT = 0.1V or V CC – 0.1V1.50.90.9V4.5 2.25 1.35 1.355.5 2.75 1.65 1.65V OHMinimum HIGH Level Output Voltage3.0I OUT = –50µA2.99 2.9 2.9V 4.5 4.49 4.4 4.45.5 5.495.4 5.43.0V IN = V IL or V IH ,I OH = –12mA 2.56 2.464.5V IN = V IL or V IH ,I OH = –24mA 3.86 3.765.5V IN = V IL or V IH ,I OH = –24mA (1) 4.864.76V OLMaximum LOW Level Output Voltage3.0I OUT = 50µA0.0020.10.1V 4.50.0010.10.15.50.0010.10.13.0V IN = V IL or V IH ,I OL = 12mA 0.360.444.5V IN = V IL or V IH,I OL = 24mA 0.360.445.5V IN = V IL or V IH ,I OL = 24mA (1)0.360.44I IN (2)Maximum Input Leakage Current 5.5V I = V CC , GND ±0.1±1.0µA I OLD Minimum Dynamic Output Current (3) 5.5V OLD = 1.65V Max.75mA I OHD 5.5V OHD = 3.85V Min.–75mA I CC (2)Maximum Quiescent Supply Current5.5V IN = V CC or GND4.040.0µA 元器件交易网Notes:4.All outputs loaded; thresholds on input associated with output under test.5.Maximum test duration 2.0ms, one output loaded at a time.I OL = 24mA 5.5V IN = V IL or V IH ,I OL = 24mA (4)0.360.44I IN Maximum Input Leakage Current 5.5V I = V CC , GND ±0.1±1.0µA I CCT Maximum I CC /Input 5.5V I = V CC – 2.1V 0.61.5mA I OLD Minimum Dynamic Output Current (5) 5.5V OLD = 1.65V Max.75mA I OHD 5.5V OHD = 3.85V Min.–75mA I CCMaximum Quiescent Supply Current5.5V IN = V CC or GND4.040.0µANote:7.Voltage range 3.3 is 3.3V ± 0.3V. Voltage range 5.0 is 5.0V ± 0.5V.SymbolParameterV CC (V)(7)T A = +25°C,C L = 50pFT A = –40°C to +85°C,C L = 50pFUnitsTyp.Guaranteed Minimumt S Setup Time, HIGH or LOW, Data to CP3.3 3.5 5.5 6.0ns 5.0 2.54.0 4.5t H Hold Time, HIGH or LOW, Data to CP3.3–2.000ns 5.0–1.0 1.0 1.0t W Clock Pulse Width, HIGH or LOW 3.3 3.5 5.5 6.0ns 5.0 2.54.0 4.5t W MR Pulse Width, HIGH or LOW 3.3 2.05.56.0ns 5.0 1.5 4.0 4.5t recRecovery Time, MR to CP3.3 1.5 3.54.5ns5.01.02.03.0Note:9.Voltage range 5.0 is 5.0V ± 0.5V.CapacitanceSymbolParameterV CC (V)UnitsTyp.Guaranteed Minimumt S Setup Time, HIGH or LOW, D n to CP5.0 1.0 3.5 3.5ns t H Hold Time, HIGH or LOW, D n to CP5.0–0.5 1.5 1.5ns t W Clock Pulse Width, HIGH or LOW 5.0 2.0 4.0 4.0ns t W MR Pulse Width, HIGH or LOW 5.0 1.5 4.0 4.0ns t WRecovery Time, MR to CP5.00.53.03.0nsSymbolParameterConditionsTyp.UnitsC IN Input CapacitanceV CC = OPEN 4.5pF C PDPower Dissipation Capacitance for AC V CC = 5.0V50.0pFPower Dissipation Capacitance for ACT40.0Figure 1. 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" WidePackage drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:/packaging/0.10CCSEE DETAIL ANOTES:UNLESS OTHERWISE SPECIFIEDA)THIS PACKAGE CONFORMS TO JEDEC MS-013,VARIATION AC,ISSUE EB)ALL DIMENSIONS ARE IN MILLIMETERS.C)DIMENSIONS DO NOT INCLUDE MOLDFLASH OR BURRS.E)LANDPATTERN STANDARD:SOIC127P1030X265-20L X 45°8°0°SEATING PLANEGAGE PLANEDETAIL ASCALE:2:1SEATING PLANEF)DRAWING FILENAME:MKT-M20BREV32.65MAX0.300.100.330.200.750.25(R0.10)(R0.10) 1.270.40(1.40)0.25D)CONFORMS TO ASME Y14.5M-1994Figure 2. 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions,Figure 3. 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePackage drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions,74AC273, 74ACT273 — Octal D-Type Flip-FlopFigure 4. 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" WidePackage drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:.001[.025]C7°TYP7°TYP10.92MAX7.116.091.781.142.547.627.873.433.175.33MAX3.553.170.38MIN0.360.560.200.35PIN #1NOTES:(0.97)subsidiaries,and is not intended to be an exhaustive list of all such trademarks.ACEx ®Build it Now ™CorePLUS ™CROSSVOLT ™CTL™Current Transfer Logic™EcoSPARK ®EZSWITCH™*™®Fairchild®Fairchild Semiconductor ®FACT Quiet Series™FACT ®FAST ®FastvCore ™FlashWriter ®*FPS ™FRFET ®Global Power Resource SM Green FPS ™Green FPS ™e-Series ™GTO ™i-Lo ™IntelliMAX ™ISOPLANAR ™MegaBuck™MICROCOUPLER ™MicroFET ™MicroPak ™MillerDrive™Motion-SPM™OPTOLOGIC ®OPTOPLANAR ®®PDP-SPM™Power220®Power247®POWEREDGE ®Power-SPM ™PowerTrench ®Programmable Active Droop ™QFET ®QS ™QT Optoelectronics ™Quiet Series ™RapidConfigure ™SMART START ™SPM ®STEALTH™SuperFET ™SuperSOT ™-3SuperSOT ™-6SuperSOT ™-8SyncFET™®The Power Franchise ®TinyBoost ™TinyBuck ™TinyLogic ®TINYOPTO ™TinyPower ™TinyPWM ™TinyWire ™µSerDes ™UHC ®Ultra FRFET ™UniFET ™VCX ™*EZSWITCH™and FlashWriter ®are trademarks of System General Corporation,used under license by Fairchild Semiconductor.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY,FUNCTION,OR DESIGN.FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS,NOR THE RIGHTS OF OTHERS.THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWIDE TERMS AND CONDITIONS,SPECIFICALLY THE WARRANTY THEREIN,WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body or (b)support or sustain life,and (c)whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury of the user.2.A critical component in any component of a life support,device,or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of Terms Datasheet Identification Product Status DefinitionAdvance InformationForm First Productionative or In DesignThis datasheet contains the design specifications for productdevelopment.Specifications may change in any manner without notice.PreliminaryThis datasheet contains preliminary data;supplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design.74AC273, 74ACT273 — Octal D-Type Flip-Flop。