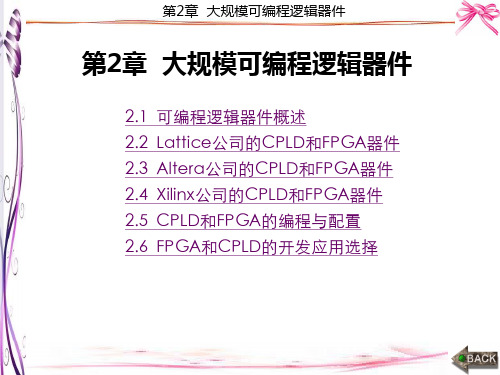

组合逻辑在SSI中和在PLD中的逻辑图

2.4

PLD的基本结构

一、简单PLD的基本结构 简单 的基本结构

1、可编程只读存储器(PROM) 、可编程只读存储器( )

可编程只读存储器(Programmable ReadOnly Memory, 简称PROM)是最早的PLD器件,它出现在20世纪70年代初。它包 含一个固定的“与”阵列和一个可编程的“或”阵列 固定的“ 阵列和一个可编程的“ 阵列,其基本结构 固定的 图如图所示。 由图可见,它的“与”阵列是一个“全译码阵列”,即对某一组 特定的输入i(i=0,1,2)只能产生一个惟一的乘积项。因为是全译码, 当输入变量为n个时,阵列的规模为2n,所以PROM的规模一般很大。 PROM存在的不足:PROM虽然也可以用来产生组合逻辑函 数,但因为往往只用到了与逻辑阵列输出的最小项的一部分,而 且有时这些最小项还可以合并,因此器件内部资源的利用率不高, 所以在绝大多数情况下,都把PROM作为存储器使用了。

8

~

15

16

~

23

24

~

31

32

~

39

40

~

47

48

~

55 56

~

63

0~3

4~7

12~15 20~23 28~31 8~11 16~19 24~27

OE

11

GAL16V8的电路结构图 的电路结构图

GAL与PAL相比较 与 相比较: 相比较 1、有可编程的OLMC输出宏单元,因此器件的通用性和应用 灵活性较高,一般可用GAL代替PAL。 2、GAL采用高性能的E2COMS工艺。保证了GAL的高速度和 低功耗,存取速度为12~40ns,功耗仅为双极型PAL器件的 1/2或1/4,编程数据可保存20年以上。因此目前在一些小 GAL 规模的数字系统的设计过程当中,仍可使用GAL。

![[工学]第2章 可编程逻辑器件可编程逻辑器件](https://img.taocdn.com/s1/m/8a1e0bf426fff705cc170a64.png)