机器指令执行

- 格式:docx

- 大小:268.40 KB

- 文档页数:7

![第四章 指令系统[一]](https://uimg.taocdn.com/0cc630d349649b6648d74742.webp)

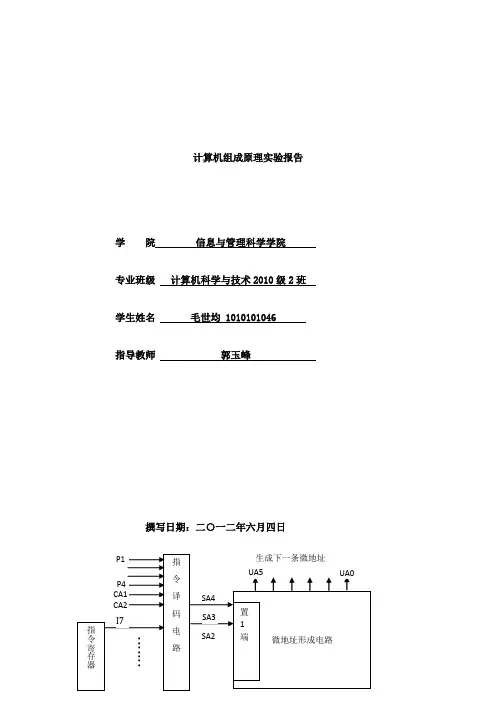

计算机组成原理实验报告学院信息与管理科学学院专业班级计算机科学与技术2010级2班学生姓名毛世均 1010101046 指导教师郭玉峰撰写日期:二○一二年六月四日SA4=1 SA3=I7·P1 SA2=I6·P1 SA1=I5·P1+I3·P2+CA2·P4 SA0=I4·P1+I2·P2+CA1·P41.根据上边的逻辑表达式,分析58页图6-2的P1测试和P4测试两条指令的微地址转移方向。

P1测试:进行P1测试时,P1为0,其他的都为1,因此SA4=1, SA3=I7,SA2=I6,SA1=I5,SA0=I4微地址011001,下址字段为001000下址字段001000译码后,高两位不变,仍然为00,低四位受到机器指令的高四位I7-I4的影响。

机器指令的高四位为0000时,下一条微指令地址为001000,转到IN 操作。

机器指令高四位0010时,下一条微指令地址为001010,转到MOV 操作。

机器指令高四位为0001时,下一条微指令地址为001001,转到ADD 操作。

机器指令高四位为0011时,下一条微指令地址为001011,转到OUT 操作。

机器指令高四位为0100时,下一条微指令地址001100,转到JMP 操作P4测试:进行P4测试时,P4为0,其他的都为1.因此SA4=SA3=SA2=1,SA1=CA2,SA0=CA1微地址000000,下址字段为010000. 010000被译码之后,高四位不变,0100低两位由CA2和CA1控制。

CA2和CA1的值是由单片机的键盘填入控制的。

当实验选择CtL2=1时,CA2和CA1被填入0和1,这时低两位被译码电路翻译成01,所以下一条微地址就是010001,然后进入写机器指令的状态。

当实验选择CtL2=2时,CA2和CA1被填入1和0,这时低两位被译码电路翻译成10,所以下一条微地址就是010010,然后进入读机器指令的状态。

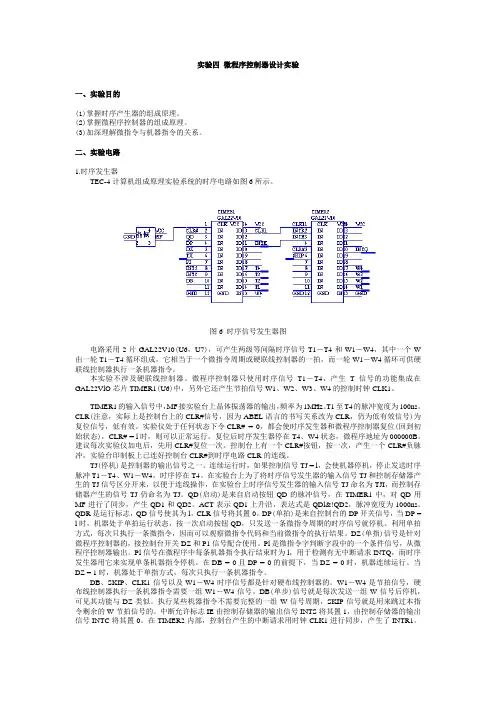

实验四微程序控制器设计实验一、实验目的(1)掌握时序产生器的组成原理。

(2)掌握微程序控制器的组成原理。

(3)加深理解微指令与机器指令的关系。

二、实验电路1.时序发生器TEC-4计算机组成原理实验系统的时序电路如图6所示。

图6 时序信号发生器图电路采用2片GAL22V10(U6,U7),可产生两级等间隔时序信号T1-T4和W1-W4,其中一个W 由一轮T1-T4循环组成,它相当于一个微指令周期或硬联线控制器的一拍,而一轮W1-W4循环可供硬联线控制器执行一条机器指令。

本实验不涉及硬联线控制器。

微程序控制器只使用时序信号T1-T4,产生T信号的功能集成在GAL22VlO芯片TIMER1(U6)中,另外它还产生节拍信号W1、W2、W3、W4的控制时钟CLK1。

TIMER1的输入信号中,MF接实验台上晶体振荡器的输出,频率为1MHz。

T1至T4的脉冲宽度为100ns。

CLR(注意,实际上是控制台上的CLR#信号,因为ABEL语言的书写关系改为CLR,仍为低有效信号)为复位信号,低有效。

实验仪处于任何状态下令CLR# = 0,都会使时序发生器和微程序控制器复位(回到初始状态),CLR# = l时,则可以正常运行。

复位后时序发生器停在T4、W4状态,微程序地址为000000B。

建议每次实验仪加电后,先用CLR#复位一次。

控制台上有一个CLR#按钮,按一次,产生一个CLR#负脉冲,实验台印制板上已连好控制台CLR#到时序电路CLR的连线。

TJ(停机)是控制器的输出信号之一。

连续运行时,如果控制信号TJ = l,会使机器停机,停止发送时序脉冲T1-T4、W1-W4,时序停在T4。

在实验台上为了将时序信号发生器的输入信号TJ和控制存储器产生的TJ信号区分开来,以便于连线操作,在实验台上时序信号发生器的输入信号TJ命名为TJI,而控制存储器产生的信号TJ仍命名为TJ。

QD(启动)是来自启动按钮QD的脉冲信号,在TIMER1中,对QD用MF进行了同步,产生QD1和QD2。

51单片机指令时间计算

一、数据传输时间计算

1、假设单片机的时钟频率为6MHz,指令长度为2个字节。

①机器指令执行时间=2Byte/6M=333ns

2、假设单片机的时钟频率为12MHz,指令长度为3个字节。

②机器指令执行时间=3Byte/12M=250ns

3、假设单片机的时钟频率为16MHz,指令长度为4个字节。

③机器指令执行时间=4Byte/16M=250ns

二、存取时间的计算

1、假设单片机的时钟频率为6MHz,地址总线为12位,存储器访问时间为90ns。

①存取时间=90ns+(2*12/6M)=126ns

2、假设单片机的时钟频率为12MHz,地址总线为16位,存储器访问时间为100ns。

②存取时间=100ns+(2*16/12M)=150ns

3、假设单片机的时钟频率为16MHz,地址总线为20位,存储器访问时间为140ns。

③存取时间=140ns+(2*20/16M)=180ns

三、总结

1、单片机的指令执行时间取决于其时钟频率和指令长度,当时钟频率和指令长度不变时,指令执行时间可以直接计算出来。

2、单片机的存取时间取决于其时钟频率、地址总线长度、存储器访问时间,当时钟频率和存储器访问时间不变时,存取时间可以直接计算出来。

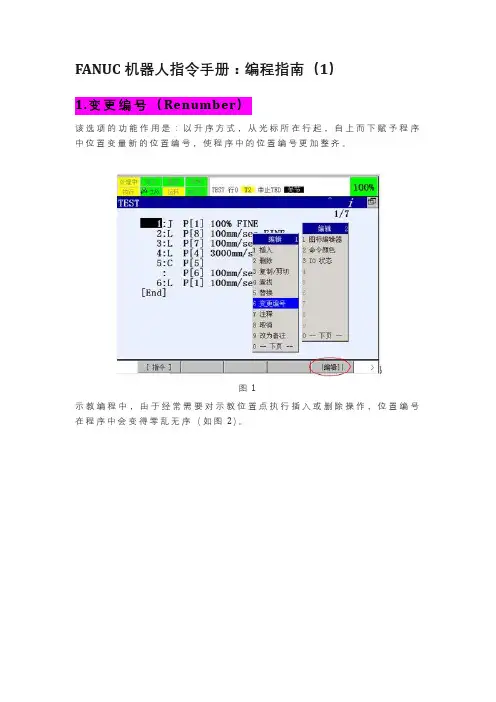

FANUC机器人指令手册:编程指南(1)1.变更编号(Renumber)该选项的功能作用是:以升序方式,从光标所在行起,自上而下赋予程序中位置变量新的位置编号,使程序中的位置编号更加整齐。

图1示教编程中,由于经常需要对示教位置点执行插入或删除操作,位置编号在程序中会变得零乱无序(如图2)。

图2通过变更编号功能,可使位置编号在程序中依序排列(如图3)。

图3注意:1、变更编号功能仅对编号顺序进行调整,不改变原程序轨迹。

2、变更编号功能只对位置变量P[i]有效,对位置寄存器PR[i]无效。

具体操作步骤:将光标移至程序首行后①选择F5编辑命令;②选择“变更编号”选项;③选择F4“是”(如图4、图5所示)。

图4备注:由于行1与行6中位置变量相同,都为P[1]。

所以,变更编号后两者编号保持一致。

图52.取消(Undo)该选项的功能作用是:可以撤销指令的更改、行插入、行删除等程序编辑操作。

注意:该功能只能撤销上一步操作,不能撤销多次操作。

下文以行删除为例对该功能进行说明。

原程序如图6所示:图6在原程序中删除1-3行后,程序如图7所示:图7通过使用取消(Undo)功能,能够撤销删除操作,恢复已删除行。

具体操作步骤:①选择F5编辑命令;②选择“取消”;③选择F4“是”(如图8、图9所示)。

图8图9取消后,程序如图10所示。

图103.改为备注(Remark)该选项的功能作用是:通过将程序中的单行或多行指令改为备注,可以在程序运行中不执行该指令。

原程序如图11,图11该程序对应机器人轨迹如图12,图12将原程序2-4行改为备注后,在行的开头会显示“//”。

改为备注的指令在程序运行中相当于被屏蔽,不会被执行。

将2-4行改为备注后,程序如图13,图13改为备注后的程序执行效果如图14,行2至行4指令内容保留,但不被执行。

图14具体操作步骤:①将光标移至需要改为备注的行号位置;②选择F5编辑命令;③选择“改为备注”选项(如图15);④根据提示,下移光标选中目标对象;⑤选择F4“改为备注”(如图16)。

第3章指令系统机器指令:能指示计算机完成基本操作的二进制代码指令系统:CPU可执行的机器指令的集合。

为了方便编程,人们又把完成特定操作的机器码用特定的符号表示,这就产生了符号表示的机器指令-------指令助记符。

第3章8086指令系统机器指令由二进制代码组成,一条指令包括操作码和操作数(或地址)两部分,操作码指明该指令进行何种操作,操作数用来说明操作对象。

个别指只有操作码没有操作数。

由于不同的指令所表达的信息不尽相同,因此指令的长度即机器码字节数也有长有短。

8086指令系统的指令是可变长指令(1~6个字节)3.18086CPU寻址方式重点是存储器寻址存放在存储器中的数据称为存储器操作数。

指令中需要确定存储单元的段地址、偏移地址(亦称有效地址EA),以及存储器操作数的类型。

段地址存放在段寄存器中,确定段地址实际上就是确定段寄存器,采用的方法是默认或添加段超越前缀。

生成存储器有效地址有多种方法,这些方法形成了对存储器操作数的多种寻址形式。

确定数据类型的方法是源操作数和目的操作数类型一致原则或附加类型说明。

立即寻址方式中操作数也在存储器中,但立即寻址中的立即数包含在指令中,随程序存放在代码段,CPU在取指令时就获得操作数。

这里所说的存储器操作数是存放在数据段、附加段或堆栈段中,取指令时也不会被立即取到。

段超越前缀变量的定义在第四章详细介绍直接寻址:MOV AX,[2000H];寄存器间接寻址:MOV ES:[DI],AH基址寻址:MOV BYTE PTR[BX+1200H],10变址寻址:MOV DL,[SI+2AH]基址加变址寻址:MOV CL,[BX+SI+5]MOV AX,[BP+DI]MOV CL,[BX+SI+5]的等价形式:MOV CL,5[BX][SI]、MOV CL,5[BX+SI]、MOV CL,[BX][SI+5]MOV CL,[BX+SI-5]等价于MOV CL,[BX+SI+65531] MOV CL,[BX-SI]MOV CL,[SI+DI]错误!MOV[BX+DI],1000H正确吗?3.2.1数据传送类指令传送指令把数据从一个位置传送到另一个位置使用MOV指令应注意1.立即数只能作为源操作数2.无存储器之间直接传送与交换的指令3.没有用立即数对段寄存器直接赋值的指令4.段寄存器之间无传送指令5.两个操作数的类型要一致6.要能确定是字节还是字操作mov ah,al mov bvar,ch mov ax,bx mov ds,ax mov al,[bx]下列MOV指令正确吗?MOV AL,050AHMOV SI,DLMOV[BX+SI],255MOV DS,100HMOV[BX],[SI]MOV[BX+SI],bvarbvar是一个已定义过的字节变量 MOV CS,[SI]将数据段中偏移地址为2000H、2001H、2002H的3个字节的存储单元置数FFH。

![[精品]指令的执行过程](https://uimg.taocdn.com/217e2354998fcc22bdd10d1f.webp)

ABB机器人程序指令汇总

一、IRProgram

1. IRProgram:使用此指令编程ABB机器人。

2. Instruction:此指令可以向机器人发送指令,包括按单次命令执行、循环执行、运动等。

3. ProgramLine:此指令设置机器人单次操作步骤的顺序,机器人按

此顺序执行指令。

4. Position:此指令确定机器人的实际位置,用来计算机器人的路

径或者运动距离。

5. Interpln:此指令用来控制机器人运动的过渡,比如采用加速度、减速度等。

6. Zonedheader:此指令定义机器人任务中的一些步骤,比如,给定

回归点、给定回归方向等。

7. Maskword:此指令用于设置机器人的安全模式,以防止机器人偏

离设定的轨迹和安全路径。

8. Stop:此指令用于控制机器人的停止。

9. Echo:此指令用于在编程过程中显示一段文字,方便开发人员从

错误中记录错误信息。

二、IRStep

2. Line:此指令可以定义任务中各个行动的顺序,机器人按此顺序

执行指令。

3. Move:此指令可以让机器人运动到指定位置。

4. Delay:此指令可以让机器人暂停其中一段时间,等待其中一种情况出现。

5. Add:此指令可用于给机器人添加各种参数,以完成不同的任务。

6. Subtract:此指令用于从机器人中减去参数,以完成任务。

计算机中指令的执行过程

1. 取指阶段:CPU从程序存储器中取出指令,并保存在指令寄存器中。

2. 译码阶段:CPU将指令寄存器中的指令翻译为机器语言,确定指令类型和操作数的位置。

3. 获取操作数阶段:CPU根据操作数的位置,从寄存器、内存中获取操作数,并将其保存在寄存器中。

4. 执行指令阶段:CPU根据指令类型和操作数,执行相应的操作,如加、减、乘、除、移位、逻辑运算等。

5. 存储结果阶段:CPU将执行结果保存在寄存器、内存或者外设中。

以上是基本的指令执行过程,不同的CPU可能在执行过程中会多出一些步骤或者优化措施,但是基本流程都是相同的。

疫情小学2年级学习计划随着疫情的逐渐得到控制,学校陆续开始了开学准备工作。

作为小学2年级的学生,我们也将迎来新的学期。

在这段特殊的时期里,学校和家长对我们的学习和生活都提出了更高的要求。

因此,制定一个科学合理的学习计划显得尤为重要。

首先,我们需要做好开学前的复习准备。

在疫情期间,由于无法正常上学,我们的学习进度可能会比往常慢一些,因此在开学前需要对上学期的知识进行回顾和复习,例如数学、语文和英语等各科目的基础知识。

可以通过做题练习、复习课本和听故事等方式来巩固知识点。

其次,我们还需要调整好学习状态。

长时间的居家学习可能会让我们的学习状态有些松懈,因此在开学前,我们可以适当地增加一些户外活动,保持良好的精神状态。

同时,也要做好回到学校后的适应工作,接受老师的教导,积极参与课堂,恢复学习生活的规律。

对于家长来说,他们也需要和老师一起制定学习计划,明确孩子在学校和家庭的学习任务。

在孩子返校后,家长可以多问问孩子在学校的情况,鼓励孩子积极参与课堂活动,关注孩子的学习进度和成绩变化,及时帮助孩子解决学习中遇到的问题。

在学习方法上,我们也需要不断改进。

在学习过程中,我们可以尝试多种学习方法,比如集中精力学习,注重细节,课后巩固和自测等等。

对于不同的科目和知识点也可以采用不同的学习方法,从而提高学习效率,更好地掌握知识。

此外,学习之余我们也要多关注身心健康。

我们可以适当锻炼身体,比如晨练、午间操等,注意合理饮食,保证充足的睡眠时间,这样才能更好地投入学习,更好地适应学校的生活。

总而言之,疫情防控的形势逐渐好转。

我们要充分利用好学校提供的资源,做好学习规划,增强学习信心,养成良好的学习习惯,不断进步。

让我们在新的学期以更好的面貌和更优异的成绩迎接挑战吧!。

川崎机器人wait指令的用法川崎机器人是一种广泛应用于工业领域的先进自动化设备。

在程序中使用wait指令是非常常见的,它允许机器人在执行任务时暂停一段时间,等待某些条件的达成。

wait指令的语法相对简单,它可以通过在程序中插入以下指令来使用:wait(time, condition)其中,time是等待的时间,以毫秒为单位;condition是等待的条件,可以是机器人关节位置的达到、IO信号的变化等。

使用wait指令可以帮助机器人实现一系列功能。

以下是几个常见的用法:1. 实现时间延迟:wait指令的最简单用法是实现时间延迟。

通过指定等待的时间,机器人可以在执行某个任务之前等待一段时间,以确保其他操作的完成。

例如,wait(2000)会使机器人停止执行2秒钟。

2. 等待特定位置达到:在某些情况下,机器人需要等待关节或末端执行器到达特定位置,才能继续执行后续任务。

通过将目标位置与当前位置进行比较,可以使用wait指令来实现等待功能。

例如,wait(0, pos(1) >= 45)将使机器人在第一个关节旋转至少45度之前一直等待。

3. 检测IO变化:机器人通常与其他设备和传感器相连,可以通过IO信号的变化来触发特定操作。

wait指令可以等待IO信号的变化,以确保操作的正确执行。

例如,wait(0, io[2])将使机器人在IO端口2的信号发生变化时继续执行后续任务。

川崎机器人wait指令是一种强大的工具,可以用于实现时间延迟、等待特定位置达到和检测IO变化等功能。

通过灵活运用wait指令,可以提高机器人的自动化程度和工作效率。

计算机一级知识点:运算器、控制器计算机一级知识点:运算器、控制器一级主要考核微型计算机基础知识和使用办公软件及因特网(Internet)的基本技能。

一级主要考核微型计算机基础知识和使用办公软件及因特网(Internet)的基本技能。

以下是为大家分享的计算机一级知识点:运算器、控制器,供大家参考借鉴,欢迎浏览!运算器、控制器2.1计算机的硬件系统冯.若依曼型计算机的硬件是计算机的基础,基本结构符合冯.若依曼的体系结构,五个功能部件:输入设备、运算器、存储器、控制器、输出设备。

其中运算器和控制器,合称中央处理器,简称CPU。

2,1,1运算器-ALU(Arithmetic Unit)功能:对二进制数码进行算术运算或逻辑运算。

算术运:即数的加减乘除,乘方开方等。

逻辑运算:即逻辑变量,与或非等基本操作。

构成:由一个加法器、若干个寄存器和一些控制线路组成。

核心是加法器(Adder),每次运算的中间结果暂时保留,所以需要若干个积存数据的据存器(Register)。

运算器的性能指标是计算机的字长和运算速度。

2.1.2控制器-CU(Contorl Unit)功能:指挥整个机器各个部件自动、协调工作。

构成:指令寄存器、译码器、时序节拍发生器、操作控制部件、指令计数器。

机器指令的执行过程:1,机器指令:计算机可以真正“执行”的命令。

操作码源操作数(或地址)目的操作数机器指令构成:操作码+操作数,操作码指明指令索要完成的操作的性质与功能。

操作数指明操作吗执行时的操作对象。

指令基本格式:(2)指令的执行过程1)取指令,根据程序计数器里的内容到存储器中读取当前要执行的指令,同时把他放到指令寄存器中。

2)分析指令,译码器开始译码,取出要执行的指令,并放到指令寄存器IR中。

3)生成控制信号,控制器根据译码器的输出,按一定顺序产生执行该指令的所有控制信号。

4)执行指令,在控制信号的作用下,计算机各个部件完成相应的工作。

5),重复执行:计算机根据PC中新的指令地址,重复执行上述4个过程,直至执行到指令结束。

汇编指令机器执行周期80x86 Integer Instruction Set (8088 - Pentium)Click FPU opcodes for floating point instructionsJump to end of legendLegend:Generalacc = AL, AX or EAX unless specified otherwisereg = any general registerr8 = any 8-bit registerr16 = any general purpose 16-bit registerr32 = any general purpose 32-bit registerimm = immediate dataimm8 = 8-bit immediate dataimm16 = 16-bit immediate datamem = memory addressmem8 = address of 8-bit data itemmem16 = address of 16-bit data itemmem32 = address of 32-bit data itemmem48 = address of 48-bit data itemdest = 16/32-bit destinationshort = 8-bit destinationInteger instruction timings:n - generally refers to a number of repeated countsm - in a jump or call;286: bytes in next instruction386/486: number of components(each byte of opcode) + 1 (if immed data) + 1 (if displacement)EA = cycles to calculate the Effective Address8088/8086:base = 5 BP+DI or BX+SI = 7 BP+DI+disp or BX+SI+disp = 11index = 5 BX+DI or BP+SI = 8 BX+DI+disp or BP+SI+disp = 12disp = 6 segment override = +2286 - 486:base+index+disp = +1 all others, no penaltyinstruction length:The byte count includes the opcode length and length of any required displacement or immediate data. If the displacement is optional, it is shown as d() with the possible lengths in parentheses. If the immediate data is optional, it is shown as i() with the possible lengths in parentheses.pairing categories for Pentium:NP = not pairableUV = pairable in the U pipe or V pipePU = pairable in the U pipe onlyPV = pairable in the V pipe only(end of legend)Instruction formats, clock cycles and Pentium? Pairing info AAA ASCII adjust after additionbytes 8088 186 286 386 486 Pentium1 8 8 3 4 3 3 NPExample: aaaAAD ASCII adjust AX before division (second byte is divisor) bytes 8088 186 286 386 486 Pentium2 60 15 14 19 14 10 NPExample: aadAAM ASCII adjust AX after multiply (second byte is divisor)bytes 8088 186 286 386 486 Pentium2 83 19 16 17 15 18 NPExample: aamAAS ASCII adjust AL after subtractionbytes 8088 186 286 386 486 Pentium1 8 7 3 4 3 3 NPExample: aasADC Integer add with carryoperands bytes 8088 186 286 386 486 Pentiumreg, reg 2 3 3 2 2 1 1 PUmem, reg 2+d(0,2) 24+EA 10 7 7 3 3 PUreg, mem 2+d(0,2) 13+EA 10 7 6 2 2 PUreg, imm 2+i(1,2) 4 4 3 2 1 1 PUmem, imm 2+d(0,2) 23+EA 16 7 7 3 3 PU*+i(1,2)acc, imm 1+i(1,2) 4 4 3 2 1 1 PU* = not pairable if there is a displacement and immediate Example: adc eax, ebxADD Integer additionoperands bytes 8088 186 286 386 486 Pentiumreg, reg 2 3 3 2 2 1 1 UVmem, reg 2+d(0,2) 24+EA 10 7 7 3 3 UVreg, mem 2+d(0,2) 13+EA 10 7 6 2 2 UVreg, imm 2+i(1,2) 4 4 3 2 1 1 UVmem, imm 2+d(0,2) 23+EA 16 7 7 3 3 UV*+i(1,2)acc, imm 1+i(1,2) 4 4 3 2 1 1 UV* = not pairable if there is a displacement and immediate Example: add eax, ebxAND Logical ANDoperands bytes 8088 186 286 386 486 Pentiumreg, reg 2 3 3 2 2 1 1 UVmem, reg 2+d(0,2) 24+EA 10 7 7 3 3 UVreg, mem 2+d(0,2) 13+EA 10 7 6 2 2 UVreg, imm 2+i(1,2) 4 4 3 2 1 1 UVmem, imm 2+d(0,2) 23+EA 16 7 7 3 3 UV*+i(1,2)acc, imm 1+i(1,2) 4 4 3 2 1 1 UV* = not pairable if there is a displacement and immediate Example: and eax, ebxARPL Adjust RPL field of selector (286+)operands bytes 286 386 486 Pentiumreg, reg 2 10 20 9 7 NPmem, reg 2+d(0-2) 11 21 9 7 NPExample: arpl ax, bxBOUND Check array index against bounds (186+) operands bytes 186 286 386 486 Pentiumreg, mem 4 35 13 10 7 8 NPExample: bound bx, arrayBSF Bit scan forward (386+)operands bytes 386 486 Pentiumr16, r16 3 10+3n 6-42 6-34 NPr32, r32 3 10+3n 6-42 6-42 NPr16, m16 3+d(0,1,2) 10+3n 7-43 6-35 NPr32, m32 3+d(0,1,2,4) 10+3n 7-43 6-43 NP Example: bsf eax, [esi]BSR Bit scan reverse (386+)operands bytes 386 486 Pentiumr16, r16 3 10+3n 6-103 7-39 NPr32, r32 3 10+3n 7-104 7-71 NPr16, m16 3+d(0,1,2) 10+3n 6-103 7-40 NP r32, m32 3+d(0,1,2,4) 10+3n 7-104 7-72 NP Example: bsr eax, [esi]BSWAP Byte swap (486+)operand bytes 486 Pentiumr32 2 1 1 NPExample: bswap eaxBT Bit test (386+)operands bytes 386 486 Pentiumreg, reg 3 3 3 4 NPmem, reg 3+d(0,1,2,4) 12 8 9 NPreg, imm8 3+i(1) 3 3 4 NPmem, imm8 3+d(0,1,2,4)+i(1) 6 3 4 NP Example: bt eax, 4BTC Bit test and complement (386+) operands bytes 386 486 Pentiumreg, reg 3 6 6 7 NPmem, reg 3+d(0,1,2,4) 13 13 13 NPreg, imm8 3+i(1) 6 6 7 NPmem, imm8 3+d(0,1,2,4)+i(1) 8 8 8 NP Example: btc eax, 4BTR Bit test and reset (386+)operands bytes 386 486 Pentiumreg, reg 3 6 6 7 NPmem, reg 3+d(0,1,2,4) 13 13 13 NPreg, imm8 3+i(1) 6 6 7 NPmem, imm8 3+d(0,1,2,4)+i(1) 8 8 8 NP Example: btr eax, 4BTS Bit test and set (386+)operands bytes 386 486 Pentiumreg, reg 3 6 6 7 NPmem, reg 3+d(0,1,2,4) 13 13 13 NPreg, imm8 3+i(1) 6 6 7 NPmem, imm8 3+d(0,1,2,4)+i(1) 8 8 8 NP Example: bts eax, 4CALL Call subroutineoperand bytes 8088 186 286 386 486 Pentiumnear 3 23 14 7+m 7+m 3 1 PVreg 2 20 13 7+m 7+m 5 2 NPmem16 2+d(0-2) 29+EA 19 11+m 10+m 5 2 NPfar 5 36 23 13+m 17+m 18 4 NPmem32 2+d(0-2) 53+EA 38 16+m 22+m 17 4 NP Protected Modeoperand bytes 286 386 486 Pentiumfar 5 26+m 34+m 20 4-13 NPmem32 2+d(0-2) 29+m 38+m 20 5-14 NPcycles not shown for calls through call and task gates Example: call my_functionCBW Convert byte to word (AL --> AX)bytes 8088 186 286 386 486 Pentium1 2 2 2 3 3 3 NPExample: cbwCWDE Convert word to dword (386+) (AX --> EAX) bytes 386 486 Pentium1 3 3 3 NPExample: cwdeCWD Convert word to double (AX --> DX:AX)bytes 8088 186 286 386 486 Pentium1 5 42 23 2 NPExample: cwdCDQ Convert double to quad (EAX --> EDX:EAX) bytes 386 486 Pentium1 2 3 2 NPExample: cdqCLC Clear the carry flagbytes 8088 186 286 386 486 Pentium1 2 2 2 2 2 2 NPExample: clcCLD Clear the direction flag (set to forward direction) bytes 8088 186 286 386 486 Pentium1 2 2 2 2 2 2 NPExample: cldCLI Clear the interrupt flag (disable interrupts) bytes 8088 186 286 386 486 Pentium1 2 2 3 3 5 7 NPExample: cliCLTS Clear task switched flag in CR0 (286+)bytes 286 386 486 Pentium2 2 5 7 10 NPExample: cltsCMC Complement carry flagbytes 8088 186 286 386 486 Pentium1 2 2 2 2 2 2 NPExample: cmcCMP Compare two operandsoperands bytes 8088 186 286 386 486 Pentium reg, reg 2 3 3 2 2 1 1 UVmem, reg 2+d(0,2) 13+EA 10 7 5 2 2 UVreg, mem 2+d(0,2) 13+EA 10 6 6 2 2 UVreg, imm 2+i(1,2) 4 4 3 2 1 1 UVmem, imm 2+d(0,2) 14+EA 10 6 5 2 2 UV*+i(1,2)acc, imm 1+i(1,2) 4 4 3 2 1 1 UV* = not pairable if there is a displacement and immediate Example: cmp eax, 3CMPS/CMPSB/CMPSW/CMPSD Compare string operands variations bytes 8088 186 286 386 486 Pentiumcmpsb 1 30 22 8 10 8 5 NPcmpsw 1 - - - 10 8 5 NPcmpsd 1 - - - 10 8 5 NPrepX cmpsb 2 9+30n 5+22n 5+9n 5+9n 7+7n* 9+4n NP repX cmpsw 2 9+30n 5+22n 5+9n 5+9n 7+7n* 9+4n NP repX cmpsd 2 - - - 5+9n 7+7n* 9+4n NPrepX = repe, repz, repne or repnz* : 5 if n = 0Example: repne cmpsbCMPXCHG Compare and Exchange (486+)operands bytes 486 Pentiumreg, reg 3 6 5 NPmem, reg 3+d(0-2) 7-10 6 NPExample: cmpxchg ebx, edxCMPXCHG8B Compare and Exchange 8 bytes (Pentium+) operands bytes Pentiummem, reg 3+d(0-2) 10 NPExample: cmpxchg8b [ebx], edxCPUID CPU identification (Pentium+)bytes PentiumExample: cpuidDAA Decimal adjust AL after additionbytes 8088 186 286 386 486 Pentium1 4 4 3 423 NPExample: daaDAS Decimal adjust AL after subtractionbytes 8088 186 286 386 486 Pentium1 4 4 3 423 NPExample: dasDEC Decrementoperand bytes 8088 186 286 386 486 Pentiumr8 2 3 3 2 2 1 1 UVr16 1 3 3 2 2 1 1 UVr32 1 3 3 2 2 1 1 UVmem 2+d(0,2) 23+EA 15 7 6 3 3 UV Example: dec eaxDIV Unsigned divideoperand bytes 8088 186 286 386 486 Pentiumr8 2 80-90 29 14 14 16 17 NPr16 2 144-162 38 22 22 24 25 NPr32 2 - - - 38 40 41 NPmem8 2+d(0-2) 86-96+EA 35 17 17 16 17 NP mem16 2+d(0-2) 150-168+EA 44 25 25 24 25 NP mem32 2+d(0-2) - - - 41 40 41 NPimplied operand quotient remainderAX / byte = AL AHDX:AX / word = AX DXEDX:EAX / dword = EAX EDXExample: div ebxENTER Make stack frame for procedure parameters (186+) operands bytes 8088 186 286 386 486 Pentiumimm16, 0 3 - 15 11 10 14 11 NPimm16, 1 4 - 25 15 12 17 15 NPimm16, imm8 4 - 22+16n 12+4n 15+4n 17+3i 15+2i NPn = imm8-1; i = imm8Example: enter 1, 0ESC Escapeescape opcodes D8 - DF are used by floating point instructionsHLT Haltbytes 8088 186 286 386 486 Pentium1 2 2 2 5 4 4 NPExample: hltIDIV Signed divideoperand bytes 8088 186 286 386 486 Pentiumr8 2 101-112 44-52 17 19 19 22 NPr16 2 165-184 53-61 25 27 27 30 NPr32 2 - - - 43 43 46 NPmem8 2+d(0-2) 107-118+EA 50-58 20 22 20 22 NPmem16 2+d(0-2) 171-190+EA 59-67 28 30 28 30 NPmem32 2+d(0-2) - - - 46 44 46 NPimplied operand quotient remainderdividendAX / byte = AL AHDX:AX / word = AX DXEDX:EAX / dword = EAX EDXExample: idiv ebxIMUL Signed multiplyAccumulator Multipliesoperand bytes 8088 186 286 386 486 Pentiumr8 2 80-98 25-28 13 9-14 13-18 11 NPr16 2 128-154 34-37 21 9-22 13-26 11 NPr32 2 - - - 9-38 13-42 10 NPmem8 2+d(0-2) 86-104+EA 32-34 16 12-17 13-18 11 NPmem16 2+d(0-2) 134-160+EA 40-43 24 12-25 13-26 11 NP mem32 2+d(0-2) - - - 12-41 13-42 10 NPimplied operand resultmultiplicand (multiplier)AL * byte = AXAX * word = DX:AXEAX * dword = EDX:EAXExample: imul ebx2 and3 operand Multipliesoperands bytes 186 286 386 486 Pentiumr16, imm 2+i(1,2) - 21 9-14/9-22 13-18/13-26 10 NPr32, imm 2+i(1,2) - - 9-38 13-42 10 NPr16,r16,imm 2+i(1,2) 22/29 21 9-14/9-22 13-18/13-26 10 NP r32,r32,imm 2+i(1,2) - - 9-38 13-42 10 NPr16,m16,imm 2+d(0-2) 25/32 24 12-17/12-25 13-18/13-26 10 NP+i(1,2)r32,m32,imm 2+d(0-2)+i(1,2) - 12-41 13-42 10 NPr16, r16 2+i(1,2) - - 9-22 13-18/13-26 10 NPr32, r32 2+i(1,2) - - 9-38 13-42 10 NPr16, m16 2+d(0-2)+i(1,2) - 12-25 13-18/13-26 10 NP r32, m32 2+d(0-2)+i(1,2) - 12-41 13-42 10 NPall forms: dest, src cycles for: byte/word or dword dest, src1, src2Example: imul eax, ebx, 10IN Input from portoperands bytes 8088 186 286 386 486 Pentiumal, imm8 2 14 10 5 12 14 7 NPax, imm8 2 14 10 5 12 14 7 NPeax, imm8 2 - - - 12 14 7 NPal, dx 1 12 8 5 13 14 7 NPax, dx 1 12 8 5 13 14 7 NPeax, dx 1 - - - 13 14 7 NPProtected modeoperands bytes 386 486 Pentiumacc, imm 2 6/26/26 9/29/274/21/19 NPacc, dx 1 7/27/27 8/28/274/21/19 NPcycles for: CPL <= IOPL / CPL > IOPL / V86 Example: in al, dxINC Incrementoperand bytes 8088 186 286 386 486 Pentiumr8 2 3 3 2 2 1 1 UVr16 1 3 3 2 2 1 1 UVr32 1 3 3 2 2 1 1 UVmem 2+d(0,2) 23+EA 15 7 6 3 3 UVExample: inc ebxINS/INSB/INSW/INSD Input from port to stringvariations bytes 8088 186 286 386 486 Pentium insb 1 - 14 5 15 17 9 NPinsw 1 - 14 5 15 17 9 NPinsd 1 - - - 15 17 9 NPProtected Modebytes 386 486 Pentium1 9/29/29 10/32/30 6/24/22 NPcycles for: CPL <= IOPL / CPL > IOPL / V86 Example: rep insbINT Call interrupt procedureoperands bytes 8088 186 286 386 486 Pentium 3 1 72 45 23+m 33 26 13 NPimm8 2 71 47 23+m 37 30 16 NPProtected modebytes 8088 186 286 386 486 Pentium1 - - (40-78)+m 59-99 44-71 27-82 NPExample: int 21hINTO Call interrupt procedure if overflow bytes 8088 186 286 386 486 Pentium1 4/73 4/48 3/24+m 3/35 3/28 4/13 NP Protected modebytes 286 386 486 Pentium1 (40-78)+m 59-99 44-71 27-56 NPTask switch clocks not shownExample: intoINVD Invalidate data cache (486+)bytes 8088 186 286 386 486 Pentium2 - - - - 4 15 NPExample: invdINVLPG Invalidate TLB entry (486+)operands bytes 486 Pentiummem32 5 12 25 NPExample: invlpg [eax]IRET Return from interruptbytes 8088 186 286 386 486 Pentium1 44 28 17+m 22 15 8-27 NPTask switch clocks not shownExample: iretIRETD 32-bit return from interrupt (386+)bytes 386 486 Pentium1 22 15 10-27 NPTask switch clocks not shownExample: iretdJcc Jump on condition codeoperand bytes 8088 186 286 386 486 Pentiumnear8 2 4/16 4/13 3/7+m 3/7+m 1/3 1 PVnear16 3 - - - 3/7+m 1/3 1 PVcycles for: no jump/jumpconditional jump instructions:ja jump if above jnbe jump if not below or equal jae jump if above or equal jnb jump if not belowjb jump if below jnae jump if not above or equal jbe jump if below or equal jna jump if not abovejg jump if greater jnle jump if not less or equal jge jump if greater or equal jnl jump if not lessjl jump if less jnge jump if not greater or equaljle jump if less or equal jng jump if not greater je jump if equal jz jump if zerojne jump if not equal jnz jump if not zerojc jump if carry jnc jump if not carryjs jump if sign jns jump if not signjnp jump if no parity (odd) jpo jump if parity odd jo jump if overflow jno jump if not overflowjp jump if parity (even) jpe jump if parity even Example: jne not_equalJCXZ/JECXZ Jump if CX/ECX = 0operand bytes 8088 186 286 386 486 Pentium dest 2 6/18 5/16 4/8+m 5/9+m 5/8 5/6 NP dest 2 - - - 5/9+m 5/8 5/6 NPcycles for: no jump/jumpExample: jcxz cx_is_zeroJMP Unconditional jumpoperand bytes 8088 186 286 386 486 Pentium short 2 15 13 7+m 7+m 3 1 PVnear 3 15 13 7+m 7+m 3 1 PVfar 5 15 13 11+m 12+m 17 3 NPr16 2 11 11 7+m 7+m 5 2 NPmem16 2+d(0,2) 18+EA 17 11+m 10+m 5 2 NP mem32 2+d(4) 24+EA 26 15+m 12+m 13 4 NP r32 2 - - - 7+m 5 2 NPmem48 2+d(6) - - - 12+m 13 4 NPcycles for jumps through call gates not shown Example: jmp target_addressLAHF Load flags into AHbytes 8088 186 286 386 486 Pentium1 42 2 23 2 NPExample: lahfLAR Load access rights byte (286+) operands bytes 286 386 486 Pentiumr16, r16 3 14 15 11 8 NPr32, r32 3 - 15 11 8 NPr16, m16 3 16 16 11 8 NPr32, m32 3 - 16 11 8 NPExample: lar eax, ebxLDS Load far pointeroperands bytes 8088 186 286 386 486 Pentium reg, mem 2+d(2) 24+EA 18 7 7 6 4 NP Example: lds si, ptr_1LES Load far pointeroperands bytes 8088 186 286 386 486 Pentium reg, mem 2+d(2) 24+EA 18 7 7 6 4 NP Example: les di, ptr_2LFS Load far pointer (386+)operands bytes 386 486 Pentium Example: lfs si, ptr_3LGS Load far pointer (386+)operands bytes 386 486 Pentiumreg, mem 3+d(2,4) 7 6 4 NPExample: lgs si, ptr_4LSS Load stack segment and offset operands bytes 386 486 Pentiumreg, mem 3+d(2,4) 7 6 4 NPExample: lss bp, ptr_5LEA Load effective addressoperands bytes 8088 186 286 386 486 Pentiumr16, mem 2+d(2) 2+EA 6 3 2 1-2 1 UVr32, mem 2+d(2) - - - 2 1-2 1 UVExample: lea eax, [eax+ebx*2+3]LEAVE High level procedure exit (186+)bytes 186 286 386 486 Pentium1 8 5 4 5 3 NPExample: leaveLGDT Load global descriptor table register (286+) operand bytes 286 386 486 Pentiummem48 5 11 11 11 6 NPExample: lgdt descriptor[ebx]LIDT Load interrupt descriptor table register (286+) mem48 5 12 11 11 6 NPExample: lidt descriptor[ebx]LLDT Load local descriptor table register (286+) operand bytes 286 386 486 Pentiumr16 3 17 20 11 9 NPmem16 3+d(0-2) 19 24 11 9 NPExample: lldt axLMSW Load machine status word (286+)operand bytes 286 386 486 Pentiumr16 3 3 10 13 8 NPmem16 3+d(0-2) 6 13 13 8 NPExample: lmsw axLOCK Lock bus on next instruction (prefix)bytes 8088 186 286 386 486 Pentium1 2 2 0 0 1 1 NP(Note: xchg always is locked whether it is specified or not) Example: lock mov mem, 1LODS/LODSB/LODSW/LODSD Load string operand variations bytes 8088 186 286 386 486 Pentium lodsb 1 16 10 5 5 5 2 NPlodsw 1 16 10 5 5 5 2 NPlodsd 1 - - - 5 5 2 NPExample: lodsbLOOP Loop control with CX countershort 2 5/17 5/15 4/8+m 11+m 6/7 5/6 NPloopw short (uses CX in 32-bit mode)loopd short (uses ECX in 16-bit mode) Example: loop loop_startLOOPE/LOOPZ Loop while equal (or zero) operand bytes 8088 186 286 386 486 Pentium short 2 6/18 5/16 4/8 11+m 6/9 7/8 NPloopew short (uses CX in 32-bit mode)loopzw short (uses CX in 32-bit mode)looped short (uses ECX in 16-bit mode)loopzd short (uses ECX in 16-bit mode) Example: loope loop_startLOOPNE/LOOPNZ Loop while not equal (or not zero) operand bytes 8088 186 286 386 486 Pentium short 2 5/19 5/16 4/8 11+m 6/9 7/8 NPloopnew short (uses CX in 32-bit mode)loopnzw short (uses CX in 32-bit mode)loopned short (uses ECX in 16-bit mode)loopnzd short (uses ECX in 16-bit mode) Example: loopne loop_startLSL Load segment limit (286+)operands bytes 286 386 486 Pentiumr16, r16 3 14 20/25 10 8 NPr32, r32 3 - 20/25 10 8r16, m16 3+d(0,2) 16 21/26 10 8r32, m32 3+d(0,2) - 21/26 10 8 Example: lsl eax, ebxLTR Load task register (286+) operand bytes 286 386 486 Pentium。

简述功能指令的执行方法及特点

功能指令是一种由用户通过语言或其他形式输入给机器人的指令,用于执行特定的功能或操作。

下面是功能指令的执行方法及特点的简要描述:

1. 执行方法:

- 文本输入:用户可通过与机器人对话、填写表单或使用特定的输入界面等方式,将指令以文本形式输入。

- 语音输入:用户通过语音识别技术,将口头指令转换为文本形式,再传递给机器人执行。

- 图像输入:用户通过拍照或上传图片的方式,将图像中的指令传递给机器人。

2. 特点:

- 实时反馈:功能指令通常会立即得到机器人的反馈,可以是文字回复、语音回答、特定操作等方式。

- 自动化执行:机器人会根据指令自动执行相应的功能,无需用户手动操作。

- 多样性:功能指令的范围很广,可以涵盖各种操作,如搜索信息、播放音乐、预订机票等。

- 个性化服务:机器人可以根据用户的个人需求和偏好执行相应的功能,提供个性化的服务。

- 学习能力:一些机器人具备自学习能力,可以根据用户的使用习惯和反馈进行改进和优化。

需要注意的是,具体的功能指令执行方法和特点可能因机器人的不同而有所差异,以上为一般情况的描述。

实验四微程序控制器设计实验一、实验目的(1)掌握时序产生器的组成原理。

(2)掌握微程序控制器的组成原理。

(3)加深理解微指令与机器指令的关系。

二、实验电路1.时序发生器TEC-4计算机组成原理实验系统的时序电路如图6所示。

图6 时序信号发生器图电路采用2片GAL22V10(U6,U7),可产生两级等间隔时序信号T1-T4和W1-W4,其中一个W 由一轮T1-T4循环组成,它相当于一个微指令周期或硬联线控制器的一拍,而一轮W1-W4循环可供硬联线控制器执行一条机器指令。

本实验不涉及硬联线控制器。

微程序控制器只使用时序信号T1-T4,产生T信号的功能集成在GAL22VlO芯片TIMER1(U6)中,另外它还产生节拍信号W1、W2、W3、W4的控制时钟CLK1。

TIMER1的输入信号中,MF接实验台上晶体振荡器的输出,频率为1MHz。

T1至T4的脉冲宽度为100ns。

CLR(注意,实际上是控制台上的CLR#信号,因为ABEL语言的书写关系改为CLR,仍为低有效信号)为复位信号,低有效。

实验仪处于任何状态下令CLR# = 0,都会使时序发生器和微程序控制器复位(回到初始状态),CLR# = l时,则可以正常运行。

复位后时序发生器停在T4、W4状态,微程序地址为000000B。

建议每次实验仪加电后,先用CLR#复位一次。

控制台上有一个CLR#按钮,按一次,产生一个CLR#负脉冲,实验台印制板上已连好控制台CLR#到时序电路CLR的连线。

TJ(停机)是控制器的输出信号之一。

连续运行时,如果控制信号TJ = l,会使机器停机,停止发送时序脉冲T1-T4、W1-W4,时序停在T4。

在实验台上为了将时序信号发生器的输入信号TJ和控制存储器产生的TJ信号区分开来,以便于连线操作,在实验台上时序信号发生器的输入信号TJ命名为TJI,而控制存储器产生的信号TJ仍命名为TJ。

QD(启动)是来自启动按钮QD的脉冲信号,在TIMER1中,对QD用MF进行了同步,产生QD1和QD2。

ACT表示QD1上升沿,表达式是QDl&!QD2,脉冲宽度为1000ns。

QDR是运行标志,QD信号使其为l,CLR信号将其置0。

DP(单拍)是来自控制台的DP开关信号,当DP = l时,机器处于单拍运行状态,按一次启动按钮QD,只发送一条微指令周期的时序信号就停机。

利用单拍方式,每次只执行一条微指令,因而可以观察微指令代码和当前微指令的执行结果。

DZ(单指)信号是针对微程序控制器的,接控制台开关DZ和P1信号配合使用。

Pl是微指令字判断字段中的一个条件信号,从微程序控制器输出。

Pl信号在微程序中每条机器指令执行结束时为l,用于检测有无中断请求INTQ,而时序发生器用它来实现单条机器指令停机。

在DB = 0且DP = 0的前提下,当DZ = 0时,机器连续运行。

当DZ = 1时,机器处于单指方式,每次只执行一条机器指令。

DB、SKIP、CLK1信号以及W1-W4时序信号都是针对硬布线控制器的。

W1-W4是节拍信号,硬布线控制器执行一条机器指令需要一组W1-W4信号。

DB(单步)信号就是每次发送一组W信号后停机,可见其功能与DZ类似。

执行某些机器指令不需要完整的一组W信号周期,SKIP信号就是用来跳过本指令剩余的W节拍信号的。

中断允许标志IE由控制存储器的输出信号INTS将其置1,由控制存储器的输出信号INTC将其置0。

在TIMER2内部,控制台产生的中断请求用时钟CLK1进行同步,产生了INTR1。

只有在INTE = l时,控制台产生的中断请求脉冲INTR才能起作用,即产生向控制器输出中断信号INTQ,INTQ = INTE & INTR1。

2.数据通路微程序控制器是根据数据通路和指令系统来设计的。

这里采用的数据通路是在综合前面各实验模块的基础上,又增加程序计数器PC(U18)、地址加法器ALU2(U17)、地址缓冲寄存器R4(U25、U26)和中断地址寄存器IAR(U19)。

PC和ALU2各采用一片GAL22V10,两者配合使用,可完成程序地址的存储、增1和加偏移量的功能。

R4由两片74HC298组成,带二选一输入端。

IAR是一片74HC374,用于中断时保存断点地址。

3.微指令格式与微程序控制器电路根据给定的12条机器指令功能和数据通路总体图的控制信号,采用的微指令格式见图7。

微指令字长共35位。

其中顺序控制部分10位(后继微地址6位,判别字段4位),操作控制字段25位,各位进行直接控制。

微指令格式中,信号名带有后缀“#”的信号为低有效信号,不带有后缀“#”的信号为高有效信号。

图7 微指令格式对应微指令格式,微程序控制器的组成如图8所是示:图8微程序控制器的组成控制存储器采用5片EEPROM 28C64(U8,U9,U10,U11,U12)。

28C64的输出是D0-D7,分别与引脚11、12、13、15、16、17、18、19相对应,CM0是最低字节,CM4是最高字节。

微地址寄存器6位,用一片6D触发器74HC174(U1)组成,带有清零端。

两级与门、或门构成微地址转移逻辑,用于产生下一微指令的地址。

在每个T1上升沿时刻,新的微指令地址会打入微地址寄存器中,控制存储器随即输出相应的微命令代码。

微地址转移逻辑生成下一地址,等下一个T1上升沿时打入微地址寄存器。

跳转开关JUMP(J1)是一组6个跳线开关。

当用短路子将它们连通时,微地址寄存器μAR从本实验系统提供的微程序地址译码电路得到新的微程序地址μD0-μD5。

当他们被断开时,用户提供自已的新微程序地址μD0-μD5。

这样用户能够使用自己设计的微程序地址译码电路。

5片EEPROM的地址A6(引脚4)直接与控制台开关SWC连接,当SWC = 1时,微地址大于或者等于40H,当SWC = 0时,微地址的范围00H-3FH。

SWC主要用于实现读寄存器堆的功能。

微地址转移逻辑的多个输入信号中,INTQ是中断请求,本实验中可以不理会它。

SWA、SWB是控制台的两个二进制开关信号,实验台上线已接好。

C是进位信号,IR7-IR4是机器指令代码,由于本次实验不连接数据通路,这些信号都接到二进制开关K0—Kl5上。

三、机器指令与微程序为了在教学中简单明了,本实验仪使用12条机器指令,均为单字长(8位)指令。

应当指出,用以上12条指令来编写实际程序是不够的。

好在我们的目的不是程序设计,而主要是为了教学,通过CPU执行一些最简单的程序来掌握微程序控制器的工作原理。

上述12条指令的微程序流程设计如图9所示。

每条微指令可按前述的微指令格式转换成二进制代码,然后写入5个28C64中。

图9 微程序流程图为了向RAM中装入程序和数据,检查写入是否正确,并能启动程序执行,还设计了以下五个控制台操作微程序:存储器写操作(KWE):按下复位按钮CLR#后,微地址寄存器状态为全零。

此时置SWC = 0、SWB =1、SWA = 0,按启动按钮后微指令地址转入27H,从而可对RAM连续进行手动写入。

存储器读操作(KRD):按下复位按钮CLR#后,置SWC = 0,SWB = 0,SWA = 1,按启动按钮后微指令地址转入17H,从而可对RAM连续进行读操作。

写寄存器操作(KLD):按下复位按钮CLR#后,置SWC = 0,SWB = 1,SWA = 1,按启动按钮后微指令地址转入37H,从而可对寄存器堆中的寄存器连续进行写操作。

读寄存器操作(KRR):按下复位按钮CLR#后,置SWC = 1,SWB = 0,SWA = 0,按启动按钮后微指令地址转入47H,从而可对寄存器堆中的寄存器连续进行读操作。

启动程序(PR):按下复位按钮CLR#后,置SWC = 0,SWB = 0,SWA = 0,用数据开关SW7-SW0设置内存中程序的首地址,按启动按钮后微指令地址转入07H,然后转到“取指”微指令。

应当着重指出,在微指令格式的设计过程中,对数据通路所需的控制信号进行了归并和化简。

细心的同学可能已经发现,微程序控制器输出的控制信号远远少于数据通路所需的控制信号。

这里提供的微程序流程图是没有经过归并和化简的。

仔细研究一下微程序流程图,就会发现有些信号出现的位置完全一样,这样的信号用其中一个信号就可以代表。

请看信号LDPC和LDR4,这两个信号都在微程序地址07H,1AH,1FH,26H出现,而在其他的微程序地址都不出现,因此这两个信号产生的逻辑条件是完全一样的。

从逻辑意义上看,这两个信号的作用是产生新的PC,完全出现在相同的微指令中是很正常的,因此用LDPC完全可以代替LDR4。

还有另一些信号,例如LDDR1和LDDR2,出现的位置基本相同。

LDDR2和LDDR1的唯一不同是在地址14H的微指令中,出现了LDDR2信号,但是没有出现LDDR1信号。

LDDR1和LDDR2是否也可以归并成一个信号呢?答案是肯定的。

微程序流程图中只是指出了在微指令中必须出现的信号,并没有指出出现其他信号行不行,这就要根据具体情况具体分析。

在地址14H的微指令中,出现LDDR1信号行不行呢?完全可以。

在地址14H出现的LDDR1是一个无用的信号,同时也是一个无害的信号,它的出现完全没有副作用,因此LDDR1和LDDR2可以归并为一个信号LDDR1。

根据以上两条原则,我们对下列信号进行了归并和化简:LDIR(CER) 为1时,允许对IR加载,此信号也可用于作为双端口存储器右端口选择CER。

LDPC(LDR4)为l时,允许对程序计数器PC加载,此信号也可用于作为R4的加载允许信号LDR4。

LDAR1(LDAR2)为l时,允许对地址寄存器AR1加载,此信号也可用于作为对地址寄存器AR2加载。

LDDR1(LDDR2)为1时允许对操作数寄存器DR1加载。

此信号也可用于作为对操作数寄存器DR2加载。

Ml(M2)当M1 = l时,操作数寄存器DR1从数据总线DBUS接收数据;当M1 = 0时,操作数寄存器DR1从寄存器堆RF接收数据。

此信号也可用于作为操作数寄存器DR2的数据来源选择信号。

在对微指令格式进行归并和化简的过程中,我们有意保留了一些信号,没有化简,同学们可以充分发挥创造性,提出更为简单的微指令格式。

还要说明的是,为什么微指令格式可以化简,而实验台数据通路的控制信号为什么不进行化简?最主要的原因是前面进行的各个实验的需要,例如LDDR1和LDDR2这两个信号,在做运算器数据通路实验时,是不能设计成一个信号的。

还有一个原因是考虑到实验时易于理解,对某些可以归并的信号也没有予以归并。

四、实验设备(1)TEC-4计算机组成原理实验系统一台(2)直流万用表一只(3)逻辑测试笔一支五、实验任务(1)按实验要求,连接实验台的开关K0—K15、按钮开关、时钟信号源和微程序控制器。