状态机时钟

- 格式:doc

- 大小:261.44 KB

- 文档页数:5

时序逻辑电路的分类时序逻辑电路是一种能够在特定的时间序列下执行特定操作的电路。

它通常由组合逻辑电路和存储器组成,可以实现复杂的计算和控制功能。

时序逻辑电路按照其实现功能的不同,可以分为以下几类。

一、触发器触发器是最基本的时序逻辑电路之一,它可以存储一个比特位,并且在时钟信号到来时根据输入信号的状态改变输出状态。

常见的触发器有SR触发器、D触发器、JK触发器和T触发器等。

二、计数器计数器是一种能够在特定条件下对输入信号进行计数并输出结果的电路。

它通常由若干个触发器组成,每个触发器都表示一个二进制位。

常见的计数器有同步计数器和异步计数器等。

三、移位寄存器移位寄存器是一种能够将输入信号从一个位置移动到另一个位置并输出结果的电路。

它通常由若干个触发器组成,每个触发器都表示一个二进制位。

常见的移位寄存器有串行入并行出移位寄存器、并行入串行出移位寄存器和并行入并行出移位寄存器等。

四、状态机状态机是一种能够根据输入信号的状态和时钟信号的变化改变输出状态的电路。

它通常由若干个触发器和组合逻辑电路组成,可以实现复杂的控制功能。

常见的状态机有Moore状态机和Mealy状态机等。

五、定时器定时器是一种能够在特定时间间隔内产生一个脉冲信号或者计数信号的电路。

它通常由若干个触发器和组合逻辑电路组成,可以实现复杂的定时功能。

常见的定时器有单稳态定时器和多稳态定时器等。

六、脉冲生成器脉冲生成器是一种能够在特定条件下产生一个脉冲信号的电路。

它通常由若干个触发器和组合逻辑电路组成,可以实现复杂的脉冲生成功能。

常见的脉冲生成器有单稳态脉冲生成器、多稳态脉冲生成器和斯奈德-哈特脉冲生成器等。

七、序列检测电路序列检测电路是一种能够在输入序列中检测出指定模式并输出相应结果的电路。

它通常由若干个触发器和组合逻辑电路组成,可以实现复杂的序列检测功能。

常见的序列检测电路有Moore序列检测器和Mealy序列检测器等。

八、时钟同步电路时钟同步电路是一种能够将异步输入信号转换为同步输出信号的电路。

vivado设计实例Vivado设计实例一、时钟分频器设计实例时钟分频器在数字电路设计中起到非常重要的作用,它可以将一个高频时钟信号分频为任意低频时钟信号。

在Vivado中,实现一个时钟分频器非常简单。

首先,我们需要创建一个新的工程,并添加时钟分频器的IP核。

然后,在IP核配置界面中,设置分频比和时钟输入输出端口。

最后,生成Bitstream文件并下载到目标FPGA芯片中即可。

二、状态机设计实例状态机是一种常见的电路设计模块,它根据输入信号的变化来改变其内部状态和输出信号。

在Vivado中,实现一个状态机可以通过HDL语言(如Verilog或VHDL)编写代码来实现。

首先,我们需要创建一个新的工程,并添加设计文件。

然后,在设计文件中编写状态机的逻辑代码,并将其综合为门级电路。

最后,生成Bitstream 文件并下载到目标FPGA芯片中即可。

三、数字信号处理设计实例数字信号处理(DSP)在通信、音频、视频等领域有着广泛的应用。

在Vivado中,实现一个简单的数字信号处理模块可以通过使用FIR滤波器来实现。

首先,我们需要创建一个新的工程,并添加FIR滤波器的IP核。

然后,在IP核配置界面中,设置滤波器的参数和输入输出端口。

最后,生成Bitstream文件并下载到目标FPGA芯片中即可。

四、图像处理设计实例图像处理在计算机视觉、图像识别等领域有着广泛的应用。

在Vivado中,实现一个简单的图像处理模块可以通过使用图像卷积来实现。

首先,我们需要创建一个新的工程,并添加图像卷积的IP核。

然后,在IP核配置界面中,设置卷积核的参数和输入输出端口。

最后,生成Bitstream文件并下载到目标FPGA芯片中即可。

五、高级通信接口设计实例高级通信接口(如PCIe、Ethernet等)在计算机系统中起到连接和传输数据的重要作用。

在Vivado中,实现一个高级通信接口可以通过使用相应的IP核来实现。

首先,我们需要创建一个新的工程,并添加所需的IP核。

jtag工作原理详解JTAG(Joint Test Action Group)是一种用于测试和调试集成电路的标准接口。

它提供了一种通用的方法,使得在生产过程中可以对芯片进行测试和调试,以确保其正常工作。

本文将详细介绍JTAG的工作原理,包括其基本原理、信号传输方式、测试模式和应用案例等方面。

一、JTAG的基本原理JTAG是一种串行接口,它通过少量的引脚与芯片内部的测试逻辑进行通信。

它主要由四个信号线组成,分别是TCK(时钟信号)、TMS(状态机信号)、TDI (数据输入信号)和TDO(数据输出信号)。

这些信号线通过一个称为TAP(Test Access Port)的接口与芯片内部的测试逻辑进行连接。

JTAG的工作原理是基于状态机的概念。

状态机是一种具有有限个状态和状态转移条件的数学模型,它用于描述JTAG在测试和调试过程中的不同操作。

JTAG通过改变TMS信号的状态来控制状态机的状态转移,从而实现不同的操作。

二、JTAG的信号传输方式JTAG使用的是一种称为“链式扫描”(Boundary Scan)的技术来传输数据。

在链式扫描中,芯片内部的各个逻辑单元被连接成一个链,数据通过这个链进行传输。

链式扫描技术使得JTAG可以在芯片生产过程中对内部的逻辑单元进行测试和调试。

链式扫描通过两个特殊的寄存器来实现数据的传输,分别是数据移位寄存器(Data Shift Register,DSR)和状态移位寄存器(State Shift Register,SSR)。

DSR用于传输数据,而SSR用于传输状态。

在数据移位寄存器中,数据从TDI输入,通过TCK的时钟信号逐位移入,然后通过TDO输出。

这样,可以将数据从外部输入到芯片内部,或者从芯片内部输出到外部。

在状态移位寄存器中,状态从TMS输入,通过TCK的时钟信号逐位移入,然后通过TDO输出。

这样,可以改变JTAG的状态,从而控制状态机的状态转移。

三、JTAG的测试模式JTAG有多种测试模式,常用的包括以下几种:1. Bypass模式:在Bypass模式下,JTAG将绕过芯片内部的测试逻辑,直接将TDI输入信号连接到TDO输出信号。

时序逻辑电路的状态机设计与时钟信号控制时序逻辑电路是一种能够根据不同的输入信号,按照一定的时序顺序产生相应的输出信号的电路。

而状态机则是一种特殊的时序逻辑电路,它能够根据当前状态和输入信号的变化来改变自身的状态,并产生相应的输出信号。

在状态机设计中,时钟信号的控制是至关重要的。

一、时序逻辑电路的基本原理时序逻辑电路是由触发器和组合逻辑门构成的。

触发器用来存储和改变电路的状态,而组合逻辑门则根据输入信号和当前的状态产生相应的输出信号。

触发器有很多种类型,如SR触发器、D触发器和JK触发器等。

它们的功能和特性各有不同,可以根据需求选择合适的触发器。

二、状态机的基本概念状态机是一种特殊的时序逻辑电路,它可以根据输入信号的变化和当前的状态来改变自身的状态,并产生相应的输出信号。

状态机由状态、输入、输出和状态转移四个部分组成。

状态表示了当前的状态,输入是指输入信号,输出是指输出信号,而状态转移则是根据输入信号和当前状态确定下一个状态的过程。

三、状态机的设计流程状态机的设计一般遵循以下几个步骤:1. 确定状态数量:首先需要确定需要多少个状态来满足设计需求。

状态数量的确定应该考虑到输入信号的变化以及输出信号的需要。

2. 状态编码:确定了状态数量后,就需要对每个状态进行编码。

状态编码可以使用二进制、格雷码或者其他编码方式。

3. 确定状态转移条件:根据输入信号和当前状态来确定下一个状态的转移条件。

可以使用真值表、卡诺图等方法进行分析和确定。

4. 绘制状态转移图:将状态数量和状态转移条件绘制成状态转移图,清晰地显示出每个状态之间的联系与转变。

5. 实现状态机:根据绘制好的状态转移图,选择合适的触发器和组合逻辑门进行设计和实现。

在设计过程中,要注意时钟信号的控制,确保状态机能够按照所需的顺序进行状态转移。

四、时钟信号对状态机的控制时钟信号是状态机中非常重要的一个因素,它用于控制状态机按照一定的时序进行状态转移。

时钟信号的频率和占空比在状态机设计中需要进行合理的选择和调整。

可调节电子表摘要我们正处在一个信息的时代,事物的发展和技术的进步,让我们享受到了诸多的便利。

尤其是电子表,它在我们的生活中无处不在。

电子表是内部装配有电子元件的表,一般分液晶显示数字式和石英指针式两种。

本次程程设计在Quartus II仿真软件上实现对电子表的设计。

学习电子表的设计不仅让我们拨开了电子表的奥妙,让我们更加牢固的掌握了74160、74193这一类的计数器的使用。

运用多个74160器件,使之产生模为24、60周期的计数器,按照一定的关系量来连接,从而产生进位,产生一个能循环计数的正常电子表的功能。

再设计一个电子表的调节电路图,以方便调节电子表。

完成两部分的封装,对设计结果进行验证,通过输入数据的变化,从而得到所需要的输出。

根据需要,或正常计时,或设定分钟和小时,都能得到正确的结果。

关键词:Quartus II,电子表,计数器,74160,调节Adjustable Electronic ClockABSTRACTWe are in the age of information, the development of things and technical progress, let us enjoy the many convenience. Especially electronic watch, it's in our life is everywhere. An electronic watch is internal assembly have electronic components watch, general points LCD digital and quartz pointer type two kinds. This ChengCheng design in Quartus II simulation software to achieve the design of electronic watch. The design of the electronic learning not only let us through the secrets of the digital watches, let us more solid knowledge of 74160, 74193 this kind of use of the counter. Use DuoGe 74160 devices, causes it to have the mold of 23, 59 cycle of counter, according to certain amount to the relationship between the connection, which carry and produce a cycle count of the normal can the function of digital watches. To design a digital watch the adjustment of the circuit diagram, with convenient adjustment electronic. Complete two part of the package, the design results were verified through the change of input data, and the output of the need. According to the needs, or normal time, or set up minutes and hours, can get the right result.Key words: Quartus II, electronic watch, counter, 74160, adjust目录前言 (1)第1章组成电路的芯片介绍 (3)1.1 74160芯片 (3)1.1.1 74160芯片符号 (3)1.1.2 74160工作原理 (3)第2章可调节电子表的顶层电路 (5)2.1 可调节电子表的顶层电路与说明 (5)2.1.1 可调节电子表的顶层电路图 (5)2.1.2 电路说明 (5)第3章可调节电子表详析 (6)3.1 可调节电子表 (6)3.2 设计原理详析 (8)3.2.1 计数原理 (8)3.2.2 校时电路原理 (8)3.3 仿真波形与分析 (10)第4章LCD液晶显示器实现 (13)4.1 LCD液晶显示器 (13)4.1.1 LCD液晶显示器源程序 (13)4.1.2 LCD显示器封装 (16)第5章下载验证 (17)结论 (19)谢辞 (20)参考文献 (21)附录 (22)前言在这个越来越时间化的社会中,各式各样的电子表在我们身边频出不烦,俨然成为我们里生活里不可或缺的一部分。

描述时序逻辑电路的方法时序逻辑电路是数字电路中的一种重要类型,它能够根据输入信号的时序关系产生特定的输出序列。

本文将介绍描述时序逻辑电路的方法。

一、引言时序逻辑电路是由时钟信号驱动的,它对输入信号的变化时间进行检测,并根据时钟信号的边沿触发产生相应的输出。

这种电路常用于计数器、状态机等应用中,可以实现各种复杂的功能。

二、状态图描述法状态图是描述时序逻辑电路工作过程的一种图形化表示方法。

它由状态和状态之间的转移组成,每个状态表示电路的某种特定状态,而状态之间的转移表示电路在不同状态之间的切换。

三、状态表描述法状态表是描述时序逻辑电路工作过程的一种表格形式。

它列出了电路的所有状态及其对应的输入和输出情况,可以清晰地表示电路的功能逻辑。

四、波形图描述法波形图是描述时序逻辑电路输入输出信号随时间变化的图形表示方法。

通过绘制输入输出信号的波形图,可以直观地观察和分析电路的工作过程。

五、RTL描述法RTL(Register Transfer Level)是一种描述时序逻辑电路的硬件描述语言。

它通过使用寄存器之间的数据传输来描述电路的功能和逻辑,可以方便地进行电路的仿真和综合。

六、Verilog描述法Verilog是一种用于描述数字系统的硬件描述语言,也可以用来描述时序逻辑电路。

通过使用Verilog语言,可以方便地进行电路的设计、仿真和验证。

七、状态方程描述法状态方程是描述时序逻辑电路状态转移关系的一种数学表达式。

它由当前状态、输入和下一个状态之间的逻辑关系组成,可以通过布尔代数等方法进行分析和求解。

八、流程图描述法流程图是描述时序逻辑电路工作过程的一种图形化表示方法。

它由各个状态和状态之间的转移组成,可以清晰地表示电路的运行流程。

九、状态机描述法状态机是描述时序逻辑电路工作过程的一种数学模型。

它由状态、输入、输出和状态转移函数组成,可以用来描述电路的功能和逻辑。

十、总结时序逻辑电路是数字电路中一种重要类型,它能够根据输入信号的时序关系产生特定的输出序列。

实验报告实验名称: [数字时钟实验]姓名:学号:指导教师:实验时间: [2013年6月15日]信息与通信工程学院DS1302数字时钟实验1.实验任务DS1302 是美国DALLAS公司推出的一种高性能、低功耗、带RAM的实时时钟电路,它可以对年、月、日、周日、时、分、秒进行计时,具有闰年补偿功能,工作电压为2.5V~5.5V。

采用三线接口与CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号或RAM数据。

DS1302内部有一个31×8的用于临时性存放数据的RAM寄存器。

DS1302是DS1202的升级产品,与DS1202兼容,但增加了主电源/后备电源双电源引脚,同时提供了对后备电源进行涓细电流充电的能力。

本实验运用DS1302实现对时间的计时,对日期的计数.利用数码管显示年、月、日、周、日、时、分、秒.能够复位,设置时间,日期.可以换键显示年月日和时分秒.学会运用FPGA实验箱用verilog语言进行一定的程序编程设计,满足一定的实验要求,掌握fpga的I/O口及并口的使用,能够处理一些简单的实验问题,学会简单的实验设计。

2.实验原理振荡器产生稳定的高频脉冲信号,作为数字钟的时间基准,然后经过分频器输出标准秒脉冲。

秒计数器满60后向分计数器进位,分计数器满60后向小时计数器进位,小时计数器按照“24翻1”规律计数,月都是12,所以不用特殊设置,日按平年计算,在润年的时候2月减一天即可。

年由于只显示后两位数字就可以,所以用两位显示可以满足。

计数满后各计数器清零,重新计数。

计数器的输出分别经译码器送数码管显示。

计时出现误差时,可以用校时电路校时、校分。

控制信号由1×5矩形键盘输入。

时基电路可以由石英晶体振荡电路构成,假设晶振频率1MHz,经过6次十分频就可以得到秒脉冲信号。

译码显示电路由八段译码器完成。

3.设计流程图形或HDL编辑Analysis & Synthesis(分析与综合)Filter(适配器)Assembler(编程文件汇编)编辑器Timing Analyzer(时序分析器)设计输入综合或编译适配器件下载仿真4.实验程序程序初始化module shuzishizhong(Clk0,SEG,DIG,rst,rst_n,sclk,data_io,button);input button;//用于选择在数码管上显示时间or日历的按键,按下为高电平input rst;//外部复位键input Clk0;//外部输入时钟50Mhzoutput [7:0] SEG,DIG;output rst_n;//ds1302的端口RTC nRSToutput sclk;//ds1302的输入时钟RTC CLKinout data_io;//ds1302的io端口RTC IOreg [12:0] CNT_R0;//用于将50Mhz时钟分频为10Khz的寄存器reg Clk_10KHz;//10Khz时钟reg [21:0] count;//用于按键消抖的计数器reg flag=0;//判断显示时间or日历的标识位,0显示时间,1显示日历reg [2:0] SCAN_R;reg [3:0] SEG_M [7:0];reg [7:0] SEG_DR;reg [7:0] SEG,DIG;wire [23:0] dat_o_TM;//来着ds1302_drive的存放时间的寄存器wire [31:0] dat_o_C;//来着ds1302_drive的存放日历的寄存器ds1302_drive(.clock(Clk0),.rst(rst),.rst_n(rst_n),.sclk(sclk),.data_io(data_io),.dat_o_T M(dat_o_TM),.dat_o_C(dat_o_C));驱动程序初始化module ds1302_drive(clock,rst,rst_n,sclk,data_io,dat_o_TM,dat_o_C);input rst;//外部复位按键重新设置数据input clock;//ds1302端口信号output rst_n,sclk;//ds1302的工作时钟inout data_io;//dat_o_TM信号接六个数码管,分别显示小时,分钟和秒//dat_o_C信号送到12864显示年,月,日和星期output[23:0] dat_o_TM;//读出的时间送出显示output[31:0]dat_o_C;//读出的日历送出显示reg rst_n;reg data;//data_io的缓存,reg clk_us;//状态机的时钟8us/periodreg clk_2us;//ds1302的工作时钟//data_io是双向口,开关link_write管理数据的出入//link_write为高时,允许输出,为低电平是高阻reg link_write;reg flag123;//重新设置日历标志位reg [4:0]step1;//WR_SET任务的状态reg [4:0]step2;//RD_T任务的状态reg [23:0] data_out_reg_time;//存放读出的时间reg [31:0] data_out_reg_calender;//存放读出的日历reg F;//读任务的标志reg FF;//写任务的标志reg [7:0]reg_CMD=0;//commandreg [7:0]reg_SEC=0;//秒reg [7:0]reg_MIN=8'h30;//分钟reg [7:0]reg_H=8'h09;//小时reg [7:0]reg_DAY=8'h03;//天reg [7:0]reg_MONTH=8'h06;//月reg [7:0]reg_X=8'h01;//星期reg [7:0]reg_YEAR=8'h13;//年reg [7:0]register1;//写操作的指令存器reg [7:0]register3;//读操作读进数据的寄存器reg [7:0]register4;//读操作的指令寄存器reg [3:0]state;//状态机//=============================================== //初始设置的状态参数//写状态parameterIDLE =4'b0000,WR_S =4'b0001,WR_Min =4'b0010,WR_H =4'b0011,WR_X =4'b0100,WR_D =4'b0101,WR_M =4'b0110,WR_Y =4'b0111;//=============================================== //=============================================== parameter //状态读RD_S =4'b1000,RD_Min =4'b1001,RD_H =4'b1010,RD_X =4'b1011,RD_D =4'b1100,RD_M =4'b1101,RD_Y =4'b1110,CLOSE_W =4'b1111;//=============================================== //WR_SET任务的参数parameterstep1_f0 =5'b00000,step1_f1 =5'b00001,step1_f2 =5'b00010,step1_f3 =5'b00011,step1_f4 =5'b00100,step1_f5 =5'b00101,step1_f6 =5'b00110,step1_f7 =5'b00111,step1_f8 =5'b01000,step1_f9 =5'b01001,step1_fa =5'b01010,step1_fb =5'b01011,step1_fc =5'b01100,step1_fd =5'b01101,step1_fe =5'b01110,step1_ff =5'b01111,step1_f10 =5'b10000;//=============================================== //RD_T任务的参数parameterstep2_f0 =5'b00000,step2_f1 =5'b00001,step2_f2 =5'b00010,step2_f3 =5'b00011,step2_f4 =5'b00100,step2_f5 =5'b00101,step2_f6 =5'b00110,step2_f7 =5'b00111,step2_f8 =5'b01000,step2_f9 =5'b01001,step2_fa =5'b01010,step2_fb =5'b01011,step2_fc =5'b01100,step2_fd =5'b01101,step2_fe =5'b01110,step2_ff =5'b01111,step2_f10=5'b10000;//++++++++++++++++++++++++++++++++++++++++++++++ //本模块的时钟20ns X 200 X 2=8us/period,reg[8:0]counter;5. 管脚分配6.实验结果如图所示实验版通过对左边3和4按键的使用可以实现年月日与时分秒的切换,图左上角的数码管用于显示时钟,对实验程序中如下部分的修改可以改变可以使数码管上的时钟改变用于设定时间。

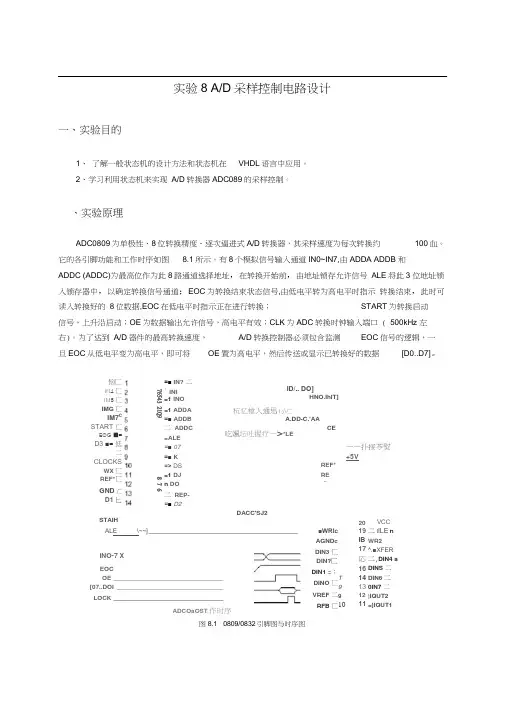

实验8 A/D 采样控制电路设计一、实验目的1、 了解一般状态机的设计方法和状态机在VHDL 语言中应用。

2、 学习利用状态机来实现 A/D 转换器ADC089的采样控制。

、实验原理ADC0809为单极性、8位转换精度、逐次逼进式A/D 转换器,其采样速度为每次转换约 100血。

它的各引脚功能和工作时序如图8.1所示。

有8个模拟信号输入通道IN0~IN7,由ADDA ADDB 和ADDC (ADDC)为最高位作为此8路通道选择地址,在转换开始前,由地址锁存允许信号 ALE 将此3 位地址锁入锁存器中,以确定转换信号通道;EOC 为转换结束状态信号,由低电平转为高电平时指示 转换结束,此时可读入转换好的 8位数据,EOC 在低电平时指示正在进行转换;START 为转换启动信号,上升沿启动;OE 为数据输出允许信号,高电平有效;CLK 为ADC 转换时钟输入端口 ( 500kHz 左右)。

为了达到 A/D 器件的最高转换速度, A/D 转换控制器必须包含监测EOC 信号的逻辑,一旦EOC 从低电平变为高电平,即可将OE 置为高电平,然后传送或显示已转换好的数据[D0..D7]。

DACC'SJ2图8.1 0809/0832引脚图与时序图恼匚IN4匚 IM5匚 IMG 匸 IM7CSTART 匸EOG ■=D3 ■= 低二CLOCKS WX 匚 REF*匚 GND 匚 D1匕76543 21Q9 Z22 2 2 222 18 7 6 111=■ IN? 二1INI =1 INO =1 ADDA =■ ADDB 二 ADDC =ALE =■ 07 =■ K => DS =1 DJ n DO二 REP-=■ D2ID/.. DO]HNO.IhlT]杭忆槍人通迅\小匚吃颯坛吐握疗一>*LEA.DD-C.'AACEREF* RE「亠——扑接苓熨+5VSTAIH ALE \~~] __________________________________________INO-7 XEOCOE _______________________________ [07..DOI ______________________________ LOCK _______________________________ADCOaOST 作时序■WRIc AGNDc DIN3 匚 DIN?匚 DIN1 =;DINO 匚 VREF 二 RFB 匚T9 910 2019 IB 17 応 16 14 13 12 11 VCC二I ILE n WR2 ^.■XFER 二,DIN4 a DINS 二 DIN6 二 0IN7 二|IQUT2 =]IQUT1.m f □ f .r ■ —j g ii\ T : e l o呂 B 口二二口口二二二LLI £匚(V |i|r^ FfQ LU P 比口CJ 口「匕口口口CJU工口门w□d d u m 口口U UHi 1 L H i图8.2 A/D采样控制器逻辑图图8.2是ADC0809 采样控制器ADC_STATE的逻辑图,其中D[7..O]为ADC0809转换结束后的输出数据(可接PI016〜PIO23); QQ[7..O]通过7段译码器在GW48-CK系统上的数码管8和数码管7上显示出来(可接PIO40〜PIO47); ST为自动转换时钟信号(接clockO)ALE和STA(即START)分别是通道选择地址锁存信号和转换启动信号(分别接PIO33和PIO34) ; EOC接PIO8 ; OE和ADDA分别为输出使能信号和通道选择低位地址信号(分别接PIO35和PIO32 );模拟信号由通道1(AIN1_VR1)进入0809的IN1。

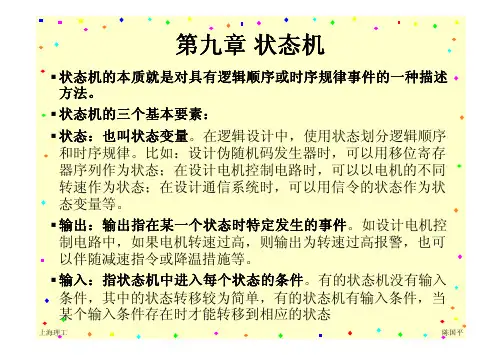

第九章状态机状态机的本质就是对具有逻辑顺序或时序规律事件的一种描述方法方法。

状态机的三个基本要素状态机的三个基本要素::状态状态::也叫状态变量。

在逻辑设计中,使用状态划分逻辑顺序和时序规律。

比如:设计伪随机码发生器时,可以用移位寄存器序列作为状态;在设计电机控制电路时,可以以电机的不同转速作为状态;在设计通信系统时,可以用信令的状态作为状态变量等。

输出输出::输出指在某一个状态时特定发生的事件。

如设计电机控制电路中,如果电机转速过高,则输出为转速过高报警,也可以伴随减速指令或降温措施等。

输入输入::指状态机中进入每个状态的条件。

有的状态机没有输入条件,其中的状态转移较为简单,有的状态机有输入条件,当某个输入条件存在时才能转移到相应的状态一、状态机状态机分为::状态机分为有限状态机((Finite State Machine,FSM)√ 有限状态机无限状态机((Infinite State Machine,ISM) 无限状态机易维护。

FSM设计要清晰易懂设计要清晰易懂、、易维护有限状态机的设计什么是有限状态机((FSM ) 什么是有限状态机FSM的种类和不同点设计举例什么是有限状态机?什么是有限状态机?-有限状态机是由寄存器组和组合逻辑构成的硬件时序电路;-其状态其状态((即由寄存器组的1和0的组合状态所构成的有限个状态有限个状态))只能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态;-究竟转向哪一状态不但取决于各个输入值究竟转向哪一状态不但取决于各个输入值,,还取决于当前状态于当前状态。

-状态状态机可用于产生在时钟跳变沿时刻开关的复杂的机可用于产生在时钟跳变沿时刻开关的复杂的控制逻辑控制逻辑,,是数字逻辑的控制核心是数字逻辑的控制核心。

Moore 状态机下一个状态= F(当前状态当前状态,,输入信号)输出信号= G(当前状态);下一状态的逻辑输出逻辑G状态寄存器输入输出当前状态激励信号时钟同步的状态机结构(Moore 状态机)F时钟信号clk clk输入Moore型状态机Mealy 状态机下一个状态= F(当前状态当前状态,,输入信号);输出信号= G(当前状态当前状态,,输入信号);下一状态输出逻辑输入时钟同步的状态机结构(Mealy 状态机)的逻辑FG状态寄存器时钟信号clkclk 输入输出当前状态激励信号Mealy型状态机带流水线输出的Mealy 状态机下一个状态= F(当前状态当前状态,,输入信号);输出信号= G(当前状态当前状态,,输入信号);输出输出输输出流带流水线输出的Mealy 状态机下一状态的逻辑F逻辑G 状态寄存器时钟信号clkclk 输入入当前状态激励信号水线寄存器clk 输入有限状态机的Verilog 描述定义模块名和输入输出端口定义模块名和输入输出端口;;定义输入定义输入、、输出变量或寄存器输出变量或寄存器;;定义时钟和复位信号定义时钟和复位信号;;定义状态变量和状态寄存器;定义状态变量和状态寄存器;用时钟沿触发的always 块表示状态转移过程块表示状态转移过程;;在复位信号有效时给状态寄存器赋初始值在复位信号有效时给状态寄存器赋初始值;;描述状态的转换过程描述状态的转换过程::符合条件符合条件,,从一个状态到另外一个状态一个状态,,否则留在原状态否则留在原状态;;验证状态转移的正确性验证状态转移的正确性,,必须完整和全面必须完整和全面。

数字电路设计中的时序逻辑与状态机设计时序逻辑与状态机设计是数字电路设计中的重要概念。

在数字电路中,时序逻辑指的是电路的输出是根据输入信号的时序关系而变化的,而状态机则是通过状态转换来实现特定功能的电路。

本文将详细介绍时序逻辑与状态机设计的原理、方法和实践经验。

一、时序逻辑设计的基础原理时序逻辑设计是指在数字电路中,通过引入时钟信号来控制电路的行为。

时钟信号可以被理解为一个周期性的信号,它将整个电路的工作分为不同的阶段。

在每个时钟周期内,时序逻辑根据输入信号的状态进行计算,并且在下一个时钟边沿产生输出信号。

时序逻辑设计的基础原理包括以下几个关键要点:1. 时钟信号:时钟信号的频率决定了电路的最大工作速度,而时钟边沿决定了电路的状态更新时机。

2. 触发器:触发器是实现时序逻辑的基本元件,它可以存储和传递信息,并在时钟边沿触发状态更新。

常见的触发器有D触发器、JK触发器和T触发器等。

3. 时序逻辑电路的设计方法:时序逻辑电路的设计方法包括状态转移图、状态转移方程和状态表等。

这些设计方法可以帮助设计师理清输入、输出和状态之间的关系,便于电路功能的实现。

二、状态机设计的基本概念与方法状态机是一种抽象的数学模型,常用于描述具有确定性行为的系统。

在数字电路设计中,状态机通常用于实现序列逻辑电路的控制部分,如计数器、序列检测器等。

状态机设计的基本概念与方法包括以下几个关键要点:1. 状态:状态是指系统在某个时刻的特定条件。

在状态机设计中,状态通常用离散的值来表示,比如二进制编码。

2. 状态转换:状态转换表示系统从一个状态切换到另一个状态的过程。

状态转换可以通过组合逻辑电路来实现,也可以通过时序逻辑电路实现。

3. 输出函数:输出函数定义了每个状态下的输出值。

它可以通过组合逻辑电路来实现,也可以通过状态寄存器的输出来实现。

4. 状态机设计流程:状态机设计的一般流程包括确定系统的输入、输出和状态集合,绘制状态转移图,推导状态转移方程,实现状态转移电路等。

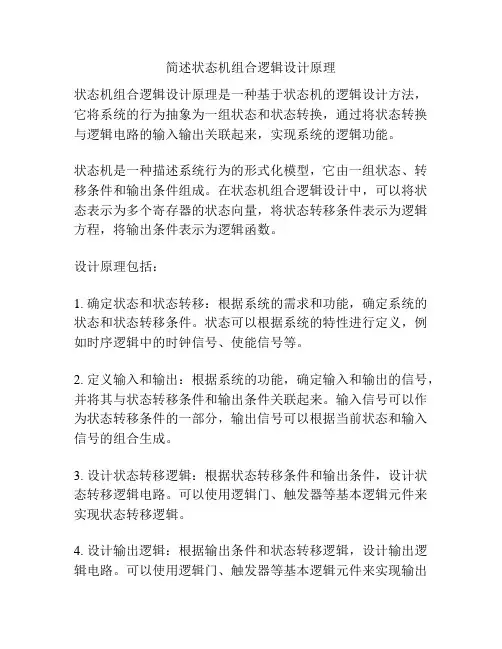

简述状态机组合逻辑设计原理

状态机组合逻辑设计原理是一种基于状态机的逻辑设计方法,它将系统的行为抽象为一组状态和状态转换,通过将状态转换与逻辑电路的输入输出关联起来,实现系统的逻辑功能。

状态机是一种描述系统行为的形式化模型,它由一组状态、转移条件和输出条件组成。

在状态机组合逻辑设计中,可以将状态表示为多个寄存器的状态向量,将状态转移条件表示为逻辑方程,将输出条件表示为逻辑函数。

设计原理包括:

1. 确定状态和状态转移:根据系统的需求和功能,确定系统的状态和状态转移条件。

状态可以根据系统的特性进行定义,例如时序逻辑中的时钟信号、使能信号等。

2. 定义输入和输出:根据系统的功能,确定输入和输出的信号,并将其与状态转移条件和输出条件关联起来。

输入信号可以作为状态转移条件的一部分,输出信号可以根据当前状态和输入信号的组合生成。

3. 设计状态转移逻辑:根据状态转移条件和输出条件,设计状态转移逻辑电路。

可以使用逻辑门、触发器等基本逻辑元件来实现状态转移逻辑。

4. 设计输出逻辑:根据输出条件和状态转移逻辑,设计输出逻辑电路。

可以使用逻辑门、触发器等基本逻辑元件来实现输出

逻辑。

5. 组合逻辑设计:将状态转移逻辑和输出逻辑组合到一起,形成完整的组合逻辑电路。

根据系统的需求和规模,可以进行优化和简化。

状态机组合逻辑设计原理的核心思想是通过状态和状态转移条件对系统行为进行建模,并将其与逻辑电路的输入输出关联起来。

通过组合逻辑设计,可以实现系统的功能需求,并优化电路的复杂度和性能。

常用的时序逻辑电路时序逻辑电路是数字电路中一类重要的电路,它根据输入信号的顺序和时序关系,产生对应的输出信号。

时序逻辑电路主要应用于计时、控制、存储等领域。

本文将介绍几种常用的时序逻辑电路。

一、触发器触发器是一种常见的时序逻辑电路,它具有两个稳态,即SET和RESET。

触发器接受输入信号,并根据输入信号的变化产生对应的输出。

触发器有很多种类型,常见的有SR触发器、D触发器、JK 触发器等。

触发器在存储、计数、控制等方面有广泛的应用。

二、时序计数器时序计数器是一种能按照一定顺序计数的电路,它根据时钟信号和控制信号进行计数。

时序计数器的输出通常是一个二进制数,用于驱动其他电路的工作。

时序计数器有很多种类型,包括二进制计数器、BCD计数器、进位计数器等。

时序计数器在计时、频率分频、序列生成等方面有广泛的应用。

三、时序比较器时序比较器是一种能够比较两个信号的大小关系的电路。

它接受两个输入信号,并根据输入信号的大小关系产生对应的输出信号。

时序比较器通常用于判断两个信号的相等性、大小关系等。

常见的时序比较器有两位比较器、四位比较器等。

四、时序多路选择器时序多路选择器是一种能够根据控制信号选择不同输入信号的电路。

它接受多个输入信号和一个控制信号,并根据控制信号的不同选择对应的输入信号作为输出。

时序多路选择器常用于多路数据选择、时序控制等方面。

五、时序移位寄存器时序移位寄存器是一种能够将数据按照一定规律进行移位的电路。

它接受输入信号和时钟信号,并根据时钟信号的变化将输入信号进行移位。

时序移位寄存器常用于数据存储、数据传输等方面。

常见的时序移位寄存器有移位寄存器、移位计数器等。

六、状态机状态机是一种能够根据输入信号和当前状态产生下一个状态的电路。

它由状态寄存器和状态转移逻辑电路组成,能够实现复杂的状态转移和控制。

状态机常用于序列识别、控制逻辑等方面。

以上是几种常用的时序逻辑电路,它们在数字电路设计中起着重要的作用。

有限状态机例题

以下是一个有限状态机的简单例子,该状态机模拟了一个计数器,可以记录输入的脉冲信号。

当没有输入信号(即输入为0)时,计数器处于空闲状态(IDLE)。

在每个时钟周期,如果输入信号为1,计数器就增加1。

当计数器达到最大值(例如,31)时,它就回到0并切换到另一个状态(称为START)。

在START状态下,如果输入信号为0,计数器就回到空闲状态。

这个有限状态机可以表示为一个状态图,其中每个状态是一个节点,每个转换是一个箭头。

箭头旁边写上触发转换的事件和目标状态。

例如,箭头从空闲状态指向开始状态,并写上“输入为1且计数器为31”。

通过这个状态图,可以清晰地看到计数器的行为。

例如,如果输入一个脉冲信号(即1),计数器会增加1;如果输入连续的两个脉冲信号,计数器就会从0计数到1,然后回到0并切换到START状态。

电路设计中的时序与时钟问题一、简介电路设计中的时序与时钟问题(100字)电路设计中的时序与时钟问题是指在数字电路设计中,为了保证各个电路模块之间的数据传输和操作的正确顺序,需要合理地设计时序逻辑电路和时钟电路。

时序与时钟问题是数字电路设计中的核心内容之一,对于提高电路的可靠性和性能至关重要。

二、时序与时钟问题的基本概念(200字)1. 时序:时序指的是在电路设计中,模块之间的操作和数据传输的时间顺序。

在时序电路设计中,需要确定输入信号的到达时间和输出信号的产生时间,以确保数据从一个模块传递到另一个模块时的正确顺序。

2. 时钟:时钟是指用来同步整个电路操作的信号。

时钟信号的频率和占空比对于电路的正确操作至关重要。

时钟信号的产生需要考虑时钟源的稳定性和可靠性。

三、时序与时钟问题的解决方法(400字)1. 时序约束分析:在电路设计过程中,需要进行时序约束分析。

时序约束分析是指根据电路设计的需求,分析各个模块之间的数据传输和操作的时间要求。

通过时序约束分析,可以确定各个模块之间的最大延迟和最小延迟,为后续的电路设计提供参考。

2. 时序逻辑电路设计:时序逻辑电路的设计是保证电路操作顺序正确的关键。

时序逻辑电路的设计需要根据时序约束分析的结果来确定输入和输出的时序关系。

在时序逻辑电路设计中,常用的方法包括状态机设计、寄存器和锁存器的设计等。

3. 时钟树设计:时钟树是指将时钟信号传输到整个电路的网络结构。

时钟树设计需要考虑时钟信号的传输延迟、时钟偏移和时钟功耗等因素。

合理的时钟树设计可以减小时钟偏移和时钟抖动,提高电路的可靠性和性能。

4. 时钟源的选择:选择合适的时钟源对于电路设计至关重要。

时钟源的选择需要考虑时钟信号的频率、占空比和稳定性等因素。

常见的时钟源包括晶体振荡器和时钟信号发生器等。

四、时序与时钟问题的重要性(200字)时序与时钟问题在数字电路设计中起着至关重要的作用。

合理地解决时序与时钟问题可以保证电路的正确操作和数据传输的顺序。

有限状态机和时序逻辑电路有限状态机和时序逻辑电路都是数字电路的重要部分,它们在数字系统中起着非常重要的作用。

这两者之间的关系是非常密切的,因为它们都是用于处理时序信号的。

虽然它们之间有很多相似之处,但是它们的实现目的、设计方法和应用场景却有很大的不同。

先来了解一下有限状态机。

有限状态机(Finite State Machine,简称FSM)是一种表示有限状态集的数学模型,它由一组状态、一组输入和一组输出构成。

有限状态机可以用来描述对象的行为,当输入变化时,状态机可以根据当前状态和输入的变化,自动地转移到一个新状态,并输出相应的结果。

FSM 的实现通常基于逻辑门电路或者触发器电路,设计中需要描述状态转移的规则和输出的逻辑关系。

因此,FSM 是一种用于控制系统的常见技术,例如自动机、解码器、数据整理器等等。

FSM 的设计和实现需要考虑状态转移的稳定性、时序性、输出控制和误差容忍度等因素。

时序逻辑电路则是一种数字电路,主要用于处理时序信号,它的输出状态是由输入信号和内部状态决定的,通常它包含了时钟信号以及各种逻辑门、触发器等方便组合的逻辑元件。

时序逻辑电路的设计和实现需要考虑时序稳定性、时钟速度、电源电压等因素。

时序逻辑电路具有小功耗、高速度、高性能等特点,因此它被广泛应用于高速通信领域、计算机内部控制电路和现代数字电子设备等领域。

在实际应用中,常常需要将有限状态机和时序逻辑电路结合起来使用,以满足控制和逻辑处理的需要。

例如,在计算机的中央处理器中,就采用了多级的逻辑电路和有限状态机实现了非常复杂的指令解释和控制功能。

总之,有限状态机和时序逻辑电路都是非常重要的数字电路部件,它们在我们的现代化社会中扮演着至关重要的角色。

无论是在通信、计算机还是其他应用领域中,它们都是支撑数字电路设计的重要基础。

[实验二]带校时功能时钟的设计与实现[实验目的]1.掌握51单片机的I/O输出特性和使用。

2.掌握LED数码管动态扫描的原理和设计方法,了解数码管的使用。

3.了解单片机中断系统原理及响应过程。

4.设计实现一个带校时功能的时钟。

[基本实验内容]1.阅读芯片数据手册,掌握I/O口有几种工作模式,如何控制I/O口的输出应用。

2.实现8位共阴极LED数码管的动态扫描显示的软件设计和硬件设计。

3.熟悉中断原理以及中断程序的编写,使用中断实现简易的时钟校准功能。

[硬件电路]硬件电路如下图所示,P0口为LED数码管的8段码输出,P2口作为控制时间显示的位选,P1.7和P1.6分别接2个按键,用于设置时钟的工作状态和校时时间的设置。

定义两个按键的功能为:K1用于设置转换时钟工作状态,K2用于设置校时时间(加1操作)。

时钟工作状态转换图如下图所示,具体每个状态的定义和功能如下:1.平时时钟工作在时钟显示状态,每按一下K1键,时钟依次进入校时时间的设置状态。

2.时钟由“时钟显示”进入“秒低位设置”时,校时时间的初始值为转换时刻的时钟值。

3.时钟由“时高位设置”回到(K1作用下)“时钟显示”时,时钟时间由校时时间代替,确认完成校时的设置。

4.当时钟处在时间设置的6个状态时,每按一次K2键,相应的位上的数值加1,并且要能根据具体所在的位置自动做相应的调整。

如秒高位的数字只能在0-5之间,而时高位的数值要限制在0、1、2(时个位数小于3时),或时高位的数值要限制在0、1(时个位数大于3时)。

5.当时钟处在时间设置的6个状态时,在20秒内无任何键按下,系统自动返回“时间显示”状态,设置的时间无效,不改变原时钟的计时时间。

6.在效时时间设置的操作过程中,时钟不停止其前时间的计时过程,除非当时钟由“时高位设置”回到(K1作用下)“时钟显示”时,时钟的计时时间由确认的校时时间代替而改变。

7.时钟显示亮度均匀、无闪烁。

当设置相应时间位时,该位应闪烁提示。

[软件设计]#include<reg52.h>unsigned char led_7[10]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f};unsigned char position[8]={0xfe,0xfd,0xfb,0xf7,0xef,0xdf};unsigned char time[3],time_set[3]; //时分秒计数和设置单元unsigned char dis_buff[6]; //显示缓冲区,存放要显示的段码值unsigned char time_counter,key_stime_counter; //时间计数单元unsigned char clock_state=6,return_time;bit point_on,set_on,time_1s_ok,key_stime_ok;void display(void) //数码管动态扫描函数{static unsigned char posit=0;P2=0xff; //P2位选P0=led_7[dis_buff[posit]]; //P0段选if(set_on&&(posit==clock_state)) P0=0x00; //校时闪烁if(point_on&&(posit==2||posit==4)) P0|=0x80; //秒闪烁P2=position[posit];if(++posit>=6) posit=0;}void T0_time() interrupt 1{display();TH0=(65536-2000)/256; //2ms定时TL0=(65536-2000)%256;if(++key_stime_counter>=5){key_stime_counter=0;key_stime_ok=1; //10ms到if(!(++time_counter%25)) set_on=!set_on; //设置校时闪烁标志if(time_counter>=100){time_counter=0;time_1s_ok=1; //1秒到}}}void time_to_disbuffer(unsigned char * time) //时钟时间送显示缓冲区函数{unsigned char i,j=0;for(i=0;i<=2;i++){dis_buff[j++]=time[i]%10;dis_buff[j++]=time[i]/10;}}#define key_input P1 //定义按键输入口#define key_mask 0xc0#define key_no 0#define key_k1 1#define key_k2 2#define key_state_0 0#define key_state_1 1#define key_state_2 2unsigned char read_key(void){static unsigned char key_state=0,key_old;unsigned char key_press,key_return=key_no;key_press=key_input&key_mask;switch(key_state){case key_state_0:if(key_press!=key_mask){key_old=key_press;key_state=key_state_1;}break;case key_state_1:if(key_press==key_old){if(key_press==0x40) key_return=key_k1;else if(key_press==0x80) key_return=key_k2;key_state=key_state_2;}elsekey_state=key_state_0;break;case key_state_2:if(key_press==key_mask) key_state=key_state_0;break;}return key_return;}void main(void){unsigned char key_temp,i;P2=0xff;TMOD=0x01;TH0=(65536-2000)/256;TL0=(65536-2000)%256;TR0=1;ET0=1;EA=1;time[2]=12; time[1]; time[0]=12; //设置初始时间12:12:12 while(1){if(time_1s_ok){time_1s_ok=0;point_on=~point_on;if(++time[0]>=60){time[0]=0;if(++time[1]>=60){time[1]=0;if(++time[2]>=24){time[2]=0;}}}if((++return_time>=20)&&(clock_state!=6)) clock_state=6;if(clock_state==6) time_to_disbuffer(time);}if(key_stime_ok){key_stime_ok=0;key_temp=read_key();if(key_temp){return_time=0;if(key_temp==key_k1) //K1键按下,状态转换{if(++clock_state>=7)clock_state=0;if(clock_state==0){for(i=0;i<=2;i++) time_set[i]=0;time_to_disbuffer(time_set);}if(clock_state==6){for(i=0;i<=2;i++) time[i]=time_set[i];time_to_disbuffer(time);}}if((clock_state!=6)&&(key_temp==key_k2)) //K2键按下if(clock_state%2) time_set[clock_state/2]+=10;else{if((time_set[clock_state/2]%10)==9)time_set[clock_state/2]-=9;elsetime_set[clock_state/2]+=1;}if(time_set[0]>=60) time_set[0]-=60;if(time_set[1]>=60) time_set[1]-=60;if(time_set[2]>=24) time_set[2]-=10;time_to_disbuffer(time_set);}}}}[实验总结]本实验参照老师书中第十一章程序,基本实现了时钟的校准功能,只用二个按键便可实现对时,分,秒位的校准。

通过本次实验学会了基于状态机的按键设置。

下一步在此基础上对时钟的功能进行扩展,如实时时钟,闹铃等。