verilog 交通灯

- 格式:pdf

- 大小:235.65 KB

- 文档页数:3

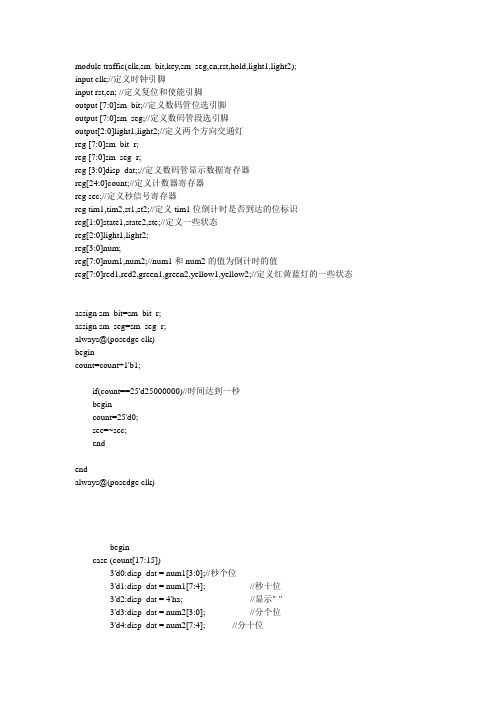

module traffic(clk,sm_bit,key,sm_seg,en,rst,hold,light1,light2);input clk;//定义时钟引脚input rst,en; //定义复位和使能引脚output [7:0]sm_bit;//定义数码管位选引脚output [7:0]sm_seg;//定义数码管段选引脚output[2:0]light1,light2;//定义两个方向交通灯reg [7:0]sm_bit_r;reg [7:0]sm_seg_r;reg [3:0]disp_dat;;//定义数码管显示数据寄存器reg[24:0]count;//定义计数器寄存器reg sec;//定义秒信号寄存器reg tim1,tim2,st1,st2;//定义tim1位倒计时是否到达的位标识reg[1:0]state1,state2,ste;//定义一些状态reg[2:0]light1,light2;reg[3:0]num;reg[7:0]num1,num2;//num1和num2的值为倒计时的值reg[7:0]red1,red2,green1,green2,yellow1,yellow2;//定义红黄蓝灯的一些状态assign sm_bit=sm_bit_r;assign sm_seg=sm_seg_r;always@(posedge clk)begincount=count+1'b1;if(count==25'd2*******)//时间达到一秒begincount=25'd0;sec=~sec;endendalways@(posedge clk)begincase (count[17:15])3'd0:disp_dat = num1[3:0];//秒个位3'd1:disp_dat = num1[7:4]; //秒十位3'd2:disp_dat = 4'ha; //显示"-"3'd3:disp_dat = num2[3:0]; //分个位3'd4:disp_dat = num2[7:4]; //分十位3'd5:disp_dat = 4'ha; //显示"-"endcasecase(count[17:15]) //选择数码管显示位3'd0:sm_bit_r = 8'b11111110; //选择第一个数码管显示3'd1:sm_bit_r = 8'b11111101; //选择第二个数码管显示3'd2:sm_bit_r = 8'b11111011; //选择第三个数码管显示3'd3:sm_bit_r = 8'b11110111; //选择第四个数码管显示3'd4:sm_bit_r = 8'b11101111; //选择第五个数码管显示3'd5:sm_bit_r = 8'b11011111; //选择第六个数码管显示3'd6:sm_bit_r = 8'b10111111; //选择第七个数码管显示3'd7:sm_bit_r = 8'b01111111; //选择第八个数码管显示endcaseendalways @(posedge clk)begincase(disp_dat)4'h0:sm_seg_r = 8'hc0; //显示04'h1:sm_seg_r = 8'hf9; //显示14'h2:sm_seg_r = 8'ha4; //显示24'h3:sm_seg_r = 8'hb0; //显示34'h4:sm_seg_r = 8'h99; //显示44'h5:sm_seg_r = 8'h92; //显示54'h6:sm_seg_r = 8'h82; //显示64'h7:sm_seg_r = 8'hf8; //显示74'h8:sm_seg_r = 8'h80; //显示84'h9:sm_seg_r = 8'h90; //显示94'ha:sm_seg_r = 8'hbf; //显示-default:sm_seg_r = 8'hff; //不显示endcaseendalways@(en)if(!en)begingreen1<=8'b00110101;red1<=8'b00100101;yellow1<=8'b00000101;green2<=8'b00100101;red2<=8'b00110101;yellow2<=8'b00000101;endalways@(posedge sec)//南北方向beginif(!rst)//复位模块beginlight1<=3'b001;num1<=green1;endif(!tim1)begintim1<=1;case(state1)2'b00:begin num1<=green1;light1<=3'b110;state1<=2'b01;end2'b01:begin num1<=yellow1;light1<=3'b101;state1<=2'b11;end2'b11:begin num1<=red1;light1<=3'b011;state1<=2'b10;end2'b10:begin num1<=yellow1;light1<=3'b101;state1<=2'b00;end//状态机使三个状态一直循环default:light1<=3'b011;endcaseendelsebeginif(num1==1)tim1<=0;else if(num1>0)if(num1[3:0]==0)beginnum1[3:0]<=4'b1001;//倒计时模块num1[7:4]<=num1[7:4]-1;endelse num1[3:0]<=num1[3:0]-1;endendalways@(posedge sec)//东西方向beginif(!rst)//复位模块beginlight2<=3'b100;num2<=red2;endif(!tim2)begintim2<=1;case(state2)2'b00:begin num2<=red2;light2<=3'b011;state2<=2'b01;end2'b01:begin num2<=yellow1;light2<=3'b101;state2<=2'b11;end2'b11:begin num2<=green2;light2<=3'b110;state2<=2'b10;end2'b10:begin num2<=yellow2;light2<=3'b101;state2<=2'b00;enddefault:light2<=3'b011;endcaseendelsebeginif(num2==1)tim2<=0;else if(num2>0)if(num2[3:0]==0)beginnum2[3:0]<=4'b1001;num2[7:4]<=num2[7:4]-1;endelse num2[3:0]<=num2[3:0]-1;endendendmodule。

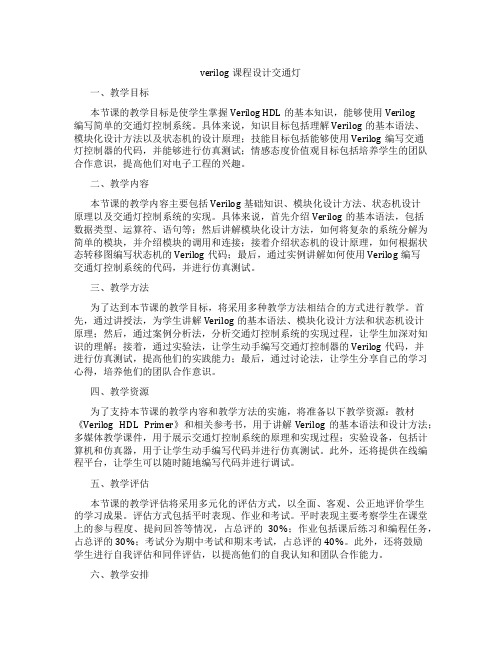

verilog课程设计交通灯一、教学目标本节课的教学目标是使学生掌握Verilog HDL的基本知识,能够使用Verilog编写简单的交通灯控制系统。

具体来说,知识目标包括理解Verilog的基本语法、模块化设计方法以及状态机的设计原理;技能目标包括能够使用Verilog编写交通灯控制器的代码,并能够进行仿真测试;情感态度价值观目标包括培养学生的团队合作意识,提高他们对电子工程的兴趣。

二、教学内容本节课的教学内容主要包括Verilog基础知识、模块化设计方法、状态机设计原理以及交通灯控制系统的实现。

具体来说,首先介绍Verilog的基本语法,包括数据类型、运算符、语句等;然后讲解模块化设计方法,如何将复杂的系统分解为简单的模块,并介绍模块的调用和连接;接着介绍状态机的设计原理,如何根据状态转移图编写状态机的Verilog代码;最后,通过实例讲解如何使用Verilog编写交通灯控制系统的代码,并进行仿真测试。

三、教学方法为了达到本节课的教学目标,将采用多种教学方法相结合的方式进行教学。

首先,通过讲授法,为学生讲解Verilog的基本语法、模块化设计方法和状态机设计原理;然后,通过案例分析法,分析交通灯控制系统的实现过程,让学生加深对知识的理解;接着,通过实验法,让学生动手编写交通灯控制器的Verilog代码,并进行仿真测试,提高他们的实践能力;最后,通过讨论法,让学生分享自己的学习心得,培养他们的团队合作意识。

四、教学资源为了支持本节课的教学内容和教学方法的实施,将准备以下教学资源:教材《Verilog HDL Primer》和相关参考书,用于讲解Verilog的基本语法和设计方法;多媒体教学课件,用于展示交通灯控制系统的原理和实现过程;实验设备,包括计算机和仿真器,用于让学生动手编写代码并进行仿真测试。

此外,还将提供在线编程平台,让学生可以随时随地编写代码并进行调试。

五、教学评估本节课的教学评估将采用多元化的评估方式,以全面、客观、公正地评价学生的学习成果。

Verilog实验报告---第四次交通灯班级:集电0802班姓名:张鹏学号: 04086057序号: 16一、规范(1)具有开关功能:当reset=0时红绿灯关闭,使主支干道六个灯全灭;(2)具有四个功能:当reset=1且func=2’b00时,主干道和支路正常计数;且func=2’b01时,支干道一直绿灯,主干道一直红灯;且func=2’b10时,主干道一直绿灯,支干道一直红灯;且func=2’b11时,主干道和支干道一直黄灯闪;(3)计数器频率:运行频率2Hz计数器;(4)信号灯种类:红、黄、绿;(5)信号灯计执行时间关系:主干道:绿灯常亮+绿灯闪+黄灯=支干道:红灯常亮;此设计中:主干道:绿灯常亮=57s,T绿灯闪=3s,T黄灯亮=3s支干道:绿灯常亮=15s,T绿灯闪=3s,T黄灯亮=3s(6)信号灯到计时功能:信号灯预置后,开始执行2Hz计数器;(7)信号灯跳转功能:当各信号灯计时至T时在下一个时钟信号上升沿到来时自动转为下一状态;(8)信号灯各状态跳转关系:绿-黄-红-绿;二、输入输出定义reset,clk, func[1:0] ,green[1:0],red[1:0],yellow[1:0]三、模块设计状态转移图:四、测试代码module frequency_divider_small(reset,clk,out); //重写一个小分频模块测试交通灯主模块功能input reset,clk;output out;reg [1:0] temp;reg out;always @ (posedge clk or negedge reset)if (!reset)temp<=2'b00;elsetemp<=(temp==2'b11)?2'b00:temp+2'b01;always @ (temp)out=(temp==2'b11);endmodulemodule test_traffic_light;reg reset,clk;reg [1:0] func;wire [1:0] green;wire [1:0] red;wire [1:0] yellow;traffic_light simulation(.reset(reset),.clk(clk),.func(func),.green(green),.red(red),.yellow(yellow));always #10 clk=~clk;initialbeginreset=0;clk=1;func=2'b00;#20 reset=1;#21000 func=2'b01;#10000 func=2'b10;#10000 func=2'b11;endendmodule波形:五、源代码module frequency_divider(reset,clk,out);//分频模块,把50MHz时钟分成半秒计时器input reset,clk;output out;reg [5:0] mol1,mol2;reg [6:0] mol3,mol4;reg out1,out2,out3,out;always @ (posedge clk or negedge reset)//把25000000分成40*40*125*125 if(!reset)mol1<=6'd0;elsemol1<=(mol1==6'd39)?6'd0:mol1+6'd1;always @ (posedge clk or negedge reset)if(!reset)mol2<=6'd0;else if(out1)mol2<=(mol2==6'd39)?6'd0:mol2+6'd1;always @ (posedge clk or negedge reset)if(!reset)mol3<=7'd0;else if(out2)mol3<=(mol3==7'd124)?7'd0:mol3+7'd1;always @ (posedge clk or negedge reset)if(!reset)mol4<=7'd0;else if(out3)mol4<=(mol4==7'd124)?7'd0:mol4+7'd1;always @ (mol1 or mol2 or mol3 or mol4)beginout1=(mol1==6'd39);out2=((mol2==6'd39)&&out1);out3=((mol3==7'd124)&&out2);out=((mol4==7'd124)&&out3);endendmodulemodule traffic_light(reset,clk,func,green,red,yellow);//交通灯主模块input reset,clk;input [1:0] func;output [1:0] green,red,yellow;reg [1:0] green,red,yellow;reg [2:0] state;reg [6:0] cnt;wire in;parameter greentime1=6'd57;//主干道绿灯时间parameter greentime0=6'd27;//支干道绿灯时间parameter yellowtime=3'd3;//黄灯时间,绿灯闪时间frequency_divider fenpin(.reset(reset),.clk(clk),.out(in));//调用分频模块always @ (posedge clk or negedge reset)if(!reset)begincnt<=7'd0;state<=3'd1;green<=2'b00;red<=2'b00;yellow<=2'b00;endelseif(in)//分频器结果当主模块始能if(func==2'b00)//选择不同功能控制开关if(cnt==7'd0)case(state)//选择不同状态3'd1:begincnt<=greentime1<<1;state<=3'd2;green<=2'b10;red<=2'b01;yellow<=2'b00;end3'd2:begincnt<=yellowtime<<1;state<=3'd3;end3'd3:begincnt<=yellowtime<<1;state<=3'd4;green<=2'b00;red<=2'b01;yellow<=2'b10;3'd4:begincnt<=greentime1<<1;state<=3'd5;green<=2'b01;red<=2'b10;yellow<=2'b00;end3'd5:begincnt<=yellowtime<<1;state<=3'd6;end3'd6:begincnt<=yellowtime<<1;state<=3'd1;green<=2'b00;red<=2'b10;yellow<=2'b01;endendcaseelsebegincnt<=cnt-7'd1;//倒计数,计数结束进入下一状态case(state)3'd3:green[1]<=cnt[0];//主干道绿灯闪3'd6:green[0]<=cnt[0];//支干道绿灯闪endcaseendelse if(func==2'b10)//主干道常绿,支干道常红begincnt<=0;state<=3'd1;green<=2'b10;red<=2'b01;yellow<=2'b00;endelse if(func==2'b01)//主干道常红,支干道常绿begincnt<=0;state<=3'd1;red<=2'b10;yellow<=2'b00;endelse if(func==2'b11)//主干道,支干道黄灯一直闪begincnt<=0;state<=3'd1;green<=2'b00;red<=2'b00;yellow[1]<=~yellow[1];yellow[0]<=~yellow[1];endendmodule。

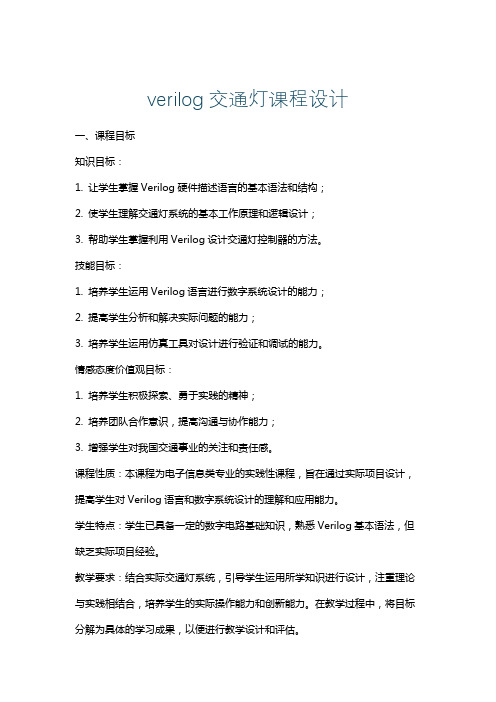

verilog交通灯课程设计一、课程目标知识目标:1. 让学生掌握Verilog硬件描述语言的基本语法和结构;2. 使学生理解交通灯系统的基本工作原理和逻辑设计;3. 帮助学生掌握利用Verilog设计交通灯控制器的方法。

技能目标:1. 培养学生运用Verilog语言进行数字系统设计的能力;2. 提高学生分析和解决实际问题的能力;3. 培养学生运用仿真工具对设计进行验证和调试的能力。

情感态度价值观目标:1. 培养学生积极探索、勇于实践的精神;2. 培养团队合作意识,提高沟通与协作能力;3. 增强学生对我国交通事业的关注和责任感。

课程性质:本课程为电子信息类专业的实践性课程,旨在通过实际项目设计,提高学生对Verilog语言和数字系统设计的理解和应用能力。

学生特点:学生已具备一定的数字电路基础知识,熟悉Verilog基本语法,但缺乏实际项目经验。

教学要求:结合实际交通灯系统,引导学生运用所学知识进行设计,注重理论与实践相结合,培养学生的实际操作能力和创新能力。

在教学过程中,将目标分解为具体的学习成果,以便进行教学设计和评估。

二、教学内容1. 交通灯系统原理介绍:分析交通灯系统的基本工作原理,包括信号灯的时序关系和控制逻辑。

- 相关教材章节:第二章 数字电路基础,第三节 时序逻辑电路。

2. Verilog基础知识回顾:复习Verilog的基本语法、数据类型、运算符和模块结构。

- 相关教材章节:第一章 Verilog语言概述,第二节 Verilog语言基础。

3. 交通灯控制器设计:指导学生使用Verilog设计一个简单的交通灯控制器。

- 相关教材章节:第三章 数字系统设计,第四节 状态机的设计与应用。

4. 仿真与验证:介绍仿真工具的使用,对设计的交通灯控制器进行功能验证和时序分析。

- 相关教材章节:第四章 仿真与验证,第一节 ModelSim仿真工具的使用。

5. 实践操作:组织学生进行实际操作,编写代码、配置仿真环境、运行仿真并调试程序。

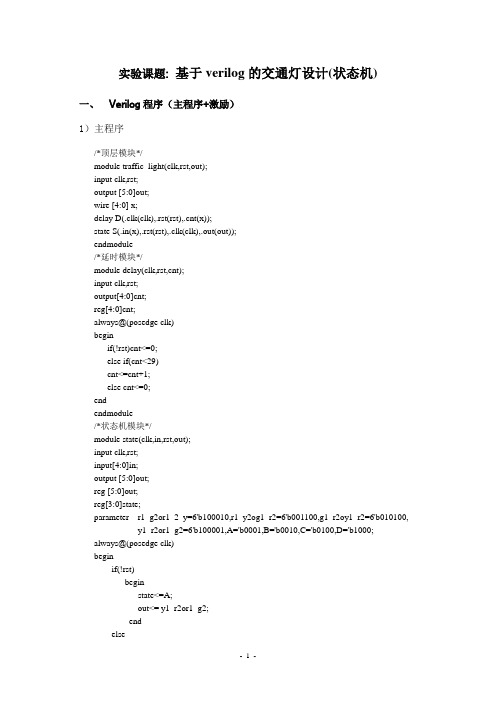

实验课题:基于verilog的交通灯设计(状态机)一、Verilog程序(主程序+激励)1)主程序/*顶层模块*/module traffic_light(clk,rst,out);input clk,rst;output [5:0]out;wire [4:0] x;delay D(.clk(clk),.rst(rst),.cnt(x));state S(.in(x),.rst(rst),.clk(clk),.out(out));endmodule/*延时模块*/module delay(clk,rst,cnt);input clk,rst;output[4:0]cnt;reg[4:0]cnt;always@(posedge clk)beginif(!rst)cnt<=0;else if(cnt<29)cnt<=cnt+1;else cnt<=0;endendmodule/*状态机模块*/module state(clk,in,rst,out);input clk,rst;input[4:0]in;output [5:0]out;reg [5:0]out;reg[3:0]state;parameter r1_g2or1_2_y=6'b100010,r1_y2og1_r2=6'b001100,g1_r2oy1_r2=6'b010100, y1_r2or1_g2=6'b100001,A='b0001,B='b0010,C='b0100,D='b1000;always@(posedge clk)beginif(!rst)beginstate<=A;out<= y1_r2or1_g2;endelsebegincase(state)A: beginif(in<25)state<=A;elsebeginstate<=B;out<=r1_g2or1_2_y;endendB: beginif(in>24)state<=B;elsebeginstate<=C;out<=r1_y2og1_r2;endendC: beginif(in<25)state<=C;elsebeginstate<=D;out<=g1_r2oy1_r2;endendD: beginif(in>24)state<=D;elsebeginstate<=A;out<=y1_r2or1_g2;endendendcaseendendendmodule2)激励module test;reg clk,rst;wire [5:0]out;traffic_light test(clk,rst,out);initialbeginclk='b1;forever #5 clk=~clk;endinitialbeginrst='b0;#10 rst='b1;#500 rst='b0;#10 rst='b1;endendmodule二、实验波形图截图三、波形分析输出out[5:0]分别对应:out[5]:主干道红灯out[4]:主干道黄灯out[3]:主干道绿灯out[2]:支干道红灯out[1]:支干道黄灯out[0]:支干道绿灯初始状态为:主干道红灯亮,支干道绿灯亮。

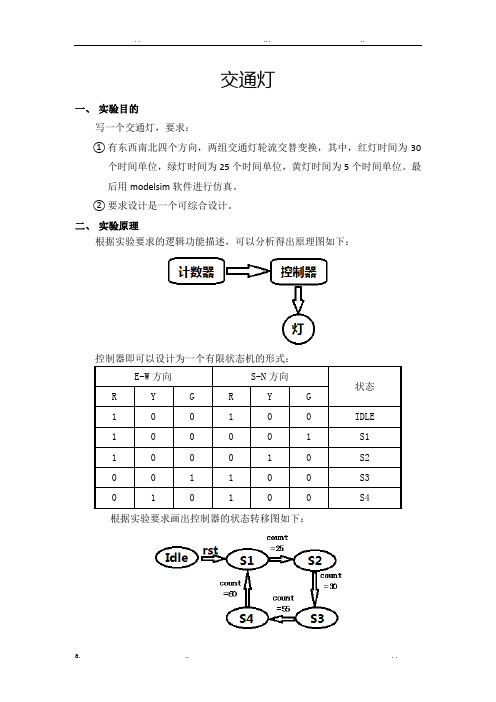

交通灯一、实验目的写一个交通灯,要求:①有东西南北四个方向,两组交通灯轮流交替变换,其中,红灯时间为30个时间单位,绿灯时间为25个时间单位,黄灯时间为5个时间单位。

最后用modelsim软件进行仿真。

②要求设计是一个可综合设计。

二、实验原理根据实验要求的逻辑功能描述,可以分析得出原理图如下:控制器即可以设计为一个有限状态机的形式:E-W方向S-N方向状态R Y G R Y G100100IDLE100001S1100010S2001100S3010100S4根据实验要求画出控制器的状态转移图如下:三、代码1、源代码(1)控制器模块module traffic_lights(clk,rst,count,ew,sn);input clk,rst;input[5:0] count;output[2:0] ew,sn;reg[2:0] ew,sn;reg[3:0] state;parameter Idle=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100; always @(posedge clk)if(!rst)beginstate<=Idle;endelsecasex(state)Idle: if(rst)beginstate<=s1;ends1: if(count=='d25)beginstate<=s2;ends2: if(count=='d30)beginstate<=s3;ends3: if(count=='d55)beginstate<=s4;ends4: if(count=='d60)beginstate<=s1;endendcasealways @(posedge clk)beginif(!rst)beginew<=3'b100;sn<=3'b100;endelsecasex(state)Idle: if(rst)beginew<=3'b100;sn<=3'b001;ends1: if(count=='d25)beginew<=3'b100;sn<=3'b010;ends2: if(count=='d30)beginew<=3'b001;sn<=3'b100;ends3: if(count=='d55)beginew<=3'b010;sn<=3'b100;ends4: if(count=='d60)beginew<=3'b100;sn<=3'b001;enddefault: state<=Idle;endcaseendendmodule(2)计数器模块module counter(en,clk,rst,out);output[5:0]out;input en,clk,rst;reg[5:0] out;always@(posedge clk or negedge rst)beginif(!rst)out<='d0;else if(!en&&out<'d60)out<=out+1;elseout<='d1;endendmodule(3)将控制器与计数器进行连接module traffic_lights_top(out,clk,rst,en,ew,sn); input clk,rst,en;output[2:0] ew,sn;output[5:0]out;wire[5:0] out;traffic_lights u1(.clk(clk),.rst(rst),.count(out),.ew(ew),.sn(sn));counter u2(.en(en),.clk(clk),.rst(rst),.out(out));endmodule2、激励`timescale 1ns/100ps module traffic_lights_tb;reg clk,rst,en;wire[2:0] ew,sn;wire[5:0]out;traffic_lights_top m(.clk(clk),.rst(rst),.en(en),.ew(ew),.sn(sn),.out(out));always#5 clk=~clk;initialen<=1;initialbeginclk<=1;en<=0;rst<=0;#5 rst<=1;endendmodule四、仿真波形(图一)(图二)五、波形说明波形图中,从上至下依次为:时钟信号clk、复位信号rst、计数器使能端en、东西方向上灯的状态ew、南北方向上灯的状态sn、计数器的输出out。

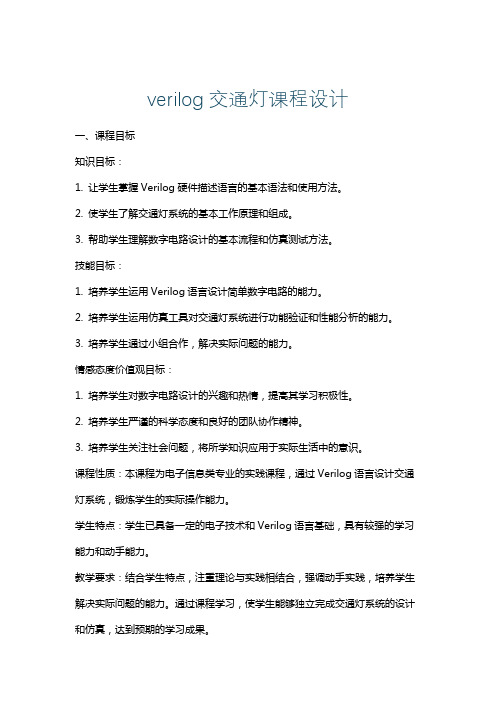

verilog交通灯课程设计一、课程目标知识目标:1. 让学生掌握Verilog硬件描述语言的基本语法和使用方法。

2. 使学生了解交通灯系统的基本工作原理和组成。

3. 帮助学生理解数字电路设计的基本流程和仿真测试方法。

技能目标:1. 培养学生运用Verilog语言设计简单数字电路的能力。

2. 培养学生运用仿真工具对交通灯系统进行功能验证和性能分析的能力。

3. 培养学生通过小组合作,解决实际问题的能力。

情感态度价值观目标:1. 培养学生对数字电路设计的兴趣和热情,提高其学习积极性。

2. 培养学生严谨的科学态度和良好的团队协作精神。

3. 培养学生关注社会问题,将所学知识应用于实际生活中的意识。

课程性质:本课程为电子信息类专业的实践课程,通过Verilog语言设计交通灯系统,锻炼学生的实际操作能力。

学生特点:学生已具备一定的电子技术和Verilog语言基础,具有较强的学习能力和动手能力。

教学要求:结合学生特点,注重理论与实践相结合,强调动手实践,培养学生解决实际问题的能力。

通过课程学习,使学生能够独立完成交通灯系统的设计和仿真,达到预期的学习成果。

1. Verilog基础知识回顾:包括数据类型、运算符、控制语句、模块和端口定义等,对应教材第1-3章内容。

2. 交通灯系统原理介绍:讲解交通灯系统的基本工作原理、状态转换和时序控制,对应教材第4章内容。

3. 交通灯系统设计:a. 设计要求:明确交通灯系统的功能要求和性能指标,对应教材第5章内容。

b. Verilog代码编写:指导学生运用Verilog语言编写交通灯控制模块,对应教材第6章内容。

c. 仿真测试:使用仿真工具对设计进行功能验证和性能分析,对应教材第7章内容。

4. 实践操作:a. 硬件描述语言实践:指导学生进行Verilog代码编写和调试,对应教材第8章内容。

b. 交通灯系统综合实践:组织学生进行交通灯系统设计和仿真,对应教材第9章内容。

5. 课程总结与评价:对学生的学习成果进行评价,总结课程收获和不足,对应教材第10章内容。

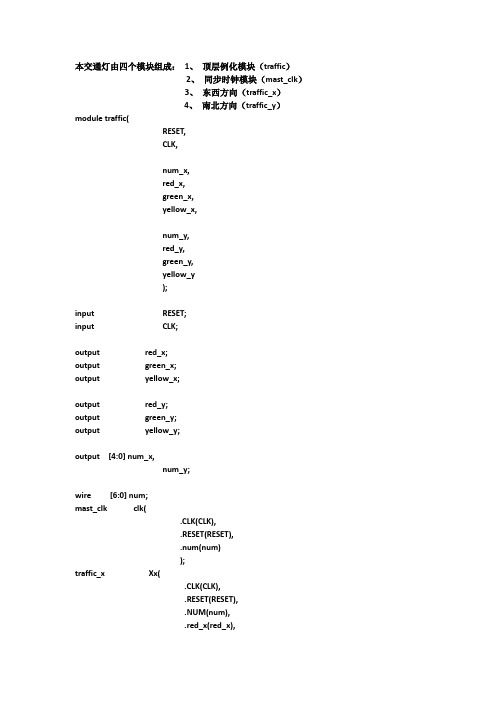

本交通灯由四个模块组成:1、顶层例化模块(traffic)2、同步时钟模块(mast_clk)3、东西方向(traffic_x)4、南北方向(traffic_y)module traffic(RESET,CLK,num_x,red_x,green_x,yellow_x,num_y,red_y,green_y,yellow_y);input RESET;input CLK;output red_x;output green_x;output yellow_x;output red_y;output green_y;output yellow_y;output [4:0] num_x,num_y;wire [6:0] num;mast_clk clk(.CLK(CLK),.RESET(RESET),.num(num));traffic_x Xx(.CLK(CLK),.RESET(RESET),.NUM(num),.red_x(red_x),.green_x(green_x),.yellow_x(yellow_x),.num_x(num_x));traffic_y Yy(.CLK(CLK),.RESET(RESET),.NUM(num),.red_y(red_y),.green_y(green_y),.yellow_y(yellow_y),.num_y(num_y));endmodulemodule mast_clk(CLK,RESET,num);input CLK;input RESET;output reg [6:0] num;always @(posedge CLK,negedge RESET)beginif(!RESET)num<=0;else if(num==59)num<=0;else num<=num+1'b1;endendmodulemodule traffic_x(CLK,RESET,NUM,red_x,green_x,yellow_x,num_x);input CLK;input RESET;input [6:0] NUM;output reg red_x;output reg green_x;output reg yellow_x;output [6:0] num_x;reg [6:0] num_x;parameter [2:0] red =3'b001,green =3'b010,yellow=3'b100;reg [2:0] state,next_state;always @(posedge CLK,negedge RESET)beginif(!RESET) state<=red;else state<=next_state;endalways @(NUM)begincase(state)red:beginif(NUM>'d29) begin next_state<=green;red_x<=0;green_x<=1;yellow_x<=0;num_x<=7'd54-NUM;endelse beginnext_state<=red;red_x<=1;green_x<=0;yellow_x<=0;num_x<=7'd29-NUM;endendgreen:beginif(NUM>'d54) begin next_state<=yellow;red_x<=0;green_x<=0;yellow_x<=1;num_x<=7'd59-NUM; endelse beginnext_state<=green;red_x<=0;green_x<=1;yellow_x<=0;num_x<=7'd54-NUM;endendyellow:beginif(NUM>'d58) begin next_state<=red; num_x=7'b0;endelse beginnext_state<=yellow;red_x<=0;green_x<=0;yellow_x<=1;num_x<=7'd59-NUM;endenddefault:next_state<=red;endcaseendendmodulemodule traffic_y(CLK,RESET,NUM,red_y,green_y,yellow_y,num_y);input CLK;input RESET;input [6:0] NUM;output reg red_y;output reg green_y;output reg yellow_y;output [6:0] num_y;reg [6:0] num_y;parameter [2:0] red =3'b001,green =3'b010,yellow=3'b100;reg [2:0] state,next_state;always @(posedge CLK,negedge RESET)beginif(!RESET) state<=green;else state<=next_state;endalways @(NUM)begincase(state)green:beginif(NUM>7'd29) begin next_state<=yellow;red_y<=1'b0;green_y<=1'b0;yellow_y<=1'b1;num_y<=7'd34-NUM;endelse beginnext_state<=green;red_y<=1'b0;green_y<=1'b1;yellow_y<=1'b0;num_y<=7'd29-NUM;endendyellow:beginif(NUM>7'd34) begin next_state<=red;red_y<=1'b1;green_y<=1'b0;yellow_y<=1'b0;num_y<=7'd59-NUM;endelse beginnext_state<=yellow;red_y<=1'b0;green_y<=1'b0;yellow_y<=1'b1;num_y<=7'd34-NUM;endendred:beginif(NUM>7'd58) beginnext_state<=green;num_y<=7'd0;endelse beginnext_state<=red;red_y<=1'b1;green_y<=1'b0;yellow_y<=1'b0;num_y<=7'd59-NUM;endenddefault:next_state<=green;endcaseendendmodule。

课程论文论文题目基于DE2的交通灯设计完成时间课程名称 Verilog语言设计任课老师专业年级1.交通信号控制器设计要求与思路1.1设计背景FPGA是一种用户根据各自需要而自行构造逻辑功能的数字集成电路,其种类很多,内部结构也不同,但共同的特点是体积小、使用方便。

本文介绍了用VerilogHDL语言设计交通灯控制器的方法,并在QuartusII系统对FPGA芯片进行编译下载,由于生成的是集成化的数字电路,没有传统设计中的接线问题,所以故障率低、可靠性高,而且体积非常小。

本文通过EDA设计,利用VerilogHDL语言模拟仿真交通灯控制电路。

1.2设计要求根据交通灯控制器要实现的功能,考虑用两个并行执行的always语句来分别控制A方向和B方向的3盏灯。

这两个always语句使用同一个时钟信号,以进行同步,也就是说,两个进程的敏感信号是同一个。

每个always语句控制一个方向的3种灯按如下顺序点亮,并往复循环:绿灯----黄灯----红灯,每种灯亮的时间采用一个减法计数器进行计数,计数器用同步预置数法设计,这样只需改变预置数据,就能改变计数器的模,因此每个方向只要一个计数器进行预置数就可以。

为便于显示灯亮的时间,计数器的输出均采用BCD码,显示由4个数码管来完成,A方向和B方向各用两个数码管。

设定A方向红灯、黄灯、绿灯亮的时间分别为:35s、5s、35s,B方向的红灯、黄灯、绿灯亮的时间分别为:35s、5s、35s。

假如要改变这些时间,只需要改变计数器的预置数即可。

1.3设计思路两个方向各种灯亮的时间能够进行设置和修改,此外,假设B方向是主干道,车流量大,因此B方向通行的时间应该比A方向长。

交通灯控制器的状态转换表见下表。

表中,1表示灯亮,0表示灯不亮。

A方向和B方向的红黄绿分别用R1、Y1、G1、R2、Y2、G2来表示。

交通灯控制器状态转换表从状态表中可以看出,每个方向3盏灯依次按如下顺序点亮,并不断循环:绿灯----黄灯----红灯,并且每个方向红灯亮的时间应该与另一个方向绿灯、黄灯亮的时间相等。

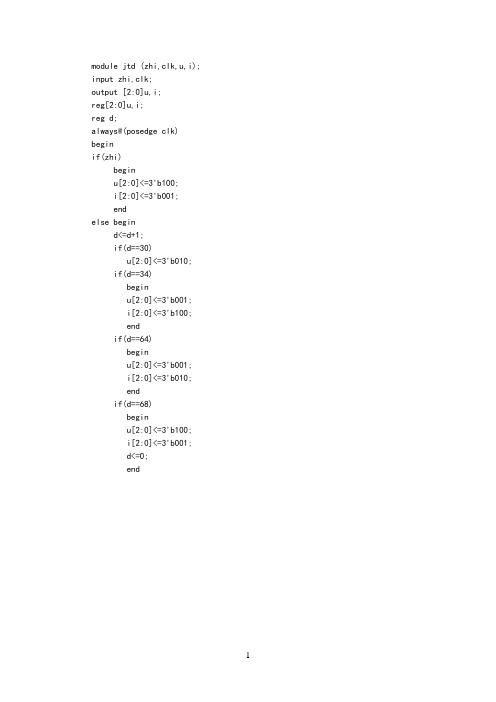

module jtd (zhi,clk,u,i); input zhi,clk;output [2:0]u,i;reg[2:0]u,i;reg d;always@(posedge clk) beginif(zhi)beginu[2:0]<=3'b100;i[2:0]<=3'b001;endelse begind<=d+1;if(d==30)u[2:0]<=3'b010; if(d==34)beginu[2:0]<=3'b001; i[2:0]<=3'b100; endif(d==64)beginu[2:0]<=3'b001; i[2:0]<=3'b010; endif(d==68)beginu[2:0]<=3'b100; i[2:0]<=3'b001; d<=0;endmodule jtd(zhi,u,i,clk,rst);input zhi,clk,rst;output [2:0]u,i;reg [2:0]u,i;reg[4:0]state;reg [5:0]d;initial d=0;parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s0;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;if(zhi)begin state<=s0;end else state<=s4;ends0:begin u[2:0]<=3'b100;i[2:0]<=3'b001;d=d+1;if(d==30)begin state<=s1;d=0;end else state<=s0;ends1:begin u[2:0]<=3'b010;i[2:0]<=3'b001;d=d+1;if(d==4)begin state<=s2;d=0;end else state<=s1;ends2:begin u[2:0]<=3'b001;i[2:0]<=3'b100;d=d+1;if(d==30) begin state<=s3;d=0;end else state<=s2;ends3:begin u[2:0]<=3'b001;i[2:0]<=3'b010;d=d+1;if(d==4)begin state<=s4;d=0;end else state<=s3;enddefault: state<=s4;endcaseendendendmodule黄灯闪module jtde(zhi,u,i,clk,rst);input zhi,clk,rst;output [2:0]u,i;reg [2:0]u,i;reg[4:0]state;reg [6:0]d;initial d=0;parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s4;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;if(zhi)begin state<=s0;end else state<=s4;ends0:begin u[2:0]<=3'b100;i[2:0]<=3'b001;d=d+1;if(d==30)begin state<=s1;d=0;end else state<=s0;ends1:begin d=d+1;if(d==1)begin u[2:0]<=3'b000;i[2:0]<=3'b001;state<=s1;endif(d==2)begin u[2:0]<=3'b010;i[2:0]<=3'b001;state<=s1;endif(d==3)begin u[2:0]<=3'b000;i[2:0]<=3'b001;state<=s1;endif(d==4)begin u[2:0]<=3'b010;i[2:0]<=3'b001;state<=s2;d=0;endends2:begin u[2:0]<=3'b001;i[2:0]<=3'b100;d=d+1;if(d==30) begin state<=s3;d=0;end else state<=s2;ends3:begin d=d+1;if(d==1)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==2)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s3;endif(d==3)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==4)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s4;d=0;endenddefault: state<=s4;endcaseendend黄灯闪且倒计时module mnb(zhi,u,i,clk,rst,ugx,usx,igx,isx);input zhi,clk,rst;output [2:0]u,i;output [3:0]ugx,usx,igx,isx;reg [2:0]u,i;reg[4:0]state;reg [4:0]ugx,usx,igx,isx;reg [6:0]d,e,f;initialbegin d<=0;e<=30;f<=34;endparameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s4;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:beginu[2:0]<=3'b100;i[2:0]<=3'b001;ugx<=0;usx<=0;igx<=0;isx<=0;if(zhi)beginstate<=s0;d<=0;e<=30;f<=35;end else state<=s4;ends0:beginu[2:0]<=3'b100;i[2:0]<=3'b001;ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e< =e-1;f<=f-1;if(d==30)begin state<=s1;d<=0;e<=4;f<=4;end else state<=s0;ends1:begin ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;e<=e-1;f<=f-1;if(d==0)begin u[2:0]<=3'b010;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==1)begin u[2:0]<=3'b000;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==2)begin u[2:0]<=3'b010;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==3)beginu[2:0]<=3'b000;i[2:0]<=3'b001;state<=s2;d<=0;e<=35;f<=30;endends2:beginu[2:0]<=3'b001;i[2:0]<=3'b100;ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e< =e-1;f<=f-1;if(d==30) begin state<=s3;d<=0;e<=4;f<=4;end else state<=s2;ends3:begin ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e<=e-1;f<=f-1;if(d==1)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==2)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s3;endif(d==3)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==4)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s4;d<=0;endenddefault: state<=s4;endcaseendendendmodule黄灯闪。

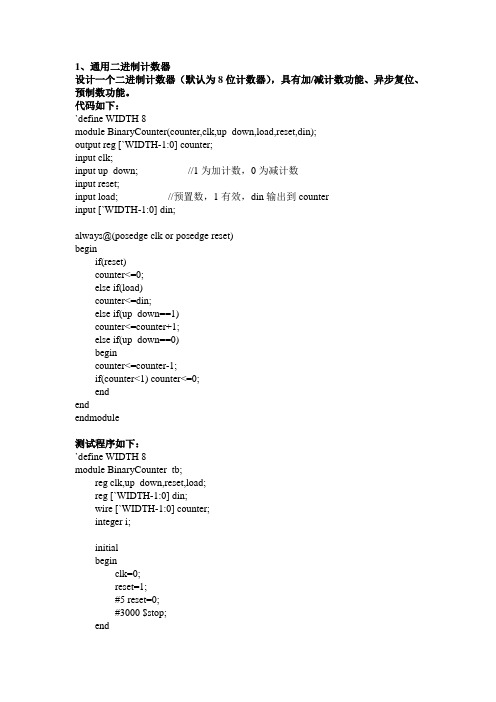

1、通用二进制计数器设计一个二进制计数器(默认为8位计数器),具有加/减计数功能、异步复位、预制数功能。

代码如下:`define WIDTH 8module BinaryCounter(counter,clk,up_down,load,reset,din);output reg [`WIDTH-1:0] counter;input clk;input up_down; //1为加计数,0为减计数input reset;input load; //预置数,1有效,din输出到counterinput [`WIDTH-1:0] din;always@(posedge clk or posedge reset)beginif(reset)counter<=0;else if(load)counter<=din;else if(up_down==1)counter<=counter+1;else if(up_down==0)begincounter<=counter-1;if(counter<1) counter<=0;endendendmodule测试程序如下:`define WIDTH 8module BinaryCounter_tb;reg clk,up_down,reset,load;reg [`WIDTH-1:0] din;wire [`WIDTH-1:0] counter;integer i;initialbeginclk=0;reset=1;#5 reset=0;#3000 $stop;endalways #5 clk=~clk;/*always@(posedge clk)beginup_down={$random}%2;load={$random}%2;din={$random}%256;end*/initialbegin#5;for(i=0;i<256;i=i+3)begindin=i;#10;endendinitialbeginup_down=1;load=1;#20 load=0;#30 load=1;#30 load=0;endalways #200 up_down=~up_down;BinaryCounter bcounter(.counter(counter),.clk(clk),.up_down(up_down),.load(load),.reset(reset),.din(din));endmodule波形图如下:图1 二进制计数器波形图图2 二进制计数器波形图从图像可看出,20s-50s为加计数,50s-80s时load=1,执行置数功能,80s-200s 时up_down=1,为加计数,200s-280s时up_down=0,为减计数。

module jtd (zhi,clk,u,i); input zhi,clk;output [2:0]u,i;reg[2:0]u,i;reg d;always(posedge clk)beginif(zhi)beginu[2:0]<=3'b100;i[2:0]<=3'b001;endelse begind<=d+1;if(d==30)u[2:0]<=3'b010; if(d==34)beginu[2:0]<=3'b001; i[2:0]<=3'b100; endif(d==64)beginu[2:0]<=3'b001; i[2:0]<=3'b010; endif(d==68)beginu[2:0]<=3'b100; i[2:0]<=3'b001; d<=0;endmodule jtd(zhi,u,i,clk,rst);input zhi,clk,rst;output [2:0]u,i;reg [2:0]u,i;reg[4:0]state;reg [5:0]d;initial d=0;parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always(posedge clk)beginif(!rst) begin state<=s0;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;if(zhi)begin state<=s0;end else state<=s4;ends0:begin u[2:0]<=3'b100;i[2:0]<=3'b001;d=d+1;if(d==30)begin state<=s1;d=0;end else state<=s0;ends1:begin u[2:0]<=3'b010;i[2:0]<=3'b001;d=d+1;if(d==4)begin state<=s2;d=0;end else state<=s1;ends2:begin u[2:0]<=3'b001;i[2:0]<=3'b100;d=d+1;if(d==30) begin state<=s3;d=0;end else state<=s2;ends3:begin u[2:0]<=3'b001;i[2:0]<=3'b010;d=d+1;if(d==4)begin state<=s4;d=0;end else state<=s3;enddefault: state<=s4;endcaseendendendmodule黄灯闪module jtde(zhi,u,i,clk,rst);input zhi,clk,rst;output [2:0]u,i;reg [2:0]u,i;reg[4:0]state;reg [6:0]d;initial d=0;parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always(posedge clk)beginif(!rst) begin state<=s4;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;if(zhi)begin state<=s0;end else state<=s4;ends0:begin u[2:0]<=3'b100;i[2:0]<=3'b001;d=d+1;if(d==30)begin state<=s1;d=0;end else state<=s0;ends1:begin d=d+1;if(d==1)begin u[2:0]<=3'b000;i[2:0]<=3'b001;state<=s1;endif(d==2)begin u[2:0]<=3'b010;i[2:0]<=3'b001;state<=s1;endif(d==3)begin u[2:0]<=3'b000;i[2:0]<=3'b001;state<=s1;endif(d==4)begin u[2:0]<=3'b010;i[2:0]<=3'b001;state<=s2;d=0;endends2:begin u[2:0]<=3'b001;i[2:0]<=3'b100;d=d+1;if(d==30) begin state<=s3;d=0;end else state<=s2;ends3:begin d=d+1;if(d==1)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==2)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s3;endif(d==3)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==4)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s4;d=0;endenddefault: state<=s4;endcaseendend黄灯闪且倒计时module mnb(zhi,u,i,clk,rst,ugx,usx,igx,isx);input zhi,clk,rst;output [2:0]u,i;output [3:0]ugx,usx,igx,isx;reg [2:0]u,i;reg[4:0]state;reg [4:0]ugx,usx,igx,isx;reg [6:0]d,e,f;initialbegin d<=0;e<=30;f<=34;endparameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always(posedge clk)beginif(!rst) begin state<=s4;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;ugx<=0;usx<=0;igx<=0;isx<=0;if(zhi)begin state<=s0;d<=0;e<=30;f<=35;end else state<=s4;ends0:beginu[2:0]<=3'b100;i[2:0]<=3'b001;ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e< =e-1;f<=f-1;if(d==30)begin state<=s1;d<=0;e<=4;f<=4;end else state<=s0;ends1:begin ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;e<=e-1;f<=f-1;if(d==0)begin u[2:0]<=3'b010;i[2:0]<=3'b001;d<=d+1;state<=s1;endif(d==1)begin u[2:0]<=3'b000;i[2:0]<=3'b001;d<=d+1;state<=s1;endif(d==2)begin u[2:0]<=3'b010;i[2:0]<=3'b001;d<=d+1;state<=s1;endif(d==3)beginu[2:0]<=3'b000;i[2:0]<=3'b001;state<=s2;d<=0;e<=35;f<=30;endends2:beginu[2:0]<=3'b001;i[2:0]<=3'b100;ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e<=e-1;f<=f-1;if(d==30) begin state<=s3;d<=0;e<=4;f<=4;end else state<=s2; ends3:begin ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e<=e-1;f<=f-1; if(d==1)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==2)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s3;endif(d==3)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==4)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s4;d<=0;endenddefault: state<=s4;endcaseendendendmodule黄灯闪。

module traffic(en,clk,rst,num1,num2,light1,light2,out1,out2,out3,out4,in1,in2); input en,clk,rst,in1,in2; //en为使能端。

in1,in2控制绿灯和红灯亮时间output [7:0] num1,num2;output [2:0] light1,light2;output [6:0]out1,out2,out3,out4;//输出四个数码管reg [6:0]out1,out2,out3,out4;reg tim1,tim2;reg [1:0]state1,state2;reg [2:0]light1,light2;reg [7:0] num1,num2;reg [7:0] red1,red2,green1,green2,yellow1,yellow2;parameter s0=2'b00,s1=2'b01,s2=2'b10,s3=2'b11;//四个循环状态reg[25:0]count;reg div;always @(en )if(en)begin //设置计数初值if (!in1)begingreen1<=8'b00110000;red2<=8'b00110000;end//30H,即30秒elsebegingreen1<=8'b01100000;red2<=8'b01100000;end//60sif (!in2)beginred1<=8'b00100000;green2<=8'b00100000;end//20selsebegin red1<=8'b01000000;green2<=8'b01000000;end//40syellow1<=8'b00000101; yellow2<=8'b00000101;//05sendalways@(posedge clk)//分频if (count==25000000) begin div<=1;count<=count+1;endelse if(count==50000000)begin div<=0;count<=0;endelse count<=count+1;always @(posedge div)beginif(rst) //复位情况控制beginlight1<=3'b001;num1<=green1;endelse if(en)begin //使能有效开始控制计数if(!tim1) //开始控制begin //主干道交通灯点亮控制tim1<=1;case(state1)//状态机s0:begin num1<=green1;light1<=3'b001;state1<=s1;end s1:begin num1<=yellow1;light1<=3'b010;state1<=s2;end s2:begin num1<=red1;light1<=3'b100;state1<=s3;ends3:begin num1<=yellow1;light1<=3'b010;state1<=s0;end default:light1<=3'b100;endcaseendelsebegin //倒数计时if(num1>0)if(num1[3:0]==0)beginnum1[3:0]<=4'b1001;num1[7:4]<=num1[7:4]-1;//十位减1endelse num1[3:0]<=num1[3:0]-1; //个位减1 if(num1==1) tim1<=0;endendelsebeginlight1<=3'b010;num1=2'b00;tim1<=0;endendalways @(posedge div ) //从干道beginif(rst) //复位情况控制beginlight2<=3'b100;num2<=red2;endelse if(en)beginif(!tim2)begintim2<=1;case(state1)s0:begin num2<=red2;light2<=3'b100;state2<=s1;ends1:begin num2<=yellow1;light2<=3'b010;state2<=s2;ends2:begin num2<=green2;light2<=3'b001;state2<=s3;ends3:begin num2<=yellow2;light2<=3'b010;state2<=s0;enddefault:light2<=3'b100;endcaseendelsebegin //倒数计时if(num2>0)if(num2[3:0]==0)beginnum2[3:0]<=4'b1001;num2[7:4]<=num2[7:4]-1;endelse num2[3:0]<=num2[3:0]-1;if(num2==1) tim2<=0;endendelsebegintim2<=0;state2<=2'b00;light2<=3'b010;endendalways @(posedge clk)begin //数码管译码显示case(num1[3:0])4'b0000: out1<=~7'b0111111; //0 ,3F4'b0001: out1<=~7'b0000110; //1 ,064'b0010: out1<=~7'b1011011; //2 ,5B4'b0011: out1<=~7'b1001111; //3 ,4F4'b0100: out1<=~7'b1100110; //4 ,664'b0101: out1<=~7'b1101101; //5 ,6D4'b0110: out1<=~7'b1111101; //6 ,7D 4'b0111: out1<=~7'b0000111; //7 ,07 4'b1000: out1<=~7'b1111111; //8, 7F 4'b1001: out1<=~7'b1101111; //9, 6F default: out1<=~7'b0111111; //0 ,3F endcaseendalways @(posedge clk)begin //数码管译码显示case(num1[7:4])4'b0000: out2<=~7'b0111111; //0 ,3F 4'b0001: out2<=~7'b0000110; //1 ,06 4'b0010: out2<=~7'b1011011; //2 ,5B 4'b0011: out2<=~7'b1001111; //3 ,4F 4'b0100: out2<=~7'b1100110; //4 ,66 4'b0101: out2<=~7'b1101101; //5 ,6D 4'b0110: out2<=~7'b1111101; //6 ,7D 4'b0111: out2<=~7'b0000111; //7 ,07 4'b1000: out2<=~7'b1111111; //8, 7F 4'b1001: out2<=~7'b1101111; //9, 6F default: out2<=~7'b0111111; //0 ,3F endcaseendalways @(posedge clk)begin //数码管译码显示case(num2[3:0])4'b0000: out3<=~7'b0111111; //0 ,3F 4'b0001: out3<=~7'b0000110; //1 ,06 4'b0010: out3<=~7'b1011011; //2 ,5B 4'b0011: out3<=~7'b1001111; //3 ,4F 4'b0100: out3<=~7'b1100110; //4 ,66 4'b0101: out3<=~7'b1101101; //5 ,6D 4'b0110: out3<=~7'b1111101; //6 ,7D 4'b0111: out3<=~7'b0000111; //7 ,07 4'b1000: out3<=~7'b1111111; //8, 7F 4'b1001: out3<=~7'b1101111; //9, 6F default: out3<=~7'b0111111; //0 ,3F endcaseendalways @(posedge clk)begin //数码管译码显示case(num2[7:4])4'b0000: out4<=~7'b0111111; //0 ,3F 4'b0001: out4<=~7'b0000110; //1 ,06 4'b0010: out4<=~7'b1011011; //2 ,5B 4'b0011: out4<=~7'b1001111; //3 ,4F 4'b0100: out4<=~7'b1100110; //4 ,66 4'b0101: out4<=~7'b1101101; //5 ,6D 4'b0110: out4<=~7'b1111101; //6 ,7D 4'b0111: out4<=~7'b0000111; //7 ,07 4'b1000: out4<=~7'b1111111; //8, 7F 4'b1001: out4<=~7'b1101111; //9, 6F default: out4<=~7'b0111111; //0 ,3F endcaseendendmodule。

Verilog语言实现设计交通灯控制器实验模块组成:(计数器+控制器)可以分开实现,最好一起实现避免接口对接时出错译码器实验要求:1.在十字路口两个方向各设一组红、绿、黄灯,显示顺序为:南北方向是绿、黄、红灯;东西方向是红、绿、黄灯。

2.要求红、绿、黄灯的持续时间分别为:10s、7s、3s,东西、南北方向各用一个数码管显示倒计时时间。

3.当任意方向出现特殊情况时,应优先放行,即使各方向均亮红灯,倒计时停止,且显示数字闪烁。

经过规定时间之后,恢复正常运行状态。

//计数器+控制器module ZTJ(clk,s,count1,count2,led);parameter s0=6’b010100,s1=6’b001100,s2=6'b100010,s3=6'b100001,s4=6'b100100;input clk,s;output[3:0]count1;output[3:0]count2;output[5:0]led;reg[3:0]count1;reg[3:0]count2;reg[5:0]led;reg[5:0]st;reg[5:0]jicun;reg[3:0]i;always @(posedge clk)if(s==0 &led==6’b000000)beginled<=s0;st<=s0;count1<=4'b0110;count2〈=4’b1001;endelse if(s==0 & led!=6’b000000)begincase(st)s0:if(count1!=4'b0000) begin led<=s0;count1〈=count1—1;count2<=count2-1;end else begin count1<=4'b0010;st<=s1;ends1:if(count1!=4'b0000)begin led〈=s1;count1〈=count1—1;count2<=count2-1;end else begin count1〈=4’b1001;count2<=4'b0110;st<=s2;ends2:if(count2!=4’b0000) begin led〈=s2;count1<=count1-1;count2〈=count2-1;end else begin count2〈=4’b0010;st〈=s3;ends3:if(count2!=4'b0000)begin led<=s3;count1〈=count1—1;count2〈=count2—1;end else begin count1<=4’b0110;count2〈=4’b1001;st<=s0;enddefault:led<=s4;endcaseendelsebeginjicun<=led;led〈=s4;count1<=count1;count2〈=count2;i<=i+1;if(i==4’b1001)led〈=jicun;endendmodule//译码器module DECL7S(A,LED7S);input [3:0]A;output [6:0]LED7S;reg [6:0]LED7S;always@(A)begincase(A)4’b0000:LED7S<=7'b0111111;4’b0001: LED7S<=7'b0000110;4'b0010: LED7S<=7'b1011011;4'b0011:LED7S〈=7'b1001111;4'b0100:LED7S<=7’b1100110;4’b0101:LED7S<=7’b1101101;4'b0110: LED7S<=7’b1111101;4'b0111:LED7S<=7'b0000111;4’b1000:LED7S<=7'b1111111;4’b1001: LED7S<=7'b1101111;4'b1010: LED7S<=7’b1110111;4’b1011:LED7S〈=7'b1111100;4’b1100: LED7S〈=7'b0111001;4'b1101:LED7S<=7’b1011110;4'b1110: LED7S<=7'b1111001;4’b1111:LED7S〈=7’b1110001;default:LED7S〈=7'b0111111;endcaseendendmodule。

交通灯一、实验目的写一个交通灯,要求:①有东西南北四个方向,两组交通灯轮流交替变换,其中,红灯时间为30个时间单位,绿灯时间为25个时间单位,黄灯时间为5个时间单位。

最后用modelsim软件进行仿真。

②要求设计是一个可综合设计。

二、实验原理根据实验要求的逻辑功能描述,可以分析得出原理图如下:控制器即可以设计为一个有限状态机的形式:E-W方向S-N方向状态R Y G R Y G1 0 0 1 0 0 IDLE1 0 0 0 0 1 S11 0 0 0 1 0 S20 0 1 1 0 0 S30 1 0 1 0 0 S4根据实验要求画出控制器的状态转移图如下:三、代码1、源代码(1)控制器模块module traffic_lights(clk,rst,count,ew,sn);input clk,rst;input[5:0] count;output[2:0] ew,sn;reg[2:0] ew,sn;reg[3:0] state;parameter Idle=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100; always (posedge clk)if(!rst)beginstate<=Idle;endelsecasex(state)Idle: if(rst)beginstate<=s1;ends1: if(count=='d25)beginstate<=s2;ends2: if(count=='d30)beginstate<=s3;ends3: if(count=='d55)beginstate<=s4;ends4: if(count=='d60)beginstate<=s1;endendcasealways (posedge clk)beginif(!rst)beginew<=3'b100;sn<=3'b100;endelsecasex(state)Idle: if(rst)beginew<=3'b100;sn<=3'b001;ends1: if(count=='d25)beginew<=3'b100;sn<=3'b010;ends2: if(count=='d30)beginew<=3'b001;sn<=3'b100;ends3: if(count=='d55)beginew<=3'b010;sn<=3'b100;ends4: if(count=='d60)beginew<=3'b100;sn<=3'b001;enddefault: state<=Idle;endcaseendendmodule(2)计数器模块module counter(en,clk,rst,out);output[5:0]out;input en,clk,rst;reg[5:0] out;always(posedge clk or negedge rst)beginif(!rst)out<='d0;else if(!en&&out<'d60)out<=out+1;elseout<='d1;endendmodule(3)将控制器与计数器进行连接module traffic_lights_top(out,clk,rst,en,ew,sn); input clk,rst,en;output[2:0] ew,sn;output[5:0]out;wire[5:0] out;traffic_lights u1(.clk(clk),.rst(rst),.count(out),.ew(ew),.sn(sn));counter u2(.en(en),.clk(clk),.rst(rst),.out(out));endmodule2、激励`timescale 1ns/100psmodule traffic_lights_tb;reg clk,rst,en;wire[2:0] ew,sn;wire[5:0]out;traffic_lights_top m(.clk(clk),.rst(rst),.en(en),.ew(ew),.sn(sn),.out(out));always#5 clk=~clk;initialen<=1;initialbeginclk<=1;en<=0;rst<=0;#5 rst<=1;endendmodule四、仿真波形(图一)(图二)五、波形说明波形图中,从上至下依次为:时钟信号clk、复位信号rst、计数器使能端en、东西方向上灯的状态ew、南北方向上灯的状态sn、计数器的输出out。

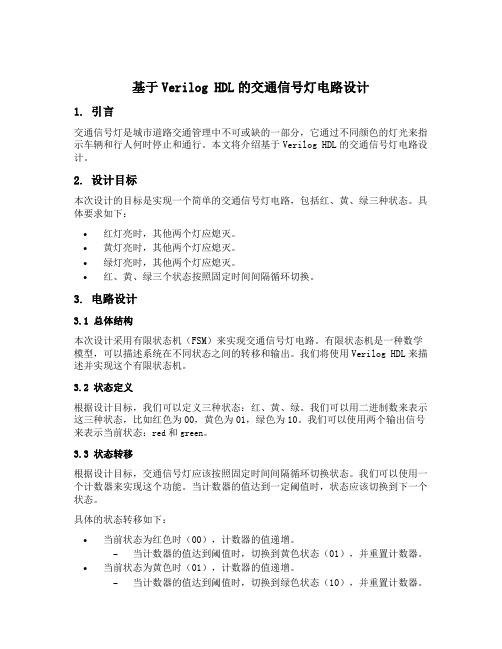

基于Verilog HDL的交通信号灯电路设计1. 引言交通信号灯是城市道路交通管理中不可或缺的一部分,它通过不同颜色的灯光来指示车辆和行人何时停止和通行。

本文将介绍基于Verilog HDL的交通信号灯电路设计。

2. 设计目标本次设计的目标是实现一个简单的交通信号灯电路,包括红、黄、绿三种状态。

具体要求如下:•红灯亮时,其他两个灯应熄灭。

•黄灯亮时,其他两个灯应熄灭。

•绿灯亮时,其他两个灯应熄灭。

•红、黄、绿三个状态按照固定时间间隔循环切换。

3. 电路设计3.1 总体结构本次设计采用有限状态机(FSM)来实现交通信号灯电路。

有限状态机是一种数学模型,可以描述系统在不同状态之间的转移和输出。

我们将使用Verilog HDL来描述并实现这个有限状态机。

3.2 状态定义根据设计目标,我们可以定义三种状态:红、黄、绿。

我们可以用二进制数来表示这三种状态,比如红色为00,黄色为01,绿色为10。

我们可以使用两个输出信号来表示当前状态:red和green。

3.3 状态转移根据设计目标,交通信号灯应该按照固定时间间隔循环切换状态。

我们可以使用一个计数器来实现这个功能。

当计数器的值达到一定阈值时,状态应该切换到下一个状态。

具体的状态转移如下:•当前状态为红色时(00),计数器的值递增。

–当计数器的值达到阈值时,切换到黄色状态(01),并重置计数器。

•当前状态为黄色时(01),计数器的值递增。

–当计数器的值达到阈值时,切换到绿色状态(10),并重置计数器。

•当前状态为绿色时(10),计数器的值递增。

–当计数器的值达到阈值时,切换到红色状态(00),并重置计数器。

3.4 Verilog HDL代码实现以下是基于Verilog HDL实现交通信号灯电路的代码:module traffic_light(input wire clk,output reg red,output reg yellow,output reg green);reg [1:0] state;reg [3:0] counter;parameter THRESHOLD = 4'b1010; // 阈值always @(posedge clk) begincase(state)2'b00: begin// 红灯状态if(counter == THRESHOLD) beginstate <= 2'b01; // 切换到黄灯状态counter <= 0;end else begincounter <= counter + 1;endend2'b01: begin// 黄灯状态if(counter == THRESHOLD) beginstate <= 2'b10; // 切换到绿灯状态counter <= 0;end else begincounter <= counter + 1;endend2'b10: begin// 绿灯状态if(counter == THRESHOLD) beginstate <= 2'b00; // 切换到红灯状态counter <= 0;end else begincounter <= counter + 1;endendendcaseendalways @(state) begincase(state)2'b00: begin// 红灯亮,其他两个灯熄灭red <= 1;yellow <= 0;green <= 0;end2'b01: begin// 黄灯亮,其他两个灯熄灭red <= 0;yellow <= 1;green <= 0;end2'b10: begin// 绿灯亮,其他两个灯熄灭red <= 0;yellow <= 0;green <= 1;endendcaseendendmodule4. 总结本文介绍了基于Verilog HDL的交通信号灯电路设计。

module traf_lamp(clk,en,lampa,lampb,acount,bcount);input clk;input en;//使能端高电平有效output reg[3:0] lampa,lampb;//4位分别用于a灯的颜色选择output [7:0] acount,bcount;//分别用于驱动数码管显示reg tempa,tempb;//用于控制路口红绿灯等的变换,低电平有效reg [7:0] numa,numb;//用于显示的数据值reg [2:0] counta,countb;//表示灯的状态reg [7:0] ared,agreen,ayellow,aleft,bred,bgreen,byellow,bleft;//各种灯计数器的预置数always@(en)if(!en) beginared <=8'd55;ayellow <=8'd5;agreen <=8'd40;aleft <=8'd15;bred <=8'd65;byellow <=8'd5;bleft <=8'd15;bgreen <=8'd30;endassign acount=numa;assign bcount=numb;always@(posedge clk) begin//交通灯a的控制if(en)if(!tempa) begintempa<=1;case(counta)0:begin numa<=agreen; lampa<=2; counta<=1;end 1:begin numa<=ayellow; lampa<=4; counta<=2;end 2:begin numa<=aleft; lampa<=1; counta<=3;end 3:begin numa<=ayellow; lampa<=4; counta<=4;end 4:begin numa<=ared; lampa<=8; counta<=0;end default:lampa<=8;endcaseendelse begin //倒计时,体会时序的实现方式if(numa>0)if(numa[3:0]==0) begin numa[3:0]<=4'b1001;numa[7:4]<=numa[7:4]-1;endelse numa[3:0]<=numa[3:0]-1;if(numa==2) tempa<=0;endelse begin counta<=0;tempa<=0;lampa<=4'b1000;endendalways@(posedge clk) begin//交通灯b的控制if(en)if(!tempb) begintempb<=1;case(countb)0:begin numb<=bred; lampb<=8; countb<=1;end1:begin numb<=bgreen; lampb<=2; countb<=2;end2:begin numb<=byellow; lampb<=4; countb<=3;end3:begin numb<=bleft; lampb<=1; countb<=4;end4:begin numb<=byellow; lampb<=4; countb<=0;enddefault:lampb<=8;endcaseendelse begin //倒计时,体会时序的实现方式if(numb>0)if(numb[3:0]==0) begin numb[3:0]<=4'b1001;numb[7:4]<=numb[7:4]-1;endelse numb[3:0]<=numb[3:0]-1;if(numb==2) tempb<=0;endelse begin countb<=0;tempb<=0;lampb<=4'b1000;endendendmodule。