时序电路VHDL设计(时序逻辑部分)

- 格式:ppt

- 大小:1.44 MB

- 文档页数:102

数电基础:时序逻辑电路虽然每个数字电路系统可能包含有,但是在实际应⽤中绝⼤多数的系统还包括,我们将这样的系统描述为时序电路。

时序电路是由最基本的加上反馈逻辑回路(输出到输⼊)或器件组合⽽成的电路,与最本质的区别在于时序电路具有记忆功能。

1. 简介是数字逻辑电路的重要组成部分,时序逻辑电路⼜称,主要由 存储电路 和 组合逻辑电路 两部分组成。

它和我们熟悉的其他电路不同,其在任何⼀个时刻的输出状态由当时的输⼊信号和电路原来的状态共同决定,⽽它的状态主要是由存储电路来记忆和表⽰的。

同时时序逻辑电路在结构以及功能上的特殊性,相较其他种类的数字逻辑电路⽽⾔,往往具有难度⼤、电路复杂并且应⽤范围⼴的特点 。

在数字电路通常分为和时序逻辑电路两⼤类,组合逻辑电路的特点是输⼊的变化直接反映了输出的变化,其输出的状态仅取决于输⼊的当前的状态,与输⼊、输出的原始状态⽆关,⽽是⼀种输出不仅与当前的输⼊有关,⽽且与其输出状态的原始状态有关,其相当于在组合逻辑的输⼊端加上了⼀个反馈输⼊,在其电路中有⼀个存储电路,其可以将输出的状态保持住,我们可以⽤下图的框图来描述时序电路的构成。

从上⾯的图上可以看出,其输出是输⼊及输出前⼀个时刻的状态的函数,这时就⽆法⽤组合逻辑电路的函数表达式的⽅法来表⽰其输出函数表达式了,在这⾥引⼊了现态(Present state)和次态(Next State)的概念,当现态表⽰现在的状态(通常⽤Qn来表⽰),⽽次态表⽰输⼊发⽣变化后其输出的状态 (通常⽤Qn+1表⽰),那么输⼊变化后的输出状态表⽰为Qn+1=f(X,Qn),其中:X为输⼊变量。

组合电路和存储元件互联后组成了时序电路。

存储元件是能够存储信息的电路。

存储元件在某⼀时刻存储的⼆进制信息定义为该时刻存储元件的状态。

时序电路通过其输⼊端从周围接受⼆进制信息。

时序电路的输⼊以及存储元件的当前状态共同决定了时序电路输出的⼆进制数据,同时它们也确定了存储元件的下⼀个状态。

时序电路的设计及显示时序电路是一种能够根据输入信号的时序关系来产生相应输出信号的电路。

它主要应用于计算机、通信系统、测控系统等领域,用于控制及处理各种时序信号。

本文将介绍时序电路的设计原理以及不同类型的时序电路显示。

1.时序电路的设计原理1.1时序逻辑电路时序逻辑电路是根据时序信号的控制来产生相应的输出信号。

它由组合逻辑门和触发器组成。

组合逻辑门根据输入信号的逻辑关系产生输出信号,而触发器则根据时钟信号的控制来保持或改变其输出状态。

时序逻辑电路的设计一般包括以下步骤:1)确定逻辑功能:根据需求确定所需的逻辑功能,包括输入输出信号及其逻辑关系。

2)设计组合逻辑电路:根据逻辑功能设计组合逻辑电路,利用逻辑门实现输入信号的逻辑关系。

3)设计时序控制电路:根据逻辑功能确定触发器的数量及其工作方式,并利用时序控制电路控制触发器的输入和输出。

4)进行仿真与验证:利用电路仿真软件进行仿真验证,确保电路的正确性。

5)设计PCB电路板:根据电路图设计PCB电路板,完成电路的布局和连线。

6)进行实际测试:将设计好的电路板进行实际测试,验证电路的性能和可靠性。

1.2时序控制电路时序控制电路用于控制时序逻辑电路的工作状态。

它主要由时钟信号发生器、时序控制器和触发器等组成。

时序控制电路主要包括同步时序控制和异步时序控制两种形式。

同步时序控制是通过时钟信号来控制触发器的工作,保证电路的同步工作。

异步时序控制则根据输入信号的状态来控制触发器的工作,适用于电路的反应时间较短或信号复杂的情况。

2.时序电路的显示2.1数码管显示数码管是一种将数字信号以数字形式显示的设备,通常由七段显示元件组成。

数码管显示通过控制数码管的每一段,将数字信号转化为相应的数字显示。

2.2液晶显示液晶显示屏是一种将数字、字母、图形等以液晶显示的设备。

液晶显示采用液晶材料的光学性质来显示信息,具有低功耗、薄、轻、反应速度快等优点。

2.3LED显示LED显示是一种通过控制发光二极管的亮灭来显示信息的设备。

数字电路与逻辑设计实验报告学院:班级:姓名:学号:日期:一.实验名称:实验一:QuartusII 原理图输入法设计与实现实验二:用VHDL 设计与实现组合逻辑电路实验三:用VHDL 设计与实现时序逻辑电路实验四:用VHDL 设计与实现数码管动态扫描控制器二.实验所用器件及仪器:1.计算机2.直流稳压电源3.数字系统与逻辑设计实验开发板三.实验要求:实验一:(1)用逻辑门设计实现一个半加器,仿真验证其功能,并生成新的半加器图形模块单元。

(2)用(1)实现的半加器和逻辑门设计实现一个全加器,仿真并验证其功能,并下载到实验板上测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号。

(3)用3—8线译码器和逻辑门设计实现函数F=/C/B/A+/CB/A+C/B/A+CBA,仿真验证其功能并下载到实验板测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号。

注:实验时将三个元器件放在一个new block diagram中实现。

实验二:(1)用VHDL语言设计实现一个共阴极7段数码译码器,仿真验证其功能,并下载到实验板测试。

要求用拨码开关设定输入信号,7段数码管显示输出信号。

(2)用VHDL语言设计实现一个8421码转余三码的代码器,仿真验证其功能,并下载到实验板测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号。

(3)用VHDL语言设计实现一个4位二进制奇校验器,输入奇数个‘1’时,输出1,否则出0;仿真验证其功能,并下载到实验板测试。

要求用拨码开关设定输入信号,发光二极管显示输出信号。

实验三:(1)用VHDL语言设计实现一个带异步复位的8421 十进制计数器,仿真验证其功能,并下载到实验板测试。

要求用按键设定输入信号,发光二极管显示输出信号。

(2)用VHDL语言设计实现一个分频系数为12,输出信号占空比为50%的分频器,仿真验证其功能。

注:实验时将(1)、(2)和数码管译码器 3 个电路进行链接,并下载到实验板显示计数结果。

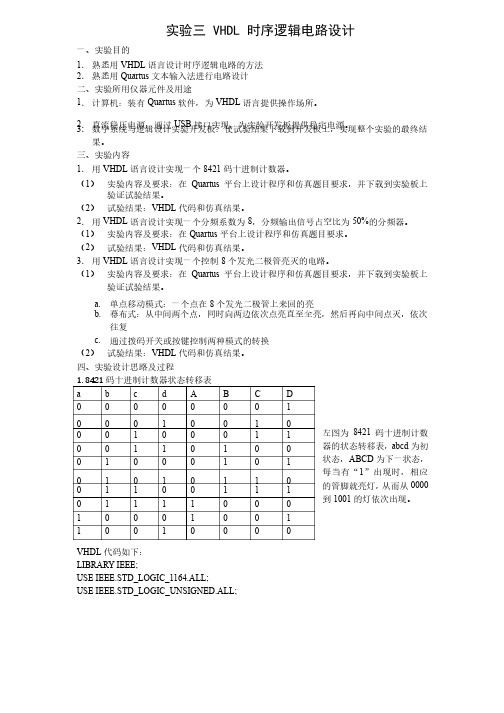

实验三 VHDL 时序逻辑电路设计一、实验目的1.熟悉用VHDL语言设计时序逻辑电路的方法2.熟悉用Quartus文本输入法进行电路设计二、实验所用仪器元件及用途1.计算机:装有Quartus软件,为VHDL语言提供操作场所。

2.直流稳压电源:通过USB接口实现,为实验开发板提供稳定电源。

3.数字系统与逻辑设计实验开发板:使试验结果下载到开发板上,实现整个实验的最终结果。

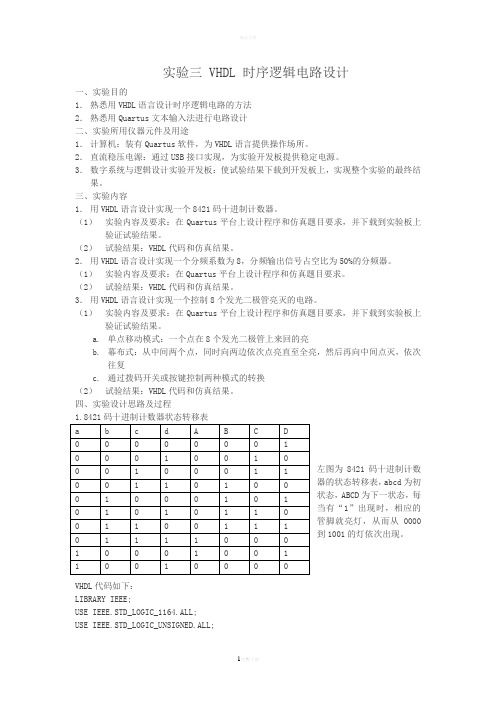

三、实验内容1.用VHDL语言设计实现一个8421码十进制计数器。

(1)实验内容及要求:在Quartus平台上设计程序和仿真题目要求,并下载到实验板上验证试验结果。

(2)试验结果:VHDL代码和仿真结果。

2.用VHDL语言设计实现一个分频系数为8,分频输出信号占空比为50%的分频器。

(1)实验内容及要求:在Quartus平台上设计程序和仿真题目要求。

(2)试验结果:VHDL代码和仿真结果。

3.用VHDL语言设计实现一个控制8个发光二极管亮灭的电路。

(1)实验内容及要求:在Quartus平台上设计程序和仿真题目要求,并下载到实验板上验证试验结果。

a.单点移动模式:一个点在8个发光二极管上来回的亮b.幕布式:从中间两个点,同时向两边依次点亮直至全亮,然后再向中间点灭,依次往复c.通过拨码开关或按键控制两种模式的转换(2)试验结果:VHDL代码和仿真结果。

四、实验设计思路及过程1.8421码十进制计数器状态转移表左图为8421码十进制计数器的状态转移表,abcd为初状态,ABCD为下一状态,每当有“1”出现时,相应的管脚就亮灯,从而从0000到1001的灯依次出现。

VHDL代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY count12 ISPORT(clk,clear:IN STD_LOGIC;q :OUT STD_LOGIC_VECTOR(3 DOWNTO 0);END count12;ARCHITECTURE a OF count12 ISSIGNAL q_temp:ATD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(clk)BEGINIF(clk'event and clk='1') THENIF clear='0' THENq_temp<="0000";ELSIF q_temp="1011"THENq_temp<="0000";ELSEq_temp<=q_temp+1;END IF;END IF;END PROCESS;q<=q_temp;END a;2.分频系数为8,输出占空比为50%的分频器的设计左图为八分频器(占空比50%)的状态转移图,其中abc为原状态,ABC为下一状态。

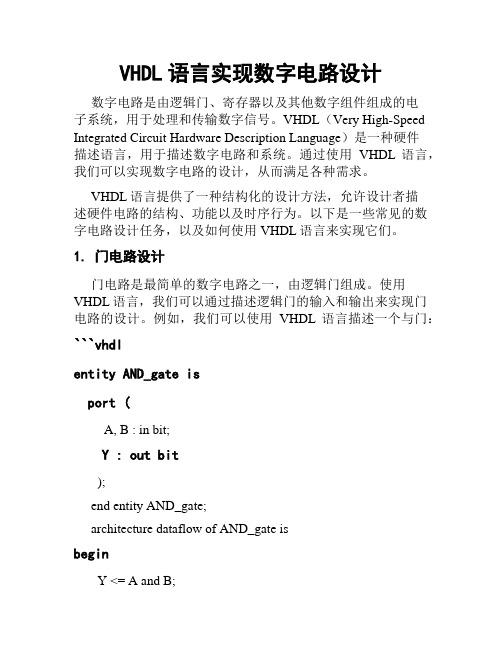

VHDL语言实现数字电路设计数字电路是由逻辑门、寄存器以及其他数字组件组成的电子系统,用于处理和传输数字信号。

VHDL(Very High-Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,用于描述数字电路和系统。

通过使用VHDL语言,我们可以实现数字电路的设计,从而满足各种需求。

VHDL语言提供了一种结构化的设计方法,允许设计者描述硬件电路的结构、功能以及时序行为。

以下是一些常见的数字电路设计任务,以及如何使用VHDL语言来实现它们。

1. 门电路设计门电路是最简单的数字电路之一,由逻辑门组成。

使用VHDL语言,我们可以通过描述逻辑门的输入和输出来实现门电路的设计。

例如,我们可以使用VHDL语言描述一个与门:```vhdlentity AND_gate isport (A, B : in bit;Y : out bit);end entity AND_gate;architecture dataflow of AND_gate isbeginY <= A and B;end architecture dataflow;```在这个例子中,我们定义了一个输入端口A和B,以及一个输出端口Y。

在architecture部分,我们使用VHDL语言描述了Y的逻辑值为A和B的逻辑与。

2. 时序逻辑电路设计时序逻辑电路是根据时钟信号进行操作和状态转换的电路。

使用VHDL语言,我们可以描述时序逻辑电路的行为和状态变化。

例如,我们可以使用VHDL语言描述一个触发器:```vhdlentity D_flip_flop isport (D, CLK : in bit;Q : out bit);end entity D_flip_flop;architecture behavior of D_flip_flop issignal Q_temp : bit;beginprocess(CLK)beginif CLK'event and CLK = '1' thenQ_temp <= D;end if;end process;Q <= Q_temp;end architecture behavior;```在这个例子中,我们定义了一个输入端口D和CLK,以及一个输出端口Q。

时序逻辑电路时序逻辑电路是一种在电子数字电路领域中应用广泛的重要概念,它主要用于解决电路中的时序问题,如时钟同步问题、时序逻辑分析等。

本文将详细介绍时序逻辑电路的基础概念、工作原理以及应用。

一、时序逻辑电路的基础概念1、时序逻辑和组合逻辑的区别组合逻辑电路是一类基于组合逻辑门的电路,其输出仅取决于输入信号的当前状态,不受先前的输入状态所影响。

而时序逻辑电路的输出则受到先前输入信号状态的影响。

2、时序逻辑电路的组成时序逻辑电路通常由时钟、触发器、寄存器等组成。

时钟信号被用于同步电路中的各个部分,触发器将输入信号存储在内部状态中,并在时钟信号的作用下用来更新输出状态。

寄存器则是一种特殊类型的触发器,它能够存储多个位的数据。

3、时序逻辑电路的分类根据时序逻辑电路的时序模型,可将其分为同步和异步电路。

同步电路按照时钟信号的周期性工作,这意味着电路通过提供时钟信号来同步所有操作,而操作仅在时钟上升沿或下降沿时才能发生。

异步电路不同,它不依赖时钟信号或时钟信号的上升和下降沿,所以在一次操作完成之前,下一次操作可能已经开始了。

二、时序逻辑电路的工作原理时序逻辑电路的主要工作原理基于触发器的行为和时钟电路的同步机制。

在时序逻辑电路中使用了一些触发器来存储电路状态,待时钟信号到达时更新输出。

时钟信号提供了同步的机制,确保电路中所有部分在时钟信号到达时同时工作。

触发器的基本工作原理是将输入信号存储到内部状态中,并在时钟信号的作用下,用来更新输出状态。

时钟信号的边沿触发触发器,即在上升沿或下降沿时触发触发器状态的更新。

这意味着在更新之前,电路的状态保持不变。

三、时序逻辑电路的应用1、时序电路在计算机系统中的应用时序逻辑电路在计算机系统中有着广泛的应用。

例如,计算机中的时钟信号可用来同步处理器、主存储器和其他外设间的工作。

此外,电路中的寄存器和触发器也被用于存储和更新信息,这些信息可以是计算机程序中的指令、运算结果或其他数据。

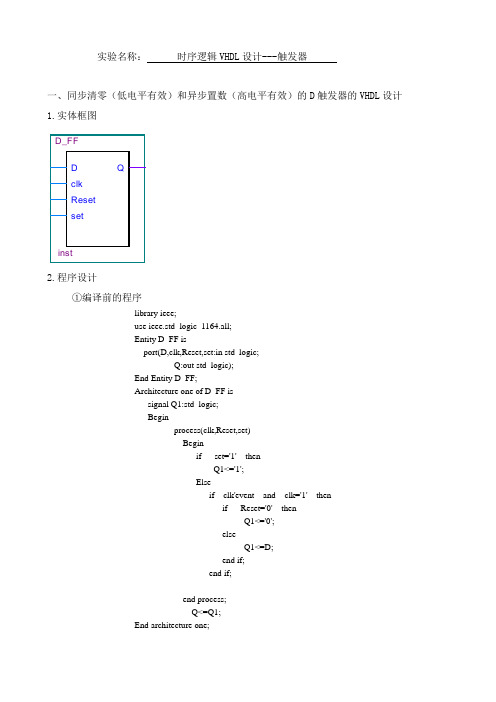

实验名称:时序逻辑VHDL设计---触发器一、同步清零(低电平有效)和异步置数(高电平有效)的D触发器的VHDL设计1.实体框图Dclk Reset set QD_FFinst2.程序设计①编译前的程序library ieee;use ieee.std_logic_1164.all;Entity D_FF isport(D,clk,Reset,set:in std_logic;Q:out std_logic);End Entity D_FF;Architecture one of D_FF issignal Q1:std_logic;Beginprocess(clk,Reset,set)Beginif set='1' thenQ1<='1';Elseif clk'event and clk='1' thenif Reset='0' thenQ1<='0';elseQ1<=D;end if;end if;end process;Q<=Q1;End architecture one;②程序编译错误情况错误1:Error (10500): VHDL syntax error at D_FF.vhd(22) near text "process"; expecting "if"错误2:Error (10500): VHDL syntax error at D_FF.vhd(24) near text "architecture"; expecting "if"分析:经检查,发现原程序少了END if,没有与if匹配,添加即可。

③正确的程序library ieee;use ieee.std_logic_1164.all;Entity D_FF isport(D,clk,Reset,set:in std_logic;Q:out std_logic);End Entity D_FF;Architecture one of D_FF issignal Q1:std_logic;Beginprocess(clk,Reset,set)Beginif set='1' thenQ1<='1';Elseif clk'event and clk='1' thenif Reset='0' thenQ1<='0';elseQ1<=D;end if;end if;end if;end process;Q<=Q1;End architecture one;3.仿真波形图4.仿真波形分析当置数端SET出现高电平时,此时不管CP脉冲和D的状态如何,输出立即置为‘1’,实现异步置数的功能;当清零端RESET出现低电平时,而且必须当CP脉冲为上升沿时,输出清零,实现同步清零;除此之外,当CP脉冲为上升沿状态时,D=0,Q=0;D=1,Q=1;二、异步清零(高电平有效)和同步置数(低电平有效)的JK触发器的VHDL设计1.实体框图clk reset setJK[0..1]QJK_FFinst2.程序设计①编译前的程序Library ieee;use ieee.std_logic_1164.all;Entity JK_FF isport( clk,reset,set,J,K:in std_logic;Q:out std_logic);End entity JK_FF;Architecture two of JK_FF issignal Q1:std_logic;beginprocess(clk,reset,set,J,K)beginif reset='1' thenQ1<='0';elseif clk'event and clk='1' thenif set='0' thenQ1<='1';elsecase JK iswhen "00" => Q1<=Q1;when "10" => Q1<='1';when "11" => Q1<=not Q1;when others =>NULL;end case;end if;end if;end if;end process;Q<=Q1;end architecture two;②程序编译错误情况错误1:Error (10482): VHDL error at JK-FF.vhd(19): object "JK" is used but not declared错误2:Error (10523): Ignored construct two at JK-FF.vhd(7) due to previous errors分析:JK为两位,需要定义如下:JK:in std_logic_vector(0 to 1);③正确的程序Library ieee;use ieee.std_logic_1164.all;Entity JK_FF isport( clk,reset,set:in std_logic;JK:in std_logic_vector(0 to 1);Q:out std_logic);End entity JK_FF;Architecture two of JK_FF issignal Q1:std_logic;beginprocess(clk,reset,set,JK)beginif reset='1' thenQ1<='0';elseif clk'event and clk='1' thenif set='0' thenQ1<='1';elsecase JK iswhen "00" => Q1<=Q1;when "01" => Q1<='0';when "10" => Q1<='1';when "11" => Q1<=not Q1;end case;end if;end if;end if;end process;Q<=Q1;end architecture two;3.仿真波形图4.仿真波形分析当清零端ResET出现高电平时,此时不管CP脉冲和JK的状态如何,输出立即清零,实现异步清零的功能;当置数端SET出现低电平时,而且必须当CP脉冲为上升沿时,输出立即置数‘1‘,实现同步置数的功能;除此之外,当CP脉冲为上升沿状态时,J=K=0,Q保持;J=0,K=1,Q置零;J=1,K=0,Q置1;J=K=1,Q翻转一、8位锁存器的VHDL设计1.实体框图D[0..7] clk Q[0..7]latch8a2.程序设计①编译前的程序Library ieee;use ieee.std_logic_1164.all;Entity latch8a isport(D:in std_logic_vector(7 to 0);clk:in std_logic;Q:out std_logic_vector(7 to 0));End latch8a;Architecture three of latch8a issignal q1:std_logic_vector(7 to 0);beginprocess (clk,D)beginif clk'event and clk='1' thenQ1<=D;end if;end process;Q<=Q1;End architecture three;②程序编译错误情况错误:无③正确的程序Library ieee;use ieee.std_logic_1164.all;Entity latch8a isport(D:in std_logic_vector(0 to 7);clk:in std_logic;Q:out std_logic_vector(0 to 7));End latch8a;Architecture three of latch8a issignal q1:std_logic_vector(0 to 7);beginprocess (clk,D)beginif clk'event and clk='1' thenend if;end process;Q<=Q1;End architecture three;3.仿真波形图4.仿真波形分析当CLK脉冲为高电平时,输出为与其相对应的输出。

《FPGA系统设计》实验报告》时序逻辑电路的设计

一、设计任务

分别设计并实现锁存器、触发器的VHDL模型。

二、设计过程

1、同步锁存器:

同步锁存器是指复位和加载功能全部与时钟同步,复位端的优先级较高。

下图为同步锁存器的VHDL程序及模型:

2、异步锁存器:

异步锁存器,是指复位与时钟不同步的锁存器。

下图为同步锁存器的VHDL程序及模型:

3、D触发器:

D触发器是最常用的触发器。

下图为简单D触发器的VHDL 模型:

4、T触发器:

T触发器的特点是在时钟沿处输出信号发生翻转。

按

照有无复位、置位信号以及使能信号等,T触发器也有多种类型。

下图为带异步复位T触发器的VHDL模型:

5、JK触发器:

JK触发器中,J、K信号分别扮演置位、复位信号的角色。

为了更清晰的表示出JK触发器的工作过程,以下给出JK触发器的真值表(如表1所示)。

表1 JK触发器真值表

按照有无复位、置位信号,常见的JK触发器也有多种类型,下图带异步复位(clr)、置位(prn)的JK触发器的VHDL模型:

三.总结

本次实验中较为顺利,在第一次课的时间内我就已经完成了必做实验与选作实验。

在实验的过程中,在防抖电路处有了较大的困难。

由于仿真中不存在此问题,在实际操作中参数选择时遇到了一定的困难。

在反复比对效果之后,我

确定了电路的参数,实现了防抖功能。

通过这次实验,我对时钟脉冲、计数器等有了更加深入的认识与理解。

GDOU-B-11-213《VHDL语言程序设计》课程教学大纲课程简介课程简介:本课程为软件工程专业嵌入式专业方向的专业课,是开发基于FPGA/CPLD嵌入式系统的必备基础。

主要内容包括FPGA/CPLD目标器件的结构和工作原理、EDA技术和工作流程、VHDL基础知识、VHDL实用方法和设计深入、原理图输入法、LPM宏功能模块实用方法、状态机设计以及EDA优化设计。

目的是为后续课程的学习和嵌入式系统的设计作必须的基础准备。

课程大纲一、课程的性质与任务:本课程是软件工程专业的专业方向课程。

教学任务主要包括使学生了解EDA技术的工作流程,正确使用开发平台,掌握以VHDL为代表的硬件描述语言的基本知识、编程实用方法和工程设计方法,掌握原理图设计法、状态机设计法,能够正确使用IP Core和LPM等宏功能模块。

本课程是软件工程专业嵌入式专业方向的第一门专业方向课,是后续课程的必备基础,具有较重要的地位。

二、课程的目的与基本要求:本课程涉及到的学科基础知识面广,要求软硬件兼备,需要较好的学科基础。

通过本课程的学习,最终达到能够设计基于FPGA/CPLD的ASIC,并能进行EDA优化的目的。

三、面向专业:软件工程四、先修课程:《计算系统基础》五、本课程与其它课程的联系:本课程的先行课程是计算系统基础。

服务的主要后续课程包括基于FPGA的嵌入式软件开发、基于ARM的嵌入式软件开发等。

六、教学内容安排、要求、学时分配及作业:第一章概述(2学时)1.1 EDA技术及其发展(C)1.2 硬件描述语言硬件描述语言种类、自顶向下设计方法、EDA工程设计流程。

(A)1.3 面向FPGA/CPLD的开发流程设计输入、分析综合、布局布线、仿真、下载和硬件测试。

(A)1.4 IP Core 及EDA技术发展趋势。

(C)第二章 FPGA硬件特性与编程技术(8学时)2.1 PLD发展历程及其分类(c)2.2 低密度PLD工作原理PROM、PLA、PAL、GAL。

使用VHDL进行数字电路设计VHDL(Very High Speed Integrated Circuit Hardware Description Language,高速集成电路硬件描述语言)是一种用于电子设计的编程语言,常用于数字电路设计。

它具备高层次抽象和结构化描述等特点,可以有效地对数字电路进行建模和仿真。

本文将介绍使用VHDL进行数字电路设计的基本步骤和方法。

一、VHDL简介VHDL是一种硬件描述语言,是一种基于事件驱动和并发处理的语言。

它具有面向对象的特点,可以对电子系统进行高层次、结构化的描述。

二、数字电路设计基本流程1. 确定需求:明确数字电路设计的功能、性能和接口要求。

2. 设计规格:根据需求定义数字电路设计的规格和功能。

3. 构建设计:使用VHDL语言描述数字电路的结构和行为。

4. 仿真验证:通过仿真工具对设计进行验证,确保其符合规格要求。

5. 综合:将VHDL代码转化为门级电路,获取门级电路的性能和面积等信息。

6. 时序分析:对门级电路进行时序分析,确保其满足时序要求。

7. 布局布线:对门级电路进行布局布线,生成物理布图。

8. 验证测试:对物理布图进行验证测试,并进行修复和调整。

9. 出版物:生成最终的数字电路设计文档和相关资料。

三、VHDL语言基础VHDL语言具有丰富的语法和语义,可以用于描述数字电路的结构和行为。

以下是一些常用的VHDL语法元素:1. 实体(Entity):描述数字电路的接口和输入输出信号。

2. 架构(Architecture):描述数字电路的内部结构和行为。

3. 进程(Process):描述数字电路的并发行为和逻辑关系。

4. 信号(Signal):描述数字电路的内部和外部信号。

5. 时钟信号(Clock):描述数字电路的时序行为。

6. 模块化设计(Modular Design):将数字电路分为多个模块进行设计和组合。

四、使用VHDL进行数字电路设计的步骤1. 确定需求:明确设计的功能需求和性能要求。

时序逻辑电路设计时序逻辑电路是指电路的输出状态不仅与当前输入状态有关,还与之前的输入状态和电路内部的状态有关。

假如某个电路中包含寄存器或计数器等状态元件,该电路被称为时序逻辑电路。

时序逻辑电路广泛应用于计算机、通信和控制系统等领域中。

时序逻辑电路的设计包括以下几个方面:1. 电路功能分析在进行时序逻辑电路设计之前,需要对电路的功能进行分析和描述。

首先要明确电路的输入和输出端口,并确定输入和输出的数值范围。

通过对电路的功能进行逐一分析,确定电路输出状态与输入状态及电路内部状态的关系。

将这些关系用逻辑函数或状态转移图等形式表示出来。

2. 状态转移图和状态表的设计为了更好地描述时序逻辑电路的状态转移过程,可以使用状态转移图和状态表进行设计。

状态转移图表示电路在不同的输入状态下,状态之间的转移关系。

状态表则用表格的形式表示电路的输入和输出状态及状态之间的转移过程。

3. 状态方程和状态图的设计可以采用状态方程和状态图的方法来设计时序逻辑电路。

状态方程表示电路的输入和输出状态之间的逻辑关系,可以通过布尔代数的方式进行描述。

状态图则用图形的方式描述电路输入和输出状态之间的转移关系,可以帮助设计者更清晰地了解电路的状态变化规律。

4. 逻辑门电路的设计逻辑门电路是时序逻辑电路的关键组成部分,它可以实现逻辑运算和状态的存储与转移。

在设计逻辑门电路时,需要根据电路的功能需求选择适当的逻辑门类型进行组合,以实现电路所需要的逻辑运算和状态转移功能。

5. 电路的布线和验证在完成电路的设计后,需要进行电路布线和验证。

电路的布线是指将电路中的元器件进行连接,形成完整的电路图。

电路的验证则是指对电路进行模拟或者硬件实现,验证电路的功能和性能。

时序逻辑电路的设计是一项复杂的任务,需要设计者具备深厚的理论基础和丰富的实践经验。

只有通过科学的方法和严格的流程,才能设计出高效稳定的时序逻辑电路。

在时序逻辑电路设计过程中,还需要注意以下问题:1.时序电路的时序问题由于时序逻辑电路的设计包含状态转移,因此时序问题是一个非常关键的问题。

实验三实验三 VHDL VHDL VHDL 时序逻辑电路设计时序逻辑电路设计 一、实验目的一、实验目的1. 熟悉用VHDL 语言设计时序逻辑电路的方法语言设计时序逻辑电路的方法 2. 熟悉用Quartus 文本输入法进行电路设计文本输入法进行电路设计 二、实验所用仪器元件及用途二、实验所用仪器元件及用途 1. 计算机:装有Quartus 软件,为VHDL 语言提供操作场所。

语言提供操作场所。

2. 直流稳压电源:通过USB 接口实现,为实验开发板提供稳定电源。

接口实现,为实验开发板提供稳定电源。

3. 数字系统与逻辑设计实验开发板:使试验结果下载到开发板上,实现整个实验的最终结果。

果。

三、实验内容三、实验内容 1. 用VHDL 语言设计实现一个8421码十进制计数器。

码十进制计数器。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求,并下载到实验板上验证试验结果。

验证试验结果。

(2) 试验结果:VHDL 代码和仿真结果。

代码和仿真结果。

2. 用VHDL 语言设计实现一个分频系数为8,分频输出信号占空比为50%的分频器。

的分频器。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求。

平台上设计程序和仿真题目要求。

(2) 试验结果:VHDL 代码和仿真结果。

代码和仿真结果。

3. 用VHDL 语言设计实现一个控制8个发光二极管亮灭的电路。

个发光二极管亮灭的电路。

(1) 实验内容及要求:在Quartus 平台上设计程序和仿真题目要求,并下载到实验板上验证试验结果。

验证试验结果。

a. 单点移动模式:一个点在8个发光二极管上来回的亮个发光二极管上来回的亮b. 幕布式:从中间两个点,同时向两边依次点亮直至全亮,然后再向中间点灭,依次往复往复c. 通过拨码开关或按键控制两种模式的转换通过拨码开关或按键控制两种模式的转换 (2) 试验结果:VHDL 代码和仿真结果。