D触发器原理D触发器电路图

- 格式:doc

- 大小:148.00 KB

- 文档页数:3

D触发器工作原理D触发器是数字电路中常用的一种触发器,它具有存储和延迟功能,常用于时序电路和存储器等应用中。

本文将详细介绍D触发器的工作原理,包括其逻辑符号、真值表、输入输出特性以及触发器的时序图。

1. 逻辑符号和真值表D触发器的逻辑符号如下所示:```D┌───┐D │ │ Q└───┘```其中,D表示输入端,Q表示输出端。

D触发器根据输入端D的电平状态,将其存储在触发器内部,并在时钟信号的上升沿或者下降沿时将存储的数据传递到输出端Q。

D触发器的真值表如下所示:```D │ Q(t) │ Q(t+1)─────┼────────┼────────0 │ 0 │ 01 │ 1 │ 1```2. 输入输出特性D触发器有两个输入端:D和时钟信号。

D输入端用于输入待存储的数据,时钟信号用于触发数据的传递。

D触发器的输出端为Q。

D触发器的输入输出特性如下所示:- 当时钟信号为上升沿时,D触发器将输入端D的电平状态传递到输出端Q;- 当时钟信号为下降沿时,D触发器将输入端D的电平状态传递到输出端Q;- 当时钟信号为稳定状态时,D触发器保持上一次时钟信号变化时的输出状态。

3. 触发器的时序图D触发器的时序图如下所示:```______ ______| | | |D | | | |───┘ └─────────┘ └───| | | || Q | | Q |```时钟信号的上升沿或者下降沿触发D触发器,使其将输入端D的电平状态传递到输出端Q。

在时钟信号变化之前和之后,D触发器的输出保持不变。

4. 工作原理D触发器的工作原理是基于存储和延迟功能。

当时钟信号发生变化时,D触发器根据输入端D的电平状态将其存储在触发器内部,并在时钟信号的上升沿或者下降沿时将存储的数据传递到输出端Q。

具体工作原理如下:- 当时钟信号为上升沿时,D触发器将输入端D的电平状态传递到输出端Q。

如果D为高电平,则输出Q也为高电平;如果D为低电平,则输出Q也为低电平。

d触发器逻辑电路介绍d触发器是数字电路中常用的组合逻辑电路。

它具有存储功能,可以通过时钟信号来控制数据的传输和存储。

在本文中,我们将深入探讨d触发器的工作原理和应用场景。

基本原理d触发器是一种双稳态触发器,它可以存储1位的数据。

它由两个与门和两个非门组成。

d触发器有两个输入端:时钟(CLK)和数据(D),以及两个输出端:输出(Q)和非输出(Q’)。

当时钟信号为高电平(正脉冲)时,d触发器的输出Q将根据数据输入D的值进行改变。

如果D为高电平,则Q也为高电平;如果D为低电平,则Q为低电平。

在时钟信号为低电平(负脉冲)时,d触发器的输出将被保持在上一次时钟信号为高电平时的状态。

工作原理下面是d触发器的逻辑电路图:_____D _____| |____ Q| d' |CLK ___|_____|根据上图,我们可以看到当CLK为高电平时,d触发器的输出Q将受到D的值的控制。

具体来说,当CLK为高电平时,两个与门的输出取决于D和d’的值。

如果D 为高电平,d’为低电平,则Q为高电平;如果D为低电平,d’为高电平,则Q为低电平。

当CLK为低电平时,与门的输出被锁存,Q的状态保持不变。

应用场景d触发器在数字电路中有着广泛的应用,特别是在时序电路中。

以下是一些常见的应用场景:1. 时序电路设计d触发器可以用于设计各种时序电路,如计数器、移位寄存器、时钟分频器等。

通过合理使用时钟信号和数据输入D,我们可以实现不同的功能,实现更复杂的计算和控制。

2. 数据存储和同步d触发器可以用作数据存储器件,可以存储和传递数据信号。

通过时钟信号的控制,我们可以实现数据的同步传输,并且确保数据在传输过程中的稳定性。

3. 状态机设计d触发器的状态保持特性使其成为状态机设计中的重要组成部分。

通过合理使用d触发器和其他逻辑门,我们可以实现复杂的状态转换和状态控制逻辑。

4. 内存设计在计算机系统中,d触发器可以被用于构建存储器单元(如SRAM),用于存储和处理数据。

d 触发器的门级电路摘要:一、D触发器的基本概念二、D触发器的门级电路实现1.使用传输门搭建D触发器原理图2.观察D触发器原理图,分析相连传输门的共用源漏区处理3.版图设计中的优化策略三、D触发器在数字电路设计中的应用四、总结与展望正文:一、D触发器的基本概念D触发器(Data Trigger)是一种常见的触发器类型,用于在数字电路中存储和传输数据。

它根据输入信号D的状态来决定输出信号的变化,因此得名。

D触发器广泛应用于各种数字系统中,如计算机、通信设备等。

二、D触发器的门级电路实现1.使用传输门搭建D触发器原理图要实现D触发器,首先需要搭建其门级电路。

打开cadence软件,配置好工艺库,打开schematic界面。

然后,使用工艺库内的nmos和pmos搭建出如下图所示的用传输门设计的D触发器原理图。

2.观察D触发器原理图,分析相连传输门的共用源漏区处理通过对D触发器原理图的观察,可以发现,相连的传输门对应的nmos和pmos的源漏区是连在一起的。

因此,可以对其进行共用源漏区处理。

这样,在版图设计中,可以减小版图面积,为制作时节省巨大的成本。

3.版图设计中的优化策略在进行版图设计之前,需要对mos管的布局有初步的规划。

相应的传输门与反相器相连的地方,也可以进行共用源漏区处理。

此外,还可以采用其他优化策略,如合理布局元件,减小信号传输延迟等,以提高电路性能。

三、D触发器在数字电路设计中的应用D触发器在数字电路设计中的应用十分广泛。

它不仅可以用于存储和传输数据,还可以用于实现计数、寄存、控制等功能。

通过与其他触发器、逻辑门等元件配合使用,可以构建出复杂的数字系统。

四、总结与展望本文详细介绍了D触发器的门级电路实现及其在数字电路设计中的应用。

在实际设计过程中,还需根据具体需求和场景,灵活调整和优化电路结构。

随着科技的不断发展,数字电路设计将面临更多挑战,如更低功耗、更高性能等。

d触发器整形电路

d触发器是一种数字电路元件,常用于存储和传输数据。

它有两个输入端和两个输出端,称为D端和Q端。

D端是数据输入端,Q端是数据输出端。

当d触发器的时钟信号上升沿到来时,它会根据D 端的电平状态来改变输出端Q的电平状态。

d触发器的工作原理如下:当时钟信号上升沿到来时,如果D端为高电平,则Q端将保持高电平;如果D端为低电平,则Q端将保持低电平。

换句话说,d触发器会将D端的电平状态存储在自己的内部,然后在时钟信号上升沿到来时将其传输到输出端。

d触发器的作用非常广泛。

它可以用于存储数据,实现数据的暂存和传输功能。

在计算机中,d触发器常常被用作存储单元,用于存储二进制数据。

此外,d触发器还可以用于时序电路的设计,例如计数器和状态机。

除了存储和传输数据的功能外,d触发器还具有一些特殊的性质。

例如,它可以实现边沿检测功能,即在时钟信号的上升沿或下降沿到来时产生输出信号。

这种特性使得d触发器可以用于设计各种触发器、计数器和时序电路。

d触发器是一种非常重要的数字电路元件,它在存储和传输数据、实现边沿检测等方面具有广泛的应用。

通过合理的电路设计和使用d触发器,我们可以实现各种复杂的数字功能,提高电路的性能和

可靠性。

D型触发器的应用电路原理1. 什么是D型触发器D型触发器是数字逻辑电路中最常用的触发器之一。

它被用于存储和传输一个信号,信号可由输入而改变,并且只有在时钟的上升沿才会传输到输出。

D型触发器具有一个数据输入(D)、时钟输入(CLK)和输出(Q),并且有一个使能输入(EN)。

2. D型触发器的基本应用D型触发器的基本应用是存储和传输一个信号。

当时钟信号(CLK)的上升沿到来时,如果使能输入(EN)为高电平,D型触发器会将数据输入(D)的值传输到输出(Q)。

如果使能输入(EN)为低电平,则不会将数据输入(D)的值传输到输出(Q)。

D型触发器的应用电路原理如下:•输入信号(D)通过逻辑门电路得到使能信号(EN)。

•时钟信号(CLK)与使能信号(EN)同时输入到D型触发器。

•当时钟信号(CLK)的上升沿到来时,根据使能信号(EN)的电平状态,D型触发器将数据输入(D)的值传输到输出(Q)。

3. D型触发器的应用示例下面是一些常见的D型触发器应用示例:3.1 数据锁存器D型触发器可以用作数据锁存器。

在这种应用中,使能输入(EN)常常被保持为高电平,这样D型触发器就可以存储并输出数据输入(D)的值,直到时钟信号(CLK)的下一个上升沿到来。

数据锁存器常用于缓存输入数据,以便在需要时传递到下一个电路模块。

3.2 时序电路D型触发器也可用于构建时序电路,如计数器和状态机。

在这种应用中,D型触发器的输出(Q)与逻辑电路中的其他输入端相连,形成反馈回路。

3.3 时钟分频器D型触发器可以通过配置适当的电路来实现时钟分频功能。

当时钟信号(CLK)的频率较高时,通过设置适当的逻辑电路,可以使D型触发器的输出(Q)频率降低到所需的分频倍数。

3.4 数据同步器当需要将异步输入信号转换为同步信号时,D型触发器可以被用作数据同步器。

在这种应用中,异步输入信号通常被连接到D型触发器的数据输入(D),而时钟信号(CLK)则用作使能输入(EN)。

边沿D 触发器:负跳沿触发的主从触发器工作时,在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

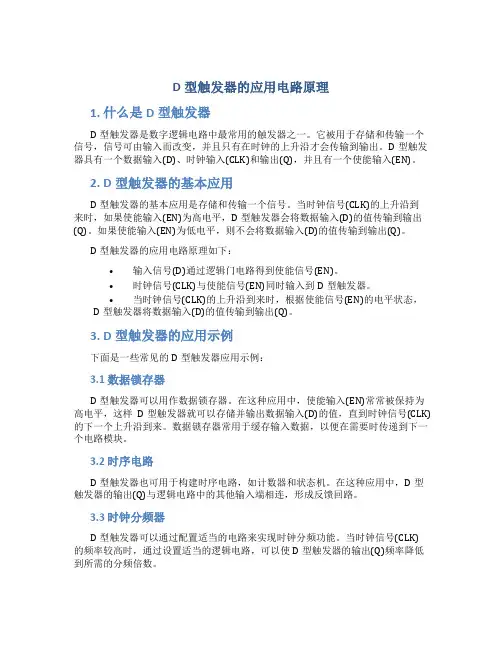

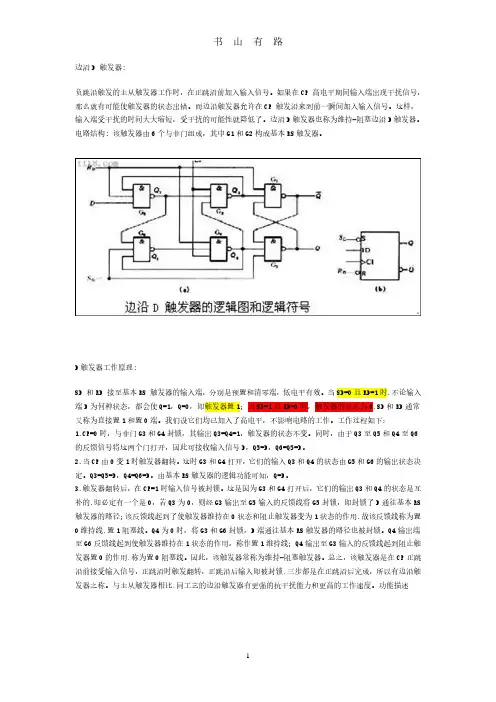

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

D触发器工作原理:SD 和RD 接至基本RS 触发器的输入端,分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。

Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。

因此,该触发器常称为维持-阻塞触发器。

总之,该触发器是在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称。

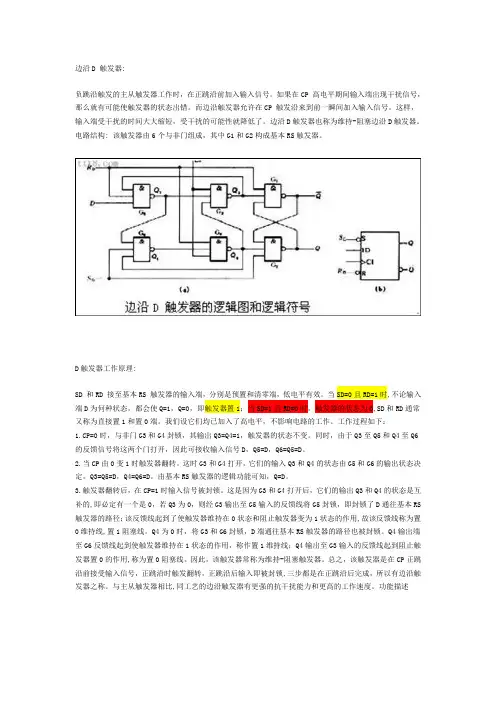

边沿D触发器:负跳沿触发的主从触发器工作时,在正跳沿前加入输入信号。

如果在CP高电平期间输入端出现干扰信号,那么就有可能使触发器的状态岀错。

而边沿触发器允许在CP触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器电路结构:该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

边沿D触发器的逻辑图和逻辑符号D触发器工作原理SD和RD接至基本RS触发器的输入端,分别是预置和清零端,低电平有效。

当SD=O且RD=1时,不论输入端D 为何种状态,都会使Q=1, Q=0,即触发器置1 ; 当SD=1且RD=O时,触发器的状态为O,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1. CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D Q6=Q5=D2. 当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D Q4=Q6=D由基本RS触发器的逻辑功能可知,Q=D3. 触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。

Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输岀至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。

因此,该触发器常称为维持-阻塞触发器。

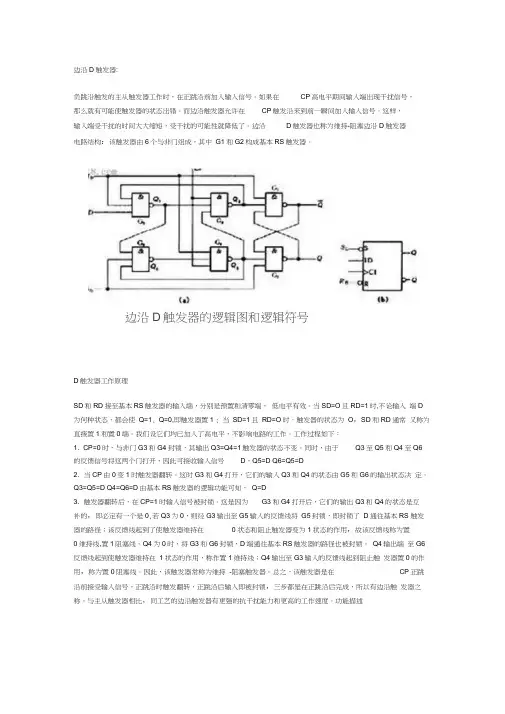

边沿D 触发器:负跳沿触发的主从触发器工作时,在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

D触发器工作原理:SD 和RD 接至基本RS 触发器的输入端,分别是预置和清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。

Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。

因此,该触发器常称为维持-阻塞触发器。

总之,该触发器是在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称。

d触发器电路工作原理一、引言d触发器是数字电路中常用的一种基本触发器。

它能够存储一个位的状态,并在时钟信号的作用下进行状态的改变。

d触发器在各种数字电路和计算机系统中都有广泛的应用,如存储器、寄存器、计数器等。

因此,了解d触发器电路的工作原理对于理解和设计数字电路至关重要。

二、d触发器电路结构d触发器电路由几个关键的部分组成,包括输入端d、时钟信号端clk、输出端q和反相输出端q'。

其中,d端用于输入数据,clk端用于提供时钟信号,q端用于输出数据,q'端用于输出数据的反相信号。

d触发器电路的基本结构如下所示:(这里不要输出图片链接)d触发器电路的工作原理可以通过以下几个步骤来解释:1. 初始状态:假设d触发器电路处于初始状态,q端和q'端都处于特定的状态,且与输入d无关。

2. 时钟信号作用:当时钟信号clk发生变化时,d触发器电路开始工作。

3. 数据输入:在时钟信号作用下,如果输入端d的电平为高电平,则d触发器会将这个高电平的数据存储到内部的存储单元中;如果输入端d的电平为低电平,则d触发器会将之前存储的数据保持不变。

4. 数据输出:根据输入端d的电平,d触发器将存储的数据通过输出端q输出,同时通过反相输出端q'输出数据的反相信号。

5. 状态保持:一旦数据存储到d触发器中,无论输入端d的电平如何变化,d触发器都会保持存储的数据,直到下一次时钟信号的作用。

四、d触发器电路的应用d触发器电路在数字电路和计算机系统中有着广泛的应用。

以下是一些常见的应用场景:1. 存储器:d触发器被广泛用于存储器中,用于存储和读取数据。

2. 寄存器:多个d触发器可以组成寄存器,用于存储和传输多位数据。

3. 计数器:d触发器可以用于构建计数器电路,实现数字计数功能。

4. 时序电路:d触发器可以用于构建时序电路,实现各种时序逻辑功能。

五、总结d触发器电路是数字电路中常用的一种基本触发器,具有存储一个位的能力,并能在时钟信号的作用下进行状态的改变。

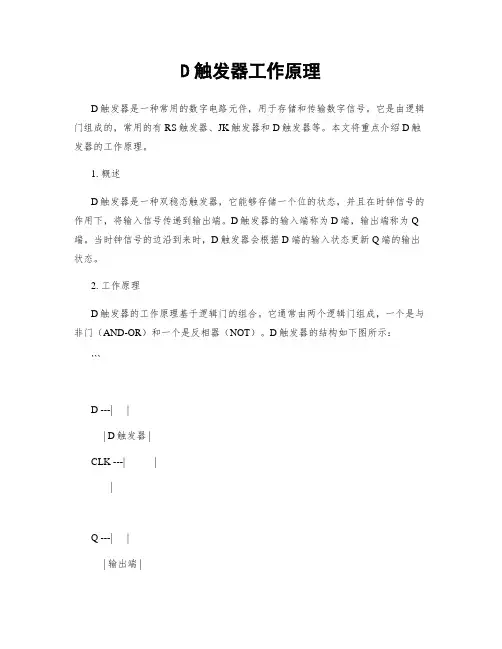

D触发器工作原理D触发器是一种常用的数字电路元件,用于存储和传输数字信号。

它是由逻辑门组成的,常用的有RS触发器、JK触发器和D触发器等。

本文将重点介绍D触发器的工作原理。

1. 概述D触发器是一种双稳态触发器,它能够存储一个位的状态,并且在时钟信号的作用下,将输入信号传递到输出端。

D触发器的输入端称为D端,输出端称为Q 端。

当时钟信号的边沿到来时,D触发器会根据D端的输入状态更新Q端的输出状态。

2. 工作原理D触发器的工作原理基于逻辑门的组合。

它通常由两个逻辑门组成,一个是与非门(AND-OR)和一个是反相器(NOT)。

D触发器的结构如下图所示:```______D ---| || D触发器 |CLK ---|______||______Q ---| || 输出端 |Q'---|______|```当时钟信号CLK为高电平时,D触发器处于工作状态。

D触发器的输入端D 可以接收一个位的输入信号,当CLK的上升沿到来时,D触发器会将输入信号传递到输出端Q。

如果输入信号为高电平,则输出端Q也为高电平;如果输入信号为低电平,则输出端Q为低电平。

当时钟信号CLK为低电平时,D触发器处于保持状态。

此时,无论输入信号如何变化,输出端Q的状态都不会改变,即保持之前的状态。

3. 应用场景D触发器广泛应用于数字电路中,常见的应用场景有以下几种:3.1. 时序电路D触发器可以用于构建各种时序电路,如计数器、寄存器等。

通过时钟信号的作用,D触发器可以实现数据的存储和传输,从而实现各种复杂的时序逻辑功能。

3.2. 数据存储D触发器可以用于数据存储。

当输入信号稳定时,D触发器可以将输入信号存储在输出端,直到时钟信号的边沿到来才更新输出状态。

这种特性使得D触发器可以用于存储数据,如RAM(随机存取存储器)等。

3.3. 信号同步D触发器可以用于信号同步。

在数字电路中,由于各个模块的时钟信号可能存在不同步的情况,为了保证数据的正确传输和处理,可以使用D触发器将信号同步到相同的时钟信号下,从而避免数据错误。

D触发器工作原理D触发器是数字电路中常用的一种触发器,用于存储和传输数字信号。

它由两个互补反相的输出端和一个输入端组成。

D触发器的工作原理是根据输入信号的变化来改变输出信号的状态。

D触发器有两种常见的类型:D型正沿触发器和D型负沿触发器。

这两种类型的触发器在输入信号的边沿上触发输出信号的变化。

D型正沿触发器在输入信号的上升沿触发输出信号的变化,而D型负沿触发器在输入信号的下降沿触发输出信号的变化。

D触发器的工作原理可以简单描述如下:1. D触发器的输入端被连接到输入信号源,该信号源可以是一个逻辑门、一个计数器或者其他数字电路的输出端。

2. 当输入信号发生变化时,D触发器会根据触发器的类型,在输入信号的边沿上触发输出信号的变化。

3. 当输入信号发生变化时,D触发器的输出端会根据触发器的类型和输入信号的变化,改变其输出状态。

4. D触发器的输出状态可以保持不变,直到下一个输入信号的边沿触发输出信号的变化。

D触发器的工作原理可以通过以下示意图来说明:```_______D ----| || D |----- QCLK ---| 触 || 发 |----- Q'| 器 ||_______|```在上述示意图中,D表示输入信号,CLK表示时钟信号,Q表示输出信号,Q'表示输出信号的补码。

D触发器的工作原理可以进一步解释如下:- 当时钟信号CLK的边沿触发D触发器时,如果D触发器为D型正沿触发器,则在CLK的上升沿时,D触发器会将输入信号D的值传递到输出信号Q上,并将Q'的值设置为Q的补码。

- 当时钟信号CLK的边沿触发D触发器时,如果D触发器为D型负沿触发器,则在CLK的下降沿时,D触发器会将输入信号D的值传递到输出信号Q上,并将Q'的值设置为Q的补码。

D触发器的工作原理使得它在数字电路中具有重要的应用。

例如,D触发器可以用于存储和传输数据,实现计数器和寄存器等功能。

此外,D触发器还可以用于时序电路中,用于控制和同步数字信号的传输和处理。

D触发器工作原理标题:D触发器工作原理引言概述:D触发器是数字电路中常用的一种触发器,具有重要的工作原理。

了解D触发器的工作原理对于理解数字电路的设计和应用非常重要。

本文将详细介绍D触发器的工作原理。

一、D触发器的基本结构1.1 D触发器的输入端D触发器有两个输入端,一个是数据输入端D,另一个是时钟输入端CLK。

1.2 D触发器的输出端D触发器有一个输出端Q,用于输出存储在触发器中的数据。

1.3 D触发器的控制端D触发器通常还有一个清零端CLR和一个置位端SET,用于对触发器进行清零和置位操作。

二、D触发器的工作原理2.1 数据输入当时钟输入端CLK的信号为上升沿时,D触发器会将数据输入端D的数据存储到触发器中。

2.2 存储数据存储在D触发器中的数据会在时钟信号的作用下保持不变,直到下一个时钟信号的到来。

2.3 输出数据当时钟信号为下降沿时,D触发器会将存储的数据输出到输出端Q。

三、D触发器的时序图3.1 时钟信号时钟信号通常是一个周期性的信号,用于控制D触发器的数据输入和输出。

3.2 数据输入数据输入端D的数据在时钟信号的上升沿时被存储到D触发器中。

3.3 数据输出数据输出端Q的数据在时钟信号的下降沿时被输出。

四、D触发器的应用4.1 数据存储D触发器常用于存储数据,如寄存器和存储器等。

4.2 时序控制D触发器可以用于时序控制,如时序逻辑电路和状态机等。

4.3 信号同步D触发器可以用于信号同步,解决时序问题和数据传输问题。

五、D触发器的优缺点5.1 优点D触发器具有简单的结构和易于控制的特点,适合于数字电路中的各种应用。

5.2 缺点D触发器在一些特殊情况下可能会浮现时序问题和数据错误,需要合理设计和应用。

总结:D触发器是数字电路中重要的元件,具有独特的工作原理和广泛的应用。

了解D触发器的工作原理有助于深入理解数字电路的设计和应用,提高数字电路设计的效率和可靠性。

边沿D 触发器: 之杨若古兰创作负跳沿触发的主从触发器工作时,在正跳沿前加入输入旌旗灯号.如果在CP 高电平期间输入端出现干扰旌旗灯号,那么就有可能使触发器的形态出错.而边沿触发器答应在CP 触发沿来到前一瞬间加入输入旌旗灯号.如许,输入端受干扰的时间大大缩短,受干扰的可能性就降低了.边沿D触发器也称为保持-梗阻边沿D触发器. 电路结构: 该触发器由6个与非门构成,其中G1和G2构成基本RS触发器.D触发器工作道理:SD 和RD 接至基本RS 触发器的输入端,分别是预置和清零端,低电平无效.当SD=0且RD=1时,不管输入端D为什么种形态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的形态为0,SD和RD通常又称为直接置1和置0端.我们设它们均已加入了高电平,不影响电路的工作.工作过程如下: 1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的形态不变.同时,因为Q3至Q5和Q4至Q6的反馈旌旗灯号将这两个门打开,是以可接收输入旌旗灯号D,Q5=D,Q6=Q5=D. 2.当CP由0变1时触发器翻转.这时候G3和G4打开,它们的输入Q3和Q4的形态由G5和G6的输出形态决定.Q3=Q5=D,Q4=Q6=D.由基本RS触发器的逻辑功能可知,Q=D. 3.触发器翻转后,在CP=1时输入旌旗灯号被封锁.这是因为G3和G4打开后,它们的输出Q3和Q4的形态是互补的,即肯定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器保持在0形态和禁止触发器变成1形态的感化,故该反馈线称为置0保持线,置1梗阻线.Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁.Q4输出端至G6反馈线起到使触发器保持在1形态的感化,称作置1保持线;Q4输出至G3输入的反馈线起到禁止触发器置0的感化,称为置0梗阻线.是以,该触发器常称为保持-梗阻触发器.总之,该触发器是在CP正跳沿前接受输入旌旗灯号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称.与主从触发器比拟,同工艺的边沿触发器有更强的抗干扰能力和更高的工作速度.功能描述2.特征方程 Qn+1=D3形态转移图脉冲特性: 1.建立时间:由下图保持梗阻触发器的电路可见,CP 旌旗灯号是加到门G3和G4上的,因此在CP上升沿到达之前门G5和G6输出端的形态必须波动地建立起来.输入旌旗灯号到达D端当前,要经过一级门电路的传输延迟时间G5的输出形态才干建立起来,而G6的输出形态须要经过两级门电路的传输延迟时间才干建立,是以D端的输入旌旗灯号必须先于CP的上升沿到达,而且建立时间应满足: tset≥2tpd. 2.坚持时间:由下图可知,为实现边沿触发,应包管CP=1期间门G6的输出形态不变,不受D端形态变更的影响.为此,在D=0的情况下,当CP上升沿到达当前还要等门G4输出的低电平返回到门G6的输入端当前,D端的低电平才答应改变.是以输入低电平旌旗灯号的坚持时间为tHL≥tpd.在 D=1的情况下,因为CP上升沿到达后G3的输出将G4封锁,所以不请求输入旌旗灯号继续坚持不变,故输入高电平旌旗灯号的坚持时间tHH=0. 3.传输延迟时间:由图工作波形图不难推算出,从CP上升沿到达时开始计算,输出由高电平变成低电平的传输延迟时间tPHL和由低电平变成高电平的传输延迟时间tPLH分别是:tPHL=3tpd tPLH=2tpd保持和梗阻D触发器的电路和动态波形4.最高时钟频率:为包管由门G1~G4构成的同步RS触发器能可靠地翻转,CP高电平的持续时间应大于 tPHL,时钟旌旗灯号高电平的宽度tWH应大于tPHL.而为了鄙人一个CP上升沿到达之前确保门G5和G6新的输出电平得以波动地建立,CP低电平的持续时间不该小于门G4的传输延迟时间和tset之和,即时钟旌旗灯号低电平的宽度tWL≥tset+tpd,是以得到:在实际集成触发器中,每个门传输时间是分歧的,而且作了分歧方式的简化,是以上面讨论的结果只是一些定性的物理概念.其真实参数由实验测定. 综上所述,对边沿D触发器归纳为以下几点: 1.边沿D触发器具有接收并记忆旌旗灯号的功能,又称为锁存器;2.边沿D触发器属于脉冲触发方式;3.边沿D触发器不存在束缚条件和一次变更景象,抗干扰功能好,工作速度快。

同步D触发器电路结构和逻辑符号

同步RS触发器在R、S同时为1且同时失效后,触发器状态不确定,说明其功能仍不完善。

D触发器针对这一问题作出改进,解决了触发器状态不确定的问题。

由于只要令R、S不同时为1,触发器就不会出现状态不稳定,最简单的方法就是令S=/R,此时仅将S作为输入端(用D表示),就得到了D触发器。

仍然是由RS触发器演变而来,是RS 触发器S=/R的特例,其电路结构和逻辑符号如图所示。

图同步D触发器

工作原理如下:

①CP=0期间,与非门G3、G4被封锁,/RD=1,/SD=1。

因此,无论输入信号R、S如何变化,都不会影响触发器的输出Q和/Q,即触发器状态保持不变。

②CP=1期间,与非门G3、G4打开,触发器输出状态随D而变化,完成置0、置1和保持等三种逻辑功能。

边沿D 触发器:

负跳沿触发的主从触发器工作时,在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1与G2构成基本RS触发器。

D触发器工作原理:

SD 与RD 接至基本RS 触发器的输入端,分别就是预置与清零端,低电平有效。

当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD与RD通常又称为直接置1与置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:

1、CP=0时,与非门G3与G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5与Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2、当CP由0变1时触发器翻转。

这时G3与G4打开,它们的输入Q3与Q4的状态由G5与G6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3、触发器翻转后,在CP=1时输入信号被封锁。

这就是因为G3与G4打开后,它们的输出Q3与Q4的状态就是互补的,即必定有一个就是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态与阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

Q4为0时,将G3与G6封锁,D端通往基本RS触发器的路径也被封锁。

Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。

因此,该触发器常称为维持-阻塞触发器。

总之,该触发器就是在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都就是在正跳沿后完成,所以有边沿触发器之称。

与主从触发器相比,同工艺的边沿触发器有更强的抗干扰能力与更高的工作速度。

功能描述

2、特征方程 Qn+1=D

3状态转移图

脉冲特性:

1、建立时间:由下图维持阻塞触发器的电路可见,CP信号就是加到门G3与G4上的,因而在CP上升沿到达之前门G5与G6输出端的状态必须稳定地建立起来。

输入信号到达D端以后,要经过一级门电路的传输延迟时间G5的输出状态才能建立起来,而G6的输出状态需要经过两级门电路的传输延迟时间才能建立,因此D 端的输入信号必须先于CP的上升沿到达,而且建立时间应满足: tset≥2tpd。

2、保持时间:由下图可知,为实现边沿触发,应保证CP=1期间门G6的输出状态不变,不受D端状态变化的影响。

为此,在D=0的情况下,当CP上升沿到达以后还要等门G4输出的低电平返回到门G6的输入端以后,D 端的低电平才允许改变。

因此输入低电平信号的保持时间为tHL≥tpd。

在 D=1的情况下,由于CP上升沿到达后G3的输出将G4封锁,所以不要求输入信号继续保持不变,故输入高电平信号的保持时间tHH=0。

3、传输延迟时间:由图工作波形图不难推算出,从CP上升沿到达时开始计算,输出由高电平变为低电平的传输延迟时间tPHL与由低电平变为高电平的传输延迟时间tPLH分别就是:tPHL=3tpd tPLH=2tpd

维持与阻塞D触发器的电路与动态波形

4、最高时钟频率:为保证由门G1~G4组成的同步RS触发器能可靠地翻转,CP高电平的持续时间应大于 tPHL,时钟信号高电平的宽度tWH应大于tPHL。

而为了在下一个CP上升沿到达之前确保门G5与G6新的输出电平得以稳定地建立,CP低电平的持续时间不应小于门G4的传输延迟时间与tset之与,即时钟信号低电平的宽度tWL≥tset+tpd,因此得到:

在实际集成触发器中,每个门传输时间就是不同的,并且作了不同形式的简化,因此上面讨论的结果只就是

一些定性的物理概念。

其真实参数由实验测定。

综上所述,对边沿D触发器归纳为以下几点:

1、边沿D触发器具有接收并记忆信号的功能,又称为锁存器;

2、边沿D触发器属于脉冲触发方式;

3、边沿D触发器不存在约束条件与一次变化现象,抗干扰性能好,工作速度快。