数字锁相环 逆变器 程序

- 格式:doc

- 大小:69.00 KB

- 文档页数:16

光伏逆变器锁相环实现方法以光伏逆变器锁相环实现方法为题,我们将介绍光伏逆变器锁相环的原理和实现方法。

光伏逆变器是将太阳能光伏电池板产生的直流电转换为交流电的设备。

而锁相环(Phase-Locked Loop,简称PLL)是一种常用的控制电路,用于将输入信号的相位与参考信号的相位保持同步。

光伏逆变器的锁相环主要用于控制电网连接,确保光伏电池板产生的交流电与电网的频率和相位保持一致。

下面我们将详细介绍光伏逆变器锁相环的实现方法。

光伏逆变器锁相环的核心部分是相位比较器(Phase Comparator)和低通滤波器(Low Pass Filter)。

相位比较器用于比较光伏电池板产生的交流电信号与参考信号的相位差,而低通滤波器则用于平滑输出信号。

通过不断调整逆变器的控制参数,使相位比较器输出的误差信号趋近于零,从而实现相位同步。

为了实现光伏逆变器锁相环的控制,需要采集光伏电池板产生的交流电信号和参考信号。

一般情况下,光伏电池板产生的交流电信号通过传感器采集,而参考信号可以通过电网提供或者使用外部稳定的时钟信号。

在实际应用中,为了提高锁相环的性能,可以采用增量式锁相环(Incremental Phase-Locked Loop,简称IPLL)。

增量式锁相环通过对相位差进行积分,可以提高相位比较器的输出精度和稳定性。

在光伏逆变器锁相环的实现中,还需要考虑噪声和干扰的抑制。

为了减小噪声和干扰对锁相环的影响,可以采用滤波器和抗干扰技术。

同时,还可以采用自适应控制算法来实时调整锁相环的参数,以适应不同的工作环境。

总结起来,光伏逆变器锁相环是一种重要的控制电路,用于保持光伏电池板产生的交流电与电网的频率和相位同步。

实现光伏逆变器锁相环的方法包括相位比较器和低通滤波器的设计、采集光伏电池板和参考信号、使用增量式锁相环和抑制噪声与干扰等。

通过合理设计和调整锁相环的参数,可以提高光伏逆变器的性能和稳定性,实现高效的光伏发电。

锁相环逆变

锁相环(Phase-Locked Loop,简称PLL)和逆变器(Inverter)是电子领域中两个不同的概念,它们通常在不同的应用中使用。

1.锁相环(PLL):PLL 是一种电子电路,通常用于频率合成、时

钟恢复和相位同步等应用。

它的基本原理是通过比较输入信号

和一个内部振荡器的输出,然后调整振荡器的频率和相位,使

输出信号与输入信号保持稳定的相位关系。

PLL 可用于从不稳

定的时钟信号中生成稳定的时钟,或者用于将信号的频率锁定

到特定的参考频率。

在通信系统、数字电路和射频应用中广泛

使用。

2.逆变器(Inverter):逆变器是一种电子设备,用于将直流电(DC)

转换为交流电(AC)。

它通常用于太阳能发电系统、风能发电系

统、电动汽车、UPS(不间断电源)等应用中,将储存的直流电

能或可再生能源的直流输出转换为可用于电网或电器设备的交

流电。

逆变器可以有不同的类型,如脉宽调制逆变器、谐波逆

变器等,具体类型取决于应用和性能需求。

这两个概念在电子领域中有不同的应用领域,通常不直接相关。

锁相环用于时钟和信号处理,而逆变器用于能源转换和电源供应。

全数字锁相环25 全数字锁相环FPGA实现的总结在本设计中的⼀阶全数字锁相环使⽤Mentor公司的ModelSim6.0软件进⾏设计的功能仿真以及Altera公司的QuartusII7.2软件时序仿真并且进⾏设计综合,并采⽤Altera的cyclone系列的EP1C6Q240C8 FPGA器件实现。

实验测试结果表明:本设计中DPLL时钟可达到10MHz,性能较⾼;⽽使⽤了256逻辑单元,占⽤资源很少。

下⾯给出详细描述全数字锁相环的⼯作过程。

(1)当环路失锁时,异或门鉴相器⽐较输⼊信号(fin)和输出信号(fout)之间的相位差异,并产⽣K变模可逆计数器的计数⽅向控制信号(dnup);(2) K变模可逆计数器根据计数⽅向控制信号(dnup)调整计数值,dnup为⾼进⾏减计数,并当计数值到达0时,输出借位脉冲信号(borrow);为低进⾏加计数,并当计数值达到预设的K模值时,输出进位脉冲信号(carryo);(3)脉冲加减电路则根据进位脉冲信号(carryo)和借位脉冲信号(borrow)在电路输出信号(idout)中进⾏脉冲的增加和扣除操作,来调整输出信号的频率;(4)重复上⾯的调整过程,当环路进⼊锁定状态时,异或门鉴相器的输出se为⼀占空⽐50%的⽅波,⽽K变模可逆计数器则周期性地产⽣进位脉冲输出carryo和借位脉冲输出borrow,导致脉冲加减电路的输出idout周期性的加⼊和扣除半个脉冲。

本次设计中开始遇到了很多困难,开始通过多⽅⾯查找资料并了解全数字锁相环的原理及⽅案,锁相环⼀般都是模拟的居多,关于数字的资料⽐较少,所以查阅资料花了⼤量时间;在确定全数字锁相环设计原理后,开始学习硬件描述语⾔verilog HDL,学习FPGA器件的使⽤,学习Mentor公司的ModelSim6.0软件来作功能仿真以及⽤Altera公司的QuartusII7.2软件进⾏时序仿真以及下载配置的等问题。

附录1.数字锁相环的顶层模块module pll_top (fin,fout,se,clk,reset,enable,Kmode,fin_dac,fout_dac);input fin,clk; //clk时钟100ns(10MHZ)input reset,enable; //reset⾼电平复位,enable⾼电平有效input [2:0]Kmode; //滤波计数器的计数模值设定output fout; //fout是锁频锁相输出output [7:0]fin_dac,fout_dac;//fin_dac,fout_dac分别是两个输⼊输出信号经过数模dac的输出output se;wire idout,reset,ca,bo;wire [14:0]N;xormy u1(.a(fin),.b(fout),.y(se));Kcounter u2(.Kclock(clk),.reset(reset),.dnup(se),.enable(enable),.Kmode(Kmode),.carryo(ca),.borrow(bo)); IDCounter u3(.IDclock(clk),.reset(reset),.inc(ca),.dec(bo),.IDout(idout));counter_N u4(.clk(clk), .fin(fin), .reset(reset), .count_N(N));div_N u5(.clkin(idout),.n(N),.reset(reset),.clkout(fout));dac u6(.clk(fin),.dout(fin_dac),.dd());dac u7(.clk(fout),.dout(fout_dac),.dd());endmodule2.异或门鉴相器模块module xormy(a,b,y);//异或门鉴相器input a,b;output y;reg y;always @(a or b)beginy=a^b;endendmodule3.K模计数器模块module KCounter(Kclock,reset,dnup,enable,Kmode,carryo,borrow);input dnup; //鉴相器输出的加减控制信号input enable; //可逆计数器计数允许信号,⾼电平有效input [2:0]Kmode; //计数器模值设置信号output carryo; //进位脉冲输出信号output borrow; //借位脉冲输出信号wire carryo,borrow;reg [8:0]Count; //可逆计数器reg [8:0]Ktop; //预设模值寄存器//根据计数器模值设置信号Kmode来设置预设模值寄存器的值always @(Kmode)begincase(Kmode)3'b001:Ktop<=7;3'b010:Ktop<=15;3'b011:Ktop<=31;3'b100:Ktop<=63;3'b101:Ktop<=127;3'b110:Ktop<=255;3'b111:Ktop<=511;default:Ktop<=15;endcaseend//根据鉴相器输出的加减控制信号dnup进⾏可逆计数器的加减运算always @(posedge Kclock or posedge reset)beginif(reset)Count<=0;else if(enable)beginif(!dnup)beginif(Count==Ktop)Count<=0;elsebeginif(Count==0)Count<=Ktop;elseCount<=Count-1;endendend//输出进位脉冲carry和借位脉冲borrowassign carryo=enable&(!dnup)&(Count==Ktop);assign borrow=enable&dnup&(Count==0);endmodule4.脉冲增减模块module IDCounter (IDclock,reset,inc,dec,IDout);//脉冲增减模块input IDclock,reset,inc,dec;output IDout;reg IDout;reg inc_new,dec_new,inc_pulse,dec_pulse;reg delayed,advanced,Tff;always @(posedge IDclock)beginif(!inc)begininc_new<=1;inc_pulse<=0;endelse if (inc_pulse)begininc_new<=0;inc_pulse<=0;inc_pulse<=1;inc_new<=0;endelsebegininc_pulse<=0;inc_new<=0;endendalways @(posedge IDclock) beginif(!dec)begindec_new<=1;dec_pulse<=0;endelse if (dec_pulse)begindec_new<=0;dec_pulse<=0;endelse if (dec&&dec_new) begindec_pulse<=1; dec_new<=0;endelsebegindec_pulse<=0;dec_new<=0;endendbegin Tff<=0; delayed<=1;advanced<=1; end elsebeginif (inc_pulse)begin advanced<=1;Tff<=!Tff; endelse if(dec_pulse)begin delayed<=1; Tff<=!Tff; endelse if (Tff==0)beginif(!advanced)Tff<=!Tff;else if(advanced)begin Tff<=Tff; advanced<=0; endendelsebeginif (!delayed)Tff<=!Tff;else if(delayed)begin Tff<=Tff;delayed<=0; endendendendalways @(IDclock or Tff)beginif (Tff)IDout=0;elsebeginif(IDclock)IDout=0;elseendendmodule5.N分频参数控制模块module counter_N (clk, fin, reset, count_N);//利⽤clk对fin脉冲的测量并给出N值 input clk, fin, reset;output [14:0] count_N;reg [14:0] count_N;reg [15:0] cnt;reg cnt_en;reg load;wire cnt_clr;always @ (posedge fin )//fin上升沿到的时候,产⽣各种标志以便后⾯控制beginif (reset)begincnt_en=0;load=1;endelsebegincnt_en=~cnt_en;load=~cnt_en;endendassign cnt_clr=~(~fin & load);always @(posedge clk or negedge cnt_clr)beginif (!cnt_clr)cnt=0;else if (cnt_en)cnt=0;elsecnt=cnt+1;endendalways @ (posedge load)begincount_N=cnt/2; //这⾥取fin周期的⼀半endendmodule6.N分频器模块module div_N (clkin,n,reset,clkout); //N分频模块 input clkin,reset;input [14:0] n;output clkout;reg clkout;integer count;always@(posedge clkin)if(reset)beginclkout=0;count=0;endelsebeginif(count>=(n/2)-1)begin clkout<=~clkout;count<=0;endelsecount<=count+1;endendmoduleoutput[7:0] dout;output[7:0] dd;reg [7:0] dout;reg [7:0] dd;reg [7:0] d;reg [5:0] q;always @(posedge clk)beginif (q<63 ) q<=q+1; else q<=0; endalways@( q )begincase(q)00: d<=255; 01: d<=254; 02: d<=252; 03: d<=249; 04: d<=245; 05: d<=239; 06: d<=233; 07: d<=225; 08: d<=217; 09: d<=207; 10: d<=197; 11: d<=186; 12: d<=174; 13: d<=162; 14: d<=150; 15: d<=137; 16: d<=124; 17: d<=112; 18: d<=99; 19: d<=87; 20: d<=75; 21: d<=64; 22: d<=53; 23: d<=43;24: d<=34; 25: d<=26; 26: d<=19; 27: d<=13;28: d<=8; 29: d<=4; 30: d<=1; 31: d<=0;32: d<=0; 33: d<=1; 34: d<=4; 35: d<=8;36: d<=13; 37: d<=19; 38: d<=26; 39: d<=34;40: d<=43; 41: d<=53; 42: d<=64; 43: d<=75;44: d<=87; 45: d<=99; 46: d<=112; 47: d<=124; 48: d<=137; 49: d<=150; 50: d<=162; 51: d<=174; 52: d<=186; 53: d<=197; 54: d<=207; 55: d<=217; 56: d<=225; 57: d<=233; 58: d<=239; 59: d<=245; 60: d<=249; 61: d<=252; 62: d<=254; 63: d<=255; default : d<=0;endcasedd<=d;end。

弱电网条件下锁相环对LCL型并网逆变器稳定性的影响研究及锁相环参数设计1. 本文概述随着可再生能源的广泛应用和电力电子技术的发展,LCL型并网逆变器在弱电网条件下的稳定性问题引起了广泛关注。

本文旨在研究弱电网条件下锁相环(PhaseLocked Loop, PLL)对LCL型并网逆变器稳定性的影响,并提出一种有效的锁相环参数设计方法。

本文分析了弱电网条件下LCL型并网逆变器的工作原理,明确了锁相环在系统稳定性中的关键作用。

接着,详细探讨了锁相环对系统稳定性的影响机制,包括其对系统动态响应、谐波抑制以及系统抗干扰能力的影响。

进一步地,本文针对锁相环参数设计问题,提出了一种基于系统稳定性和动态性能综合优化的参数设计方法。

该方法不仅考虑了锁相环的快速性和准确性,还兼顾了系统在弱电网条件下的稳定性和鲁棒性。

通过仿真和实验验证,本文所提出的锁相环参数设计方法在提高LCL型并网逆变器在弱电网条件下的稳定性方面具有显著效果。

本文的研究成果对于促进可再生能源的高效利用和电网稳定运行具有重要意义,并为类似系统的设计和优化提供了理论指导和实践参考。

2. 型并网逆变器与锁相环的基本原理在弱电网条件下探讨锁相环(PhaseLocked Loop, PLL)对LCL 型并网逆变器稳定性的影响以及锁相环参数设计,首先需要理解并网逆变器和锁相环的基本原理。

LCL型并网逆变器是一种广泛应用在新能源发电系统中的关键设备,特别是光伏和风能发电系统中。

它的结构主要包括逆变器、LCL 滤波器和并网接口。

LCL滤波器由串联的电感(L)和两个并联的电容(C)组成,这种配置能显著减少输出电流的谐波含量,提高电能质量,同时降低了对电网的电磁干扰。

LCL滤波器引入了固有的三阶动态特性,可能会导致谐振现象,对系统稳定性构成挑战。

为了保证并网逆变器能在宽频范围内稳定且高效地工作,需要设计有效的电流控制器,并结合电容电流反馈实现有源阻尼,以抑制LCL滤波器产生的谐振。

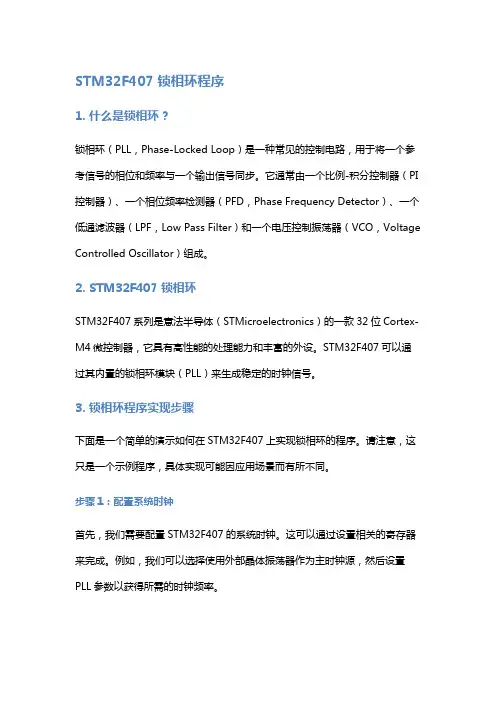

STM32F407 锁相环程序1. 什么是锁相环?锁相环(PLL,Phase-Locked Loop)是一种常见的控制电路,用于将一个参考信号的相位和频率与一个输出信号同步。

它通常由一个比例-积分控制器(PI 控制器)、一个相位频率检测器(PFD,Phase Frequency Detector)、一个低通滤波器(LPF,Low Pass Filter)和一个电压控制振荡器(VCO,Voltage Controlled Oscillator)组成。

2. STM32F407 锁相环STM32F407系列是意法半导体(STMicroelectronics)的一款32位Cortex-M4微控制器,它具有高性能的处理能力和丰富的外设。

STM32F407可以通过其内置的锁相环模块(PLL)来生成稳定的时钟信号。

3. 锁相环程序实现步骤下面是一个简单的演示如何在STM32F407上实现锁相环的程序。

请注意,这只是一个示例程序,具体实现可能因应用场景而有所不同。

步骤1:配置系统时钟首先,我们需要配置STM32F407的系统时钟。

这可以通过设置相关的寄存器来完成。

例如,我们可以选择使用外部晶体振荡器作为主时钟源,然后设置PLL参数以获得所需的时钟频率。

步骤2:初始化锁相环模块在这一步中,我们需要初始化锁相环模块,配置相关的寄存器以使其工作在我们所需的方式下。

这包括设置PLL输入时钟源、选择输出时钟的倍频因子、配置PLL分频因子等。

步骤3:等待锁定在配置锁相环之后,我们需要等待锁相环模块稳定并锁定到我们所需的频率。

在这个过程中,我们可以使用相关的状态位或中断来监测锁相环的状态,以便在锁定之前等待。

步骤4:配置输出时钟一旦锁相环模块稳定并锁定到所需的频率,我们就可以配置输出时钟。

这可以通过设置相关的寄存器来实现,以使其输出到我们所需的GPIO引脚或其他外设。

4. 总结在STM32F407上实现锁相环的程序可以通过配置系统时钟、初始化锁相环模块、等待锁定和配置输出时钟这几个步骤来完成。

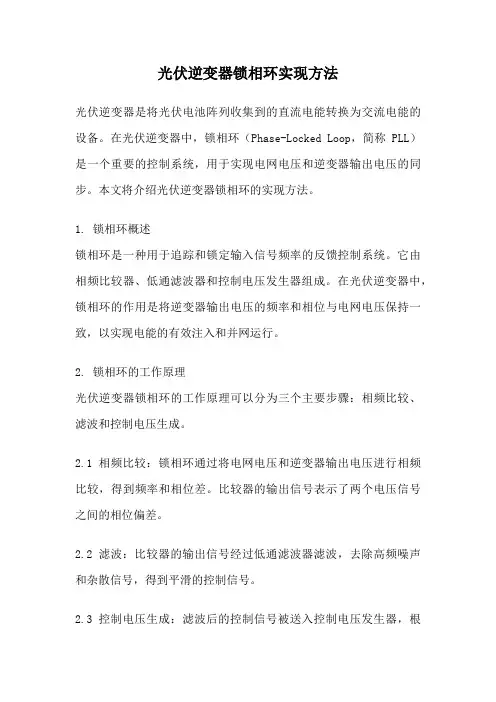

光伏逆变器锁相环实现方法光伏逆变器是将光伏电池阵列收集到的直流电能转换为交流电能的设备。

在光伏逆变器中,锁相环(Phase-Locked Loop,简称PLL)是一个重要的控制系统,用于实现电网电压和逆变器输出电压的同步。

本文将介绍光伏逆变器锁相环的实现方法。

1. 锁相环概述锁相环是一种用于追踪和锁定输入信号频率的反馈控制系统。

它由相频比较器、低通滤波器和控制电压发生器组成。

在光伏逆变器中,锁相环的作用是将逆变器输出电压的频率和相位与电网电压保持一致,以实现电能的有效注入和并网运行。

2. 锁相环的工作原理光伏逆变器锁相环的工作原理可以分为三个主要步骤:相频比较、滤波和控制电压生成。

2.1 相频比较:锁相环通过将电网电压和逆变器输出电压进行相频比较,得到频率和相位差。

比较器的输出信号表示了两个电压信号之间的相位偏差。

2.2 滤波:比较器的输出信号经过低通滤波器滤波,去除高频噪声和杂散信号,得到平滑的控制信号。

2.3 控制电压生成:滤波后的控制信号被送入控制电压发生器,根据信号的大小和方向,控制电压发生器会产生相应的控制电压,用于调整逆变器的输出频率和相位,使其与电网电压保持同步。

3. 光伏逆变器锁相环的实现方法光伏逆变器锁相环的实现方法主要包括相频检测、滤波和控制电压生成。

3.1 相频检测:相频检测是通过比较电网电压和逆变器输出电压的相频差来实现的。

常用的相频检测方法有零交叉检测法和频率锁定环检测法。

零交叉检测法通过检测电压波形的零交叉点来确定相频差。

频率锁定环检测法则通过比较两个电压波形的周期性来确定相频差。

这两种方法各有特点,可以根据实际需求选择适合的方法。

3.2 滤波:滤波是为了去除相频检测过程中产生的高频噪声和杂散信号。

常用的滤波方法有低通滤波和带通滤波。

低通滤波器可以去除高频噪声,使得控制信号更加平滑。

带通滤波器则可以选择特定频率范围内的信号,对逆变器输出进行更精确的控制。

3.3 控制电压生成:控制电压生成是根据滤波后的控制信号来生成用于调整逆变器输出频率和相位的控制电压。

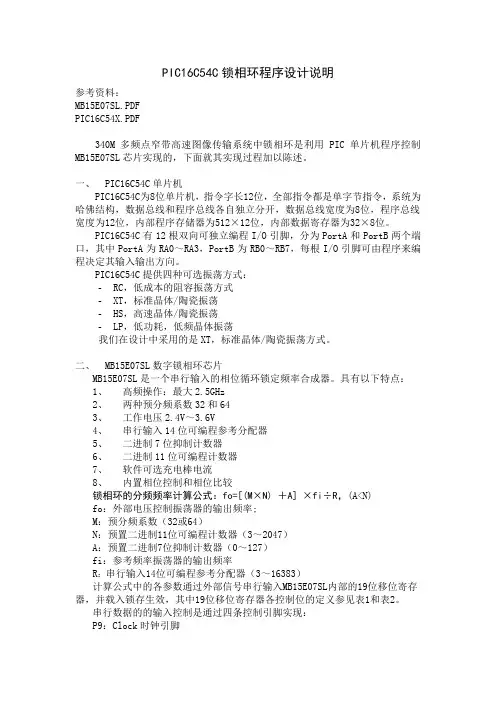

PIC16C54C锁相环程序设计说明参考资料:MB15E07SL.PDFPIC16C54X.PDF340M多频点窄带高速图像传输系统中锁相环是利用PIC单片机程序控制MB15E07SL芯片实现的,下面就其实现过程加以陈述。

一、PIC16C54C单片机PIC16C54C为8位单片机,指令字长12位,全部指令都是单字节指令,系统为哈佛结构,数据总线和程序总线各自独立分开,数据总线宽度为8位,程序总线宽度为12位,内部程序存储器为512×12位,内部数据寄存器为32×8位。

PIC16C54C有12根双向可独立编程I/O引脚,分为PortA和PortB两个端口,其中PortA为RA0~RA3,PortB为RB0~RB7,每根I/O引脚可由程序来编程决定其输入输出方向。

PIC16C54C提供四种可选振荡方式:-RC,低成本的阻容振荡方式-XT,标准晶体/陶瓷振荡-HS,高速晶体/陶瓷振荡-LP,低功耗,低频晶体振荡我们在设计中采用的是XT,标准晶体/陶瓷振荡方式。

二、MB15E07SL数字锁相环芯片MB15E07SL是一个串行输入的相位循环锁定频率合成器。

具有以下特点:1、高频操作:最大2.5GHz2、两种预分频系数32和643、工作电压2.4V~3.6V4、串行输入14位可编程参考分配器5、二进制7位抑制计数器6、二进制11位可编程计数器7、软件可选充电棒电流8、内置相位控制和相位比较锁相环的分频频率计算公式:fo=[(M×N) +A] ×fi÷R,(A<N)fo:外部电压控制振荡器的输出频率;M:预分频系数(32或64)N:预置二进制11位可编程计数器(3~2047)A:预置二进制7位抑制计数器(0~127)fi:参考频率振荡器的输出频率R:串行输入14位可编程参考分配器(3~16383)计算公式中的各参数通过外部信号串行输入MB15E07SL内部的19位移位寄存器,并载入锁存生效,其中19位移位寄存器各控制位的定义参见表1和表2。

锁相环调试流程锁相环(Phase-Locked Loop,简称PLL)是一种用于提供稳定的时钟和频率的电路。

在电子系统中,锁相环常用于时钟恢复、频率合成、时钟同步等应用场景。

为了确保锁相环正常工作,需要进行调试和优化。

本文将详细介绍锁相环调试的流程和步骤。

1. 确定基本参数在进行锁相环调试之前,首先需要确定一些基本参数,包括输入信号频率范围、输出信号频率范围、参考时钟频率等。

这些参数将决定锁相环的设计和优化方向。

2. 设计锁相环电路根据确定的基本参数,设计锁相环电路。

常见的锁相环电路包括比例积分器(PI)控制器、低通滤波器、振荡器等模块。

根据具体应用需求,还可以添加其他功能模块。

3. 搭建实验平台准备好所需的硬件设备和软件工具,并搭建实验平台。

硬件设备包括信号发生器、示波器、频谱分析仪等仪器;软件工具包括仿真软件和调试工具。

4. 初步测试将锁相环电路连接到实验平台上,进行初步测试。

输入一个稳定的参考时钟信号,观察输出信号的频率和相位。

如果输出信号与预期不符,需要检查电路连接是否正确,并调整基本参数。

5. 稳定性分析通过改变输入信号的频率和幅度,观察锁相环的稳定性。

稳定性分析可以通过观察输出信号的抖动情况来评估。

如果抖动较大或频率范围不稳定,可能需要调整锁相环参数或改进电路设计。

6. 频率合成和时钟恢复测试根据锁相环的具体应用场景,进行频率合成和时钟恢复的测试。

对于频率合成,输入一个参考时钟信号,并观察输出信号的频率和相位;对于时钟恢复,输入一个失真或噪声较大的时钟信号,并观察输出信号是否能够恢复为稳定的时钟。

7. 相位裕度测量在某些应用场景下,锁相环需要具有一定的相位裕度。

通过改变输入信号的相位,并观察输出信号与输入信号之间的相位差来评估相位裕度。

如果相位差超过预期范围,可能需要调整锁相环参数或改进电路设计。

8. 参数优化根据测试结果,对锁相环的参数进行优化。

常见的优化方法包括调整比例积分器(PI)控制器的参数、改变低通滤波器的截止频率等。

三相逆变器锁相环pll 工作原理三相逆变器是一种将直流电能转换为交流电能的设备。

它通常由逆变电路和控制电路两部分组成。

锁相环(Phase-Locked Loop,PLL)是三相逆变器中的一个重要组成部分,用于实现电网电压和逆变器输出电压之间的同步控制。

锁相环(PLL)是一种用于提取频率和相位信息的控制系统。

在三相逆变器中,PLL的主要功能是将电网电压的频率和相位信息提取出来,并与逆变器的输出电压进行比较,以实现同步控制。

具体来说,锁相环通过不断调整逆变器的输出频率和相位,使其与电网电压保持同步,从而实现电能的高效转换。

锁相环的工作原理可以简单地分为三个步骤:相频检测、滤波和控制。

首先,相频检测器会对电网电压和逆变器输出电压进行相频检测,得到它们之间的相位差和频率差。

然后,滤波器会对相位差和频率差进行滤波处理,以减小干扰和噪声的影响。

最后,控制器根据滤波后的结果,调整逆变器的输出频率和相位,使其与电网电压保持同步。

在具体实现中,锁相环通常由相频检测器、环路滤波器和控制器三部分组成。

相频检测器可以通过比较电网电压和逆变器输出电压的相位差和频率差来提取同步信息。

环路滤波器则用于对相位差和频率差进行滤波处理,以消除噪声和干扰的影响。

控制器则根据滤波后的结果,调整逆变器的输出频率和相位,使其与电网电压保持同步。

在三相逆变器中,锁相环的工作原理非常重要。

通过锁相环的同步控制,可以有效地实现逆变器输出电压与电网电压的同步,从而提高逆变器的转换效率和功率质量。

同时,锁相环还具有快速响应、高精度和抗干扰等特点,能够在电网电压波动或扰动的情况下保持逆变器的稳定运行。

总结起来,三相逆变器中的锁相环是一种用于实现电网电压和逆变器输出电压同步控制的重要组成部分。

它通过相频检测、滤波和控制等步骤,不断调整逆变器的输出频率和相位,使其与电网电压保持同步。

锁相环的工作原理能够有效提高逆变器的转换效率和功率质量,并具有快速响应、高精度和抗干扰等特点,能够保持逆变器的稳定运行。

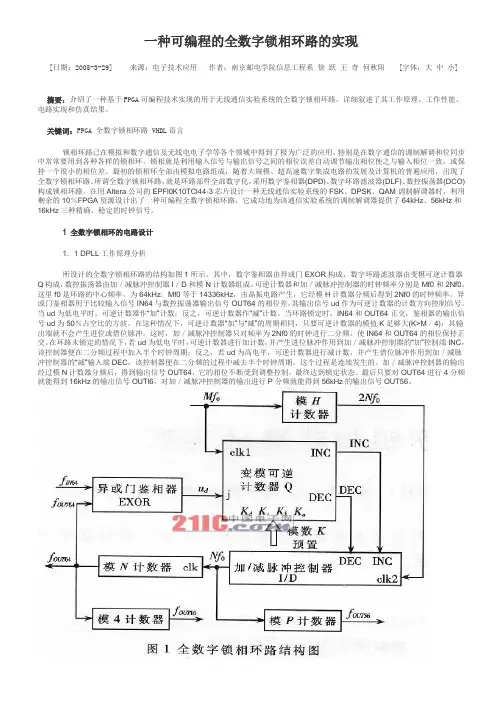

一种可编程的全数字锁相环路的实现[日期:2005-3-29] 来源:电子技术应用作者:南京邮电学院信息工程系徐跃王奇何秋阳[字体:大中小]摘要:介绍了一种基于FPGA可编程技术实现的用于无线通信实验系统的全数字锁相环路。

详细叙述了其工作原理、工作性能、电路实现和仿真结果。

关键词:FPGA 全数字锁相环路 VHDL语言锁相环路已在模拟和数字通信及无线电电子学等各个领域中得到了极为广泛的应用,特别是在数字通信的调制解调和位同步中常常要用到各种各样的锁相环。

锁相就是利用输入信号与输出信号之间的相位误差自动调节输出相位使之与输入相位一致,或保持一个很小的相位差。

最初的锁相环全部由模拟电路组成,随着大规模、超高速数字集成电路的发展及计算机的普遍应用,出现了全数字锁相环路。

所谓全数字锁相环路,就是环路部件全部数字化,采用数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)构成锁相环路。

在用Altera公司的EPFl0K10TCl44-3芯片设计一种无线通信实验系统的FSK、DPSK、QAM调制解调器时,利用剩余的10%FPGA资源设计出了一种可编程全数字锁相环路,它成功地为该通信实验系统的调制解调器提供了64kHz、56kHz和16kHz三种精确、稳定的时钟信号。

1 全数字锁相环的电路设计1.1 DPLL工作原理分析所设计的全数字锁相环路的结构如图1所示。

其中,数字鉴相器由异或门EXOR构成,数字环路滤波器由变模可逆计数器Q构成,数控振荡器由加/减脉冲控制器I/D和模N计数器组成。

可逆计数器和加/减脉冲控制器的时钟频率分别是Mf0和2Nf0。

这里f0是环路的中心频率,为64kHz。

Mf0等于14336kHz,由晶振电路产生,它经模H计数器分频后得到2Nf0的时钟频率。

异或门鉴相器用于比较输入信号IN64与数控振荡器输出信号OUT64的相位差,其输出信号ud作为可逆计数器的计数方向控制信号。

当ud为低电平时,可逆计数器作“加”计数;反之,可逆计数器作“减”计数。

基于单片机的简易数字锁相环设计通过捕获中断和周期中断获取的输入、输出相差,经过分段式变PI控制器,计算出载波周期的补偿量,采用分组线性插补再调制技术,改变了每个载波周期值,从而实现了高精度数字锁相功能。

在此,给出了硬件实现电路及软件流程图。

通过实验验证了该方案的可行性。

1 引言随着信息技术的迅速发展和计算机的日益普及,对电源系统供电质量和可靠性的要求越来越高,不间断电源(UPS)的应用也越来越广泛。

在运行时,要求UPS的输出电压、频率和相位都与市电保持一致,这样才能在市电发生变化时保证UPS 向负载提供不间断、稳定的电能,且不对负载产生过大的冲击。

所以,UPS中的逆变器须有锁相环节,以保证UPS与市电的同步。

同步锁相控制应具备下述功能:①当电网频率满足精度要求时,使逆变器与电网同步运行;②当电网频率超出精度要求范围或电网发生故障时,使逆变器与内部高精度的基准频率同步运行。

此外,两种状态之间的转换要平稳,以免造成转换过程中逆变器工作频率的剧烈抖动。

锁相可分为模拟锁相和数字锁相。

与传统的模拟锁相相比,数字锁相不仅能简化硬件电路的设计,降低成本,还可解决模拟电路中需要调整电路参数,以及器件的老化和温漂等问题,大大提高了电路的可靠性和锁相精度。

在此,讨论了逆变器的输出电压数字锁相技术[1,2]。

2数字锁相环2.1 锁相原理锁相环是一个闭环的相位控制系统,能够自动跟踪输入信号的频率和相位。

图1示出普通的模拟锁相环控制框图。

它由鉴相器(PD)、低通滤波器 (LPF)和压控振荡器(VCO)组成。

通过将VCO的输出电压信号uout(t)和电网电压的采样信号uin(t)这两路频率与相位不同的信号送入鉴相器,生成误差信号Ue(t),该信号是相位差的线性函数。

ue(t)经过低通滤波器后输出电压信号UD(t)。

VCO 在uc(t)的控制下将改变uout(t)的频率和相位,以减小uout(t)的频率和相位差。

500)this.style.width=500;"border=0>在UPS的数字化控制中,传统的模拟锁相环改变为用软件实现的数字锁相环。

//DSPIC30F2010 单相逆变带数字锁相环程序#include <p30f2010.h> //中断优先级还没设置,先t2,t1,spwm,其他#include <timer.h>#include <math.h>#include "lcd.h"#define _T1ON T1CONbits.TON#define _T2ON T2CONbits.TON_FOSC(CSW_FSCM_OFF & XT_PLL8);_FWDT(WDT_OFF);_FBORPOR( RST_PWMPIN& PWMxH_ACT_HI& PWMxL_ACT_HI&PBOR_OFF & MCLR_EN);_FGS(CODE_PROT_OFF);void IC2_INI(void);void T2_INI(void);void PWM_INI(void);void AD_INI(void);void T1_INI(void);void PWM_CAL(unsigned int ,unsigned int k,unsigned int a );void IOUT_PROTECT(void);void US_PROTECT(void);void PROTECT_RE(void);void PID_CAL(void);void smooth_test(unsigned int ,unsigned int );void smooth_3_test(unsigned int a,unsigned int b,unsigned int c);unsigned int IC2_0,IC2_1; //捕捉周期用,前后相减unsigned long CAP_T,CAP_T_0; //捕捉得到的周期,不过有分频,记得<<3 unsigned int CAP_N,PWM_N,AD_N,T1_N;unsigned int AD0,AD1; //ADCBUF的结果读到这里来,采样满64次后,转存并清空,记得清空unsigned int UD,US,AD_N_200,AD_N_50; //AD转存的数据,供外部计算用,64次计数到位unsigned int AD2,AD3,IOUT,UO; //正弦波采样采用均方根的方法要用32位变量来存,ad结果和转存数unsigned int Kp,Ki,Ud0,Ud1,Us0,Us1; //pid环节数,和2次处理的采样电压数据unsigned int UD_10,US_10,IOUT_10,UO_10; //采样结果,转换为10位的有效值,unsigned int RE_DELAY; //保护后延迟计数,计数1时,等于一个周波50个约1sunsigned char PROTECT_FLAG; //保护标志位unsigned int io_10_0,io_10_1,io_10_2,io_10_max_temp,io_10_max,smooth_fail_n; //电流采样的全局变量const unsigned int d1[100]= //0~90度份100份的正弦{515 ,1544 ,2573 ,3601 ,4629 ,5655 ,6680 ,7703 ,8724 ,9743 ,10760 ,11774 ,12785 ,13793 ,14798 ,15799 ,16796 ,17789 ,18778 ,19762 ,20741 ,21715 ,22683 ,23646 ,24603 ,25554 ,26499 ,27437 ,28369 ,29293 ,30210 ,31120 ,32022 ,32916 ,33803 ,34680 ,35549 ,36410 ,37261 ,38103 ,38936 ,39760 ,40573 ,41376 ,42170 ,42952 ,43724 ,44486 ,45236 ,45976 ,46703 ,47420 ,48125 ,48817 ,49498 ,50167 ,50823 ,51467 ,52097 ,52716 ,53321 ,53913 ,54491 ,55056 ,55608 ,56146 ,56670 ,57180 ,57676 ,58158 ,58625 ,59078 ,59516 ,59940 ,60349 ,60742 ,61121 ,61485 ,61834 ,62167 ,62486 ,62788 ,63075 ,63347 ,63603 ,63843 ,64068 ,64277 ,64470 ,64647 ,64808 ,64953 ,65082 ,65195 ,65292 ,65372 ,65437 ,65485 ,65518 ,65534 ,};unsigned int PWM_N,k,a; //n=当前在的段的位置,k映射到0~99的查表位置,a变比后期主要控制这个unsigned long temp;//*************************************************//主程序//**************************************************int main(void){LCD_Init();LCD_WRITE_8BIT(LINE1,CMD);DISP_10(78);PWM_INI();AD_INI();T1_INI();// T2_INI();// _T2ON=1;// IC2_INI();// _IC2IE=1;_T1ON=1;_T1IE=1;_ADON=1;_ADIF=0;_ADIE=1;a=32768;//while(_IC2IF==0) //过零点时启动pwm _PTEN=1;_PWMIE=1;_PWMIP=7;Ki=60;Kp=7;IOUT_10=1;while(1){LCD_WRITE_8BIT(LINE1,CMD);DISP_10(IOUT_10);DISP_10(UD_10);nop;delay1ms(200);}}//*************************************//捕捉初始化程序,IC1 IC2//**************************************void IC2_INI(void){ _TRISD1=1;//IC2CONIC2CONbits.ICSIDL=0; //空闲运行IC2CONbits.ICTMR=1; //1=采样tmr2,0=采样tmr3IC2CONbits.ICI=0B00; //每1次捕捉中断//IC2CONbits.ICOV //只读,溢出//IC2CONbits.ICBNE //只读,缓冲器非空IC2CONbits.ICM=0B011; //每一个上升沿捕捉一次//000=关闭捕捉_IC2IF=0;_IC2IE=0;}//*******************************************//T2初始化,为ic2提供时基//*******************************************void T2_INI(void){T2CONbits.TON=0; //设置前关闭T2CONbits.TSIDL=0; //空闲运行T2CONbits.TGATE=0; //门控计数禁止T2CONbits.TCKPS=0B01; //1:8T2CONbits.T32=0; //禁止32位计数T2CONbits.TCS=0; //内部时钟源TMR2=0; //初始化计数值PR2=49999; //周期满,就是不周期T2CONbits.TON=0; //定时器工作_T2IF=0;_T2IE=0;}//******************************************//IC2捕捉中断程序,锁频锁相用;入口参数IC2BUF,出口参数PTPER,PWM_N//*******************************************void __attribute__ ((interrupt)) _IC2Interrupt(void){_IC2IF=0;PWM_N=200; //实现锁相IC2_0=IC2_1;IC2_1=IC2BUF;CAP_T_0=CAP_T;if(IC2_0<IC2_1)CAP_T=(long)IC2_1+50000-IC2_0;else CAP_T=(long)IC2_1+100000-IC2_0;if(CAP_T<CAP_T_0+64 && CAP_T>CAP_T_0-64) return;PTPER=(CAP_T<<3)/400-1; //重新设置pwm周期,实现锁频// PWM_N=200; //实现锁相PR1=(CAP_T<<3)/200-1; //定时器1 ,1:1分频,一个周期分为64份,为ad提供出发时间//这里把PR1的结果多减去几个,这样一个周期完成,使得定时器的时间多点,//要是少了就麻烦,采样次数会少一个,这样对电流采样是要守相位的很不利,//于是把它减小几个,这样在pwm_n=0是,定时器会多点时间,把时间清掉,就可以保证相位了。

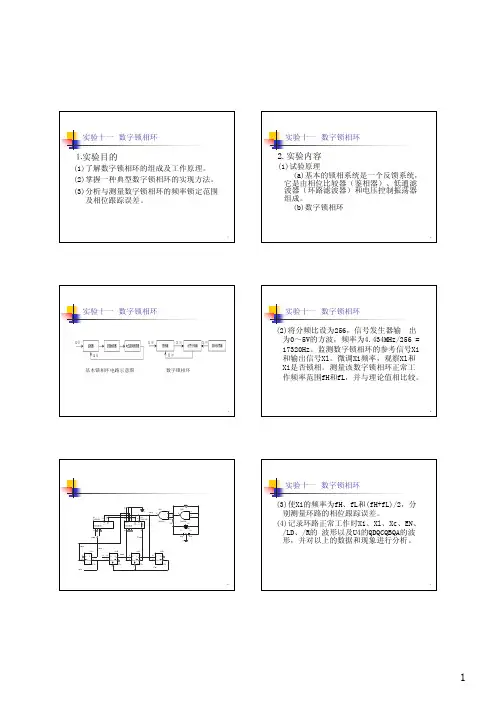

通信原理实验报告数字锁相环实验姓名:学号:实验2 数字锁相环实验一、实验原理和电路说明在电信网中,同步是一个十分重要的概念。

同步的种类很多,有时钟同步、比特同步等等,其最终目的使本地终端时钟源锁定在另一个参考时钟源上,如果所有的终端均采用这种方式,则所有终端将以统一步调进行工作。

同步的技术基础是锁相,因而锁相技术是通信中最重要的技术之一。

锁相环分为模拟锁相环与数字锁相环,本实验将对数字锁相环进行实验。

图2.2.1 数字锁相环的结构数字锁相环的结构如图2.2.1所示,其主要由四大部分组成:参考时钟、多模分频器(一般为三种模式:超前分频、正常分频、滞后分频)、相位比较(双路相位比较)、高倍时钟振荡器(一般为参考时钟的整数倍,此倍数大于20)等。

数字锁相环均在FPGA内部实现,其工作过程如图2.2.2所示。

T1时刻T2时刻T3时刻T4时刻图2.2.2 数字锁相环的基本锁相过程与数字锁相环的基本特征在图2.2.1,采样器1、2构成一个数字鉴相器,时钟信号E、F对D信号进行采样,如果采样值为01,则数字锁相环不进行调整(÷64);如果采样值为00,则下一个分频系数为(1/63);如果采样值为11,则下一分频系数为(÷65)。

数字锁相环调整的最终结果使本地分频时钟锁在输入的信道时钟上。

在图2.2.2中也给出了数字锁相环的基本锁相过程与数字锁相环的基本特征。

在锁相环开始工作之前的T1时该,图2.2.2中D点的时钟与输入参考时钟C没有确定的相关系,鉴相输出为00,则下一时刻分频器为÷63模式,这样使D点信号前沿提前。

在T2时刻,鉴相输出为01,则下一时刻分频器为÷64模式。

由于振荡器为自由方式,因而在T3时刻,鉴相输出为11,则下一时刻分频器为÷65模式,这样使D点信号前沿滞后。

这样,可变分频器不断在三种模式之间进行切换,其最终目的使D点时钟信号的时钟沿在E、F时钟上升沿之间,从而使D点信号与外部参考信号达到同步。

湖北民族学院毕业论文(设计)毕业设计(论文)题目学生姓名:金锋学号: 031040815 系别:信息工程学院专业:电气工程及其自动化指导教师:高仕红评阅教师:论文答辩日期2014-5-24答辩委员会主席摘要本论文致力于对逆变电源并联系统的控制技术的研究。

文中以实际的科研项目为背景,在对逆变电源并联系统的一些运行特性和三相锁相环进行深入地分析和研究的基础上建立结构图了逆变,并通过MATLAB 中的SIMULINK 搭建了整个逆变电源并联系统的仿真模型。

逆变电源电压的幅值和相位信息是逆变电源并联系统控制的参考基准,而高性能锁相环系统能够快速、准确地跟踪电网瞬态变化,提取逆变电源正序分量,为逆变电源的并联提供参考信号。

因此,锁相环系统的研究具有十分重要的实际意义。

本文首先简要地介绍了一些逆变电源并联系统的控制技术的基础理论与优势,并介绍了逆变电源并联的基本原理,然后从最简单的逆变电源并联系统(两台逆变电源)着手对逆变电源并联系统的数学模型、环流分量、功率特性以及闭环特性进行了分析,最后提出了在使主从逆变电源的电压相位一致时比较困难的问题。

为了解决上面所提出的问题,在逆变电源并联系统中运用锁相环技术,并先后讨论了锁相环的基本原理、三相锁相环的原理以及自解耦的三相锁相环的基本原理,然后又在自解耦的三相锁相环的基本原理上设计了自解耦的三相锁相环的参数。

最后基于前面的分析搭建了三相锁相环和基于主从方式并联技术下逆变电源并联系统的结构图并分情况对其进行了仿真与分析,得出了在这种并联技术下,即便系统中的参数很不平衡也能很好地抑制环流。

关键字:逆变电源,并联系统,幅值,相位,锁相环AbstractThis paper concentrates on the study of the control technology of inverter parallel system . Text in the context of actual research projects , establishment of structural diagram of the inverter in a number of operating characteristics and three-phase locked loop inverter parallel system of in-depth analysis and research on the basis of , and through the built in MATLAB SIMULINK the simulation model of the entire inverter parallel system .Amplitude and phase information of the inverter supply voltage is controlled inverter parallel system reference point , and high-performance phase locked loop system can quickly and accurately track the grid transients , power inverter to extract positive sequence component of the inverter providing parallel power reference signal . Therefore, the study of phase-locked loop system has a very important practical significance .This paper begins with a brief introduction to some of the basic theory and advantages of the parallel inverter control technology system and introduces the basic principles of power inverters in parallel , and then from the most simple inverter parallel system ( two power inverter ) begin mathematical model of inverter parallel system , circulation components , power characteristics , and a closed-loop characteristics were analyzed , and finally presented at the main power supply voltage from the phase inverter consistent difficult problem.To address the issues raised above, in the power inverter parallel system using phase-locked loop technology , and has discussed the basic principles of phase-locked loop , the principle of three-phase phase-locked loop and decoupled from the phase locked loop of the basic principle , and then on the basic principles of self- decoupling phase locked loop design phase locked loop since decoupling parameters .Finally, based on the above analysis to build a three-phase locked loop based structure of master-slave parallel technology under inverter parallel system and its simulation of the situation and analysis obtained in this parallel technique, even very unbalanced system parameters can be well suppressed circulation .Keywords: Power inverter, Parallel system , Amplitude, phase , Phase-locked loop目录摘要 (I)ABSTRACT (II)1 绪言 (1)1.1 课题背景 (1)1.2 几种主要的逆变电源的控制技术 (1)1.3 国外逆变电源并联系统技术的特点 (3)1.4 课题研究的目的和意义 (4)2 逆变电源的并联系统的研究与分析 (5)2.1 逆变电源并联的基本原理 (5)2.2 逆变电源并联系统的数学模型 (7)2.3 逆变电源并联系统的环流分析 (8)2.4 逆变电源并联系统的功率特性 (10)2.5 逆变电源并联系统电压的闭环特性 (13)3 逆变电源并联系统的锁相环设计 (16)3.1 锁相环的基本原理 (16)3.2 对三相锁相环的分析 (18)3.3 自解耦的三相锁相环的基本原理 (22)3.4 自解耦的三相锁相环参数设计 (24)4 三相逆变电源并联系统的锁相环仿真与分析 (28)4.1 三相锁相环的仿真与分析 (28)4.2 逆变电源并联系统的仿真与分析 (29)5 总结与展望 (35)致谢 (36)参考文献 (37)1 绪言1.1课题背景随着社会和经济的发展,需要不断地增加用电设备,而供电系统的容量、性能和发展可靠性的要求也越来越高。

//DSPIC30F2010 单相逆变带数字锁相环程序#include <p30f2010.h> //中断优先级还没设置,先t2,t1,spwm,其他#include <timer.h>#include <math.h>#include "lcd.h"#define _T1ON T1CONbits.TON#define _T2ON T2CONbits.TON_FOSC(CSW_FSCM_OFF & XT_PLL8);_FWDT(WDT_OFF);_FBORPOR( RST_PWMPIN& PWMxH_ACT_HI& PWMxL_ACT_HI&PBOR_OFF & MCLR_EN);_FGS(CODE_PROT_OFF);void IC2_INI(void);void T2_INI(void);void PWM_INI(void);void AD_INI(void);void T1_INI(void);void PWM_CAL(unsigned int ,unsigned int k,unsigned int a );void IOUT_PROTECT(void);void US_PROTECT(void);void PROTECT_RE(void);void PID_CAL(void);void smooth_test(unsigned int ,unsigned int );void smooth_3_test(unsigned int a,unsigned int b,unsigned int c);unsigned int IC2_0,IC2_1; //捕捉周期用,前后相减unsigned long CAP_T,CAP_T_0; //捕捉得到的周期,不过有分频,记得<<3 unsigned int CAP_N,PWM_N,AD_N,T1_N;unsigned int AD0,AD1; //ADCBUF的结果读到这里来,采样满64次后,转存并清空,记得清空unsigned int UD,US,AD_N_200,AD_N_50; //AD转存的数据,供外部计算用,64次计数到位unsigned int AD2,AD3,IOUT,UO; //正弦波采样采用均方根的方法要用32位变量来存,ad结果和转存数unsigned int Kp,Ki,Ud0,Ud1,Us0,Us1; //pid环节数,和2次处理的采样电压数据unsigned int UD_10,US_10,IOUT_10,UO_10; //采样结果,转换为10位的有效值,unsigned int RE_DELAY; //保护后延迟计数,计数1时,等于一个周波50个约1sunsigned char PROTECT_FLAG; //保护标志位unsigned int io_10_0,io_10_1,io_10_2,io_10_max_temp,io_10_max,smooth_fail_n; //电流采样的全局变量const unsigned int d1[100]= //0~90度份100份的正弦{515 ,1544 ,2573 ,3601 ,4629 ,5655 ,6680 ,7703 ,8724 ,9743 ,10760 ,11774 ,12785 ,13793 ,14798 ,15799 ,16796 ,17789 ,18778 ,19762 ,20741 ,21715 ,22683 ,23646 ,24603 ,25554 ,26499 ,27437 ,28369 ,29293 ,30210 ,31120 ,32022 ,32916 ,33803 ,34680 ,35549 ,36410 ,37261 ,38103 ,38936 ,39760 ,40573 ,41376 ,42170 ,42952 ,43724 ,44486 ,45236 ,45976 ,46703 ,47420 ,48125 ,48817 ,49498 ,50167 ,50823 ,51467 ,52097 ,52716 ,53321 ,53913 ,54491 ,55056 ,55608 ,56146 ,56670 ,57180 ,57676 ,58158 ,58625 ,59078 ,59516 ,59940 ,60349 ,60742 ,61121 ,61485 ,61834 ,62167 ,62486 ,62788 ,63075 ,63347 ,63603 ,63843 ,64068 ,64277 ,64470 ,64647 ,64808 ,64953 ,65082 ,65195 ,65292 ,65372 ,65437 ,65485 ,65518 ,65534 ,};unsigned int PWM_N,k,a; //n=当前在的段的位置,k映射到0~99的查表位置,a变比后期主要控制这个unsigned long temp;//*************************************************//主程序//**************************************************int main(void){LCD_Init();LCD_WRITE_8BIT(LINE1,CMD);DISP_10(78);PWM_INI();AD_INI();T1_INI();// T2_INI();// _T2ON=1;// IC2_INI();// _IC2IE=1;_T1ON=1;_T1IE=1;_ADON=1;_ADIF=0;_ADIE=1;a=32768;//while(_IC2IF==0) //过零点时启动pwm _PTEN=1;_PWMIE=1;_PWMIP=7;Ki=60;Kp=7;IOUT_10=1;while(1){LCD_WRITE_8BIT(LINE1,CMD);DISP_10(IOUT_10);DISP_10(UD_10);nop;delay1ms(200);}}//*************************************//捕捉初始化程序,IC1 IC2//**************************************void IC2_INI(void){ _TRISD1=1;//IC2CONIC2CONbits.ICSIDL=0; //空闲运行IC2CONbits.ICTMR=1; //1=采样tmr2,0=采样tmr3IC2CONbits.ICI=0B00; //每1次捕捉中断//IC2CONbits.ICOV //只读,溢出//IC2CONbits.ICBNE //只读,缓冲器非空IC2CONbits.ICM=0B011; //每一个上升沿捕捉一次//000=关闭捕捉_IC2IF=0;_IC2IE=0;}//*******************************************//T2初始化,为ic2提供时基//*******************************************void T2_INI(void){T2CONbits.TON=0; //设置前关闭T2CONbits.TSIDL=0; //空闲运行T2CONbits.TGATE=0; //门控计数禁止T2CONbits.TCKPS=0B01; //1:8T2CONbits.T32=0; //禁止32位计数T2CONbits.TCS=0; //内部时钟源TMR2=0; //初始化计数值PR2=49999; //周期满,就是不周期T2CONbits.TON=0; //定时器工作_T2IF=0;_T2IE=0;}//******************************************//IC2捕捉中断程序,锁频锁相用;入口参数IC2BUF,出口参数PTPER,PWM_N//*******************************************void __attribute__ ((interrupt)) _IC2Interrupt(void){_IC2IF=0;PWM_N=200; //实现锁相IC2_0=IC2_1;IC2_1=IC2BUF;CAP_T_0=CAP_T;if(IC2_0<IC2_1)CAP_T=(long)IC2_1+50000-IC2_0;else CAP_T=(long)IC2_1+100000-IC2_0;if(CAP_T<CAP_T_0+64 && CAP_T>CAP_T_0-64) return;PTPER=(CAP_T<<3)/400-1; //重新设置pwm周期,实现锁频// PWM_N=200; //实现锁相PR1=(CAP_T<<3)/200-1; //定时器1 ,1:1分频,一个周期分为64份,为ad提供出发时间//这里把PR1的结果多减去几个,这样一个周期完成,使得定时器的时间多点,//要是少了就麻烦,采样次数会少一个,这样对电流采样是要守相位的很不利,//于是把它减小几个,这样在pwm_n=0是,定时器会多点时间,把时间清掉,就可以保证相位了。

必须保证最大值在相位区间内//结果在pwm中断中开始相位补偿,这里就不补了,要不然这个数不好确定CAP_N++;if(CAP_N==64)CAP_N=0;return;}//**********************************************void __attribute__ ((interrupt)) _PWMInterrupt(void)//**********************************************{_PWMIF=0; //_PWMIF=0;/* if(PWM_N==0) //把t1 的ad时间清理,保住采样相位,对才交流有效,这里进行相位补偿,多减少加{ //无论这里pwm_N=多少,都没关系,只要一个周期进行一次时间补偿就行了。

if(TMR1<(PR1>>1)) TMR1=0;else TMR1=PR1-10;}*/if(PWM_N<100){k=PWM_N;PWM_CAL(PWM_N,k,a);}else if(PWM_N<200){k=200-PWM_N-1;PWM_CAL(PWM_N,k,a);}else if(PWM_N<300){k=PWM_N-200;//负数的PWM_CAL(PWM_N,k,a);}else if(PWM_N<400){k=400-PWM_N-1;PWM_CAL(PWM_N,k,a);}PWM_N++;if(PWM_N==400)PWM_N=0;_PWMIF=0;}//*****************************************************void PWM_CAL(unsigned int n,unsigned int k,unsigned int a ) //占空比计算,调用= PWM_CAL(n,k,a);//*****************************************************{unsigned int _sin,tempd; //a=变比,_sin=查表得正弦值,tempd=a*_sin>>17;unsigned long a_sin,temppdc; //a_sin=a*_sin,temppdc=PTPER*tempd;_sin=d1[k];//PDC1=PTPER*(1+-a*_sin)// ***<<32// a、_sin 小于1,都扩大2^16倍,a_sin=a;a_sin=a_sin*_sin; //计算结果为32位a_sin=a_sin>>17;//移动后是15位***>>17tempd=a_sin; //结果存起来if( n<200)tempd=32768+tempd; //加1,结果为16位;1被扩大了2^15倍,两个15位数相加为16位;else tempd=32768-tempd;temppdc=(PTPER+1); //_16*_16为_32temppdc=temppdc*tempd;temppdc=temppdc>>15; //结果>>16得到16位要的结果***>>15 (**扩大和缩小移位刚好全抵消**)。