南邮集成电路与CAD实验报告1_张长春sh

- 格式:docx

- 大小:2.01 MB

- 文档页数:10

《集成电路与CAD》课程实验第3 次实验报告实验名称:Verilog HDL设计与仿真实验目的:1.熟悉NC软件2.掌握Verilog程序编译3.掌握CADEDNCE基本使用,进行HDL程序设计与仿真概述:1.Verilog的主要应用包括:ASIC和FPGA工程师编写可综合的RTL代码高抽象级系统仿真进行系统结构开发测试工程师用于编写各种层次的测试程序用于ASIC和FPGA单元或更高层次的模块的模型开硬件描述语言(HDL: Hardware Description Language)2.Verilog HDL 的抽象级别行为级:有关行为和技术指标模块,容易理解RTL级:有关逻辑执行步骤的模块,较难理解门级:有关逻辑部件互相连接的模块,很难理解开关级:有关物理形状和布局参数的模块,非常难理解本次实验包含行为级仿真和门级verilog仿真实验内容与结果分析:1,Verilog代码:16位加法器module count(out,clk,rst); //源程序input clk,rst; //指定输入output[3:0] out; //指定输出reg[3:0] out; //out为4位reg型initial out=4'd0; //初始,输出为0always @(posedge clk or negedge rst) //always块beginif(!rst) out=4'd0; //如果rst信号为0输出为0 else //否则开始下面beginout=out+4'd1; //out=out+1if(out==4'd16) out=4'd0; 如果输出为16,归0endendendmodule实验心得:VerilogHDL语言的很多功能可以通过c语言的思想方法去理解,这样感觉这门语言的学习难度就有所下降。

通过上面的例子可以看到:Verilog HDL程序是由模块构成的。

集成电路CAD实验报告集成电路CAD实验报告姓名:席悦学号:2120503018 班级:微电子31班一、实验目的:通过设计一个简单的缓冲器的原理图到最终的版图,对Cadence 的Composer,Analog Design Environment,Virtuoso,Assura等各大功能模块逐一了解,使学生掌握模拟集成电路设计的总体流程,为日后的学习、工作打下坚实的基础。

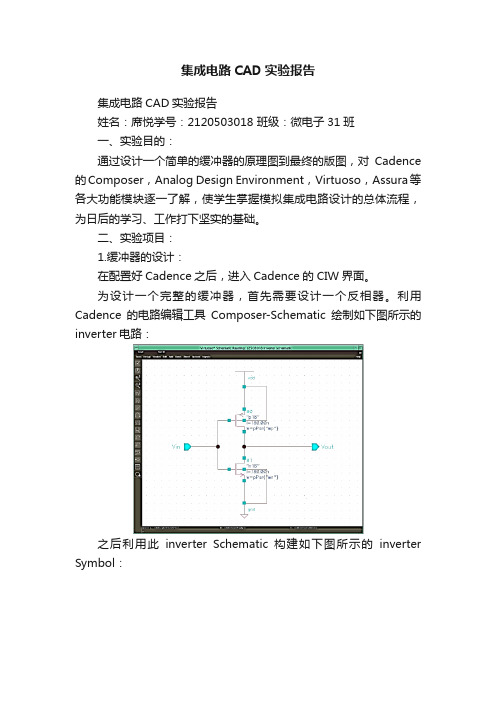

二、实验项目:1.缓冲器的设计:在配置好Cadence之后,进入Cadence的CIW界面。

为设计一个完整的缓冲器,首先需要设计一个反相器。

利用Cadence的电路编辑工具Composer-Schematic绘制如下图所示的inverter电路:之后利用此inverter Schematic 构建如下图所示的inverter Symbol:我们知道,一个Buffer是由两个Inverter组成,利用前边构建Inverter Schematic的方法,画出缓冲器Buffer的电路原理图:其中的反相器直接调用之前做好的Inverter的Symbol。

同样的,利用此缓冲器的原理图生成相应的缓冲器Symbol图:之后构建仿真电路,对所设计的Buffer电路进行电路仿真(ADE)。

仿真电路图如下:在仿真过程中,我们分别采用tt,ss,ff工艺角进行仿真,得到了如下的波形图和仿真数据:①tt工艺角:其相应数据参数为:Marker,/I5/V1,/OUT,/INM0:Y,900mV,900mV,900mV x[0],111.36ps,778.31ps,50ps x[1],5.1063ns,5.9952ns,5.05ns ②ss工艺角:其相应数据参数为:Marker,/I5/V1,/OUT,/INM0:Y,900mV,900mV,900mV x[0],121.55ps,927.99ps,50ps x[1],5.1155ns,6.1676ns,5.05ns ③ff工艺角:其相应数据参数为:Marker,/I5/V1,/OUT,/INM0:Y,900mV,900mV,900mVx[0],103.43ps,653.72ps,50psx[1],5.0984ns,5.8613ns,5.05ns④分析总结:通过对不同工艺角的仿真,可以清晰的看到ss的上升延迟和下降延迟时间最长,而ff的上升延迟和下降延迟最短,而tt工艺角是上升延迟和下降延迟的典型值。

集成电路设计实验报告时间:2011年12月实验一原理图设计一、实验目的1.学会使用Unix操作系统2.学会使用CADENCE的SCHEMA TIC COMPOSOR软件二:实验内容使用schematic软件,设计出D触发器,设置好参数。

二、实验步骤1、在桌面上点击Xstart图标2、在User name:一栏中填入用户名,在Host:中填入IP地址,在Password:一栏中填入用户密码,在protocol:中选择telnet类型3、点击菜单上的Run!,即可进入该用户unix界面4、系统中用户名为“test9”,密码为test1234565、在命令行中(提示符后,如:test22>)键入以下命令icfb&↙(回车键),其中& 表示后台工作,调出Cadence软件。

出现的主窗口所示:6、建立库(library):窗口分Library和Technology File两部分。

Library部分有Name和Directory 两项,分别输入要建立的Library的名称和路径。

如果只建立进行SPICE模拟的线路图,Technology部分选择Don’t need a techfile选项。

如果在库中要创立掩模版或其它的物理数据(即要建立除了schematic外的一些view),则须选择Compile a new techfile(建立新的techfile)或Attach to an existing techfile(使用原有的techfile)。

7、建立单元文件(cell):在Library Name中选择存放新文件的库,在Cell Name中输入名称,然后在Tool选项中选择Composer-Schematic工具(进行SPICE模拟),在View Name中就会自动填上相应的View Name—schematic。

当然在Tool工具中还有很多别的工具,常用的像Composer-symbol、virtuoso-layout等,分别建立的是symbol、layout 的视图(view)。

集成电路设计与集成系统专业毕业实习报*名:***学号:**********专业:集成电路设计与集成系统班级:集成电路设计与集成系统01班指导教师:***实习时间:XXXX-X-X—XXXX-X-X20XX年1月9日目录目录 (2)前言 (3)一、实习目的及任务 (3)1.1实习目的 (3)1.2实习任务要求 (4)二、实习单位及岗位简介 (4)2.1实习单位简介 (4)2.2实习岗位简介(概况) (5)三、实习内容(过程) (5)3.1举行计算科学与技术专业岗位上岗培训。

(5)3.2适应集成电路设计与集成系统专业岗位工作。

(5)3.3学习岗位所需的知识。

(6)四、实习心得体会 (6)4.1人生角色的转变 (6)4.2虚心请教,不断学习。

(7)4.3摆着心态,快乐工作 (7)五、实习总结 (8)5.1打好基础是关键 (8)5.2实习中积累经验 (8)5.3专业知识掌握的不够全面。

(8)5.4专业实践阅历远不够丰富。

(8)本文共计5000字,是一篇各专业通用的毕业实习报告范文,属于作者原创,绝非简单复制粘贴。

欢迎同学们下载,助你毕业一臂之力。

前言随着社会的快速发展,用人单位对大学生的要求越来越高,对于即将毕业的集成电路设计与集成系统专业在校生而言,为了能更好的适应严峻的就业形势,毕业后能够尽快的融入到社会,同时能够为自己步入社会打下坚实的基础,毕业实习是必不可少的阶段。

毕业实习能够使我们在实践中了解社会,让我们学到了很多在集成电路设计与集成系统专业课堂上根本就学不到的知识,受益匪浅,也打开了视野,增长了见识,使我认识到将所学的知识具体应用到工作中去,为以后进一步走向社会打下坚实的基础,只有在实习期间尽快调整好自己的学习方式,适应社会,才能被这个社会所接纳,进而生存发展。

刚进入实习单位的时候我有些担心,在大学学习集成电路设计与集成系统专业知识与实习岗位所需的知识有些脱节,但在经历了几天的适应过程之后,我慢慢调整观念,正确认识了实习单位和个人的岗位以及发展方向。

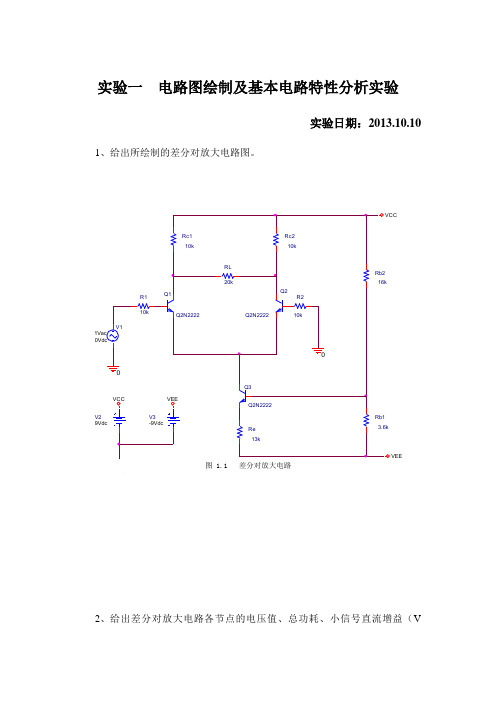

实验一电路图绘制及基本电路特性分析实验实验日期:2013.10.10 1、给出所绘制的差分对放大电路图。

2、给出差分对放大电路各节点的电压值、总功耗、小信号直流增益(V(OUT2)/V_V1)、输入电阻值和输出电阻值。

图 2.1 DC分析的相关数据图 2.2 DC分析的相关数据3、给出V(OUT2)~V_V1曲线,X轴设为0~300mv,Y轴设为5~12.5V。

12.5V10.0V7.5V5.0V0V50mV100mV150mV200mV250mV300mV V(out2)V_V1图 3.1 V(OUT2)~V_V1曲线4、给出AC/Noise分析得到的V(OUT2)~频率的曲线,输入噪声~频率、输出噪声~频率的曲线(用2个Y轴在同一坐标中表示),并给出OUT 输出文件中Freq=1KHz时的噪声分析结果数据。

8.0V6.0V4.0V2.0V0V1.0KHz10KHz100KHz 1.0MHz10MHz100MHzV(OUT2)Frequency图 4.1 V(OUT2)~频率曲线Frequency1.0KHz10KHz100KHz 1.0MHz 10MHz 100MHz1V(ONOISE) 2V(INOISE)0V40nV80nV 120nV160nV10V50nV100nV2>>图 4.2 V(ONOISE)~频率、V(INOISE)~频率曲线图 4.3 OUT 输出文件中Freq=1KHz 时的噪声分析(1)图 4.4 OUT 输出文件中Freq=1KHz 时的噪声分析(2)5、给出瞬态及傅里叶分析的相关曲线:V (OUT2)、V (V1:+)(在同一张图上,用2个坐标表示);给出在Probe 窗口下对V (OUT2)的傅里叶分析后的曲线,要求标出其直流分量、基波和三次谐波分量值;给出OUT 输出文件中傅里叶分析结果的数据。

Time200ns400ns 600ns 800ns 1000ns1V(OUT2)2 V(V1:+)7.96V7.98V 8.00V 8.02V 8.04V1-100mV-50mV0V50mV100mV2>>图 5.1 V (OUT2)、V (V1:+)曲线直流分量图 5.2 V(OUT2)的傅里叶分析曲线图 5.3 OUT输出文件中傅里叶分析结果。

集成电路CAD实训报告系部:尚德光伏学院班级:液晶1001姓名:吴海洋学号:100100266指导老师:陆亚青2012年5月课题一缓冲器1.电路原理图(Schematic Mode 和Symbol Mode)Schematic modeSymbol mode2.瞬时分析语句及波形结果3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md"vin IN GND 1.0vvdd Vdd GND 5.0.dc lin source vin 0 5.0 0.02.print dc v(OUT)4.版图5.LVS对比结果课题二与非门1.电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param 1=0.5uvvdd Vdd GND 5.0va A GND PULSE (0 5 50n 5n 5n 100n 200n)vb B GND BIT ({0011} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) .tran/op 1n 400n method=bdf.print tran v(OUT) v(B) v3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md"va A Gnd 5.0vb B Gnd 5.0vvdd Vdd Gnd 5.0.dc lin source va 0 5.0 0.1 sweep lin source vb 0 5.0 1.print dc v(OUT)4.版图5.LVS对比结果课题三或非门1.电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param 1=0.5uvvdd Vdd GND 5.0va A GND PULSE (0 5 50n 5n 5n 50n 100n)vb B GND BIT ({0011} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) .tran/op 1n 400n method=bdf.print tran v(OUT) v(B) v(A)3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md"vvdd Vdd GND 5.0va A GND 5.0vb b GND 5.0.dc lin source va 0 5.0 0.1 sweep lin source vb 0 5.0 1.print dc v(OUT)4.版图5.LVS对比结果课题四CMOS传输门1.电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0vin IN GND PULSE (0 5 50n 5n 5n 50n 100n)vc C GND BIT ({1010} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) .tran/op 1n 400n method=bdf.print tran v(OUT) v(C) v(IN)3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0vin IN GND 5.0vc C GND 5.0.dc lin source vin 0 5.0 0.1 sweep lin source vc 0 5.0 1 .print dc v(OUT)4.版图5.LVS对比结果课题五与或非门1.电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0va A GND PULSE (0 5 50n 5n 5n 50n 100n)vb B GND BIT ({0011 0110 1010 1100 0111} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) vc C GND PWL (0ns 0V 200ns 0V 205ns 5V 400ns 5V)vd D GND PULSE (5 0 100n 5n 5n 100n 200n).tran/op 1n 400n method=bdf.print tran v(F) v(D) v(C) v(B) v(A)3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0va A GND 5.0vb B GND 5.0vc C GND 5.0vd D GND 5.0.dc lin source va 0 5.0 1 sweep lin source vb 0 5.0 1 sweep lin source vc 0 5.0 1 .print dc v(F)4.版图5.LVS对比结果课题六异或门1.电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0va A GND PULSE (0 5 50n 5n 5n 50n 100n)vb B GND BIT ({0011 1010 0101} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) .tran/op 1n 400n method=bdf.print tran v(F) v(B) v(A)3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0va A GND 5.0vb b GND 5.0.dc lin source va 0 5.0 0.1 sweep lin source vb 0 5.0 1 .print dc v(F)4.版图5.LVS对比结果课题七四位加法器1.全加器电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.四位加法器电路原理图(Schematic Mode)3.四位加法器瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0.vector A {A3 A2 A1 A0}.vector B {B3 B2 B1 B0}va A GND BUS ({0011 1110 1100 1010} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) vb B GND BUS ({1101 0111 1010 0101} lt=50n ht=50n on=5 off=0 rt=5n ft=5n).tran/op 1n 400n method=bdf.print tran v(Cout) v(S3) v(S2) v(S1) v(S0)4.四位加法器SPR电路图5.四位加法器SPR版图6.LVS对比结果课题八四位减法器1.全减器电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.四位减法器电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode3.四位减法器瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0.vector A {A3 A2 A1 A0}.vector B {B3 B2 B1 B0}va A GND BUS ({0011 1110 1100 1010} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) vb B GND BUS ({1101 0111 1010 0101} lt=50n ht=50n on=5 off=0 rt=5n ft=5n).tran/op 1n 400n method=bdf.print tran v(Cout) v(S3) v(S2) v(S1) v(S0)4.四位减法器SPR电路图5.四位减法器SPR版图6.LVS对比结果课题九二选一数据选择器1.电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0vd0 D0 GND PULSE (0 5 50n 5n 5n 50n 100n)vd1 D1 GND BIT ({1010} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) vs S GND PWL (0ns 0V 200ns 0V 205ns 5V 400ns 5V).tran/op 1n 400n method=bdf.print tran v(Y) v(S) v(D1) v(D0)3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0vd0 D0 GND 5.0vd1 D1 GND 5.0vs S GND 5.0.dc lin source vd0 0 5.0 1 sweep lin source vd1 0 5.0 1 sweep lin source vs 0 5.0 1 .print dc v(Y)4.版图5.LVS对比结果课题十D触发器1.电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0vd D GND PULSE (0 5 50n 5n 5n 50n 100n)vclk CLK GND BIT ({0101} lt=100n ht=100n on=5 off=0 rt=5n ft=5n) .tran/op 1n 400n method=bdf.print tran v(Q) v(CLK) v(D)3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0vd D GND 5.0vclk CLK GND 5.0.dc lin source vd 0 5.0 0.1 sweep lin source vclk 0 5.0 1 .print dc v(Q)4.版图5.LVS对比结果。

集成电路CAD实验报告姓名:席悦学号:2120503018 班级:微电子31班一、实验目的:通过设计一个简单的缓冲器的原理图到最终的版图,对Cadence的Composer,Analog Design Environment,Virtuoso,Assura等各大功能模块逐一了解,使学生掌握模拟集成电路设计的总体流程,为日后的学习、工作打下坚实的基础。

二、实验项目:1.缓冲器的设计:在配置好Cadence之后,进入Cadence的CIW界面。

为设计一个完整的缓冲器,首先需要设计一个反相器。

利用Cadence的电路编辑工具Composer-Schematic绘制如下图所示的inverter电路:之后利用此inverter Schematic 构建如下图所示的inverter Symbol:我们知道,一个Buffer是由两个Inverter组成,利用前边构建Inverter Schematic的方法,画出缓冲器Buffer的电路原理图:其中的反相器直接调用之前做好的Inverter的Symbol。

同样的,利用此缓冲器的原理图生成相应的缓冲器Symbol图:之后构建仿真电路,对所设计的Buffer电路进行电路仿真(ADE)。

仿真电路图如下:在仿真过程中,我们分别采用tt,ss,ff工艺角进行仿真,得到了如下的波形图和仿真数据:①tt工艺角:其相应数据参数为:Marker, /I5/V1, /OUT, /INM0: Y, 900mV, 900mV, 900mVx[0], 111.36ps, 778.31ps, 50psx[1], 5.1063ns ,5.9952ns, 5.05ns②ss工艺角:其相应数据参数为:Marker, /I5/V1, /OUT, /INM0: Y, 900mV, 900mV, 900mVx[0], 121.55ps, 927.99ps, 50psx[1], 5.1155ns, 6.1676ns, 5.05ns③ff工艺角:其相应数据参数为:Marker, /I5/V1, /OUT, /INM0: Y, 900mV, 900mV, 900mVx[0], 103.43ps, 653.72ps, 50psx[1], 5.0984ns, 5.8613ns, 5.05ns④分析总结:通过对不同工艺角的仿真,可以清晰的看到ss的上升延迟和下降延迟时间最长,而ff的上升延迟和下降延迟最短,而tt工艺角是上升延迟和下降延迟的典型值。

《集成电路与CAD》课程实验第2次实验报告实验名称:SPICE仿真实验目的:1,掌握spice程序的仿真方法2,掌握hspice的使用3,进一步熟悉spice语法知识实验原理:1.Hspice是一个模拟电路仿真软件,在给定电路结构和元器件参数的条件下,它可以模拟和计算电路的各种性能。

用Hspice分析一个电路,熟悉要做到以下三点:(1)给定电路的结构(也就是电路连接关系)元器件参数(指定元器件的参数库)(2)确定分析电路特性所需要的分析内容和分析类型(加入激励和设置分析类型)(3)定义电路的输出信息和变量Hspice规定了一系列输入,输出语句,用这些语句对电路仿真的标题,电路连接方式,组成电路元器件的名称,参数,模型以及分析类型,以及输出变量等进行描述。

2.SPICE网表文件是文本文件,默认的输入文件名为:*.cir因为目前各个版本的SPICE软件都已图形化,并增加了很多功能,所以产生的语句顺序和格式有了一些变化,但主要是以*开头的注释语句的不同变化,便于阅读和模块化,而基本的语句变化不大,包括以下几种:1) 标题语句:网表文件第一行为标题语句,由任意字符串和字母组成,软件并不处理,而是直接在输出文件中作为第一行打印出来2) 注释语句:由*开头的字符串,为文件的说明部分,为方便阅读而在自动产生的SPICE网表文件中大量存在;HSPICE中也可用“$”。

3) 电路描述语句:定义电路拓扑结构和元器件参数的语句,由元器件描述语句、模型描述语句、电源语句等组成4) 电路特性分析和控制语句:以.开头的语句,描述要分析的电路特性及控制命令5) 结束语句:即.END ,标志电路描述语句的结束,在文件最后一行实验内容与结果分析:1,反相器代码:Inverter Circuit.OPTIONS LIST NODE POST.TRAN 200P 20N //瞬态仿真,200.PRINT TRAN V(IN) V(OUT) //打印瞬态仿真结果,Vin和VoutM1 OUT IN VCC VCC PCH L=1U W=20U//M1参数:p管,DGSB,栅长栅宽1和20umM2 OUT IN 0 0 NCH L=1U W=20U//M2参数:n管,DGSB,栅长栅宽1和20umVCC VCC 0 5VIN IN 0 0 PULSE .2 4.8 2N 1N 1N 5N 20N//激励信号:初值0.2,幅度4.8,上升时间2ns,下降时间1ns,延迟1ns,脉宽5ns,周期20ns CLOAD OUT 0 .75P.MODEL PCH PMOS LEVEL=1.MODEL NCH NMOS LEVEL=1.END仿真波形:2,HSPICE 仿真分析电流源负载共源放大电路电流源负载共源放大器结构MOS 管尺寸:W=5u,L=1uMOS 管模型:.MODEL nch NMOS VTO=0.7 KP=110U GAMMA=0.4 LAMBDA=0.04 PHI=0.7.MODEL pch PMOS VTO=-0.7 KP=50U GAMMA=0.57 LAMBDA=0.05 PHI=0.8电路如图所示,试用HSPICE 仿真器得到Vout 作为Vin 函数关系的曲线。

集成电路实验报告第一篇:集成电路实验报告集成电路实验报告班级:姓名:学号:指导老师:实验一:反相器的设计及反相器环的分析一、实验目的1、学习及掌握cadence图形输入及仿真方法;2、掌握基本反相器的原理与设计方法;3、掌握反相器电压传输特性曲线VTC的测试方法;4、分析电压传输特性曲线,确定五个关键电压VOH、VOL、VIH、VIL、VTH。

二、实验内容本次实验主要是利用 cadence 软件来设计一基本反相器(inverter),并利用仿真工具Analog Artist(Spectre)来测试反相器的电压传输特性曲线(VTC,Voltage transfer characteristic curves),并分析其五个关键电压:输出高电平VOH、输出低电平VOL、输入高电平VIH、输入低电平VIL、阈值电压 VTH。

三、实验步骤1.在cadence环境中绘制的反相器原理图如图所示。

2.在Analog Environment中,对反相器进行瞬态分析(tran),仿真时间设置为4ns。

其输入输出波形如图所示。

分开查看:分析:反相器的输出波形在由低跳变到高和由高跳变到底时都会出现尖脉冲,而不是直接跳变。

其主要原因是由于MOS管栅极和漏极上存在覆盖电容,在输出信号变化时,由于电容储存的电荷不能发生突变,所以在信号跳变时覆盖电容仍会发生充放电现象,进而产生了如图所示的尖脉冲。

3.测试反相器的电压传输特性曲线,采用的是直流分析(DC),我们把输入信号修改为5V直流电源,如图所示。

4.然后对该直流电源从0V到5V进行线性扫描,进而得到电压传输特性曲线如图所示。

5.为反相器创建symbol,并调用连成反相器环,如图。

6.测量延时,对环形振荡器进行瞬态分析,仿真时间为4ns,bcd 节点的输出波形如图所示。

7.测量上升延时和下降延时。

(1)测量上升延时:可以利用计算器(calculator)delay函数来计算信号c与信号b间的上升延时和下降延时如图所示。

电路cad技术实验报告一、实验目的本实验旨在使学生熟悉电路CAD软件的使用,理解电路设计的基本流程,掌握电路仿真分析的方法,并通过实践加深对电路理论知识的理解。

二、实验原理电路CAD技术,即计算机辅助设计技术,是利用计算机软件对电路进行设计、仿真和分析的一种技术。

通过电路CAD软件,可以快速地设计电路图,进行电路的参数设置和仿真分析,从而验证电路设计的正确性和性能。

三、实验内容1. 学习电路CAD软件的基本操作,包括软件的安装、启动和界面布局。

2. 设计一个基本的电路图,如放大器电路、滤波器电路等。

3. 对设计的电路进行仿真分析,包括直流工作点分析、交流小信号分析等。

4. 根据仿真结果,调整电路参数,优化电路设计。

5. 记录实验过程中的关键步骤和结果,撰写实验报告。

四、实验步骤1. 启动电路CAD软件,熟悉界面布局和菜单功能。

2. 根据实验要求,绘制电路原理图。

选择适当的元件符号,按照电路原理连接元件。

3. 设置仿真参数,包括仿真类型、频率范围、步长等。

4. 运行仿真,观察仿真波形,分析电路的频率响应、增益等性能指标。

5. 根据仿真结果,调整电路元件参数,如电阻、电容值等,优化电路设计。

6. 重复步骤3-5,直至达到设计要求。

五、实验结果通过本次实验,成功设计并仿真了一个放大器电路。

在仿真过程中,观察到电路的增益、带宽等性能指标满足设计要求。

通过调整元件参数,进一步优化了电路性能。

六、实验分析在实验过程中,发现电路设计中的一些关键因素,如元件的选取、参数的设置等,对电路性能有显著影响。

通过仿真分析,可以直观地观察电路的工作状态,为电路设计提供了有力的支持。

七、实验总结通过本次电路CAD技术实验,加深了对电路设计流程的理解,掌握了电路仿真分析的方法。

实验过程中,学会了如何使用电路CAD软件进行电路设计和仿真,提高了电路设计的能力。

同时,也认识到了在电路设计中需要注意的问题,为今后的学习和研究打下了基础。