锁相环PLL的电路原理以及基本构成

- 格式:pdf

- 大小:98.45 KB

- 文档页数:4

锁相环基本原理

锁相环(Phase Locked Loop,PLL)是一种常用的电子电路,可以用来解决信号同步和频率合成等问题。

它的基本原理是通过比较两个信号的相位差,通过反馈调节使得相位差保持在一个稳定的值,从而达到信号同步的目的。

锁相环的基本组成部分包括相位检测器、低通滤波器、振荡器和分频器等。

其中,相位检测器是锁相环的核心部件,它的作用是将输入信号和反馈信号进行比较,得到相位差信号。

常用的相位检测器有边沿检测器、乘积检测器和采样保持器等。

在锁相环的工作过程中,输入信号经过相位检测器与反馈信号进行比较,产生相位差信号,经过低通滤波器进行滤波处理,然后输出给振荡器进行调节,从而使得振荡器的输出信号与输入信号达到同步。

如果输入信号的频率发生变化,相位差信号也会随之变化,这时锁相环会通过反馈调节振荡器的输出频率,使得相位差保持在一个稳定的值。

锁相环在实际应用中具有广泛的用途,如在通信系统中用于时钟恢复和信号重构,可以提高信号质量和传输距离;在计算机系统中用于时钟同步和频率合成,可以提高计算机的稳定性和性能;在音频系统中用于音频合成和去噪,可以提高音质和降低噪声等。

锁相环作为一种常用的电子电路,其基本原理是通过比较两个信号的相位差,通过反馈调节使得相位差保持在一个稳定的值,从而达到信号同步的目的。

它在实际应用中具有广泛的用途,可以提高系统的稳定性和性能,提高信号质量和传输距离,降低噪声等。

锁相环PLL(PhaseLockedLoop)锁相环PLL目前我见到的所有芯片中都含有PLL模块,而且一直不知道如何利用PLL对晶振进行倍频的,这次利用维基百科好好的学习了下PLL 的原理。

1. 时钟与振荡电路在芯片中,最重要的就是时钟,时钟就像是心脏的脉冲,如果心脏停止了跳动,那人也就死亡了,对于芯片也一样。

了解了时钟的重要性,那时钟是怎么来的呢?时钟可以看成周期性的0与1信号变化,而这种周期性的变化可以看成振荡。

因此,振荡电路成为了时钟的来源。

振荡电路的形成可以分两类:1. 石英晶体的压电效应:电导致晶片的机械变形,而晶片两侧施加机械压力又会产生电,形成振荡。

它的谐振频率与晶片的切割方式、几何形状、尺寸有关,可以做得精确,因此其振荡电路可以获得很高的频率稳定度。

2. 电容Capacity的充电放电:能够存储电能,而充放电的电流方向是反的,形成振荡。

可通过电压等控制振荡电路的频率。

2. PLL与倍频由上面可以知道,晶振由于其频率的稳定性,一般作为系统的外部时钟源。

但是晶振的频率虽然稳定,但是频率无法做到很高(成本与工艺限制),因此芯片中高频时钟就需要一种叫做压控振荡器(Voltage Controlled Oscillator)的东西生成了(顾名思义,VCO 就是根据电压来调整输出频率的不同)。

可压控振荡器也有问题,其频率不够稳定,而且变化时很难快速稳定频率。

哇偶,看到这种现象是不是很熟悉?嘿嘿,这就是标准开环系统所出现的问题,解决办法就是接入反馈,使开环系统变成闭环系统,并且加入稳定的基准信号,与反馈比较,以便生成正确的控制。

PLL倍频电路因此,为了将频率锁定在一个固定的期望值,锁相环PLL出现了!一个锁相环PLL电路通常由以下模块组成:·鉴相鉴频器PFD(Phase Frequency Detector):对输入的基准信号(来自频率稳定的晶振)和反馈回路的信号进行频率的比较,输出一个代表两者差异的信号·低通滤波器LPF(Low-Pass Filter):将PFD中生成的差异信号的高频成分滤除,保留直流部分·压控振荡器VCO(Voltage Controlled Oscillator):根据输入电压,输出对应频率的周期信号。

锁相环PLL的电路原理以及基本构成锁相环(phase locked loop),顾名思义,就是锁定相位的环路。

学过自动控制原理的人都知道,这是一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,一般用于闭环跟踪电路。

是无线电发射中使频率较为稳定的一种方法,主要有VCO(压控振荡器)和PLL IC (锁相环集成电路),压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与PLL IC所产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则PLL IC的电压输出端的电压发生变化,去控制VCO,直到相位差恢复,达到锁相的目的。

能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。

PLL(锁相环)电路原理在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。

无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。

但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。

如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。

此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。

PLL(锁相环)电路的基本构成PLL(锁相环)电路的概要图1所示的为PLL(锁相环)电路的基本方块图。

此所使用的基准信号为稳定度很高的晶体振荡电路信号。

此一电路的中心为相位此较器。

相位比较器可以将基准信号与VCO (V oltage Controlled Oscillator电压控制振荡器)的相位比较。

如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。

(将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。

)。

锁相环的组成和原理及应用一.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

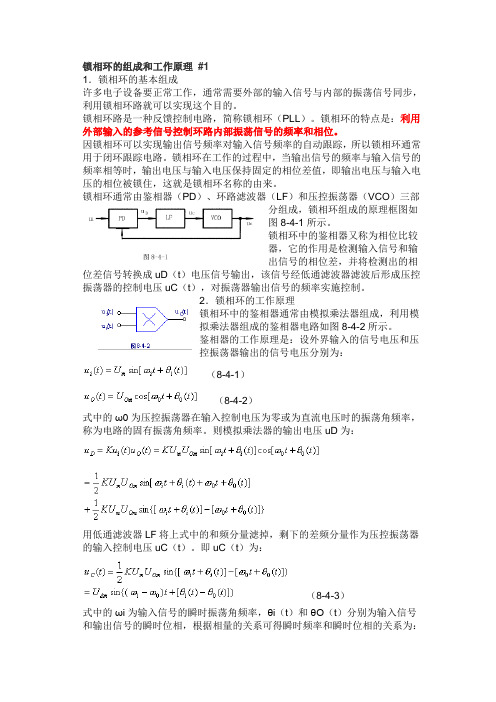

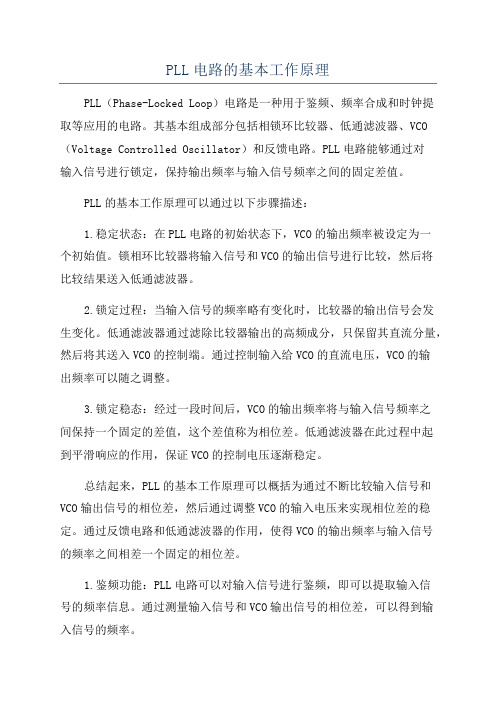

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。

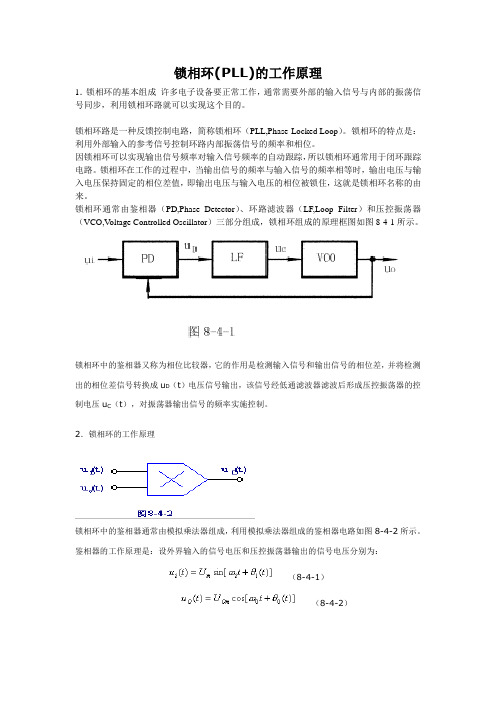

二.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压uD为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压uC(t)。

即uC(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,uc(t)为恒定值。

锁相环的基本组成锁相环(Phase Locked Loop,简称PLL)是一种常用的电子电路,用于频率合成、时钟同步和相位锁定等应用。

它由相频比较器、低通滤波器、电压控制振荡器(Voltage Controlled Oscillator,简称VCO)和分频器等基本组成部分构成。

锁相环通过不断调整VCO的频率,使其与参考信号的频率保持同步,从而实现相位和频率的锁定。

相频比较器是锁相环的核心部分之一。

它将参考信号和VCO输出的信号进行比较,并产生一个误差信号,表示两者之间的相位差。

低通滤波器用于去除误差信号中的高频成分,得到平滑的控制电压。

这个电压被送入VCO,通过改变VCO的频率来减小相位差。

通过不断调整VCO的频率,使其与参考信号的频率保持同步,最终实现相位锁定。

VCO是另一个重要的组成部分。

它根据输入的控制电压来调整输出信号的频率。

当控制电压增加时,VCO的频率也随之增加,相位差减小。

反之,当控制电压减小时,VCO的频率降低,相位差增大。

通过这样的反馈机制,VCO能够自动调整频率,使其与参考信号保持同步。

除了相频比较器、低通滤波器和VCO,锁相环还常常包含一个分频器。

分频器将VCO输出的信号进行分频,得到一个与参考信号频率相同或相倍的信号。

这个信号被送回相频比较器,与参考信号进行比较,从而实现闭环控制。

分频器的选择取决于具体应用的需求。

锁相环广泛应用于各种领域。

在通信系统中,锁相环用于时钟恢复、频率合成和时钟同步等关键任务。

在数字信号处理中,锁相环被用来实现数字时钟的生成和同步。

在模拟电路中,锁相环可以用来生成高稳定度的本地振荡信号,用于时序控制和频率合成。

锁相环的性能受到多个因素的影响。

首先是相频比较器的性能,它决定了锁相环的相位检测精度。

其次是低通滤波器的带宽,它决定了锁相环的跟踪速度和抑制高频噪声的能力。

此外,VCO的线性度和频率范围也会对锁相环的性能产生影响。

因此,在设计锁相环时,需要根据具体应用的要求,选择合适的元器件,并进行系统级的优化。

锁相环实验报告锁相环实验报告一、实验目的本次实验的目的是了解锁相环(PLL)的原理和应用,掌握PLL电路的设计和调试方法,以及了解PLL在通信系统中的应用。

二、实验原理1. PLL原理锁相环是一种基于反馈控制的电路,由比例积分环节、相位检测器、低通滤波器和振荡器等组成。

其基本原理是将输入信号与参考信号进行比较,并通过反馈调整振荡频率,使得输入信号与参考信号同步。

2. PLL应用PLL广泛应用于通信系统中,如频率合成器、时钟恢复器、数字调制解调器等。

三、实验设备和材料1. 实验仪器:示波器、函数发生器等。

2. 实验元件:电阻、电容等。

四、实验步骤1. 搭建PLL电路并连接到示波器上。

2. 调节函数发生器输出正弦波作为参考信号,并将其输入到PLL电路中。

同时,在函数发生器上设置另一个正弦波作为输入信号,并将其连接到PLL电路中。

3. 调节PLL参数,包括比例积分系数和低通滤波器截止频率等,使得输入信号与参考信号同步。

4. 观察示波器上的输出波形,记录下PLL参数的取值。

五、实验结果与分析1. 实验结果通过调节PLL参数,成功实现了输入信号与参考信号的同步,并在示波器上观察到了稳定的输出波形。

记录下了PLL参数的取值,如比例积分系数和低通滤波器截止频率等。

2. 实验分析通过本次实验,我们深入了解了锁相环的原理和应用,并掌握了PLL电路的设计和调试方法。

同时,我们也了解到PLL在通信系统中的重要作用,如时钟恢复、数字调制解调等。

六、实验结论本次实验成功地实现了输入信号与参考信号的同步,并掌握了PLL电路的设计和调试方法。

同时也加深对于PLL在通信系统中应用的认识。

七、实验注意事项1. 在搭建电路时应注意接线正确性。

2. 在调节PLL参数时应注意逐步调整,避免过度调整导致系统失控。

3. 在观察示波器输出波形时应注意放大倍数和时间基准设置。

锁相环的组成和工作原理#11.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。

2.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压uD为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压uC(t)。

即uC(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,uc(t)为恒定值。

锁相环工作原理锁相环(Phase-Locked Loop,简称PLL)是一种常用的电子电路,用于实现频率合成、时钟恢复、相位同步等功能。

它由相位比较器、低通滤波器、电压控制振荡器和分频器等组成。

本文将详细介绍锁相环的工作原理及其各个组成部分的功能和作用。

一、相位比较器(Phase Detector)相位比较器是锁相环的核心部分,其作用是比较输入信号和反馈信号的相位差,并输出相应的控制信号。

常用的相位比较器有边沿比较器、恒幅比较器和恒相位比较器等。

相位比较器的输出信号经过滤波后,作为电压控制振荡器的输入。

二、低通滤波器(Low-Pass Filter)低通滤波器主要用于滤除相位比较器输出信号中的高频噪声,保留其直流分量。

它可以采用RC电路或者激励响应滤波器等形式。

滤波后的信号经过放大后,作为电压控制振荡器的输入。

三、电压控制振荡器(Voltage-Controlled Oscillator,简称VCO)电压控制振荡器是锁相环的核心部件之一,它根据输入的控制电压来产生相应频率的输出信号。

VCO的频率与输入电压成正比关系,通过调节输入电压的大小,可以实现对输出信号频率的控制。

四、分频器(Divider)分频器用于将VCO的输出信号进行频率分频,得到所需的参考信号。

分频器通常采用可编程分频器,可以根据需要选择不同的分频比。

参考信号经过分频后,与输入信号经过相位比较器输出的控制信号相比较,得到相位误差信号。

五、反馈回路锁相环的反馈回路起到了关键的作用,它将分频器输出的参考信号反馈给相位比较器,与输入信号进行比较,从而实现相位同步。

通过不断调节VCO的频率,使得输入信号和参考信号的相位差保持在一个很小的范围内,实现了稳定的频率合成或时钟恢复。

六、工作原理锁相环的工作原理可以概括为以下几个步骤:1. 初始状态下,输入信号和参考信号的相位差较大,相位比较器输出的控制信号经过滤波器放大后,作为VCO的输入电压。

2. VCO根据输入电压产生相应频率的输出信号,经过分频器分频后得到参考信号。

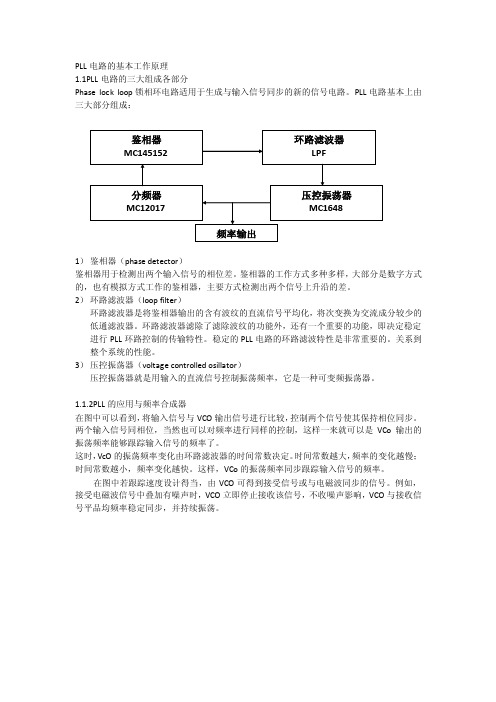

PLL电路的基本工作原理1.1PLL电路的三大组成各部分Phase lock loop锁相环电路适用于生成与输入信号同步的新的信号电路。

PLL电路基本上由三大部分组成:1)鉴相器(phase detector)鉴相器用于检测出两个输入信号的相位差。

鉴相器的工作方式多种多样,大部分是数字方式的,也有模拟方式工作的鉴相器,主要方式检测出两个信号上升沿的差。

2)环路滤波器(loop filter)环路滤波器是将鉴相器输出的含有波纹的直流信号平均化,将次变换为交流成分较少的低通滤波器。

环路滤波器滤除了滤除波纹的功能外,还有一个重要的功能,即决定稳定进行PLL环路控制的传输特性。

稳定的PLL电路的环路滤波特性是非常重要的。

关系到整个系统的性能。

3)压控振荡器(voltage controlled osillator)压控振荡器就是用输入的直流信号控制振荡频率,它是一种可变频振荡器。

1.1.2PLL的应用与频率合成器在图中可以看到,将输入信号与VCO输出信号进行比较,控制两个信号使其保持相位同步。

两个输入信号同相位,当然也可以对频率进行同样的控制,这样一来就可以是VCo输出的振荡频率能够跟踪输入信号的频率了。

这时,VcO的振荡频率变化由环路滤波器的时间常数决定。

时间常数越大,频率的变化越慢;时间常数越小,频率变化越快。

这样,VCo的振荡频率同步跟踪输入信号的频率。

在图中若跟踪速度设计得当,由VCO可得到接受信号或与电磁波同步的信号。

例如,接受电磁波信号中叠加有噪声时,VCO立即停止接收该信号,不收噪声影响,VCO与接收信号平品均频率稳定同步,并持续振荡。

另外,在图中,若VCO输出与鉴相器输入之间接入分频器,则输入频率与VCO输出频率的分频频率同步。

也就是说,VCO的振荡频率对输入信号的分频频率进行控制。

因此,若在PLL输入信号中加上由晶振等产生的稳定频率信号,并对分频器的频率进行切换,则由VCO的输出得到与输入频率同样精度的分频信号。

锁相环技术原理及fpga实现一、锁相环技术原理锁相环(Phase Locked Loop,PLL)是一种电路技术,用于在输入信号与参考信号之间产生固定的相位关系。

它由一个相位比较器、一个低通滤波器和一个控制电压源组成。

1. 相位比较器相位比较器是锁相环的核心部件,用于比较输入信号和参考信号的相位差。

常见的有两种类型:单极性和双极性。

单极性相位比较器只能检测到一个方向的相位差,而双极性可以检测两个方向的相位差。

2. 低通滤波器低通滤波器用于对比较结果进行平滑处理,去除高频噪声和不稳定因素。

3. 控制电压源控制电压源根据低通滤波器输出的直流电压来调整VCO(VoltageControlled Oscillator)的频率。

当输入信号与参考信号之间存在相位差时,控制电压源会调整VCO输出频率使其与参考信号同步。

二、FPGA实现FPGA(Field Programmable Gate Array)是一种可编程逻辑芯片,可以被重新编程以实现各种功能。

在FPGA中实现锁相环的过程主要包括以下几个步骤:1. 时钟分频器首先需要将输入信号进行分频,使其与参考信号具有相同的频率。

这可以通过时钟分频器实现,FPGA中常见的时钟分频器有计数器和DDS(Direct Digital Synthesis)。

2. 相位比较器相位比较器可以采用XOR门或D触发器等逻辑门电路实现。

其中XOR门可以检测到单极性相位差,而D触发器可以检测到双极性相位差。

3. 低通滤波器低通滤波器可以使用FPGA中的数字滤波器实现,常见的有FIR (Finite Impulse Response)和IIR(Infinite Impulse Response)滤波器。

4. 控制电压源控制电压源通常由DAC(Digital-to-Analog Converter)实现,将数字控制信号转换为模拟电压输出。

这个电压输出会通过OPA (Operational Amplifier)放大并接入VCO来调整其输出频率。

PLL电路的基本工作原理PLL(Phase-Locked Loop)电路是一种用于鉴频、频率合成和时钟提取等应用的电路。

其基本组成部分包括相锁环比较器、低通滤波器、VCO (Voltage Controlled Oscillator)和反馈电路。

PLL电路能够通过对输入信号进行锁定,保持输出频率与输入信号频率之间的固定差值。

PLL的基本工作原理可以通过以下步骤描述:1.稳定状态:在PLL电路的初始状态下,VCO的输出频率被设定为一个初始值。

锁相环比较器将输入信号和VCO的输出信号进行比较,然后将比较结果送入低通滤波器。

2.锁定过程:当输入信号的频率略有变化时,比较器的输出信号会发生变化。

低通滤波器通过滤除比较器输出的高频成分,只保留其直流分量,然后将其送入VCO的控制端。

通过控制输入给VCO的直流电压,VCO的输出频率可以随之调整。

3.锁定稳态:经过一段时间后,VCO的输出频率将与输入信号频率之间保持一个固定的差值,这个差值称为相位差。

低通滤波器在此过程中起到平滑响应的作用,保证VCO的控制电压逐渐稳定。

总结起来,PLL的基本工作原理可以概括为通过不断比较输入信号和VCO输出信号的相位差,然后通过调整VCO的输入电压来实现相位差的稳定。

通过反馈电路和低通滤波器的作用,使得VCO的输出频率与输入信号的频率之间相差一个固定的相位差。

1.鉴频功能:PLL电路可以对输入信号进行鉴频,即可以提取输入信号的频率信息。

通过测量输入信号和VCO输出信号的相位差,可以得到输入信号的频率。

2.频率合成:通过改变VCO的控制电压,可以实现VCO输出频率是输入信号频率的整数倍。

这可以用于产生高稳定性的时钟信号或者合成特定的频率信号。

3.时钟提取:PLL电路也可以用于提取时钟信号。

输入信号是待提取的信号,而VCO的输出频率是预定的时钟频率。

通过PLL电路的控制,VCO的输出信号能够与输入信号同步,从而实现时钟信号的提取。

锁相环(PLL)的工作原理1.锁相环的基本组成许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。

2.锁相环的工作原理锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。

鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为:(8-4-1)(8-4-2)式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。

则模拟乘法器的输出电压u D为:用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压u C (t)。

即u C(t)为:(8-4-3)式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:即(8-4-4)则,瞬时相位差θd为:(8-4-5)对两边求微分,可得频差的关系式为(8-4-6)上式等于零,说明锁相环进入相位锁定的状态,此时输出和输入信号的频率和相位保持恒定不变的状态,u c(t)为恒定值。

三相逆变器锁相环pll 工作原理三相逆变器是一种将直流电能转换为交流电能的设备。

它通常由逆变电路和控制电路两部分组成。

锁相环(Phase-Locked Loop,PLL)是三相逆变器中的一个重要组成部分,用于实现电网电压和逆变器输出电压之间的同步控制。

锁相环(PLL)是一种用于提取频率和相位信息的控制系统。

在三相逆变器中,PLL的主要功能是将电网电压的频率和相位信息提取出来,并与逆变器的输出电压进行比较,以实现同步控制。

具体来说,锁相环通过不断调整逆变器的输出频率和相位,使其与电网电压保持同步,从而实现电能的高效转换。

锁相环的工作原理可以简单地分为三个步骤:相频检测、滤波和控制。

首先,相频检测器会对电网电压和逆变器输出电压进行相频检测,得到它们之间的相位差和频率差。

然后,滤波器会对相位差和频率差进行滤波处理,以减小干扰和噪声的影响。

最后,控制器根据滤波后的结果,调整逆变器的输出频率和相位,使其与电网电压保持同步。

在具体实现中,锁相环通常由相频检测器、环路滤波器和控制器三部分组成。

相频检测器可以通过比较电网电压和逆变器输出电压的相位差和频率差来提取同步信息。

环路滤波器则用于对相位差和频率差进行滤波处理,以消除噪声和干扰的影响。

控制器则根据滤波后的结果,调整逆变器的输出频率和相位,使其与电网电压保持同步。

在三相逆变器中,锁相环的工作原理非常重要。

通过锁相环的同步控制,可以有效地实现逆变器输出电压与电网电压的同步,从而提高逆变器的转换效率和功率质量。

同时,锁相环还具有快速响应、高精度和抗干扰等特点,能够在电网电压波动或扰动的情况下保持逆变器的稳定运行。

总结起来,三相逆变器中的锁相环是一种用于实现电网电压和逆变器输出电压同步控制的重要组成部分。

它通过相频检测、滤波和控制等步骤,不断调整逆变器的输出频率和相位,使其与电网电压保持同步。

锁相环的工作原理能够有效提高逆变器的转换效率和功率质量,并具有快速响应、高精度和抗干扰等特点,能够保持逆变器的稳定运行。

锁相环工作原理锁相环(Phase-Locked Loop,简称PLL)是一种常用的电子电路,用于将输入信号与参考信号进行比较,并通过反馈控制,使得输出信号与参考信号保持相位一致。

锁相环广泛应用于通信系统、时钟同步、频率合成等领域。

本文将详细介绍锁相环的工作原理及其组成部分。

一、锁相环的组成部分锁相环主要由相位比较器、低通滤波器、控制电压源和振荡器四个主要部分组成。

1. 相位比较器(Phase Detector)相位比较器是锁相环的核心部分,用于比较输入信号与参考信号的相位差,并产生一个误差电压。

常见的相位比较器有异或门、乘法器等。

相位比较器的输出电压正比于输入信号与参考信号的相位差,用于驱动锁相环的控制电路。

2. 低通滤波器(Low Pass Filter)低通滤波器用于对相位比较器输出的误差电压进行滤波,去除高频噪声,得到平滑的控制电压。

低通滤波器通常采用RC滤波器或者积分器。

3. 控制电压源(Voltage Controlled Oscillator)控制电压源是锁相环的输出部分,它根据低通滤波器输出的控制电压来控制振荡器的频率和相位。

控制电压源通常采用电压控制振荡器(VCO)。

4. 振荡器(Oscillator)振荡器是锁相环的参考信号源,它产生一个稳定的参考信号,并与输入信号进行比较。

常见的振荡器有晶体振荡器、LC振荡器等。

二、锁相环的工作原理锁相环的工作原理可以分为两个阶段:捕获阶段和跟踪阶段。

1. 捕获阶段在捕获阶段,锁相环的目标是将输出信号与输入信号的相位差逐渐减小,直到达到稳定的状态。

具体步骤如下:a. 相位比较器比较输入信号与参考信号的相位差,产生一个误差电压。

b. 低通滤波器对误差电压进行滤波,得到平滑的控制电压。

c. 控制电压源根据控制电压调节振荡器的频率和相位,使得输出信号的相位逐渐接近参考信号的相位。

d. 当输出信号的相位与参考信号的相位差小于某个阈值时,进入跟踪阶段。

锁相环的组成和工作原理锁相环(Phase Locked Loop,简称PLL)是一种经常用于时钟恢复、频率合成和频率同步等应用的电路。

它由几个组成部分构成,包括相频偵测器(Phase Frequency Detector,简称PFD)、环形計數器(Divider),低通滤波器(Loop Filter)和振荡器(VoltageControlled Oscillator,简称VCO)。

锁相环通过调节振荡器的频率,以跟踪和同步输入信号的相位和频率。

锁相环的工作原理如下:1. 相频检测:锁相环的相频检测器(Phase Frequency Detector,简称PFD)用于测量输入信号和反馈信号之间的相位差和频率差。

根据相频检测器的输出,可以得到一个锁定的电压信号,该信号与相位差和频率差成正比。

2. 环形计数器:环形计数器(Divider)是用于将输出信号的频率降低至可控制范围的计数器。

当输出信号进入环形计数器时,计数器开始对信号进行计数,并输出一个较低频率的信号作为反馈信号输入到PFD中。

3. 低通滤波器:低通滤波器(Loop Filter)用于减小环形计数器输出信号的噪音,并将输出信号平滑化。

滤波器的输出电压与输入信号的频率和相位差成正比。

通过调整滤波器的参数,可以控制锁相环的锁定时间和跟踪精度。

4. 振荡器:振荡器(Voltage Controlled Oscillator,简称VCO)是一个根据输入电压的大小来调整输出频率的振荡器。

当输入电压增加时,振荡器的输出频率也会增加;当输入电压减小时,振荡器的输出频率也会减小。

在锁相环中,VCO的频率通过调节输入电压来实现相位和频率的跟踪。

当锁相环处于锁定状态时,相位差为零,频率差为零,输入信号的相位和频率与反馈信号完全同步。

如果输入信号的相位或频率发生变化,锁相环会通过调节VCO的频率来追踪这些变化,并使输入信号的相位和频率保持同步。

锁相环的工作原理可以简单描述为:输入信号经过相频检测器和环形计数器,产生一个较低频率的反馈信号。

锁相环(Phase-locked loop,简称PLL)是一种常见的电子电路,用于提供频率稳定和相位对齐的功能。

它的基本原理是通过反馈机制将输出信号的相位与参考信号的相位保持同步。

锁相环由以下几个主要部分组成:1. 相频检测器(Phase/Frequency Detector,PFD):相频检测器比较参考信号与输出信号之间的相位差,并产生一个控制信号。

2. 低通滤波器(Loop Filter):低通滤波器对相频检测器输出的控制信号进行滤波和平滑,以去除噪声和快速变化的部分。

3. 电压控制振荡器(Voltage Controlled Oscillator,VCO):电压控制振荡器产生输出信号,并根据低通滤波器输出的控制信号调整频率和相位。

4. 分频器(Divider):分频器将VCO的输出信号分频,得到一个反馈信号,用于与参考信号进行比较。

工作原理如下:1. 初始状态:PLL的初始状态下,输出信号与参考信号的相位差较大。

2. 相频检测:相频检测器比较参考信号和输出信号的相位差,并产生一个控制信号,其大小与相位差成正比。

3. 控制信号处理:控制信号经过低通滤波器滤波,去除高频噪声和快速变化的部分,得到一个平滑的控制电压。

4. 控制电压调整:控制电压作用于电压控制振荡器,调整振荡器的频率和相位。

5. 反馈信号产生:VCO的输出信号通过分频器分频,得到一个反馈信号,与参考信号进行比较。

6. 调整过程:反馈信号与参考信号的相位差通过相频检测器进行比较,并产生新的控制信号。

这个过程不断迭代,直到输出信号与参考信号的相位差趋近于零,达到锁定状态。

锁相环通过不断调整VCO的频率和相位,使输出信号与参考信号保持稳定的频率和相位关系。

它被广泛应用于时钟同步、频率合成、调制解调、通信系统和数字信号处理等领域。

PLL锁相环的基本结构及工作原理PLL(Phase Locked Loop):为锁相回路或锁相环,用来统一整合时脉讯号,使高频器件正常工作,如内存的存取资料等。

PLL用于振荡器中的反馈技术。

许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步。

一般的晶振由于工艺与成本原因,做不到很高的频率,而在需要高频应用时,有相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路就可以实现稳定且高频的时脉冲讯号。

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环,简称PLL。

它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域。

一个典型的锁相环(PLL)系统,是由鉴相器(PD),压控荡器(VCO)和低通滤波器(LPF)三个基本电路组成,如图锁相环路的捕捉与跟踪过程当锁相环路刚开始工作时,其起始时一般都处于失锁状态,由于输入到鉴相器的二路信号之间存在着相位差,鉴相器将输出误差电压来改变压控振荡器的振荡频率,使之与基准信号相一致。

锁相环由失锁到锁定的过程,人们称为捕捉过程。

系统能捕捉的最大频率范围或最大固有频带称为捕捉带或捕捉范围。

当锁相环路锁定后,由于某些原因引起输入信号或压控振荡器频率发生变化,环路可以通过自身的反馈迅速进行调节。

结果是VCO的输出频率、相位又被锁定在基准信号参数上,从而又维持了环路的锁定。

这个过程人们称为环路的跟踪过程。

系统能保持跟踪的最大频率范围或最大固有频带称为同步带或同步范围,或称锁定范围。

捕捉过程与跟踪过程是锁相环路的两种不同的自动调节过程。

由此可见,自动频率控制(AFC)电路,在锁定状态下,存在着固定频差。

而锁相环路控制(PLL)电路,在锁定状态下,则存在着固定相位差。

虽然锁相环存在着相位差,但它和基准信号之间不存在频差,即输出频率等于输入频率.这也表明,通过锁相环来进行频。

锁相环PLL的电路原理以及基本构成

锁相环(phase locked loop),顾名思义,就是锁定相位的环路。

学过自动控制原理的人都知道,这是一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,一般用于闭环跟踪电路。

是无线电发射中使频率较为稳定的一种方法,主要有VCO(压控振荡器)和PLL IC (锁相环集成电路),压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与PLL IC所产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则PLL IC的电压输出端的电压发生变化,去控制VCO,直到相位差恢复,达到锁相的目的。

能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。

PLL(锁相环)电路原理

在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。

无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电

路比较。

但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。

如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。

此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。