八位加法器设计实验报告

- 格式:doc

- 大小:1.10 MB

- 文档页数:10

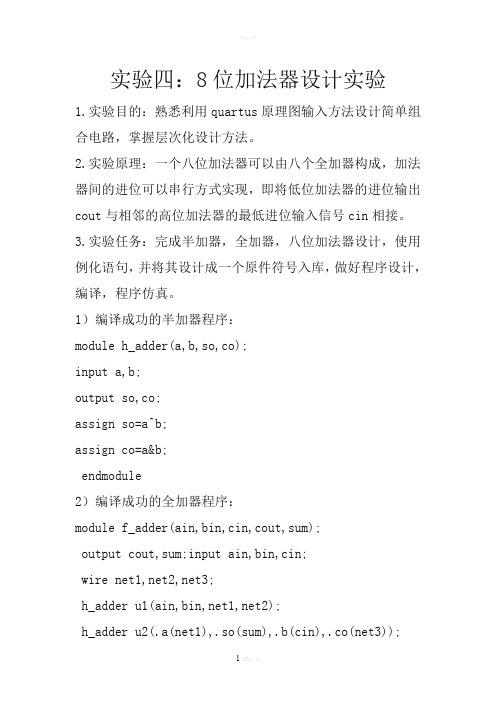

实验四:8位加法器设计实验1.实验目的:熟悉利用quartus原理图输入方法设计简单组合电路,掌握层次化设计方法。

2.实验原理:一个八位加法器可以由八个全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的最低进位输入信号cin相接。

3.实验任务:完成半加器,全加器,八位加法器设计,使用例化语句,并将其设计成一个原件符号入库,做好程序设计,编译,程序仿真。

1)编译成功的半加器程序:module h_adder(a,b,so,co);input a,b;output so,co;assign so=a^b;assign co=a&b;endmodule2)编译成功的全加器程序:module f_adder(ain,bin,cin,cout,sum);output cout,sum;input ain,bin,cin;wire net1,net2,net3;h_adder u1(ain,bin,net1,net2);h_adder u2(.a(net1),.so(sum),.b(cin),.co(net3));or u3(cout,net2,net3);endmodule3)编译成功的八位加法器程序:module f_adder8(ain,bin,cin,cout,sum);output [7:0]sum; output cout;input [7:0]ain,bin;input cin;wire cout0, cout1, cout2 ,cout3, cout4,cout5,cout6; f_adderu0(.ain(ain[0]),.bin(bin[0]),.cin(cin),.sum(sum[0]) ,.cout(cout0));f_adderu1(.ain(ain[1]),.bin(bin[1]),.cin(cout0),.sum(sum[1 ]),.cout(cout1));f_adderu2(.ain(ain[2]),.bin(bin[2]),.cin(cout1),.sum(sum[2 ]),.cout(cout2));f_adderu3(.ain(ain[3]),.bin(bin[3]),.cin(cout2),.sum(sum[3 ]),.cout(cout3));f_adderu4(.ain(ain[4]),.bin(bin[4]),.cin(cout3),.sum(sum[4]),.cout(cout4));f_adderu5(.ain(ain[5]),.bin(bin[5]),.cin(cout4),.sum(sum[5 ]),.cout(cout5));f_adderu6(.ain(ain[6]),.bin(bin[6]),.cin(cout5),.sum(sum[6 ]),.cout(cout6));f_adderu7(.ain(ain[7]),.bin(bin[7]),.cin(cout6),.sum(sum[7 ]),.cout(cout));endmodule4)八位加法器仿真程序:module f_adder8_vlg_tst();// constants // general purpose registers//reg eachvec;// test vector input registersreg [7:0] ain;reg [7:0] bin;reg cin;// wires wire cout;wire [7:0] sum;// assign statements (if any) f_adder8 i1 (// port map - connection between master ports and signals/registers.ain(ain),.bin(bin),.cin(cin),.cout(cout),.sum(sum));initial begin ain=10;bin=11;cin=0;#100 ain=10;bin=10;cin=0;#100 ain=10;bin=10;cin=1;#100 ain=12;bin=18;cin=0;#100 ain=12;bin=18;cin=1;#100 $stop;endendmodule5)八位加法器仿真图:6)元件原理图及元件入库:半加器原理图:文件入库bsf:全加器原理图:全加器元件入库:八位全加器rtl图:八位全加器仿真图:精品文档。

湖北汽车工业学院计算机组成原理实验报告一、实验目的本次实验旨在通过搭建和设计8位加法器电路,掌握计算机组成原理中加法器的基本原理和实现方法。

二、实验原理1.8位加法器8位加法器是一种用于执行二进制数相加的逻辑电路。

基本的8位加法器是由8个全加器组成的,在8个输入位和一个进位输入位中,通过逻辑门、逻辑电路互连、时钟信号等实现。

输出为一个8位的和,以及一个进位输出。

2.全加器全加器是指一个三输入二输出的逻辑电路,它可以实现两个二进制位的相加运算,并且能够接收来自前一位的进位。

全加器的输入包括三个二进制位,分别为两个相加的二进制位和来自前一位的进位,输出也是两个二进制位,分别为相加的结果和向后传递的进位。

三、实验步骤1.利用电线和逻辑门,按照电路原理图搭建8位加法器电路,并连接时钟信号。

2.在适当的位置输入两个8位的二进制数,并设置进位输入。

3.使用示波器来观察输出的和和进位。

四、实验结果五、实验分析1.实验结果验证了8位加法器的设计和搭建的正确性,能够准确地进行二进制数相加运算,并正确输出和进位结果。

2.通过使用示波器观察输出的和和进位,不仅可以直观地了解到加法器电路的工作原理,还可以帮助我们检验加法器的正确性。

六、实验总结通过本次实验,我深入了解了计算机组成原理中加法器的基本原理和实现方法,并通过实际搭建和设计电路的方式进行了验证。

通过观察实验结果和使用示波器测量输出,我对加法器电路的工作原理有了更加深入的理解。

此外,本次实验还加强了我与逻辑门、逻辑电路的熟悉,并提升了我分析和解决问题的能力。

通过实验过程中的调试和验证,我学会了容易出错的地方以及如何进行错误排查。

总之,本次实验在计算机组成原理的学习中起到了非常重要的作用,使我能够更好地理解和掌握课程知识。

《组成原理》实验报告姓名:***____________专业:网络工程________学号:**********______日期:2014年11月25日实验一:8位运算器的设计1,设计目的:1)学习并练习verilog语言2)了解8位加法器实现原理2,设计目标:1)使用verilog语言编写8为运算器并进行仿真模拟3,模块设计规格及输入输出端变量说明1)3模块设计规格及输入输出端变量说明:输入:[2:0]s(操作指令), LDA,LDB(输入控制), [7:0]IN(输入数);输出:[7:0]A,B(操作数), ALU(结果寄存器),FZ(判零), FC(进位);2)操作指令表:4,程序原理连接图5,程序代码Module test (T4,s,A,B,LDA,LDB,FZ,FC,IN,ALU);input [2:0] s;input LDA,LDB,T4;input [7:0] IN;output [7:0] A,B,ALU;output FZ,FC;reg [7:0] A,B,ALU;reg FZ,FC;/** 输入模块,当clk上升沿时,如果LDA为1,则把IN的值给A,否则赋给B */always @ (posedge CLK)beginif(LDA==1'b1)beginA<=IN;endelse if(LDB==1'b1)beginB<=IN;endend/**计算模块,根据操作数s的不同值为A和B进行八种不同的计算,其中当A+B *进行加法计算时,把进位值赋给FC*/always @ (s[2] or s[1] or s[0])begincase ({s[2],s[1],s[0]})3'b000:ALU<=A;//直接赋值3'b001:ALU<=A&B;//A与B按位与3'b010:ALU<=A|B;//A与B按位或3'b011:ALU<=~A;//非A3'b100:ALU<=(A<<1);//A左移一位3'b101:{FC,ALU}<=A+B;//ALU=A+B,FC为A+B的进位3'b110:ALU<=A+1;//加一操作3'b111:ALU<=A-1;//减一操作endcaseend/**该模块的作用是判断ALU是否为,若是FZ赋为1*/always @ (negedge T4)beginif(ALU==8'b00000000)FZ<=1'b1;elseFZ<=1'b0;endendmodule6时序仿真图:。

E D A技术实验报告题目实验一、8位加法器的设计学生姓名学号10100140所在学院物理与电信工程学院专业班级物理101班一、实验原理基本原理:调用库(USE IEEE.STD_LOGIC_ARITH.ALL)直接进行算术运算,以实现加法器功能,从而不用去编写全加器,即程序尽量简单化。

并用函数CONV_INTEGER(D)把输入的8位二进制数转换成整形数,再相加以十进制数在数码管上显示出来。

加法信号由(ST)控制,ST接一个正脉冲信号,当来一个下降沿时,就读进第一个8位二进制数,再来一个下降沿时就执行加法功能,前后两个8位二进制数相加。

进程process (p)就是把三位十进制数的百位、十位、各位分别取出来,再转换成4位逻辑位矢量。

一个简单加法器,能够实现加法运算并显示结果,在按键控制下,由开关变量以二进制(不超过8位)的形式送入加数和被加数,但必须以十进制的形式显示,按下加法按键后,以十进制方式显示结果。

根据要求首先加法器中必须有二进制(8位)转换成十进制电路,其次加法器中需要用开关变量来控制加数和被加数的输入,再次输入的二进制加数和被加数必须经过转换成十进制后显示,最后加法完成结果以十进制显示。

其二进制(8位)全为1时转换成十进制表示为255,先设三位分别表示十进制数的百位、十位和个位。

将二进制数分别减去100的二进制数,循环直至二进制数小于100,百位循环一次加一,根据同样的道理得出十位和个位。

加数和被加数的输入和显示,利用高低电平控制显示器,当电平为高电平时显示加数和被加数的和,利用选择器来分别选择输出显示,当低电平时分别显示输入的二进制加数和被加数。

加法器是数字系统中的基本逻辑器件,减法器和硬件乘法器都可由加法器来构成。

多位加法器的构成有两种方式:并行进位和串行进位。

并行进位加法器设有进位产生逻辑,运算速度较快;串行进位方式是将全加器级联构成多位加法器。

并行进位加法器通常比串行级联加法器占用更多的资源。

计算机科学与技术学院计算机组成原理实验报告书实验名称八位补码加/减法器的设计与实现班级学号姓名指导教师日期成绩实验1八位补码加/减法器的设计与实现一、实验目的1.掌握算术逻辑运算单元(ALU)的工作原理。

2.熟悉简单运算器的数据传送通路。

3.掌握8位补码加/减法运算器的设计方法。

4.掌握运算器电路的仿真测试方法二、实验任务1.设计一个8位补码加/减法运算器(1)参考图1,在QUARTUS II里输入原理图,设计一个8位补码加/减法运算器。

(2)创建波形文件,对该8位补码加/减法运算器进行功能仿真测试。

(3)测试通过后,封装成一个芯片。

2.设计8位运算器通路电路参考下图,利用实验任务1设计的8位补码加/减法运算器芯片建立运算器通路。

3.利用仿真波形,测试数据通路的正确性。

设定各控制信号的状态,完成下列操作,要求记录各控制信号的值及时序关系。

(1)在输入数据IN7~IN0上输入数据后,开启输入缓冲三态门,检查总线BUS7~BUS0上的值与IN0~IN7端输入的数据是否一致。

(2)给DR1存入55H,检查数据是否存入,请说明检查方法。

(3)给DR2存入AAH,检查数据是否存入,请说明检查方法。

(4)完成加法运算,求55H+AAH,检查运算结果是否正确,请说明检查方法。

(5)完成减法运算,分别求55H-AAH和AAH-55H,检查运算结果是否正确,请说明检查方法。

(6)求12H+34H-56H,将结果存入寄存器R0,检查运算结果是否正确,同时检查数据是否存入,请说明检查方法。

三、实验要求(1)做好实验预习,掌握运算器的数据传送通路和ALU的功能特性。

(2)实验完毕,写出实验报告,内容如下:①实验目的。

②实验电路图。

③按实验任务3的要求,填写下表,以记录各控制信号的值及时序关系。

表中的序号表示各控制信号之间的时序关系。

要求一个控制任务填一张表,并可用文字对有关内容进行说明。

⑤实验体会与小结。

四、实验预习内容1.实验电路设计原理及思路说明本实验利用基本逻辑门电路设计一位全加器(FA),如表1:加法又可以实现减法,所以使用了一个M输入来进行方式控制加减。

CMOS数字集成电路设计课程设计报告学院:******专业:******班级:******姓名:Wang Ke qin指导老师:******学号:******日期:2012-5-30目录一、设计要求..............................................错误!未定义书签。

二、设计思路..............................................错误!未定义书签。

三、电路设计与验证........................................错误!未定义书签。

(一) 1位全加器的电路设计与验证........................错误!未定义书签。

1) 原理图设计......................................错误!未定义书签。

2) 生成符号图......................................错误!未定义书签。

3) 建立测试激励源..................................错误!未定义书签。

4) 测试电路........................................错误!未定义书签。

5) 波形仿真........................................错误!未定义书签。

(二) 4位全加器的电路设计与验证........................错误!未定义书签。

1) 原理图设计......................................错误!未定义书签。

2) 生成符号图......................................错误!未定义书签。

3) 建立测试激励源..................................错误!未定义书签。

实验六8位全加器的设计实验报告一、实验要求1、GW48实验箱;2、用原理图输入方式设计8位全加器,并进行编译、仿真、下载;3、总结实验步骤和实验结果。

二、实验内容1、本设计中的8位二进制并行加法器即是由两个4位二进制并行加法器级联而成的,其电路原理图如图所示2、完成4位全加器ADDER4B的设计,并将此全加器电路设置成一个硬件符号入库。

建立一个更高的原理图设计层次,可以取名为ADDER8B。

利用以上获得的4位全加器构成8位全加器,并完成编译,仿真和硬件测试。

3、硬件逻辑验证:选择实验电路结构图NO.1和上图确定引脚的锁定。

如可取实验电路结构图的PIO3~PIO0接A[3..0],PIO7~PIO4接A[7..4],PIO11~PIO8接B[3..0],PIO15~PIO12接B[7..4],PIO49接CIN。

此加法器的被加数A和加数B分别由键2与键1、键4与键3输入,加法器的最低位进位CIN由键8输入,计算和S将分别通过PIO23~PIO20,PIO19~PIO16输出并显示于数码管6(高四位)和数码管5(低四位),溢出进位COUT由PIO39输出,当有进位时,结果显示于发光管D8上。

参考源程序:4位二进制并行加法器的源程序ADDER4Bmodule ADDER4B(A,B,CIN,S,CONT);output [3:0]S;output CONT;input [3:0]A,B;input CIN;assign {CONT, S}=A+B+CIN;endmodule三、实验步骤1、创建文件Max-plus->text editor源代码2、创建缺省符号(Creat Default Symbol)然后添加到框图中:3、连线并标注接口4、编译5、仿真6、下载1)引脚锁定2)开始下载四、实验结果选择实验电路结构图NO.1,此加法器的被加数A和加数B分别由键2与键1、键4与键3输入,加法器的最低位进位CIN由键8输入,当有进位时,结果显示于发光管D8上。

8位全加器课程设计报告一、课程目标知识目标:1. 学生理解8位全加器的基本概念,掌握全加器的逻辑结构和工作原理;2. 学生掌握8位全加器的电路图绘制方法,能分析并解释全加器中各个部分的作用;3. 学生了解8位全加器在计算机运算中的应用,理解其重要性。

技能目标:1. 学生能够运用所学知识,独立完成8位全加器的电路图设计;2. 学生能够运用逻辑门电路,搭建8位全加器电路,并进行功能验证;3. 学生能够通过实际操作,提高解决问题的能力和团队协作能力。

情感态度价值观目标:1. 学生培养对电子技术课程的兴趣,激发学习热情;2. 学生在学习过程中,树立正确的科学态度,注重实践,勇于创新;3. 学生通过团队合作,培养沟通与协作能力,增强集体荣誉感。

课程性质分析:本课程为电子技术课程的一部分,重点在于让学生掌握8位全加器的原理和应用,培养实际操作能力。

学生特点分析:八年级学生具有一定的电子技术基础,对电路有一定的了解,但可能对全加器的理解尚浅,需要通过具体实例和操作来加深理解。

教学要求分析:本课程要求教师以理论与实践相结合的方式进行教学,注重培养学生的实际操作能力和团队协作能力。

在教学过程中,关注学生的个体差异,给予个性化指导,确保课程目标的实现。

通过本课程的学习,学生能够达到上述具体的学习成果。

二、教学内容1. 引言:介绍全加器在数字电路中的重要性,回顾一位全加器的基本原理,引出8位全加器的研究意义。

2. 理论知识:a. 8位全加器的定义和功能;b. 8位全加器的逻辑结构,包括加法器、进位发生器和进位传递部分;c. 8位全加器的真值表和逻辑表达式。

3. 实践操作:a. 8位全加器电路图的绘制;b. 利用集成电路芯片搭建8位全加器电路;c. 电路功能测试及故障排查。

4. 应用拓展:a. 8位全加器在计算机运算中的应用案例;b. 探讨8位全加器与其他数字电路模块的组合应用。

教学大纲安排:第一课时:引言及理论知识(1、2a)第二课时:理论知识(2b、2c)第三课时:实践操作(3a、3b)第四课时:实践操作(3c)第五课时:应用拓展(4a、4b)教材章节关联:本教学内容与教材中“第十章 数字电路及其应用”相关,涉及全加器部分的内容,与教材中的理论知识和实践操作相结合,确保学生能够系统地学习和掌握8位全加器的相关知识。

南通大学计算机科学与技术学院课程实验报告

课程名称:计算机组成原理年级:2012级上机日期:11月6日姓名:学号:班级:信管122

实验名称:八位全加器设计教师:陈越成绩:

上图为n个1位的全加器FA级联成的n位的行波进位加减器。

M为方式控制输入线,当M=0时,做加法运算;当M=1时,做减法运算。

图中左边还表示出单符号位法的溢出检测逻辑:当C n=C n-1时,运算无溢出;而当C n≠C n-1时,运算有溢出,经异或门产生溢出信号,0无溢出,1表示溢出。

四、内容及步骤(包括程序流程及说明)

1.建立add8项目

2.建立一位全加器原理图,输入如下

3.将一位全加器封装成芯片FA,如图

4.将FA级联成8位全加器如图,至此8位全加器原理图设计完毕

四、运行结果

建立波形文件,验证8位全加器。

实验一:8位全加器实验步骤1、熟悉QUARTUSⅡ集成开发环境;2、熟悉GW48-PK2型FPGA实验箱;3、编写8位全加器的Verilog HDL源代码;4、完成计算机模拟功能仿真;5、下载到Altera ACEXEP1K30中,使用实验箱完成硬件验证;6、完成实验报告实验要求8位全加器输入:Clk,Rst_,In1,In2,Cin输出:Count,Sum1.实验代码如下:module adder_8(Cout,Sum,In1,In2,Cin,Rst_,Clk);input[7:0]In1,In2;input Clk,Rst_,Cin;output[7:0]Sum;output Cout;reg[7:0]Sum;reg Cout;always@(posedge Clk)beginif(!Rst_)beginSum<=8'b0000_0000;Cout<=1'b0;endelse{Cout,Sum}=In1+In2+Cin;endendmodule2.实验仿真截图如下:(1)无输出进位的仿真截图:说明1:此图中,由于加数和被加数都比较小,导致高位没有进位。

此图中,输入低位进位设为总为1,所以和总是比两个加数直接相加所得结果大1。

只有时钟脉冲上升沿到达时,此之前的加数相加在复位端为高电平时所加和才不为零,其他所加结果都为零。

而且在图中,采集频率要比时钟频率高,也即加数和被加数及所加的和的数字采集时间要比时钟慢。

如图中,时钟的周期是10ns,数字采集周期是20ns,所以图中和的结果总是比加数有延迟。

(2)有输出进位得仿真截图:说明2:此图中,由于加数和被加数都比较大,所以有输出进位。

图中低位进位与(1)图相比,有0又有1,所以结果也和(1)中略有不同。

只有时钟脉冲上升沿到达时,此之前的加数相加在复位端为高电平时所加和才不为零,其他所加结果都为零。

且和(1)中一样,图中,采集频率要比时钟频率高,也即加数和被加数及所加的和的数字采集时间要比时钟慢。

实验四:8位加法器设计实验

1.实验目的:熟悉利用quartus原理图输入方法设计简单组合电路,掌握层次化设计方法。

2.实验原理:一个八位加法器可以由八个全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的最低进位输入信号cin相接。

3.实验任务:完成半加器,全加器,八位加法器设计,使用例化语句,并将其设计成一个原件符号入库,做好程序设计,编译,程序仿真。

1)编译成功的半加器程序:

module h_adder(a,b,so,co);

input a,b;

output so,co;

assign so=a^b;

assign co=a&b;

endmodule

2)编译成功的全加器程序:

module f_adder(ain,bin,cin,cout,sum);

output cout,sum;input ain,bin,cin;

wire net1,net2,net3;

h_adder u1(ain,bin,net1,net2);

h_adder u2(.a(net1),.so(sum),.b(cin),.co(net3));

or u3(cout,net2,net3);

endmodule

3)编译成功的八位加法器程序:

module f_adder8(ain,bin,cin,cout,sum);

output [7:0]sum; output cout;input [7:0]ain,bin;input cin;

wire cout0, cout1, cout2 ,cout3, cout4,cout5,cout6; f_adder

u0(.ain(ain[0]),.bin(bin[0]),.cin(cin),.sum(sum[0]) ,.cout(cout0));

f_adder

u1(.ain(ain[1]),.bin(bin[1]),.cin(cout0),.sum(sum[1 ]),.cout(cout1));

f_adder

u2(.ain(ain[2]),.bin(bin[2]),.cin(cout1),.sum(sum[2 ]),.cout(cout2));

f_adder

u3(.ain(ain[3]),.bin(bin[3]),.cin(cout2),.sum(sum[3 ]),.cout(cout3));

f_adder

u4(.ain(ain[4]),.bin(bin[4]),.cin(cout3),.sum(sum[4

]),.cout(cout4));

f_adder

u5(.ain(ain[5]),.bin(bin[5]),.cin(cout4),.sum(sum[5 ]),.cout(cout5));

f_adder

u6(.ain(ain[6]),.bin(bin[6]),.cin(cout5),.sum(sum[6 ]),.cout(cout6));

f_adder

u7(.ain(ain[7]),.bin(bin[7]),.cin(cout6),.sum(sum[7 ]),.cout(cout));

endmodule

4)八位加法器仿真程序:

module f_adder8_vlg_tst();

// constants // general purpose registers

//reg eachvec;

// test vector input registers

reg [7:0] ain;

reg [7:0] bin;

reg cin;

// wires wire cout;

wire [7:0] sum;

// assign statements (if any) f_adder8 i1 (

// port map - connection between master ports and signals/registers

.ain(ain),

.bin(bin),

.cin(cin),

.cout(cout),

.sum(sum)

);

initial begin ain=10;bin=11;cin=0;

#100 ain=10;bin=10;cin=0;

#100 ain=10;bin=10;cin=1;

#100 ain=12;bin=18;cin=0;

#100 ain=12;bin=18;cin=1;

#100 $stop;

end

endmodule

5)八位加法器仿真图:

6)元件原理图及元件入库:

半加器原理图:

文件入库bsf:

全加器原理图:

全加器元件入库:

八位全加器rtl图:

八位全加器仿真图:。