ARM_CORTEX-M3指令集

- 格式:xls

- 大小:27.50 KB

- 文档页数:5

名字功能带进位加法加法宽加法(可以加位立即数)按位与(原文是逻辑与,有误——译注)算术右移位清零(把一个数按位取反后,与另一个数逻辑与)位段清零位段插入负向比较(把一个数和另一个数地二进制补码比较,并更新标志位)比较两个数并更新标志位计算前导零地数目按位异或逻辑左移逻辑右移乘加乘减把位立即数放到寄存器地底位,高位清加载位立即数到寄存器(其实汇编器会产生——译注)把位立即数放到寄存器地高位,低位不影响移动一个数地补码乘法按位或(原文为逻辑或,有误——译注)把源操作数按位取反后,再执行按位或(原文为逻辑或,有误——译注)位反转(把一个位整数先用进制表达,再旋转度——译注)对一个位整数做按字节反转对一个位整数地高低半字都执行字节反转对一个位整数地低半字执行字节反转,再带符号扩展成位数圆圈右移带进位地逻辑右移一格(最高位用填充,且不影响地值——译注)从一个位整数中提取任意地位段,并且带符号扩展成位整数带符号除法带符号长乘加(两个带符号地位整数相乘得到位地带符号积,再把积加到另一个带符号位整数中)带符号长乘法(两个带符号地位整数相乘得到位地带符号积)带符号地饱和运算带借位地减法减法宽减法,可以减位立即数字节带符号扩展到位数测试是否相等(对两个数执行异或,更新标志但不存储结果)测试(对两个数执行按位与,更新标志但不存储结果)无符号位段提取无符号除法无符号长乘加(两个无符号地位整数相乘得到位地无符号积,再把积加到另一个无符号位整数中)无符号长乘法(两个无符号地位整数相乘得到位地无符号积)无符号饱和操作(但是源操作数是带符号地——译注)字节被无符号扩展到位(高位清——译注)半字被无符号扩展到位(高位清——译注)。

wordARMCortex-M3内核结构2.1ARMCortex-M3处理器简介概述ARM公司成立于上个世纪九十年代初,致力于处理器内核研究,ARM 即Advanced RISC Machines的缩写,ARM公司本身不生产芯片,只设计内核,靠转让设计许可,由合作伙伴公司来生产各具特色的芯片。

这种运行模式运营的成果受到全球半导公司以与用户的青睐。

目前ARM体系结构的处理器内核有:ARM7TDMI、ARM9TDMI、ARM10TDMI、ARM11以与Cortex等。

2005年ARM推出的ARMCortex系列内核,分别为:A系列、R系列和M系列,其中A系列是针对可以运行复杂操作系统〔Linux、WindowsCE、Symbian等〕的处理器;R系列是主要针对处理实时性要求较高的处理器〔汽车电子、网络、影像系统〕;M系列又叫微控制器,对开发费用敏感,对性能要求较高的场合。

Cortex-M系列目前的产品有M0、M1、M3,其中M1用在FPGA中。

Cortex-M系列对微控制器和低本钱应用提供优化,具有低本钱、低功耗和高性能的特点,能够满足微控制器设计师进展创新设计的需求。

其中,ARMCortex-M3处理器的性能是ARM7的两倍,而功耗却只有ARM7的1/3,适用于众多高性能、极其低本钱需求的嵌入式应用,如微控制器、汽车系统、大型家用电器、网络装置等,ARMCortex-M3提供了32位微控制器市场前所未有的优势。

Cortex-M3内核,内部的数据路径为32位,存放器为32位,存储器接口也是32位。

Cortex-M3采用了哈佛结构,拥有独立的指令总线和数据总线,可以让取指与数据访问分开进展。

Cortex-M3还提供一个可选的MPU,对存储器进展保护,而且在需要的情况下也可以使用外部的cache。

另外在Cortex-M3中,存储器支持小端模式和大端存储格式。

Cortex-M3内部还附赠了很多调试组件,用于在硬件水平上支持调试操作,如指令断点,数据观察点等。

Cortex-M系列处理器指令集_指令集特性比较总结1、指令集简介大多数情况下,应用程序代码可以用C或其他高级语言编写。

但是,对Cortex-M 处理器支持指令集的基本了解有助于开发者针对具体应用选择合适的Cortex-M处理器。

指令集(ISA)是处理器架构的一部分,Cortex-M处理器可以分为几个架构规范。

所有的Cortex-M 处理器都支持Thumb指令集。

整套Thumb指令集扩展到Thumb-2版本时变得相当大。

但是,不同的Cortex-M处理器支持不同的Thumb 指令集的子集,如图3所示2、Cortex-M0/M0+/M1指令集Cortex-M0/M0+/M1处理器基于ARMv6-M架构。

这是一个只支持56条指令的小指令集,大部分指令是16位指令,如图3所示只占很小的一部分。

但是,此类处理器中的寄存器和处理的数据长度是32位的。

对于大多数简单的I/O控制任务和普通的数据处理,这些指令已经足够了。

这么小的指令集可以用很少的电路门数来实现处理器设计,Cortex-M0 和Cortex-M0+最小配置仅仅12K门。

然而,其中的很多指令无法使用高位寄存器(R8 到R12),并且生成立即数的能力有限。

这是平衡了超低功耗和性能需求的结果。

3、Cortex-M3指令集Cortex-M3处理器是基于ARMv7-M架构的处理器,支持更丰富的指令集,包括许多32位指令,这些指令可以高效的使用高位寄存器。

另外,M3还支持:查表跳转指令和条件执行(使用IT指令)硬件除法指令乘加指令(MAC)各种位操作指令更丰富的指令集通过几种途径来增强性能;例如,32位Thumb指令支持了更大范围的立即数,跳转偏移和内存数据范围的地址偏移。

支持基本的DSP操作(例如,支持若干条需要多个时钟周期执行的MAC指令,还有饱和运算指令)。

最后,这些32位指令允许用单个指令对多个数据一起做桶型移位操作。

支持更丰富的指令导致了更大的面积成本和更高的功耗。

Arm Cortex-M3程序运行机制1. 引言在当今科技快速发展的时代,嵌入式系统在各个领域都有着广泛的应用。

而Arm Cortex-M3处理器作为一款低功耗、高性能的嵌入式处理器,其程序运行机制尤为重要。

本文将详细探讨Arm Cortex-M3程序运行机制,以帮助读者更深入地理解这一主题。

2. 程序运行机制概述在开始深入探讨Arm Cortex-M3程序运行机制之前,我们先来了解一下其基本概念。

Arm Cortex-M3处理器采用哈佛结构,将指令和数据存储在不同的存储器中,这有利于提高处理器的并行度和性能。

而其程序运行机制主要包括指令获取、指令解码、指令执行和结果写回等步骤。

3. 指令获取在程序运行过程中,处理器首先需要从存储器中获取指令。

Arm Cortex-M3处理器采用了高速缓存和预取技术,以提高指令获取的效率。

处理器还会根据指令的位置区域生成预取请求,以确保能够及时获取到所需的指令。

4. 指令解码当指令被获取到后,处理器需要对指令进行解码,以确定其具体的操作。

Arm Cortex-M3处理器采用了精简指令集(RISC)架构,使得指令解码的过程更加高效。

处理器还会根据指令类型和操作数的位置等信息,对指令进行进一步的解析和处理。

5. 指令执行在指令解码完成后,处理器会根据指令的类型和操作数,执行相应的操作。

对于不同类型的指令,处理器会采用不同的执行单元和执行流水线,以确保指令的高效执行。

处理器还会根据需要进行寄存器操作和内存访问等操作,以完成指令的执行过程。

6. 结果写回在指令执行完成后,处理器会将计算的结果写回寄存器或存储器中。

处理器还会更新程序计数器(PC)的值,以指向下一条需要执行的指令。

这样,整个程序运行的过程就完成了一次循环,从而实现了指令的连续执行。

7. 总结和回顾通过以上对Arm Cortex-M3程序运行机制的全面探讨,我们可以看到其采用了一系列高效的技术和方法,以确保程序能够高效地运行。

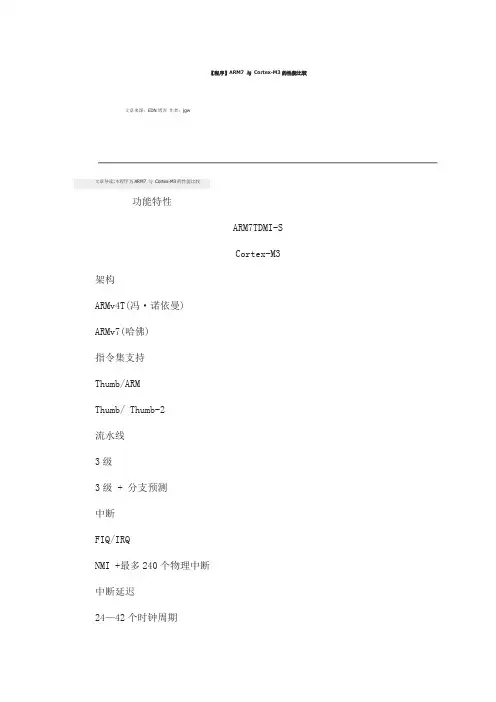

【程序】ARM7 与 Cortex-M3的性能比较文章来源:EDN 博客 作者:jgw文章导读:本程序为ARM7 与 Cortex-M3的性能比较功能特性 ARM7TDMI-SCortex-M3架构ARMv4T(冯·诺依曼)ARMv7(哈佛)指令集支持Thumb/ARMThumb/ Thumb-2流水线3级3级 + 分支预测中断FIQ/IRQNMI +最多240个物理中断中断延迟24—42个时钟周期12个时钟周期休眠模式无内置存储器保护无8段存储器保护单元指令执行速度0.95DMIPS/MHz (ARM模式)1.25DMIPS/MHz功耗0.28mW/MHz0.19mW/MHz面积0.62m2(仅内核)0.86m2(内核 + 外设)* 存储器映射方式4G空间有厂家自由划分4G空间划分由内核确定处理器模式7种处理器模式2种处理器模式*不包含可选系统外设(MPU和ETM)或者集成的部件最近有点小空,想学习一下眼下最流行的ARM,初步了解主流的ARM体系有2个:ARM7和Cortex-M3,下午在网上搜索了一下,结果令我大吃一惊。

本来我以为只要在市场上能共存的两种东西,肯定是各有千秋,否则其中较弱的的一个就会被彻底淘汰。

事实上我看到的却是完全一边倒的局面:Cortex-M3完胜ARM7!以下是摘录的一些对比:Cortex-M3 ARM7最新的ARM内核成熟使用近10年的ARM内核哈佛体系冯诺曼体系只支持最新的Thumb-2指令集支持ARM和Thumb指令集硬件自动压栈软件手工压栈单周期乘法指令多周期乘法指令2-12周期除法指令无除法指令有位操作无位操作内置系统节拍定时器无系统节拍定时器方便操作系统移植指令执行速度1.25DMIPS/MHz 0.95DMIPS/MHz功耗0.19mW/MHz 0.28mW/MHz从以上对比看,Cortex-M3在性能和功耗等方面基本上是完胜ARM7。

ARM Cortex-M3相比于ARM其他系列微控制器,具有以下优势或特点:1. 三级流水线+分支预测ARM Cortex-M3与ARM7内核一样,采用适合于微控制器应用的三级流水线,但增加了分支预测功能。

现代处理器大多采用指令预取和流水线技术,以提高处理器的指令执行速度。

流水线处理器在正常执行指令时,如果碰到分支(跳转)指令,由于指令执行的顺序可能会发生变化,指令预取队列和流水线中的部分指令就可能作废,而需要从新的地址重新取指、执行,这样就会使流水线“断流”,处理器性能因此而受到影响。

特别是现代C语言程序,经编译器优化生成的目标代码中,分支指令所占的比例可达10-20%,对流水线处理器的影响会的更大。

为此,现代高性能流水线处理器中一般都加入了分支预测部件,就是在处理器从存储器预取指令时,当遇到分支(跳转)指令时,能自动预测跳转是否会发生,再从预测的方向进行取指,从而提供给流水线连续的指令流,流水线就可以不断地执行有效指令,保证了其性能的发挥。

ARM Cortex-M3内核的预取部件具有分支预测功能,可以预取分支目标地址的指令,使分支延迟减少到一个时钟周期。

2. 哈佛结构从内核访问指令和数据的不同空间与总线结构,可以把处理器分为哈佛结构和普林斯顿结构(或冯.诺伊曼结构)。

冯.诺伊曼结构的机器指令、数据和I/O共用一条总线,这样内核在取指时就不能进行数据读写,反之亦然。

这在传统的非流水线处理器(如MCS51)上是没有什么问题的,它们取指、执行分时进行,不会发生冲突。

但在现代流水线处理器上,由于取指、译码和执行是同时进行的(不是同一条指令),一条总线就会发生总线冲突,必须插入延迟等待,从而影响了系统性能。

ARM7TDMI内核就是这种结构的。

而哈佛结构的处理器采用独立的指令总线和数据总线,可以同时进行取指和数据读写操作,从而提高了处理器的运行性能。

ARMCortex-M3、ARM966E、ARM926EJ、ARM1136JF等内核都采用了哈佛结构。

ARMCortexM3指令集⼀、跳转指令跳转指令⽤于实现程序流程的跳转,在ARM 程序中有两种⽅法可以实现程序流程的跳转:Ⅰ.使⽤专门的跳转指令。

Ⅱ.直接向程序计数器PC 写⼊跳转地址值。

通过向程序计数器PC 写⼊跳转地址值,可以实现在4GB 的地址空间中的任意跳转,在跳转之前结合使⽤ MOV LR,PC 等类似指令,可以保存将来的返回地址值,从⽽实现在4GB 连续的线性地址空间的⼦程序调⽤。

ARM指令集中的跳转指令可以完成从当前指令向前或向后的32MB的地址空间的跳转,包括以下4 条指令:1、 B 指令B 指令的格式为:B{条件} ⽬标地址B 指令是最简单的跳转指令。

⼀旦遇到⼀个 B 指令,ARM 处理器将⽴即跳转到给定的⽬标地址,从那⾥继续执⾏。

注意存储在跳转指令中的实际值是相对当前PC 值的⼀个偏移量,⽽不是⼀个绝对地址,它的值由汇编器来计算(参考寻址⽅式中的相对寻址)。

它是 24 位有符号数,左移两位后有符号扩展为 32 位,表⽰的有效偏移为 26 位(前后32MB 的地址空间)。

以下指令:B Label ;程序⽆条件跳转到标号Label 处执⾏CMP R1,#0 ;当CPSR 寄存器中的Z 条件码置位时,程序跳转到标号Label 处执⾏BEQ Label2、 BL 指令BL 指令的格式为:BL{条件} ⽬标地址BL 是另⼀个跳转指令,但跳转之前,会在寄存器R14 中保存PC 的当前内容,因此,可以通过将R14 的内容重新加载到PC 中,来返回到跳转指令之后的那个指令处执⾏。

该指令是实现⼦程序调⽤的⼀个基本但常⽤的⼿段。

以下指令:BL Label ;当程序⽆条件跳转到标号Label 处执⾏时,同时将当前的PC 值保存到R14 中3、 BLX 指令BLX 指令的格式为:BLX ⽬标地址BLX 指令从ARM 指令集跳转到指令中所指定的⽬标地址,并将处理器的⼯作状态有ARM 状态切换到Thumb 状态,该指令同时将PC 的当前内容保存到寄存器R14 中。

名字功能ADC带进位加法ADD加法AND 按位与(原文为逻辑与,有误——译注)。

这里的按位与和C 的”&” 功能相同ASR算术右移BIC 按位清0(把一个数跟另一个无符号数的反码按位与)CMN 负向比较(把一个数跟另一个数据的二进制补码相比较)CMP比较(比较两个数并且更新标志)CPY把一个寄存器的值拷贝到另一个寄存器中EOR近位异或LSL 逻辑左移(如无其它说明,所有移位操作都可以一次移动最多 31格——译注)LSR逻辑右移MOV 寄存器加载数据,既能用于寄存器间的传输,也能用于加载立即数MUL乘法MVN加载一个数的 NOT 值(取到逻辑反的值)NEG取二进制补码ORR按位或(原文为逻辑或,有误——译注)ROR圆圈右移SBC带借位的减法SUB减法TST 测试(执行按位与操作,并且根据结果更新 Z )REV在一个32位寄存器中反转字节序REVH 把一个32位寄存器分成两个 16位数,在每个 16位数中反转字节序REVSH 把一个32位寄存器的低 16位半字进行字节反转,然后带符号扩展到 32位SXTB带符号扩展一个字节到 32位SXTH带符号扩展一个半字到 32位UXTB无符号扩展一个字节到 32位UXTH无符号扩展一个半字到 32位16位转移指令B无条件转移B<cond>条件转移BL 转移并连接。

用于呼叫一个子程序,返回地址被存储在 LR 中BLX #im使用立即数的BLX不要在CM3 中使用CBZ 比较,如果结果为 0 就转移(只能跳到后面的指令——译注)CBNZ 比较,如果结果非 0 就转移(只能跳到后面的指令——译注)ARM CORTEX M3指令集16位数据操作指令IT If - Then16位存储器数据传送指令LDR从存储器中加载字到一个寄存器中LDRH从存储器中加载半字到一个寄存器中LDRB从存储器中加载字节到一个寄存器中LDRSH 从存储器中加载半字,再经过带符号扩展后存储一个寄存器中LDRSB 从存储器中加载字节,再经过带符号扩展后存储一个寄存器中STR把一个寄存器按字存储到存储器中STRH 把一个寄存器存器的低半字存储到存储器中STRB把一个寄存器的低字节存储到存储器中LDMIA 加载多个字,并且在加载后自增基址寄存器STMIA 存储多个字,并且在存储 后自增基址寄存器PUSH压入多个寄存器到栈中POP从栈中弹出多个值到寄存器中其它16位指令名字功能SVC系统服务调用BKPT 断点指令。

Cortex-M3 32位数据操作指令名字功能ADC 带进位加法ADD 加法ADDW 宽加法(可以加12 位立即数)AND 按位与(原文是逻辑与,有误——译注)ASR 算术右移BIC 位清零(把一个数按位取反后,与另一个数逻辑与)BFC 位段清零BFI 位段插入CMN 负向比较(把一个数和另一个数的二进制补码比较,并更新标志位)CMP 比较两个数并更新标志位CLZ 计算前导零的数目EOR 按位异或LSL 逻辑左移LSR 逻辑右移MLA 乘加MLS 乘减MOVW 把16 位立即数放到寄存器的底16 位,高16 位清0MOV 加载16 位立即数到寄存器(其实汇编器会产生MOVW——译注)MOVT 把16 位立即数放到寄存器的高16 位,低16 位不影响MVN 移动一个数的补码MUL 乘法ORR 按位或(原文为逻辑或,有误——译注)ORN 把源操作数按位取反后,再执行按位或(原文为逻辑或,有误——译注)RBIT 位反转(把一个32 位整数先用2 进制表达,再旋转180 度——译注)REV 对一个32 位整数做按字节反转REVH/REV16对一个32 位整数的高低半字都执行字节反转REVSH 对一个32 位整数的低半字执行字节反转,再带符号扩展成32 位数ROR 圆圈右移RRX 带进位的逻辑右移一格(最高位用C 填充,且不影响C 的值——译注)SFBX 从一个32 位整数中提取任意的位段,并且带符号扩展成32 位整数SDIV 带符号除法SMLAL 带符号长乘加(两个带符号的32 位整数相乘得到64 位的带符号积,再把积加到另一个带符号64 位整数中)SMULL 带符号长乘法(两个带符号的32 位整数相乘得到64 位的带符号积)SSAT 带符号的饱和运算SBC 带借位的减法SUB 减法SUBW 宽减法,可以减12 位立即数SXTB 字节带符号扩展到32 位数TEQ 测试是否相等(对两个数执行异或,更新标志但不存储结果)TST 测试(对两个数执行按位与,更新Z 标志但不存储结果)UBFX 无符号位段提取UDIV 无符号除法UMLAL 无符号长乘加(两个无符号的32 位整数相乘得到64 位的无符号积,再把积加到另一个无符号64 位整数中)UMULL 无符号长乘法(两个无符号的32 位整数相乘得到64 位的无符号积)USAT 无符号饱和操作(但是源操作数是带符号的——译注)UXTB 字节被无符号扩展到32 位(高24 位清0——译注)UXTH 半字被无符号扩展到32 位(高16 位清0——译注)。

名字功能

ADC带进位加法ADD加法

AND 按位与(原文为逻辑与,有误——译注)。

这里的按位与和C 的”&” 功能相同

ASR算术右移

BIC 按位清0(把一个数跟另一个无符号数的反码按位与)

CMN 负向比较(把一个数跟另一个数据的二进制补码相比较)

CMP比较(比较两个数并且更新标志)

CPY把一个寄存器的值拷贝到另一个寄存器中EOR近位异或

LSL 逻辑左移(如无其它说明,所有移位操作都可以一次移动最多 31格——译注)

LSR逻辑右移

MOV 寄存器加载数据,既能用于寄存器间的传输,也能用于加载立即数

MUL乘法

MVN加载一个数的 NOT 值(取到逻辑反的值)NEG取二进制补码

ORR按位或(原文为逻辑或,有误——译注)ROR圆圈右移

SBC带借位的减法

SUB减法

TST 测试(执行按位与操作,并且根据结果更新 Z )

REV在一个32位寄存器中反转字节序

REVH 把一个32位寄存器分成两个 16位数,在每个 16位数中反转字节序

REVSH 把一个32位寄存器的低 16位半字进行字节反转,然后带符号扩展到 32位

SXTB带符号扩展一个字节到 32位

SXTH带符号扩展一个半字到 32位

UXTB无符号扩展一个字节到 32位

UXTH无符号扩展一个半字到 32位16位转移指令B无条件转移

B<cond>条件转移

BL 转移并连接。

用于呼叫一个子程序,返回地址被存储在 LR 中

BLX #im使用立即数的BLX不要在CM3 中使用

CBZ 比较,如果结果为 0 就转移(只能跳到后面的指令——译注)

CBNZ 比较,如果结果非 0 就转移(只能跳到后面的指令——译注)

ARM CORTEX M3指令集16位数据操作

指令

IT If - Then

16位存储器数据传送

指令

LDR从存储器中加载字到一个寄存器中

LDRH从存储器中加载半字到一个寄存器中

LDRB从存储器中加载字节到一个寄存器中

LDRSH 从存储器中加载半字,再经过带符号扩展后存储一个寄存器中

LDRSB 从存储器中加载字节,再经过带符号扩展后存储一个寄存器中

STR把一个寄存器按字存储到存储器中

STRH 把一个寄存器存器的低半字存储到存储器中

STRB把一个寄存器的低字节存储到存储器中

LDMIA 加载多个字,并且在加载后自增基址寄存器

STMIA 存储多个字,并且在存储 后自增基址寄存器

PUSH压入多个寄存器到栈中

POP从栈中弹出多个值到寄存器中其它16位指令名字功能

SVC系统服务调用

BKPT 断点指令。

如果使能了调试,则进入调试状态(停机)。

否则的话产生调试监视器异常。

在调试监视器异常被使能时,调用其服务例程;如果连调试监视器异常也被除能,则无奈下只好诉诸于一个fault 异常。

NOP无操作

CPSIE 使能PRIMASK(CPSIE i)/ FAULTMASK(CPSIE f)——清0 相应的位

CPSID 除能PRIMASK(CPSID i)/

FAULTMASK(CPSID f) ——置位相应的位

32位数据操作指令ADC带进位加法

ADD加法

ADDW宽加法(可以加12位立即数)

AND 按位与(原文是逻辑与,有误。

对应C 言的“|”运算符——译注)

ASR算术右移

BIC 位清零(把一个数按位取反后,与另一个数逻辑与)

BFC位段清零BFI位段插入

CMN 负向比较(把一个数和另一个数的二进制补码比较,并更新标志位)

CMP比较两个数并更新标志位CLZ计算前导零的数目

EOR按位异或LSL逻辑左移LSR逻辑右移MLA乘加MLS乘减

MOVW 把16位立即数放到寄存器的低 16位,高16位清0

MOV 加载16位立即数到寄存器(其实汇编器会产生 MOVW ——译注)

MOVT 把16位立即数放到寄存器的高 16位,低16位不影响

MVN移动一个数的补码

MUL乘法

ORR按位或(原文为逻辑或,有误——译注)

ORN 把源操作数按位取反后,再执行按位或(原文为逻辑或,有误—— 译注)

RBIT 位反转(把一个 32位整数用2 进制表达后,再旋转 180 度——译注)

REV对一个32位整数按字节反转

REVH/REV16对一个32位整数的高低半字都执行字节反转

REVSH 对一个32位整数的低半字执行字节反转,再带符号扩展成 32位数

ROR圆圈右移

RRX 带进位位的逻辑右移一格 (最高位用 C 填充,执行后不影响 C 的值——译注)

SFBX 从一个32位整数中提取任意长度和位置的位段,并且带符号扩展成 32位整数

SDIV带符号除法

SMLAL 带符号长乘加(两个带符号的 32位整数相乘得到 64位的带符号积,再把积加到另一个带符号64位整数中)

SMULL 带符号长乘法(两个带符号的 32位整数相乘得到 64位的带符号积)

SSAT带符号的饱和运算

SBC带借位的减法

SUB减法

SUBW宽减法,可以减 12位立即数SXTB字节带符号扩展到 32位数

TEQ 测试是否相等(对两个数执行异或,更新标志但不存储结果)

TST 测试(对两个数执行按位与,更新 Z 标志但不存储结果)

UBFX无符号位段提取UDIV无符号除法

UMLAL 无符号长乘加(两个无符号的 32位整数相乘得到 64位的无符号积,再把积加到另一个无符号64位整数中)

UMULL 无符号长乘法(两个无符号的 32位整数相乘得到 64位的无符号积)

USAT 无符号饱和操作(但是源操作数是带符号的——译注)

UXTB 字节被无符号扩展到 32位(高24位清0——译注)

UXTH 半字被无符号扩展到 32位(高16位清0——译注)

32位存储器数据传送

指令

名字功能

LDR加载字到寄存器

LDRB加载字节到寄存器

LDRH加载半字到寄存器

LDRSH加载半字到寄存器,再带符号扩展到 32位

LDM 从一片连续的地址空间中加载若干个字,并选中相同数目的寄存器放进去

LDRD 从连续的地址空间加载双字(64位整数)到 2 个寄存器

STR存储寄存器中的字STRB存储寄存器中的低字节STRH存储寄存器中的低半字

STM 存储若干寄存器中的字到一片连续的地址空间中,占用相同数目的字

STRD 存储2 个寄存器组成的双字到连续的地址空间中

PUSH把若干寄存器的值压入堆栈中

POP从堆栈中弹出若干的寄存器的值32位转移指令名字功能

B无条件转移

BL转移并连接(呼叫子程序)

TBB 以字节为单位的查表转移。

从一个字节数组中选一个 8 位前向跳转地址并转移

TBH 以半字为单位的查表转移。

从一个半字数组中选一个 16位前向跳转的地址并转移

其它32位指令LDREX 加载字到寄存器,并且在内核中标明一段地址进入了互斥访问状态

LDREXH 加载半字到寄存器,并且在内核中标明一段地址进入了互斥访问状态

LDREXB 加载字节到寄存器,并且在内核中标明一段地址进入了互斥访问状态

STREX 检查将要写入的地址是否已进入了互斥访问状态,如果是则存储寄存器的字

STREXH 检查将要写入的地址是否已进入了互斥访问状态,如果是则存储寄存器的半字

STREXB 检查将要写入的地址是否已进入了互斥访问状态,如果是则存储寄存器的字节

CLREX 在本地处理器上清除互斥访问状态的标记(先前由 LDREX/LDREXH/LDREXB 做的标记)

MRS加载特殊功能寄存器的值到通用寄存器MSR存储通用寄存器的值到特殊功能寄存器NOP无操作

SEV发送事件

WFE休眠并且在发生事件时被唤醒

WFI休眠并且在发生中断时被唤醒

ISB 指令同步隔离(与流水线和 MPU 等有关——译注)

DSB 数据同步隔离(与流水线、MPU 和cache 等有关——译注)

DMB 数据存储隔离(与流水线、MPU 和cache 等有关——译注)。