实验四八位七段数码管动态显示电路的设计

- 格式:docx

- 大小:14.01 KB

- 文档页数:4

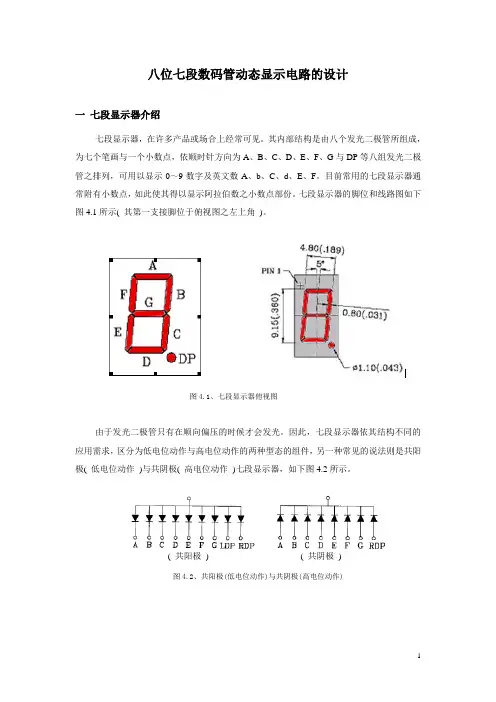

八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。

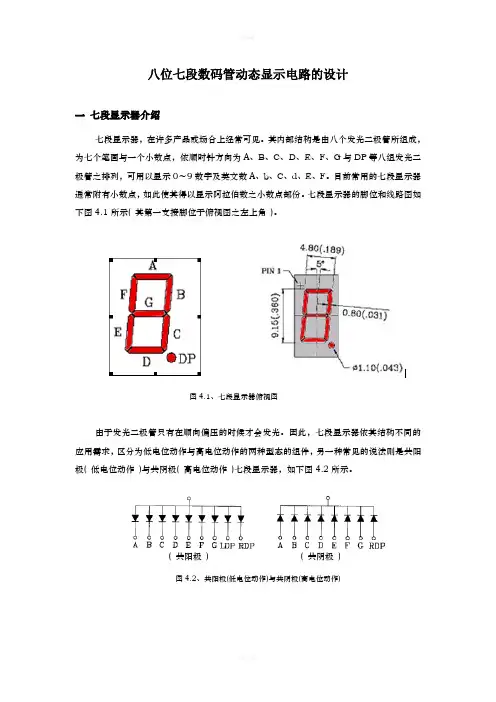

其内部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。

目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。

七段显示器的脚位和线路图如下图4.1所示( 其第一支接脚位于俯视图之左上角)。

图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时候才会发光。

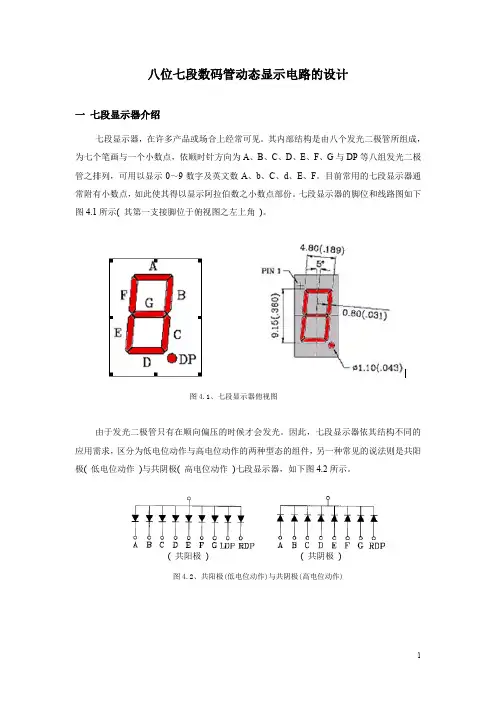

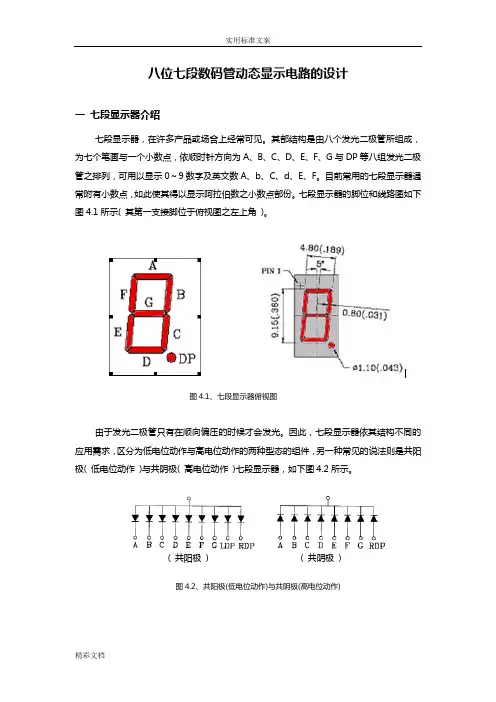

因此,七段显示器依其结构不同的应用需求,区分为低电位动作与高电位动作的两种型态的组件,另一种常见的说法则是共阳极( 低电位动作)与共阴极( 高电位动作)七段显示器,如下图4.2所示。

( 共阳极) ( 共阴极)图4.2、共阳极(低电位动作)与共阴极(高电位动作)要如何使七段显示器发光呢?对于共阴极规格的七段显示器来说,必须使用“ Sink Current ”方式,亦即是共同接脚COM为VCC,并由Cyclone II FPGA使接脚成为高电位,进而使外部电源将流经七段显示器,再流入Cyclone II FPGA的一种方式本实验平台之七段显示器模块接线图如下图4.5所示。

此平台配置了八组共阳极之七段显示器,亦即是每一组七段显示器之COM接脚,均接连至VCC电源。

而每一段发光二极管,其脚位亦均与Cyclone II FPGA接连。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

图4.5、七段显示器模块接线图七段显示器之常见应用如下➢可作为与数值显示相关之设计。

⏹电子时钟应用显示⏹倒数定时器⏹秒表⏹计数器、定时器⏹算数运算之数值显示器二七段显示器显示原理七段显示器可用来显示单一的十进制或十六进制的数字,它是由八个发光二极管所构成的( 每一个二极管依位置不同而赋予不同的名称,请参见图4.1 ) 。

八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。

其内部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。

目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。

七段显示器的脚位和线路图如下图4.1所示( 其第一支接脚位于俯视图之左上角)。

图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时候才会发光。

因此,七段显示器依其结构不同的应用需求,区分为低电位动作与高电位动作的两种型态的组件,另一种常见的说法则是共阳极( 低电位动作)与共阴极( 高电位动作)七段显示器,如下图4.2所示。

( 共阳极) ( 共阴极)图4.2、共阳极(低电位动作)与共阴极(高电位动作)要如何使七段显示器发光呢?对于共阴极规格的七段显示器来说,必须使用“ Sink Current ”方式,亦即是共同接脚COM为VCC,并由Cyclone II FPGA使接脚成为高电位,进而使外部电源将流经七段显示器,再流入Cyclone II FPGA的一种方式本实验平台之七段显示器模块接线图如下图4.5所示。

此平台配置了八组共阳极之七段显示器,亦即是每一组七段显示器之COM接脚,均接连至VCC电源。

而每一段发光二极管,其脚位亦均与Cyclone II FPGA接连。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

图4.5、七段显示器模块接线图七段显示器之常见应用如下可作为与数值显示相关之设计。

⏹电子时钟应用显示⏹倒数定时器⏹秒表⏹计数器、定时器⏹算数运算之数值显示器二七段显示器显示原理七段显示器可用来显示单一的十进制或十六进制的数字,它是由八个发光二极管所构成的( 每一个二极管依位置不同而赋予不同的名称,请参见图4.1 ) 。

八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。

其部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。

目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。

七段显示器的脚位和线路图如下图4.1所示( 其第一支接脚位于俯视图之左上角)。

图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时候才会发光。

因此,七段显示器依其结构不同的应用需求,区分为低电位动作与高电位动作的两种型态的组件,另一种常见的说法则是共阳极( 低电位动作)与共阴极( 高电位动作)七段显示器,如下图4.2所示。

( 共阳极) ( 共阴极)图4.2、共阳极(低电位动作)与共阴极(高电位动作)要如何使七段显示器发光呢?对于共阴极规格的七段显示器来说,必须使用“Sink Current ”方式,亦即是共同接脚COM为VCC,并由Cyclone II FPGA使接脚成为高电位,进而使外部电源将流经七段显示器,再流入Cyclone II FPGA的一种方式本实验平台之七段显示器模块接线图如下图4.5所示。

此平台配置了八组共阳极之七段显示器,亦即是每一组七段显示器之COM接脚,均接连至VCC电源。

而每一段发光二极管,其脚位亦均与Cyclone II FPGA接连。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

图4.5、七段显示器模块接线图七段显示器之常见应用如下➢可作为与数值显示相关之设计。

⏹电子时钟应用显示⏹倒数定时器⏹秒表⏹计数器、定时器⏹算数运算之数值显示器二七段显示器显示原理七段显示器可用来显示单一的十进制或十六进制的数字,它是由八个发光二极管所构成的( 每一个二极管依位置不同而赋予不同的名称,请参见图4.1 ) 。

实验七七段LED数码管显示电路设计一、实验目的1.学习EDA软件的基本操作2.学习使用原理图进行设计输入3.初步掌握软件输入、编译、仿真和编程的过程4.学习实验开发系统的使用方法二、实验说明本实验通过七段LED数码管显示电路的设计,初步掌握EDA 设计方法中的设计输入、编译、综合、仿真和编程的基本过程。

七段LED数码管显示电路有四个数据输入端(D0-D3),七个数据输出端(A-G。

三、实验要求1、完成七段LED数码管显示电路的原理图输入并进行编译2、对设计的电路经行仿真验证3、编程下载并在实验开发系统上验证设计结果四、实验步骤1、新建工程2、新建Verilog HDL文件3、在文本输入窗口键入代码4、保存HDL文件5、编译文件直至没有错误6、新建波形文件7、添加观察信号8、添加输入激励,保存波形文件9、功能仿真七段LED数码管显示电路真值表:输入D3D2D1D0G F E D C B A 000000111111 100010000110 200101011011 300111001111 401001100110 501011101101 601101111101 701110001111 810001111111910011101111 A10101110111 B10111111100 C11001111001 D110111011110 E11101111001 F11111110001五、电路原理图啊Verilog代码描述:module qiduan(data_in,data_out;input [3:0]data_in;output [6:0]data_out;reg [6:0]data_out;always @(data_inbegincasex(data_in4'b0000:data_out<=7'b0111111;4'b0001:data_out<=7'b0000110; 4'b0010:data_out<=7'b1011011; 4'b0011:data_out<=7'b1001111; 4'b0100:data_out<=7'b1100110; 4'b0101:data_out<=7'b1101101; 4'b0110:data_out<=7'b1111100; 4'b0111:data_out<=7'b0000111; 4'b1000:data_out<=7'b1111111; 4'b1001:data_out<=7'b1100111; 4'b1010:data_out<=7'b1110111; 4'b1011:data_out<=7'b1111100; 4'b1100:data_out<=7'b0111001; 4'b1101:data_out<=7'b1011110; 4'b1110:data_out<=7'b1111001; 4'b1111:data_out<=7'b1110001; default:data_out<=7'b0000000; endcaseendendmodule仿真波形:六、实验体会七段LED数码管显示电路是常用的数码管之一,它有四个数据输入端(D0-D3),七个数据输出端(A-G。

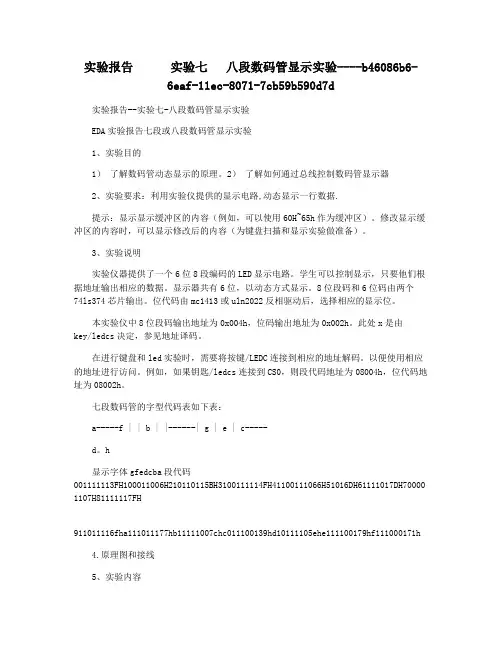

实验报告实验七八段数码管显示实验----b46086b6-6eaf-11ec-8071-7cb59b590d7d实验报告--实验七-八段数码管显示实验EDA实验报告七段或八段数码管显示实验1、实验目的1)了解数码管动态显示的原理。

2)了解如何通过总线控制数码管显示器2、实验要求:利用实验仪提供的显示电路,动态显示一行数据.提示:显示显示缓冲区的内容(例如,可以使用60H~65h作为缓冲区)。

修改显示缓冲区的内容时,可以显示修改后的内容(为键盘扫描和显示实验做准备)。

3、实验说明实验仪器提供了一个6位8段编码的LED显示电路。

学生可以控制显示,只要他们根据地址输出相应的数据。

显示器共有6位,以动态方式显示。

8位段码和6位码由两个74ls374芯片输出。

位代码由mc1413或uln2022反相驱动后,选择相应的显示位。

本实验仪中8位段码输出地址为0x004h,位码输出地址为0x002h。

此处x是由key/ledcs决定,参见地址译码。

在进行键盘和led实验时,需要将按键/LEDC连接到相应的地址解码。

以便使用相应的地址进行访问。

例如,如果钥匙/ledcs连接到CS0,则段代码地址为08004h,位代码地址为08002h。

七段数码管的字型代码表如下表:a-----f | | b | |------| g | e | c-----d。

h显示字体gfedcba段代码001111113FH100011006H210110115BH3100111114FH41100111066H51016DH61111017DH70000 1107H81111117FH911011116fha111011177hb11111007chc011100139hd10111105ehe111100179hf111000171h4.原理图和接线5、实验内容1)使用仪器和仪表开发平台模型本实验用到了wave6000软件平台,电脑一台,lab6000实验箱,示波器,若干连线,串行数据线。

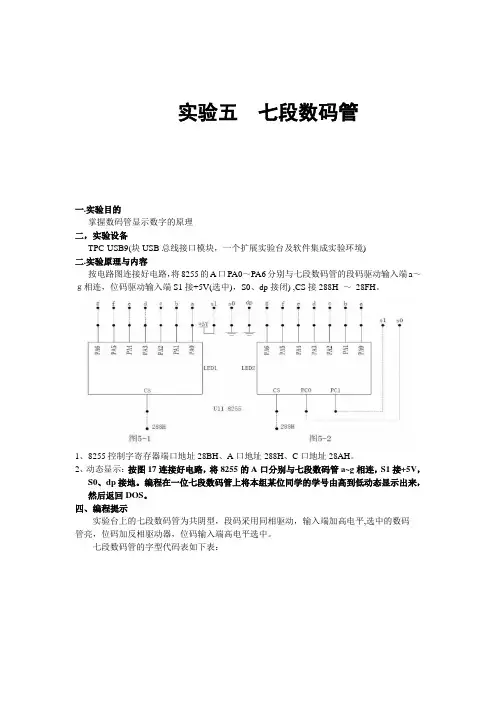

实验五七段数码管一.实验目的掌握数码管显示数字的原理二,实验设备TPC-USB9(块USB总线接口模块,一个扩展实验台及软件集成实验环境)二.实验原理与内容按电路图连接好电路,将8255的A口PA0~PA6分别与七段数码管的段码驱动输入端a~g相连,位码驱动输入端S1接+5V(选中),S0、dp接闭) ,CS接288H ~28FH。

1、8255控制字寄存器端口地址28BH、A口地址288H、C口地址28AH。

2、动态显示:按图17连接好电路,将8255的A口分别与七段数码管a~g相连,S1接+5V,S0、dp接地。

编程在一位七段数码管上将本组某位同学的学号由高到低动态显示出来,然后返回DOS。

四、编程提示实验台上的七段数码管为共阴型,段码采用同相驱动,输入端加高电平,选中的数码管亮,位码加反相驱动器,位码输入端高电平选中。

七段数码管的字型代码表如下表:五、程序流程图六、汇编程序stack segment stack ‘stack’dw 32 dup(0)stack endsdata segmentbegin proc farassume cs:code,ds:data,ss:stackpush dssub ax,axpush axmov ax,datamov ds,ax;/**************************************************************/ MOV DX,28BH ;设置8255为端口A的工作方式0 MOV AL,00HOUT DX,ALMOV DX,288H ;设置端口A的地址MOV AL,06H ;显示数字1OUT DX,ALCALL DELAYMOV AL,06H ;显示数字1OUT DX,ALCALL DELAYMOV AL,3FH ;显示数字0OUT DX,ALCALL DELAYMOV AL,07H ;显示数字7OUT DX,ALCALL DELAYMOV AL,3FH ;显示数字0OUT DX,ALCALL DELAYMOV AL,4FH ;显示数字3OUT DX,ALCALL DELAYMOV AL,06H ;显示数字1OUT DX,ALCALL DELAYMOV AL,4FH ;显示数字3OUT DX,ALCALL DELAYMOV AL,06H ;显示数字1OUT DX,ALCALL DELAYMOV AH,4CH ;返回DOSINT 21HRETBEGIN ENDPDELAY PROC ;设置延时程序PUSH AXPUSH BXPUSH CXPUSH DXMOV BX,20000L1:MOV CX,1000L2:LOOP L2DEC DXJNZ L1POP DXPOP CXPOP BXPOP AXRETDELAY ENDPCODE ENDSEND BEGIN六、心得体会:通过本次试验,让我熟悉了用EDIT进行汇编程序编写的操作,也加强了在DOS上编译、连接、运行汇编程序的步骤。

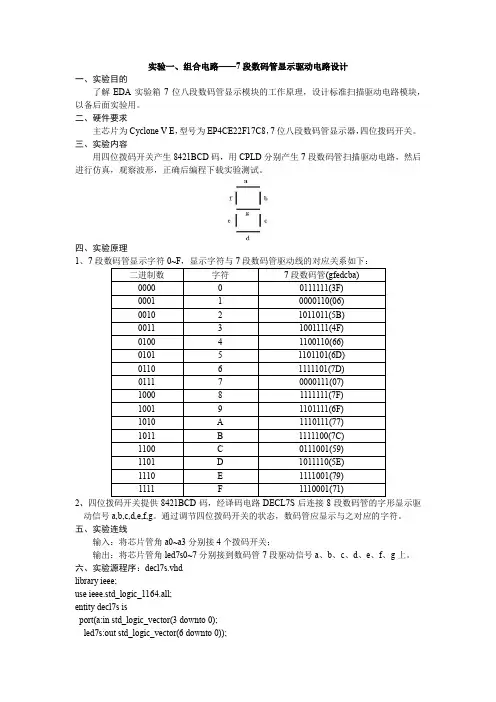

实验一、组合电路——7段数码管显示驱动电路设计一、实验目的了解EDA实验箱7位八段数码管显示模块的工作原理,设计标准扫描驱动电路模块,以备后面实验用。

二、硬件要求主芯片为Cyclone V E,型号为EP4CE22F17C8,7位八段数码管显示器,四位拨码开关。

三、实验内容用四位拨码开关产生8421BCD码,用CPLD分别产生7段数码管扫描驱动电路,然后进行仿真,观察波形,正确后编程下载实验测试。

四、实验原理1、72、动信号a,b,c,d,e,f,g。

通过调节四位拨码开关的状态,数码管应显示与之对应的字符。

五、实验连线输入:将芯片管角a0~a3分别接4个拨码开关;输出:将芯片管角led7s0~7分别接到数码管7段驱动信号a、b、c、d、e、f、g上。

六、实验源程序:decl7s.vhdlibrary ieee;use ieee.std_logic_1164.all;entity decl7s isport(a:in std_logic_vector(3 downto 0);led7s:out std_logic_vector(6 downto 0));end;architecture one of decl7s isbeginprocess(a)begincase a iswhen "0000" => led7s<="0111111"; when "0001" => led7s<="0000110"; when "0010" => led7s<="1011011"; when "0011" => led7s<="1001111"; when "0100" => led7s<="1100110"; when "0101" => led7s<="1101101"; when "0110" => led7s<="1111101"; when "0111" => led7s<="0000111"; when "1000" => led7s<="1111111"; when "1001" => led7s<="1101111"; when "1010" => led7s<="1110111"; when "1011" => led7s<="1111100"; when "1100" => led7s<="0111001"; when "1101" => led7s<="1011110"; when "1110" => led7s<="1111001"; when "1111" => led7s<="1110001"; when others => null;end case;end process;end;七、波形仿真结果。

八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。

其内部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。

目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。

七段显示器的脚位和线路图如下图4.1所示( 其第一支接脚位于俯视图之左上角)。

图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时候才会发光。

因此,七段显示器依其结构不同的应用需求,区分为低电位动作与高电位动作的两种型态的组件,另一种常见的说法则是共阳极( 低电位动作)与共阴极( 高电位动作)七段显示器,如下图4.2所示。

( 共阳极) ( 共阴极)图4.2、共阳极(低电位动作)与共阴极(高电位动作)要如何使七段显示器发光呢?对于共阴极规格的七段显示器来说,必须使用“ Sink Current ”方式,亦即是共同接脚COM为VCC,并由Cyclone II FPGA使接脚成为高电位,进而使外部电源将流经七段显示器,再流入Cyclone II FPGA的一种方式本实验平台之七段显示器模块接线图如下图4.5所示。

此平台配置了八组共阳极之七段显示器,亦即是每一组七段显示器之COM接脚,均接连至VCC电源。

而每一段发光二极管,其脚位亦均与Cyclone II FPGA接连。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

图4.5、七段显示器模块接线图七段显示器之常见应用如下可作为与数值显示相关之设计。

⏹电子时钟应用显示⏹倒数定时器⏹秒表⏹计数器、定时器⏹算数运算之数值显示器二七段显示器显示原理七段显示器可用来显示单一的十进制或十六进制的数字,它是由八个发光二极管所构成的( 每一个二极管依位置不同而赋予不同的名称,请参见图4.1 ) 。

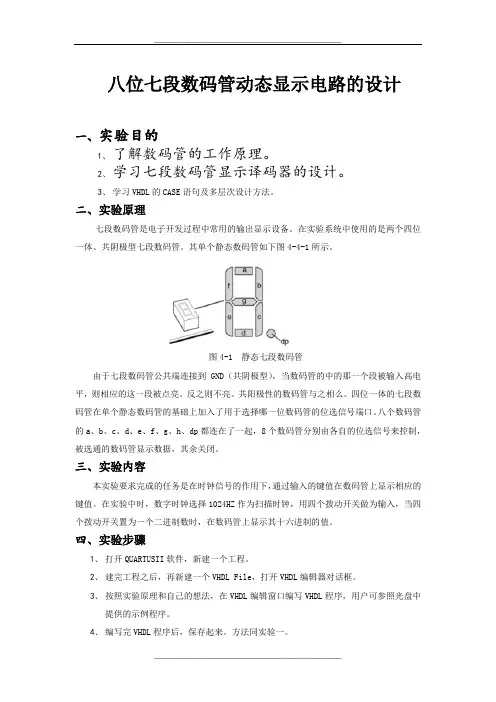

八位七段数码管动态显示电路的设计一、实验目的1、了解数码管的工作原理。

2、学习七段数码管显示译码器的设计。

3、学习VHDL的CASE语句及多层次设计方法。

二、实验原理七段数码管是电子开发过程中常用的输出显示设备。

在实验系统中使用的是两个四位一体、共阴极型七段数码管。

其单个静态数码管如下图4-4-1所示。

图4-1 静态七段数码管由于七段数码管公共端连接到GND(共阴极型),当数码管的中的那一个段被输入高电平,则相应的这一段被点亮。

反之则不亮。

共阳极性的数码管与之相么。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

三、实验内容本实验要求完成的任务是在时钟信号的作用下,通过输入的键值在数码管上显示相应的键值。

在实验中时,数字时钟选择1024HZ作为扫描时钟,用四个拨动开关做为输入,当四个拨动开关置为一个二进制数时,在数码管上显示其十六进制的值。

四、实验步骤1、打开QUARTUSII软件,新建一个工程。

2、建完工程之后,再新建一个VHDL File,打开VHDL编辑器对话框。

3、按照实验原理和自己的想法,在VHDL编辑窗口编写VHDL程序,用户可参照光盘中提供的示例程序。

4、编写完VHDL程序后,保存起来。

方法同实验一。

5、对自己编写的VHDL程序进行编译并仿真,对程序的错误进行修改。

6、编译仿真无误后,根据用户自己的要求进行管脚分配。

分配完成后,再进行全编译一次,以使管脚分配生效。

7、根据实验内容用实验导线将上面管脚分配的FPGA管脚与对应的模块连接起来。

如果是调用的本书提供的VHDL代码,则实验连线如下:CLK:FPGA时钟信号,接数字时钟CLOCK3,并将这组时钟设为1024HZ。

KEY[3..0]:数码管显示输入信号,分别接拨动开关的S4,S3,S2,S1。

电子课程设计—8位数码管动态显示电路设计学院:电子信息工程学院专业、班级:姓名:学号:指导老师:2014年12月目录一、设计任务与要求................................................. (3)二、总体框图................................................. (3)三、选择器件................................................. (3)四、功能模块................................................. (9)五、总体设计电路图................................................. . (10)六、心得体会.................................................. .. (12)8位数码管动态显示电路设计一、设计任务与要求1. 设计个8位数码管动态显示电路,动态显示1、2、3、4、5、6、7、8。

2. 要求在某一时刻,仅有一个LED数码管发光。

3. 该数码管发光一段时间后,下一个LED发光,这样8只数码管循环发光。

4. 当循环扫描速度足够快时,由于视觉暂留的原因,就会感觉8只数码管是在持续发光。

5、研究循环地址码发生器的时钟频率和显示闪烁的关系。

二、总体框图设计的总体框图如图2-1所示。

图2-1总体框图三、选择器件1、数码管数码管是一种由发光二极管组成的断码型显示器件,如图1所示。

U13DCD_HEX图1 数码管数码管里有八个小LED发光二极管,通过控制不同的LED的亮灭来显示出不同的字形。

数码管又分为共阴极和共阳极两种类型,其实共阴极就是将八个LED 的阴极连在一起,让其接地,这样给任何一个LED的另一端高电平,它便能点亮。

而共阳极就是将八个LED的阳极连在一起。

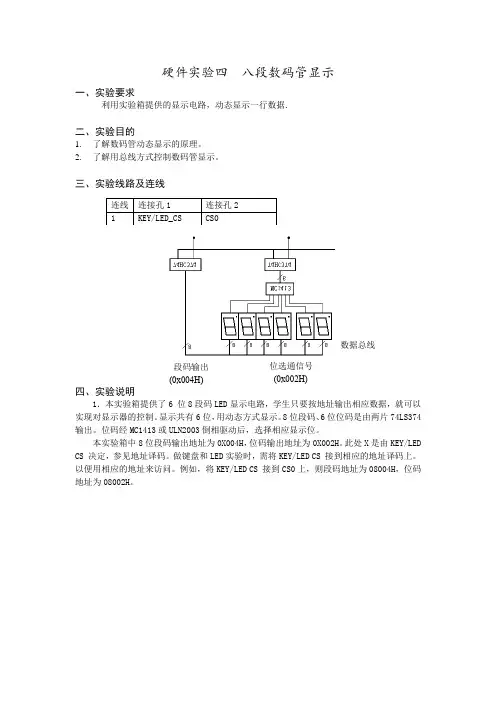

硬件实验四 八段数码管显示一、实验要求利用实验箱提供的显示电路,动态显示一行数据.二、实验目的1. 了解数码管动态显示的原理。

2. 了解用总线方式控制数码管显示。

三、实验线路及连线四、实验说明1.本实验箱提供了6 位8段码LED 显示电路,学生只要按地址输出相应数据,就可以实现对显示器的控制。

显示共有6位,用动态方式显示。

8位段码、6位位码是由两片74LS374输出。

位码经MC1413或ULN2003倒相驱动后,选择相应显示位。

本实验箱中8位段码输出地址为0X004H ,位码输出地址为0X002H 。

此处X 是由KEY/LED CS 决定,参见地址译码。

做键盘和LED 实验时,需将KEY/LED CS 接到相应的地址译码上。

以便用相应的地址来访问。

例如,将KEY/LED CS 接到CS0上,则段码地址为08004H ,位码地址为08002H 。

连线 连接孔1连接孔2 1KEY/LED_CS CS0 位选通信号 (0x002H) 段码输出(0x004H) 数据总线七段数码管的字型代码表如下表:五、程序参考程序、框图OUTBIT equ 08002h ; 位控制口OUTSEG equ 08004h ; 段控制口data segmentLEDBuf db 6 dup(?) ; 显示缓冲Num db 1 dup(?) ; 显示的数据DelayT db 1 dup(?)LEDMAP: ; 八段管显示码db 3fh, 06h, 5bh, 4fh, 66h, 6dh, 7dh, 07h db 7fh, 6fh, 77h, 7ch, 39h, 5eh, 79h, 71h data endscode segmentassume cs:code, ds:dataDelay proc nearpush ax ; 延时子程序push cxmov al, 0mov cx,axloop $pop cxpop axretDelay endpDisplayLED proc nearmov bx, offset LEDBufmov cl, 6 ; 共6个八段管mov ah, 00100000b ; 从左边开始显示DLoop:mov dx, OUTBITmov al, 0out dx,al ; 关所有八段管mov al, [bx]mov dx, OUTSEGout dx,almov dx, OUTBITmov al, ahout dx, al ; 显示一位八段管push axmov ah, 1call Delaypop axshr ah, 1inc bxdec cljnz DLoopmov dx, OUTBITmov al, 0out dx,al ; 关所有八段管retDisplayLED endpStart proc nearmov ax, datamov ds, axmov Num, 0MLoop:inc Nummov ch,Nummov ah,0mov cl,6mov bx,offset LEDBufFillBuf:mov si, offset LEDMapmov al,chand al,0fhadd ax,simov si,axmov al,[si] ; 数据转换成显示码 mov [bx], al ; 显示码存入显示缓冲 inc bxinc chdec cljnz FillBufmov DelayT,20DispAgain:call DisplayLED ; 显示dec DelayTjnz DispAgainjmp MLoopStart endpcode endsend start六、实验步骤(1) 在实验箱断电的情况下连好线。

实验四七段数码管显示实验一、实验目的掌握数码管显示数字的原理。

二、实验内容1.静态显示:数码管为共阴极,通过BCD码译码驱动器CD4511驱动,其输入端A~D输入4位BCD码,位码输入低电平选中。

按图4-1连接好电路,将8255的A口PA0~PA3与七段数码管LED1的BCD码驱动输入端A1~D1相连,8255的A口PA4~PA7与七段数码管LED2的BCD码驱动输入端A2~D2相连,8255的B口PB0~PB3与七段数码管LED3的BCD码驱动输入端A3~D3相连,8255的B口PB4~PB7与七段数码管LED4的BCD码驱动输入端A4~D4相连,8255的C口PC0~PC3分别与七段数码管LED4~LED4的位驱动输入端DG1~DG4相连。

编程从键盘上每输入4个0~9数字,在七段数码管LED4~LED4上依次显示出来。

图4-12.动态显示:数码管为共阴极,段码采用相同驱动,输入端加高电平,选中的数码管对应段点亮,位码采用同相驱动,位码输入端低电平选中,按图4-2连接好电路,图中只画了2个数码管,实际是8个数码管,将8255的A口PA0~PA7分别与七段数码管的段码驱动输入端a~g相连(32TCI0模块上的J1连32LED8模块J2),8255的C口的PC0~PC7接七段数码管的段码驱动输入(32TCI0模块上的J3连32LED8模块J1),跳线器K1连2和3。

编程在8个数码管上显示“12345678”。

按任意键推出运行。

图4-2三、编程提示1.由于DVCC卡使用PCI总线,所以分配的IO地址每台微机可能都不用,编程时需要了解当前的微机使用那段IO地址并进行处理。

2.对实验内容1,七段数码管字型代码与输入的关系如下表:四、参考流程图1.实验内容一的参考流程图图4-3 2.实验内容二的参考流程图图4-4五、参考程序1.内容一的参考程序源程序清单如下:data segmentioport equ 0c400h-0280hio8255a equ ioport+288hio8255b equ ioport+289hio8255c equ ioport+28ahio8255k equ ioport+28bhled db 3fh,06h,5bh,4fh,66h,6dh,7dh,07h,7fh,6fhmesg1 db 0dh,0ah,'Input a num (0--9),other key is exit:',0dh,0ah,'$'bz db ?cz db 04hdata endscode segmentassume cs:code,ds:datastart: mov ax,datamov ds,axmov dx,io8255k ;使8255的A口为输出方式mov ax,80hout dx,alsss0: mov si,offset bzmov cx,04hsss1: mov dx,offset mesg1 ;显示提示信息mov ah,09hint 21hmov ah,01 ;从键盘接收字符int 21hcmp al,'0' ;是否小于0jl exit ;若是则退出cmp al,'9' ;是否大于9jg exit ;若是则退出sub al,30h ;将所得字符的ASCII码减30Hmov [si],al ;存入显示缓冲区inc si ;显示缓冲区指针加1dec cx ;判断输入满4个数字吗?jnz sss1 ;不满继续mov si,offset bz ;从显示缓冲区取第一个数字的BCD 码mov al,[si]and al,0fh ;屏蔽高四位暂存ALinc si ;显示缓冲区指针加1mov ah,[si] ;取第二个数字的BCD码到AHsal ah,4h ;右移4次到高四位add al,ah ;两个BCD码合并成一个字节mov bl,al ;暂存入BLinc simov al,[si] ;取第三个数字的BCD码and al,0fhinc simov ah,[si] ;取第四个数字的BCD码到AHsal ah,4hadd ah,almov al,ahmov dx,io8255a ;从8255的A口输出(后两个数字)out dx,almov al,blmov dx,io8255b ;从8255的B口输出(前两个数字)out dx,almov al,0f0hmov dx,io8255c ;从8255的C口输出位码out dx,almov dl,0ffhmov ah,06int 21hje sss0 ;有键按下则退出exit: mov ah,4ch ;返回int 21hcode endsend start2.内容二的参考程序源程序清单如下:data segmentioport equ 0C400h-0280hio8255c equ ioport+28ahio8255k equ ioport+28bhio8255a equ ioport+288hled db 3fh,06h,5bh,4fh,66h,6dh,7dh,07h,7fh,6fh ;段码buffer1 db 01h,02h,03h,04h,05h,06h,07h,08h ;存放要显示的十位和个位con db ? ;位码data endscode segmentassume cs:code, ds:datastart: mov ax,datamov ds,axmov dx,io8255k ;将8255设为A口C口输出mov al,80hout dx,alloop2: mov al,08h ;设置数码管位计数器初值到CON mov byte ptr con,almov si,offset buffer1 ;置显示缓冲器指针SImov ah,7fh ;置位码初值disp0: mov cx,0ffffhmov bl,ds:[si] ;取显示缓冲区显示值存BXmov bh,0hpush simov dx,io8255c ;位码从C口输出mov al,ahout dx,almov dx,io8255amov si,offset led ;置led数码表偏移地址为SIadd si,bx ;求出对应的led数码mov al,byte ptr [si]out dx,al ;段码从A口输出disp1: loop disp1 ;延时mov cx,0ffffhdisp2: loop disp2ror ah,01h ;位码右移1位pop siinc si ;显示缓冲区指针加1mov al,byte ptr condec almov byte ptr con,aljnz disp0 ;数码管位计数器减1为0吗?,不为0继续mov dx,io8255a ;为0,关数码管显示mov al,0out dx,almov dl,0ffhmov ah,06int 21hje loop2 ;有键按下则退出mov ah,4ch ;返回int 21hcode endsend start实验总结:通过这次试验,我了解到自定义数据类型可以根据自己的需要方便设定,有很大的灵活性。

七段数码管的动态显示1、实验内容:数码管的动态显示利用实验板上的某四位数码管依次显示16 进制的0000~FFFF。

为实现功能重用的目的,我们仍然将系统划分为几个部分:(1)时钟分频模块:将开发板上的50MHz 高速时钟进行分频产生一个5Hz 的时钟用于计数。

(2)计数模块:实现从0000~FFFF 的计数功能。

用4位十六进制数来实现,其中15‐12 位表示十六进制数的最高位,11‐8 位表示次高位,7‐4 位表示次低位,3‐0位表示最低位(3)数码管动态显示模块:将计数模块的输出作为显示字符的输入值,分时送出相应段码,实现数码管的动态显示效果。

2、参考程序:module SegDynamicDisp(CLK,rst_n,SEG0,SEG1,SEG2,SEG3);//数码管动态显示模块? input CLK;input rst_n;output [7:0]SEG0;//定义输出数码管0的段码带output [7:0]SEG1;//定义输出数码管1的段码带output [7:0]SEG2;//定义输出数码管2的段码带output [7:0]SEG3;//定义输出数码管3的段码带//..............................................................reg [7:0]SEG0;//定义输出数码管0的段码带reg [7:0]SEG1;//定义输出数码管1的段码带reg [7:0]SEG2;//定义输出数码管2的段码带reg [7:0]SEG3;//定义输出数码管3的段码带//..................................................................parameter seg0=8'hC0,seg1=8'hF9,seg2=8'hA4,seg3=8'hB0,seg4=8'h99,seg5=8'h92,seg6=8'h82,seg7=8'hF8,seg8=8'h80,seg9=8'h90,sega=8'h88,segb=8'h83,segc=8'hC6,segd=8'hA1,sege=8'h86,segf=8'h8E;//....................................................................reg[23:0] cnt;//定义计数寄存器,用来实现定时的功能reg [15:0]counter;//定义计数寄存器,用于实现显示的数值always @(posedge CLK or negedge rst_n)//计数过程,记录当前显示的位选序号if(!rst_n)begincnt<=24'D0;//复位时cnt初始化为0counter<=2'b00;//复位时counter初始化为0endelsebegincnt<=cnt+1'b1;//实现计数的功能if(cnt==24'D1*******)begincnt<=0;//当达到计数值以后回复初始值counter<=counter+1;//当达到计时时间以后显示的数值也相应的+1endend//....................................................always @(posedge CLK or negedge rst_n)if(!rst_n)beginSEG0<=0;SEG1<=0;SEG2<=0;SEG3<=0;endelsealways @(counter)begincase(counter[3:0])4'h0: sm_dbr <= seg0;4'h1: sm_dbr <= seg1;4'h2: sm_dbr <= seg2;4'h4: sm_dbr <= seg4;4'h5: sm_dbr <= seg5;4'h6: sm_dbr <= seg6;4'h7: sm_dbr <= seg7;4'h8: sm_dbr <= seg8;4'h9: sm_dbr <= seg9; 4'ha: sm_dbr <= sega;4'hb: sm_dbr <= segb;4'hc: sm_dbr <= segc;4'hd: sm_dbr <= segd;4'he: sm_dbr <= sege;4'hf: sm_dbr <= segf;default: ;endcasecase(counter[7:4])4'h0: sm_dbr <= seg0;4'h1: sm_dbr <= seg1;4'h2: sm_dbr <= seg2;4'h3: sm_dbr <= seg3;4'h4: sm_dbr <= seg4;4'h5: sm_dbr <= seg5;4'h6: sm_dbr <= seg6;4'h7: sm_dbr <= seg7;4'h8: sm_dbr <= seg8;4'h9: sm_dbr <= seg9;4'ha: sm_dbr <= sega;4'hb: sm_dbr <= segb;4'hc: sm_dbr <= segc;4'hd: sm_dbr <= segd;4'he: sm_dbr <= sege;4'hf: sm_dbr <= segf;default: ;endcasecase(counter[11:8])4'h0: sm_dbr <= seg0;4'h1: sm_dbr <= seg1;4'h2: sm_dbr <= seg2;4'h3: sm_dbr <= seg3;4'h4: sm_dbr <= seg4;4'h6: sm_dbr <= seg6; 4'h7: sm_dbr <= seg7; 4'h8: sm_dbr <= seg8; 4'h9: sm_dbr <= seg9; 4'ha: sm_dbr <= sega; 4'hb: sm_dbr <= segb; 4'hc: sm_dbr <= segc; 4'hd: sm_dbr <= segd; 4'he: sm_dbr <= sege; 4'hf: sm_dbr <= segf; default: ;endcasecase(counter[15:12])4'h0: sm_dbr <= seg0; 4'h1: sm_dbr <= seg1; 4'h2: sm_dbr <= seg2; 4'h3: sm_dbr <= seg3; 4'h4: sm_dbr <= seg4; 4'h5: sm_dbr <= seg5; 4'h6: sm_dbr <= seg6; 4'h7: sm_dbr <= seg7; 4'h8: sm_dbr <= seg8; 4'h9: sm_dbr <= seg9; 4'ha: sm_dbr <= sega; 4'hb: sm_dbr <= segb; 4'hc: sm_dbr <= segc; 4'hd: sm_dbr <= segd; 4'he: sm_dbr <= sege; 4'hf: sm_dbr <= segf; default: ;endcaseendendmodule3、接口:clk--PIN_N2rst_n--PIN_N25SEG0[0]--PIN_AF10SEG0[1]--PIN_AB12SEG0[2]--PIN_AC12SEG0[3]--PIN_AD11SEG0[4]--PIN_AE11SEG0[5]--PIN_V14SEG0[6]--PIN_V13SEG1[0]--PIN_V20SEG1[1]--PIN_V21SEG1[2]--PIN_W21SEG1[3]--PIN_Y22SEG1[4]--PIN_AA24SEG1[5]--PIN_AA23SEG1[6]--PIN_AB24SEG2[0]--PIN_AB23SEG2[1]--PIN_V22SEG2[2]--PIN_AC25SEG2[3]--PIN_AC26SEG2[4]--PIN_AB26SEG2[5]--PIN_AB25SEG2[6]--PIN_Y24SEG3[0]--PIN_Y23SEG3[1]--PIN_AA25SEG3[2]--PIN_AA26SEG3[3]--PIN_Y26SEG3[4]--PIN_Y25SEG3[5]--PIN_U22SEG3[6]--PIN_W244、上机程序module SegDynamicDisp(CLK,rst_n,SEG0,SEG1,SEG2,SEG3); input CLK;input rst_n;output [6:0]SEG0;output [6:0]SEG1;output [6:0]SEG2;output [6:0]SEG3;reg [6:0]SEG0;reg [6:0]SEG1;reg [6:0]SEG2;reg [6:0]SEG3;//........以上是定义的一些输入输出接口.......................... parameter seg0=7'hC0,seg1=7'hF9,seg2=7'hA4,seg3=7'hB0,seg4=7'h99,seg5=7'h92,seg6=7'h82,seg7=7'hF8,seg8=7'h80,seg9=7'h90,sega=7'h88,segb=7'h83,segc=7'hC6,segd=7'hA1,sege=7'h86,segf=7'h8E;//..............以上是定义的参数,用来标记段代码................... reg[23:0] cnt;reg [15:0]counter;always @(posedge CLK or negedge rst_n)if(!rst_n)begincnt<=24'D0;counter<=2'b00;endelsebegincnt<=cnt+1'b1;if(cnt==24'D1*******)begincnt<=0;counter<=counter+1;endend//..........用来实现计数功能和控制数字递增的速度.................... always @(counter)begincase(counter[3:0])4'h0: SEG0 <= seg0; 4'h1: SEG0 <= seg1; 4'h2: SEG0 <= seg2; 4'h3: SEG0 <= seg3; 4'h4: SEG0 <= seg4; 4'h5: SEG0 <= seg5; 4'h6: SEG0 <= seg6; 4'h7: SEG0 <= seg7; 4'h8: SEG0 <= seg8; 4'h9: SEG0 <= seg9; 4'ha: SEG0 <= sega; 4'hb: SEG0 <= segb; 4'hc: SEG0 <= segc; 4'hd: SEG0 <= segd; 4'he: SEG0 <= sege; 4'hf: SEG0 <= segf; default: ;endcasecase(counter[7:4])4'h0: SEG1 <= seg0; 4'h1: SEG1 <= seg1; 4'h2: SEG1 <= seg2; 4'h3: SEG1 <= seg3; 4'h4: SEG1 <= seg4; 4'h5: SEG1 <= seg5; 4'h6: SEG1 <= seg6; 4'h7: SEG1 <= seg7; 4'h8: SEG1 <= seg8; 4'h9: SEG1 <= seg9; 4'ha: SEG1 <= sega; 4'hb: SEG1 <= segb; 4'hc: SEG1 <= segc; 4'hd: SEG1 <= segd; 4'he: SEG1 <= sege; 4'hf: SEG1 <= segf; default: ;endcasecase(counter[11:8])4'h0: SEG2 <= seg0; 4'h1: SEG2 <= seg1; 4'h2: SEG2 <= seg2; 4'h3: SEG2 <= seg3;4'h4: SEG2 <= seg4;4'h5: SEG2 <= seg5;4'h6: SEG2 <= seg6;4'h7: SEG2 <= seg7;4'h8: SEG2 <= seg8;4'h9: SEG2 <= seg9;4'ha: SEG2 <= sega;4'hb: SEG2 <= segb;4'hc: SEG2 <= segc;4'hd: SEG2 <= segd;4'he: SEG2 <= sege;4'hf: SEG2 <= segf;default: ;endcasecase(counter[15:12])4'h0: SEG3 <= seg0;4'h1: SEG3 <= seg1;4'h2: SEG3 <= seg2;4'h3: SEG3 <= seg3;4'h4: SEG3 <= seg4;4'h5: SEG3 <= seg5;4'h6: SEG3 <= seg6;4'h7: SEG3 <= seg7;4'h8: SEG3 <= seg8;4'h9: SEG3 <= seg9;4'ha: SEG3 <= sega;4'hb: SEG3 <= segb;4'hc: SEG3 <= segc;4'hd: SEG3 <= segd;4'he: SEG3 <= sege;4'hf: SEG3 <= segf;default: ;endcaseend//...................用来实现显示功能..................... endmodule5、实验结果复位按键为0时:HEX3HEX2 HEX1 HEX0 显示的为0000;复位按键为1时:HEX3 HEX2 HEX1 HEX0 显示的依次为:0000——FFFF。

实验四数码管的动态显示实验班级通信1102 姓名谢剑辉学号20110803223 指导老师袁文澹一、实验目的熟悉掌握数码管动态显示的基本方法;根据已知电路和设计要求在实验板上实现数码管动态显示。

根据已知电路和设计要求在PROTEUS平台仿真实现控制系统。

二、实验内容1、在STC89C52实验平台的4位数码管上实现动态显示0123→1234→2345→3456→4567→5678→6789→7890→8901→9012→0123→不断反复,每隔2s切换显示内容。

2、思考:如何实现当4位数码管显示的内容中有“1”时,蜂鸣器蜂鸣。

三、实验原理实验要求“4位数码管上实现动态显示0123→1234→2345→3456→4567→5678→6789→7890→8901→9012→0123→不断反复,每隔2s切换显示内容”。

动态扫描可以实现要求。

简单地说,动态扫描就是选通一位,送一位数据。

原理图中的P10~P13是位选信号,即选择哪个数码管显示数字;P00~P07是段码,即要显示的数字。

可以通过依次选通一位7段数码管并通过P0端口送出显示数据。

由于人眼的视觉残留原理,如果这种依次唯一选通每一位7段数码管的动作在0.1s内完成,就会造成多位数码管同时点亮显示各自数字的假象。

本实验使用中断,实现每2s更新一次数字。

四、实验方法与步骤设计思路和方法:1、根据电路图,分析数码管动态显示的设计思路,使用中断实现每2秒更新一次数字的设计思路,以及实现当4位数码管显示的内容中有“1”时,蜂鸣器蜂鸣的设计思路。

(1)数码管动态显示的原理如“实验原理”里所述,不赘述;(2)使用中断实现每2s更新一次数字的设计思路:本次实验使用Timer0中断,由于其定时时间最大为65536us,不能实现2s的长延时,那么可以使用多次中断来实现,并且在中断到来时,不断地死循环显示数字,即根据动态显示原理“选通一位,来一位数据”。

由于最大的数字为9,则(x%10),(x+1)%10,(x+2)%10,(x+3)%10分别是千位,百位,十位,个位上的数字。

八位七段数码管动态显示电路设计八位七段数码管动态显示电路的设计一七段显示器介绍七段显示器,在许多产品或场合上经常可见。

其内部结构是由八个发光二极管所组成,为七个笔画与一个小数点,依顺时针方向为A、B、C、D、E、F、G与DP等八组发光二极管之排列,可用以显示0~9数字及英文数A、b、C、d、E、F。

目前常用的七段显示器通常附有小数点,如此使其得以显示阿拉伯数之小数点部份。

七段显示器的脚位和线路图如下图4.1所示( 其第一支接脚位于俯视图之左上角 )。

图4.1、七段显示器俯视图由于发光二极管只有在顺向偏压的时候才会发光。

因此,七段显示器依其结构不同的应用需求,区分为低电位动作与高电位动作的两种型态的组件,另一种常见的说法则是共阳极( 低电位动作 )与共阴极( 高电位动作 )七段显示器,如下图4.2所示。

( 共阳极 ) ( 共阴极 )图4.2、共阳极(低电位动作)与共阴极(高电位动作)要如何使七段显示器发光呢?对于共阴极规格的七段显示器来说,必须使用“ Sink Current ”方式,亦即是共同接脚COM为VCC,并由Cyclone II FPGA使接脚成为高电位,进而使外部电源将流经七段显示器,再流入Cyclone II FPGA的一种方式本实验平台之七段显示器模块接线图如下图4.5所示。

此平台配置了八组共阳极之七段显示器,亦即是每一组七段显示器之COM接脚,均接连至VCC 电源。

而每一段发光二极管,其脚位亦均与Cyclone II FPGA接连。

四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。

图4.5、七段显示器模块接线图七段显示器之常见应用如下➢可作为与数值显示相关之设计。

⏹电子时钟应用显示⏹倒数定时器⏹秒表⏹计数器、定时器⏹算数运算之数值显示器二七段显示器显示原理七段显示器可用来显示单一的十进制或十六进制的数字,它是由八个发光二极管所构成的( 每一个二极管依位置不同而赋予不同的名称,请参见图4.1 ) 。

EDA实验二八位七段数码管动态显示电路的设计八位七段数码管动态显示电路是一种常用的显示电路,用于将数字信号转换成七段数码管的显示形式。

本文将详细介绍八位七段数码管动态显示电路的设计原理和实现方法。

首先,我们先介绍一下七段数码管的基本原理和工作方式。

一、七段数码管的基本原理和工作方式七段数码管通常由七个独立的LED组成,分别代表数字0到9和字母A到F。

这七个LED分别为a,b,c,d,e,f,g,用于显示不同的数字。

通过控制每个LED的亮灭状态,可以显示出不同的数字。

七段数码管通常采用共阳极或共阴极的方式控制。

在共阳极的情况下,数码管的共阳极引脚接Vcc,每个LED的阴极引脚分别通过控制芯片上的开关来控制灯的亮灭;在共阴极的情况下,数码管的共阴极引脚接GND,每个LED的阳极引脚通过控制芯片上的开关来控制灯的亮灭。

根据实际需要选择共阳极或共阴极的七段数码管。

在七段数码管中,每个LED代表一个计算机的位数。

例如,数码管中的aLED表示计算机数据的最低位,而gLED表示计算机数据的最高位。

二、八位七段数码管动态显示电路的设计原理八位七段数码管动态显示电路的设计原理是将八个七段数码管连接在一起,通过改变每个数码管的亮灭状态,实现数字的动态显示。

具体的设计原理是通过一个计数器生成7个时序信号,然后再通过逻辑控制器将这些时序信号分配给各个数码管。

可以用三个个位计数器来实现生成的7个时序信号。

其中,一个计数器用于控制7个段的扫描,即a,b,c,d,e,f,g;另外两个计数器用于控制8位数码管中的8个数位,即1,2,3,4,5,6,7,8具体实现时,可以通过一个时钟信号来驱动计数器,每个计数器都有一个计数使能信号和一个计数复位信号。

通过适当的设计时钟信号的频率和计数使能/复位信号的控制,可以实现不同的动态显示效果。

三、八位七段数码管动态显示电路的实现方法八位七段数码管动态显示电路的实现方法可以分为三个步骤:计数器设计、逻辑控制器设计和电路布线。

电子课程设计—8位数码管动态显示电路设计学院:电子信息工程学院专业、班级:姓名:学号:指导老师:2014年12月目录一、设计任务与要求................................................. (3)二、总体框图................................................. (3)三、选择器件................................................. (3)四、功能模块................................................. (9)五、总体设计电路图................................................. . (10)六、心得体会.................................................. .. (12)8位数码管动态显示电路设计一、设计任务与要求1. 设计个8位数码管动态显示电路,动态显示1、2、3、4、5、6、7、8。

2. 要求在某一时刻,仅有一个LED数码管发光。

3. 该数码管发光一段时间后,下一个LED发光,这样8只数码管循环发光。

4. 当循环扫描速度足够快时,由于视觉暂留的原因,就会感觉8只数码管是在持续发光。

5、研究循环地址码发生器的时钟频率和显示闪烁的关系。

二、总体框图设计的总体框图如图2-1所示。

图2-1总体框图三、选择器件 1、数码管数码管是一种由发光二极管组成的断码型显示器件,如图1所示。

U13DCD_HEX图1 数码管数码管里有八个小LED 发光二极管,通过控制不同的LED 的亮灭来显示出不同的字形。

数码管又分为共阴极和共阳极两种类型,其实共阴极就是将八个LED 的阴极连在一起,让其接地,这样给任何一个LED 的另一端高电平,它便能点亮。

八位七段数码管动态显示电路的设计

一、 实验目的

1、 了解数码管的工作原理。

2、 学习七段数码管显示译码器的设计。

3、 学习VHDL 的 CASE 语句及多层次设计方法。

二、 实验原理

七段数码管是电子开发过程中常用的输出显示设备。

在实验系统中使用的是两个四位 一体、共阴极型七段数码管。

其单个静态数码管如下图 4-4-1所示。

数码管与之相么。

四位一体的七段数

数码管的位选信号端口。

八个数码管

个数码管分别由各自的位选信号来控制, 被选通的数码管显示数据,其余关闭。

三、 实验内容 本实验要求完成的任务是在时钟信号的作用下, 通过输入的键值在数码管上显示相应的 键值。

在实验中时,数字时钟选择 1024HZ 作为扫描时钟,用四个拨动开关做为输入,当四 个拨动开关置为一个二进制数时,在数码管上显示其十六进制的值。

四、 实验步骤 1、 打开QUARTUSI 软件,新建一个工程。

2、 建完工程之后,再新建一个 VHDL File ,打开VHDL 编辑器对话框。

3、 按照实验原理和自己的想法,在 VHDL 编辑窗口编写 VHDL 程序,用户可参照光盘中 提供的示例程序。

4、 编写完VHDL 程序后,保存起来。

方法同实验一。

5、 对自己编写的VHDL 程序进行编译并仿真,对程序的错误进行修改。

6、 编译仿真无误后,根据用户自己的要求进行管脚分配。

分配完成后,再进行全编译 一次,以使管脚分配

生效。

7、 根据实验内容用实验导线将上面管脚分配的 FPGA f 脚与对应的模块连接起来。

如果是调用的本书提供的 VHDL 代码,则实验连线如下:

CLK FPGA 寸钟信号,接数字时钟 CLOCK3并将这组时钟设为 1024HZ 。

由于七段数码管公共端连接到

I b ,当数码管的中的那一个段被输入高电

、 e

、 d 、 c 、 b

、 a 的

KEY[3..O]:数码管显示输入信号,分别接拨动开关的S4, S3, S2, S1。

LEDAG[6..0] :数码管显示信号,接数码管的

G 、 F 、E 、D 、C 、B 、A 。

SEL[2..0] :数码管的位选信号,接数码管的 SEL2、SEL1、 SEL0。

8、用下载电缆通过 JTAG 口将对应的sof 文件加载到FPGA 中。

观察实验结果是否与自

己的编程思想一致。

五、实验现象与结果

以设计的参考示例为例, 当设计文件加载到目标器件后, 将数字信号源模块的时钟选择 为1464H Z,拨动四位拨动开关,使其为一个数值,则八个数码管均显示拨动开关所表示的

六进制的值。

六、源代码

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

);

end smg;

architecture beha of smg is

Signal key:std_logic_vector(3 downto

0); begin process(clk)

variable dount : std_logic_vector(2 downto 0); begin if clk'event and clk='1' then -- end if;

del<=dount;

end process;

process(del,k)

begin

case (del) is

when "000"=>key<=k;--+"0000";

when "001"=>key<=k;--+"0001";

when "010"=>key<=k;--+"0010";

when "011"=>key<=k;--+"0011";

when "100"=>key<=k;--+"0100";

when "101"=>key<=k;--+"0101"; when "110"=>key<=k;--+"0110"; when

"111"=>key<=k;--+"0111"; end case;

end process; process(key) begin case key is

entity smg is

port( clk : in std_logic; - k : in std_logic_vector(3 downto 0); -- ledag : out std_logic_vector(6

downto 0); -- del :

buffer std_logic_vector(2 示信号

定义动态扫描时钟信号

定义四位输入信号

定义七位输出信号 downto 0) -- 定义八位数码管位置显

检测时钟上升沿 dount:=dount+1; --

计数器 dount 累加

when "0000" => ledag <="0111111"; when "0001" => ledag <="0000110"; when "0010" => ledag <="1011011"; when "0011" => ledag <="1001111"; when "0100" => ledag <="1100110"; when "0101" => ledag <="1101101"; when "0110" => ledag <="1111101"; when "0111" => ledag <="0000111"; when "1000" => ledag <="1111111"; when "1001" => ledag <="1101111"; when "1010" => ledag <="1110111"; when "1011" => ledag <="1111100"; when "1100" => ledag <="0111001"; when "1101" => ledag <="1011110"; when "1110" => ledag <="1111001"; when "1111" => ledag <="1110001"; when others => null;

end case;

end process; end beha;。