课程设计--篮球24秒定时器的制作

- 格式:doc

- 大小:112.00 KB

- 文档页数:10

随着电子技术的飞速发展,电子技术在社会生活中发挥越来越重要的作用,特别是各种竞技运动中,定时器成为检验运动员成绩的重要工具。

篮球是一项大众化的运动,现实生活中的比赛有很多规则,正规比赛中我们知道,在一次进攻中,一方队员只有24秒的进攻时间,超过这个时间则表示一次违例。本课程设计题目紧密联系生活实际,用简单的数字逻辑电路实现24秒减数计时器,每隔一秒计数一次直到减到零并发生光报警,计数器有置数功能,最初置数为24,并且有清零功能和暂停功能,使设计电路具有很好的实用价值;

计时器主要是由即使电路、控制电路、以及译码显示电路3个部分组成。电路结构简单,功能方便、快捷。

篮球24秒定时器的制作

结构设计与方案选择

本设计是以555构成震荡电路,由74LS192来充当计数器,构成NBA24秒倒计时电路。该电路简单,无需用到晶振,芯片都是市场上容易购得的。设计功能完善,能实现直接清零、启动和暂停/连续计时,还具有报警功能。

一、设计原理与电路

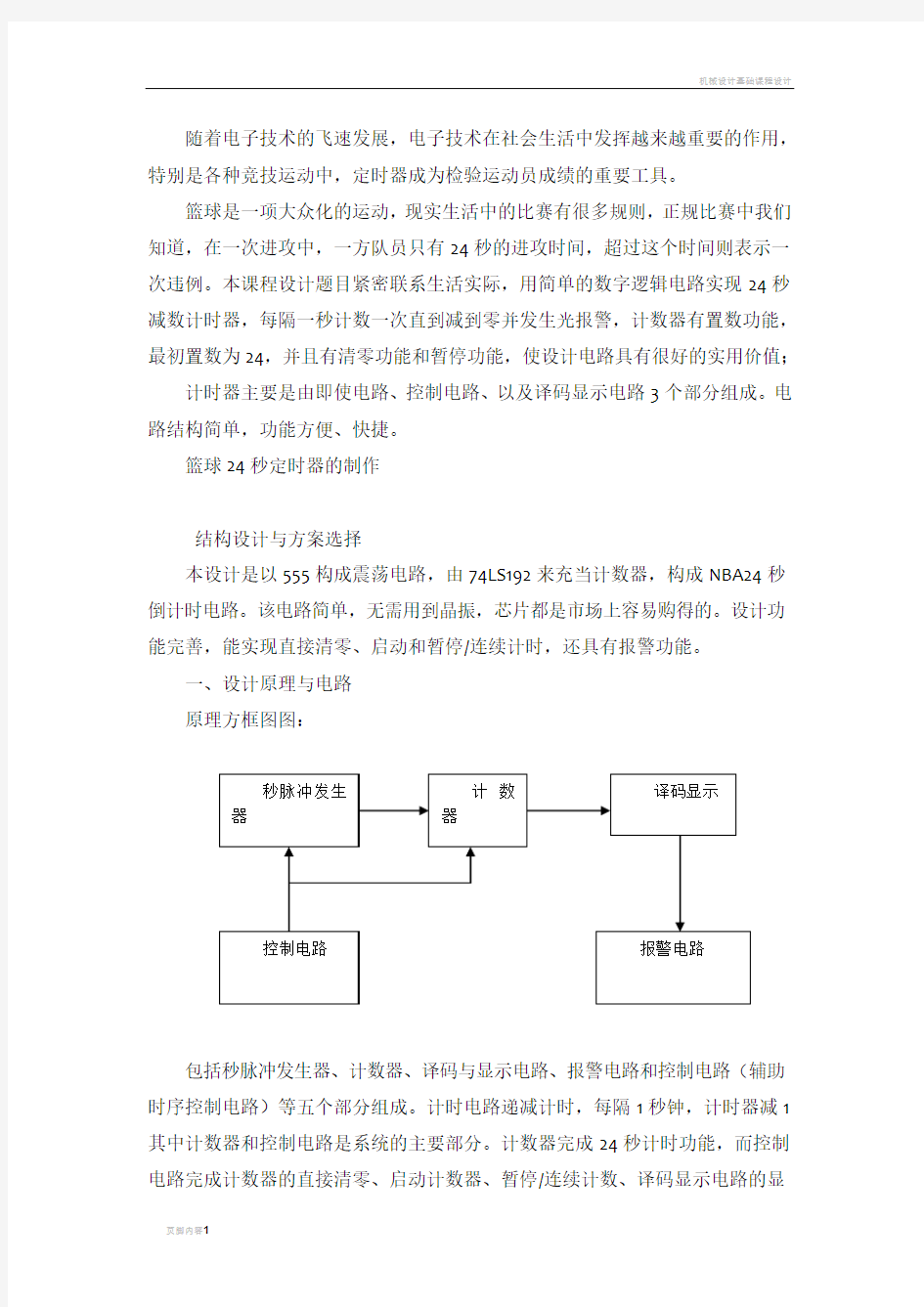

原理方框图图:

包括秒脉冲发生器、计数器、译码与显示电路、报警电路和控制电路(辅助时序控制电路)等五个部分组成。计时电路递减计时,每隔1秒钟,计时器减1其中计数器和控制电路是系统的主要部分。计数器完成24秒计时功能,而控制电路完成计数器的直接清零、启动计数器、暂停/连续计数、译码显示电路的显

示与灭灯、定时时间到报警等功能。当计时器递减计时到零(即定时时间到)时,显示器上显示00,同时发出光电报警信号。

二、电路

方案中采用两片192芯片,能实现暂停、清零、置数的功能。结构比较简单,开关3为清零控制端,开关2为置数端,开关1为暂停/继续开关。秒脉冲由555定时器构成。

它的工作原理是:只有当低位BO1端发出借位脉冲时,高位计数器才做减数器。当高低位全部变为零时,且CPD为0时置数端LD2=0,计数器完成置数,在CPD脉冲信号的作用下,计数器再次进入下一轮减计数。

秒脉冲发生器产生的信号是电路的时钟脉冲和定时标准,但本设计对此信号要求并不是太高,电路采用555集成电路或由TTL与非门组成的多谐振荡器的构成。

译码显示电路用74LS48和共阴极七段LED显示器组成。报警电路在实验中可用发光二极管代替。

三、单元电路的设计

1、进制计数器的设计

计数器选用集成电路74LS192是十进制可编码同步加法计数器,它有可逆计数功能,CPU、CPD分别是加计数器、减计数器的时钟脉冲输入端(上升沿触发)其中RD是异步清零端,高电平有效,PL是异步并行置数控制端(低电平有效)预置数据输入端包括P0,P1,P2,P3,其中最高端为P3。TCU为加法计数的进位输出端,TCD是减法计数的借位输出端,MR是并行数据输入端,Q3-Q0是输出端。

计数器选用中规模继承74LS192进行设计较为简便,74LS192是十进制可编程同步加/减计数功能。下图是74LS192外引线排列图与功能表:

当PL=1,MR=O时,若时钟脉冲加到端CU,且CD=1则计数器在预置数的基础上完成加数技能,当加数到9时,TCu端发出进位下跳脉冲;若时钟脉冲加到CD端,且CU=1,则计数器在预制位置数的基础上完成计数功能,当减到0时,TCd端发出借位下跳脉冲。

实验核心电路如图:

其预置数为N=(00100100)8421BCD=( 24)10,只有当低位1端发出借位脉冲时,高位计数器才作减计数。当高、低位计数器处于全零,且=0时,置数端2=0,计数器完成并行置数,在端的输入时钟脉冲作用下,计数器再次进入下一循环减计数。

2秒脉冲电路

试验中,可以采用555定时器或者是TTL与非门电路来实现秒脉冲,但是555 定时器成本低,性能可靠,只需要外接几个电阻、电容,就可以实现多谐振荡器、脉冲产生与变换电路,555定时器比较容易操作,故本实验采用555定时器

555定时器的内部框图如下:

、

其中1脚为接地端,8脚接电源。4端是复位端,555构成的多谐振振荡器。接通电源后,电容C2被充电,,当Vc上升到2/3Vcc时,触发器被复位,同时放电BJTT导通,此时V0为低电平,电容C通过R5和T放电,使Vc下降,当下降至1/3Vcc时,触发器又被置位,V0翻转为高电平,当C放电结束时,T 截止,Vcc将通过R5和Rw、R4向电容器充电,Vc由1/3Vcc上升到2/3Vcc 当Vc上升到2/3Vcc时,触发器又发生翻转,如此周而复始,在输出端就得到一个周期性的方波

555逻辑功能表

R D Vi1(6端输入

信号)

Vi2(2端输入

信号)

V0(输出电

压)

T的

状态

0X X低电平导

通

1<2/3Vcc>1/3Vcc不变不

变

1>2/3Vcc<1/3Vcc高电平(不

定)

截止

1<2/3Vcc<1/3Vcc高电平截

止

1>2/3Vcc>1/3Vcc低电平导

通

秒脉冲电路图

3数码显示电路的设计

显示电路用两块74LS48和两块数码管构成,74LS48芯片是一种常用七段数码管驱动器,其显示电路如图所示

(A、B、C、D是BCD码的输入端;a、b、c、d、e、f、g是输入端)

74LS48的功能表

4、控制电路

输入端13为秒脉冲输入,输出端2接上低端192的CPD,输入端2为一个开关,当输入高电平时,电路正常工作,当输入低电平时,与非门输出为高电平,输出端2被封锁一直会输出低电平。输入端1为一个反馈值,为高端192的BO2端(13脚)。在未达到00秒时,一端一直输入为高电平,当到达00时,一端输为低电平将使其封锁。

5、元器件清单