运算放大器参数的基本仿真方法示例(2nd edition)

- 格式:pdf

- 大小:188.44 KB

- 文档页数:15

virtuoso运放基础参数仿真方法Virtuoso is a type of operational amplifier, also known as op-amp, used in electronic circuits to amplify weak electric signals. It is essential to understand the basic parameters of the Virtuoso op-amp in order to effectively simulate its performance and behavior in various circuit designs.Virtuoso运放是一种运算放大器,也称为运放,用于电子电路中放大弱电信号。

在有效地模拟Virtuoso运放在各种电路设计中的性能和行为之前,了解其基本参数是至关重要的。

The first basic parameter to consider when simulating the Virtuoso op-amp is the open-loop gain, which is the gain of the amplifier when there is no feedback in the circuit. This parameter is crucial in determining the overall amplification capability of the op-amp and understanding its linear behavior. To simulate the open-loop gain, one can use SPICE (Simulation Program with Integrated Circuit Emphasis) software to create a test circuit with the op-amp and measure the gain using the simulation results.模拟Virtuoso运放时首先要考虑的基本参数是开环增益,即在电路中没有反馈时放大器的增益。

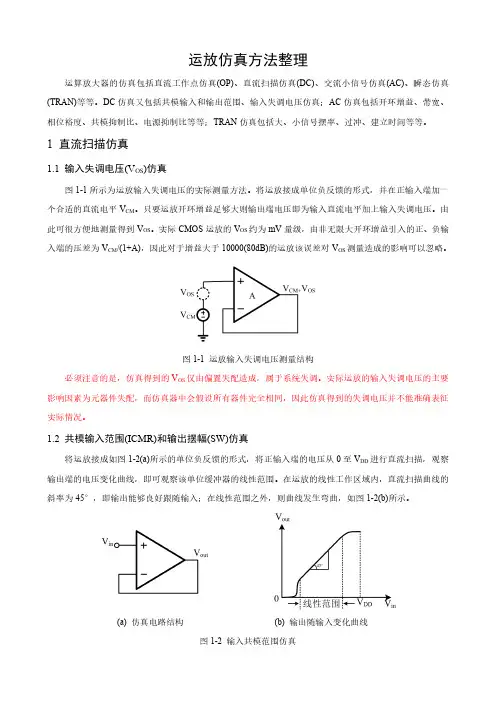

运放仿真方法整理运算放大器的仿真包括直流工作点仿真(OP)、直流扫描仿真(DC)、交流小信号仿真(AC)、瞬态仿真(TRAN)等等。

DC仿真又包括共模输入和输出范围、输入失调电压仿真;AC仿真包括开环增益、带宽、相位裕度、共模抑制比、电源抑制比等等;TRAN仿真包括大、小信号摆率、过冲、建立时间等等。

1直流扫描仿真1.1输入失调电压(V OS)仿真图1-1所示为运放输入失调电压的实际测量方法。

将运放接成单位负反馈的形式,并在正输入端加一个合适的直流电平V CM。

只要运放开环增益足够大则输出端电压即为输入直流电平加上输入失调电压。

由此可很方便地测量得到V OS。

实际CMOS运放的V OS约为mV量级,由非无限大开环增益引入的正、负输入端的压差为V CM/(1+A),因此对于增益大于10000(80dB)的运放该误差对V OS测量造成的影响可以忽略。

图1-1运放输入失调电压测量结构必须注意的是,仿真得到的V OS仅由偏置失配造成,属于系统失调。

实际运放的输入失调电压的主要影响因素为元器件失配,而仿真器中会假设所有器件完全相同,因此仿真得到的失调电压并不能准确表征实际情况。

1.2共模输入范围(ICMR)和输出摆幅(SW)仿真将运放接成如图1-2(a)所示的单位负反馈的形式,将正输入端的电压从0至V DD进行直流扫描,观察输出端的电压变化曲线,即可观察该单位缓冲器的线性范围。

在运放的线性工作区域内,直流扫描曲线的斜率为45°,即输出能够良好跟随输入;在线性范围之外,则曲线发生弯曲,如图1-2(b)所示。

(a)仿真电路结构(b)输出随输入变化曲线图1-2输入共模范围仿真用该结构仿真得到的线性范围同时受到输入共模范围和输出摆幅的限制,因此无法用该结构精确测得ICMR。

对于一般的运放,输出摆幅范围通常大于输入共模范围,故该方法能够大致预估输入共模范围。

图1-3(a)所示的反相电压放大器增益为-10。

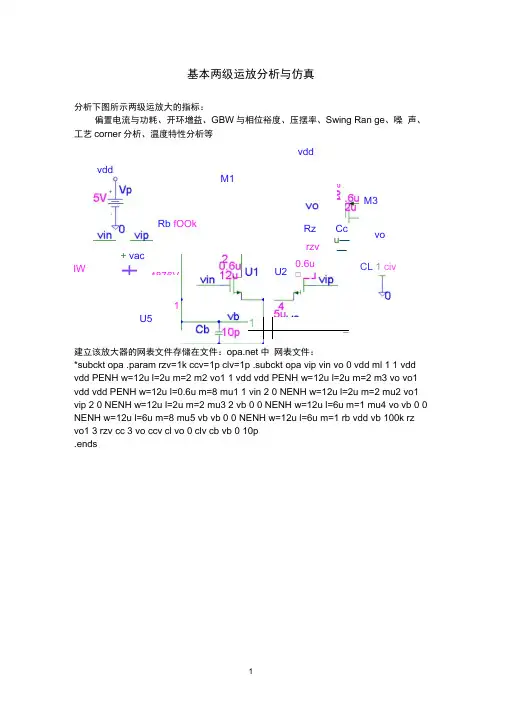

基本两级运放分析与仿真分析下图所示两级运放大的指标:偏置电流与功耗、开环增益、GBW 与相位裕度、压摆率、Swing Ran ge 、噪 声、工艺corner 分析、温度特性分析等vdd建立该放大器的网表文件存储在文件: 中 网表文件:*subckt opa .param rzv=1k ccv=1p clv=1p .subckt opa vip vin vo 0 vdd ml 1 1 vdd vdd PENH w=12u l=2u m=2 m2 vo1 1 vdd vdd PENH w=12u l=2u m=2 m3 vo vo1 vdd vdd PENH w=12u l=0.6u m=8 mu1 1 vin 2 0 NENH w=12u l=2u m=2 mu2 vo1 vip 2 0 NENH w=12u l=2u m=2 mu3 2 vb 0 0 NENH w=12u l=6u m=1 mu4 vo vb 0 0 NENH w=12u l=6u m=8 mu5 vb vb 0 0 NENH w=12u l=6u m=1 rb vdd vb 100k rz vo1 3 rzv cc 3 vo ccv cl vo 0 clv cb vb 0 10p .endsIWU5M1Rz 801rzv0.6u □ 2uCc u —— ccvM3 vo CL 1 civ1—Rb fOOkvdd1+ vac士 .4876VU21. 工作点分析由仿真结果查得电路的功耗是多少?各个 mos 管的工作区域,以及 MOS f的漏极电流为多少?该放大器的偏置电流为多少?网表如下:*opa fivea.sp .optio ns post=2.lib 7home/fzu/hspice/models/cz6h_v28.lib' TT .in clude "/home/fzu/example/zuoye/opa. net" xa1 vip vin vo 0 vdd opa vdd vdd 0 5vin1 vin 0 dc 2.4876vip1 vip 0 dc 2.4876 ac 1 0 .op .end(1)电路的功耗:电路功耗为1.7896mW(2)各个mos 管的工作区域,MOS 管的漏极电流,以及放大器的偏置电流:aubcktxalxalxal xalelement 1 :ml 11 :m3 1 :mul 1 :mu2 1 :rau3 model 0:penh0 :penh 0 :penhO :nenh 0:nenh 0 :nenhregion Sarurati Sarurati Sarurati Sarurati Saturati Saturati id -17.2O45U -17.2O45U -?S8.8356u17.2O45U 17.2O45U 34.4089Usubcktxal xalelementl:mu4 1;model 0:nenh 0: nenliregionSaturati Saturatiid2S0.8355U34,6021u2. 直流分析仿真该运放的输入输出特性曲线,求小信号增益、输出摆幅( output swing range ) 网表如下:*opa fiveb.sp .optio ns post=2.lib 7home/fzu/hspice/models/cz6h_v28.lib' TT .in eludesubck t element 0 :vdd 0:vinl0:viplvol t 吕 5.0000 2.4876 2.4S76 current -357.9266u 0.0. power1.7&96m 0. 0.■st 蓝盍盖T/cilt:age sourcestotal voltage source power dissipation=watts"/home/fzu/example/zuoye/opa .n et" xa1 vip vin vo 0 vdd opavdd vdd 0 5vin1 vin 0 dc 2.4876vip1 vip 0 dc 2.4876 ac 1 0.dc vip1 2.484 2.491 0.0001.end(1)输入输出特性曲线、小信号增益(2)输出摆幅由输入输出特性曲线图可得输出摆幅为: 4.9112V-0.01057V=4.90063V3. 交流分析(调整管子尺寸使运放的增益大于60dB,调整补偿电容使相位裕度大于60)①在没有补偿电阻(Rz),补偿电容(Cc)为1pf的条件下求该放大器单位增益带宽(GW/B相位裕度;网表如下:*opa fivec.sp.optio ns post=2.lib 7home/fzu/hspice/models/cz6h_v28.lib' TT.in clude "/home/fzu/example/zuoye/opa. net".param rzv=0xa1 vip vin vo 0 vdd opa vdd vdd 0 5vin1 vin 0 dc 2.4876vip1 vip 0 dc 2.4876 ac 1 0.ac dec 100 100 200meg.print ac vdb(vo) vp(vo).endSHCF FxpIfflFr ^n-Kinn 7HC-. I Cn^iljhi "z 呼n I nr. P^ip^nal hi■叭yTags ia r:nfis ssss(,仇•”:ma■M"S- HWViH J? «I*^|HW 的HMWIM 3S i I : I--Fi* *J M¥T**iR +1 "iLI! : I'M*!* <? WYV^iM +] >I MPW3*I> *A , WV^jlH *E 壬,b«Vr>iW 4? VVWi* 国tawjR[d£d E<J■- ] cimril hrtm:* | . J R, jhmuhMnJrrij 讥■皿摯>| 呼SR 匚 E Ev 加百Vim ns 2DC 序呼List文件截图:23.44229x2・9183m -110.3815由上图有,该放大器单位增益带宽(GWB为:23.44229MHz,相位裕度为:180-110.3815=79.6185②分析没有补偿电阻,补偿电容在(0~5pf)变化的时候对GWB口相位裕度的影响;网表如下:*opa fivec.sp.optio ns post=2.lib 7home/fzu/hspice/models/cz6h_v28.lib' TT.in clude "/home/fzu/example/zuoye/opa. net".param rzv=0xa1 vip vin vo 0 vdd opavdd vdd 0 5vin1 vin 0 dc 2.4876vip1 vip 0 dc 2.4876 ac 1 0.ac dec 100 10 200meg sweep ccv 0 5p 0.5p.print ac vdb(vo) vp(vo).end:* | 在“口.巾w章他卫hui.、j B? SF1 C£ Exdni V rn』母hu "List文件截图:ccv=0pf ccv=0.5pf165.958693(48.2706m161.8799|42.65795X93-S095m-122.3574 ccv=1pf ccv=1.5pf23.44229X 1.1939m-1 10.3fi2715.84893x8jD. 7018m-105.5736 ccv=2pf ccv=2.5pf12 022fi4K«5.9371m-IDS.19339.5499SX175.8782m-101.5&22 ccv=3pf ccv=3.5pf&.12831X20.4489m-100.S029 6.91&31X102.5128m-99.9992 ccv=4pf ccv=4.5pf6.0256QX155.0402m-99.4129 5.37032X144.4577m-99.015S ccv=5pf4.B9779x37.0887m-98.7967由上知随着电容增大,单位增益带宽减小,相位裕度增大③ 分析补偿电阻在(0~2K变化,补偿电容为1pf的时候对GWB口相位裕度的影响。

实验一、两级运算放大器的仿真验证一、实验目的1、学习集成运算电路单元的设计参数的仿真、测试、验证。

2、学习采用Cadence工具实现IC电路设计的基本操作和方法,包括电路图的编辑以及仿真调试过程。

二、实验内容本实验通过设计一个两级运算放大器电路学习Cadence工具下电路的设计和仿真方法。

实验内容包括:1.熟悉Cadence界面及基本的建立新的cell文件等基本过程;2.完成两级运算放大器电路的设计;3.利用Cadence的仿真环境得到波形,分析仿真结果。

该电路设计采用上华CSMC0.5umCMOS工艺设计,工作电压5V。

三、实验原理运算放大器是一个能将两个输入电压之差放大并输出的集成电路。

运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT或FET 的电子器件。

它是许多模拟系统和混合信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。

1.共模抑制比:差分放大电路抑制共模信号及放大差模信号的能力,常用共模抑制比作为一项技术指标来衡量,其定义为放大器对差模信号的电压放大倍数Aud与对共模信号的电压放大倍数Auc之比,称为共模抑制比,英文全称是Common Mode Rejection Ratio,因此一般用简写CMRR来表示,符号为Kcmr,单位是分贝db。

2.共模输入范围:是指在差分放大电路中,二个输入端所加的是大小相等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范围。

3.电源抑制比:是输入电源变化量(以伏为单位)与转换器输出变化量(以伏为单位)的比值(PSRR),常用分贝表示。

通常把满量程电压变化的百分数与电源电压变化的百分数之比称为电源抑制比。

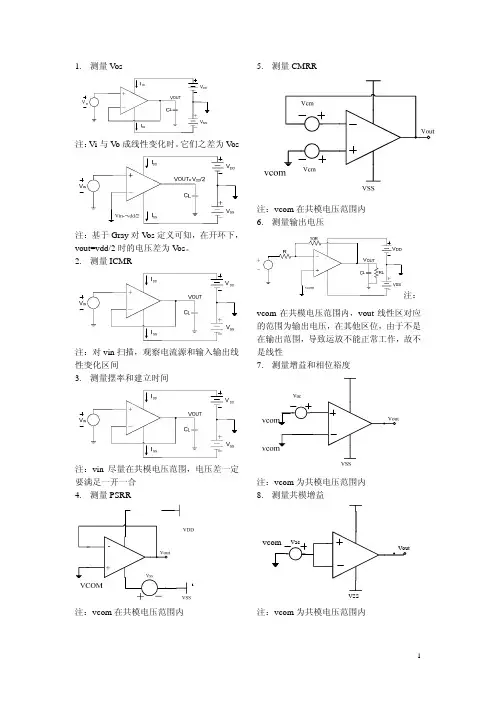

1. 测量V os

注:Vi 与V o 成线性变化时。

它们之差为V

os

注:基于Gray 对V os 定义可知,在开环下,vout=vdd/2时的电压差为V os 。

2. 测量

ICMR

注:对vin 扫描,观察电流源和输入输出线性变化区间

3. 测量摆率和建立时间

注:vin 尽量在共模电压范围,电压差一定要满足一开一合 4. 测量

PSRR

注:vcom 在共模电压范围内

5. 测量

CMRR

注:vcom 在共模电压范围内 6. 测量输出电压

vcom 在共模电压范围内,vout 线性区对应的范围为输出电压,在其他区位,由于不是在输出范围,导致运放不能正常工作,故不是线性

7. 测量增益和相位裕度

注:vcom 为共模电压范围内 8. 测量共模增益

VSS

注:vcom 为共模电压范围内

表1 典型的无缓冲CMOS运算放大器特性。

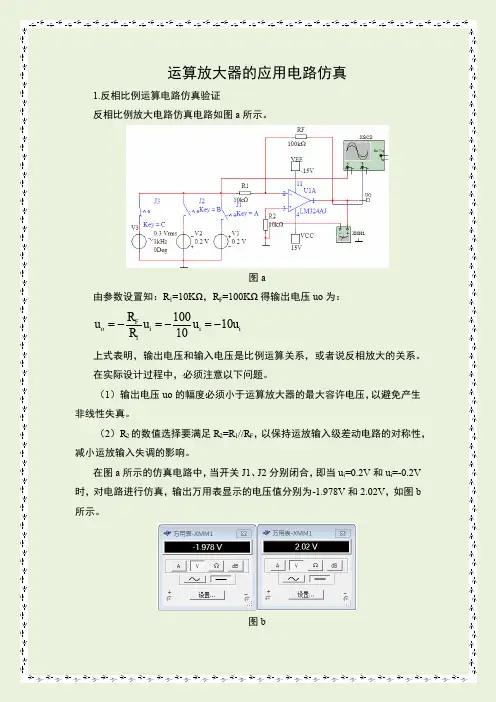

运算放大器的应用电路仿真1.反相比例运算电路仿真验证反相比例放大电路仿真电路如图a所示。

图a由参数设置知:R1=10KΩ,R F=100KΩ得输出电压u o为:iii1o1010100uuuRRu F-=-=-=上式表明,输出电压和输入电压是比例运算关系,或者说反相放大的关系。

在实际设计过程中,必须注意以下问题。

(1)输出电压u o的幅度必须小于运算放大器的最大容许电压,以避免产生非线性失真。

(2)R2的数值选择要满足R2=R1//R F,以保持运放输入级差动电路的对称性,减小运放输入失调的影响。

在图a所示的仿真电路中,当开关J1、J2分别闭合,即当u i=0.2V和u i=-0.2V 时,对电路进行仿真,输出万用表显示的电压值分别为-1.978V和2.02V,如图b 所示。

图b由仿真结果可以看出,由于运算放大器的非理想性,使得仿真结果和理论分析结果之间有一定的差别,但相差不大,可以认为仿真结果与理论计算结果一致。

当开关J3闭合时,按下仿真开关,观察示波器的输入、输出波形,如图c所示。

图c2.具有限幅作用的电压比较器当u i<u R时,比较器输出端的电压为-U om,稳压管正向导通,忽略其正向导通压降,u o≈0;当u i>u R时,比较器输出端的电压为U om,稳压管反向击穿,u o≈U Z。

图e为带双向限幅的过零比较器的仿真电路。

图e仿真输入、输出信号的波形如图f所示,此时输出正的最大值为稳压管D2的稳定电压+5.755V,负的最大值为稳压管D1的稳定电压-5.755V。

图f。

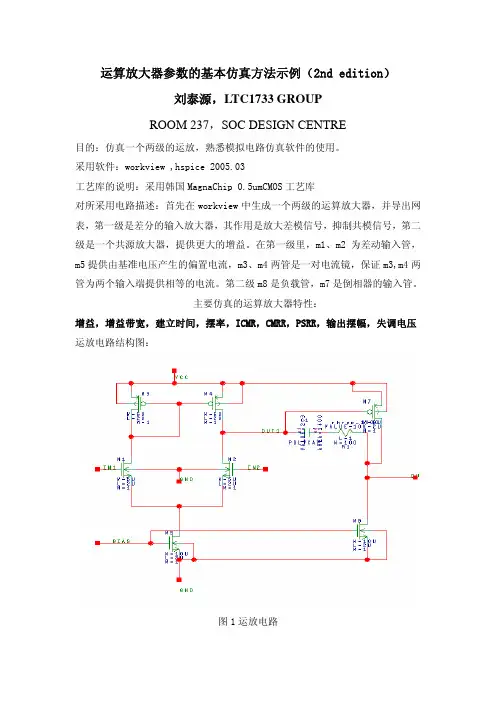

运算放大器参数的基本仿真方法示例(2nd edition)刘泰源,LTC1733 GROUPROOM 237,SOC DESIGN CENTRE目的:仿真一个两级的运放,熟悉模拟电路仿真软件的使用。

采用软件:workview ,hspice 2005.03工艺库的说明:采用韩国MagnaChip 0.5umCMOS工艺库对所采用电路描述:首先在workview中生成一个两级的运算放大器,并导出网表,第一级是差分的输入放大器,其作用是放大差模信号,抑制共模信号,第二级是一个共源放大器,提供更大的增益。

在第一级里,m1、m2为差动输入管,m5提供由基准电压产生的偏置电流,m3、m4两管是一对电流镜,保证m3,m4两管为两个输入端提供相等的电流。

第二级m8是负载管,m7是倒相器的输入管。

主要仿真的运算放大器特性:增益,增益带宽,建立时间,摆率,ICMR,CMRR,PSRR,输出摆幅,失调电压 运放电路结构图:图1运放电路静态工作点的调节在整个模拟电路的设计中是非常重要的,因为不同功能的模块对器件的工作状态有不同的要求,在电路设计初期确定下的管子的工作状态就在这个阶段与以实现。

实现的语句在hspice里面是.op语句。

这个语句会在仿真生成的.lis文件里面形成一个关于管子工作状态的理解,查找.lis文件中的region关键字,就能找到各个管子工作点的列表。

静态工作点的调节:采用的方法,先设计第一级的的工作点,再设计第二级的工作点。

第一级工作点设计要求五个管子都工作在饱和区,并且保证电路的对称,在vcc,in1,in2和bias上要加上适当的偏置电压。

我设定的bias为 1.5v,in1=in2=2.5v,这个时候要注意调节各管子的宽长比使管子达到饱和,如果m3,m4是线形区,则应该调节减小m3,m4的宽长比,同时通过增加m5的宽长比增大偏置电流,如果m5处于线形区,则应该采取与上面所说的相反的方法,如果输入管处于线形区,要考虑输入的偏置电压是否合适,同时折中上面的调节方法。

基本两级运放分析与仿真分析下图所示两级运放大的指标:偏置电流与功耗、开环增益、GBW 与相位裕度、压摆率、Swing Ran ge 、噪 声、工艺corner 分析、温度特性分析等vdd建立该放大器的网表文件存储在文件: 中 网表文件:*subckt opa .param rzv=1k ccv=1p clv=1p .subckt opa vip vin vo 0 vdd ml 1 1 vdd vdd PENH w=12u l=2u m=2 m2 vo1 1 vdd vdd PENH w=12u l=2u m=2 m3 vo vo1 vdd vdd PENH w=12u l=0.6u m=8 mu1 1 vin 2 0 NENH w=12u l=2u m=2 mu2 vo1 vip 2 0 NENH w=12u l=2u m=2 mu3 2 vb 0 0 NENH w=12u l=6u m=1 mu4 vo vb 0 0 NENH w=12u l=6u m=8 mu5 vb vb 0 0 NENH w=12u l=6u m=1 rb vdd vb 100k rz vo1 3 rzv cc 3 vo ccv cl vo 0 clv cb vb 0 10p .endsIWU5M1Rz 801rzv0.6u □ 2uCc u —— ccvM3 vo CL 1 civ1—Rb fOOkvdd1+ vac士 .4876VU21. 工作点分析由仿真结果查得电路的功耗是多少?各个 mos 管的工作区域,以及 MOS f的漏极电流为多少?该放大器的偏置电流为多少?网表如下:*opa fivea.sp .optio ns post=2.lib 7home/fzu/hspice/models/cz6h_v28.lib' TT .in clude "/home/fzu/example/zuoye/opa. net" xa1 vip vin vo 0 vdd opa vdd vdd 0 5vin1 vin 0 dc 2.4876vip1 vip 0 dc 2.4876 ac 1 0 .op .end(1)电路的功耗:电路功耗为1.7896mW(2)各个mos 管的工作区域,MOS 管的漏极电流,以及放大器的偏置电流:aubcktxalxalxal xalelement 1 :ml 11 :m3 1 :mul 1 :mu2 1 :rau3 model 0:penh0 :penh 0 :penhO :nenh 0:nenh 0 :nenhregion Sarurati Sarurati Sarurati Sarurati Saturati Saturati id -17.2O45U -17.2O45U -?S8.8356u17.2O45U 17.2O45U 34.4089Usubcktxal xalelementl:mu4 1;model 0:nenh 0: nenliregionSaturati Saturatiid2S0.8355U34,6021u2. 直流分析仿真该运放的输入输出特性曲线,求小信号增益、输出摆幅( output swing range ) 网表如下:*opa fiveb.sp .optio ns post=2.lib 7home/fzu/hspice/models/cz6h_v28.lib' TT .in eludesubck t element 0 :vdd 0:vinl0:viplvol t 吕 5.0000 2.4876 2.4S76 current -357.9266u 0.0. power1.7&96m 0. 0.■st 蓝盍盖T/cilt:age sourcestotal voltage source power dissipation=watts"/home/fzu/example/zuoye/opa .n et" xa1 vip vin vo 0 vdd opavdd vdd 0 5vin1 vin 0 dc 2.4876vip1 vip 0 dc 2.4876 ac 1 0.dc vip1 2.484 2.491 0.0001.end(1)输入输出特性曲线、小信号增益(2)输出摆幅由输入输出特性曲线图可得输出摆幅为: 4.9112V-0.01057V=4.90063V3. 交流分析(调整管子尺寸使运放的增益大于60dB,调整补偿电容使相位裕度大于60)①在没有补偿电阻(Rz),补偿电容(Cc)为1pf的条件下求该放大器单位增益带宽(GW/B相位裕度;网表如下:*opa fivec.sp.optio ns post=2.lib 7home/fzu/hspice/models/cz6h_v28.lib' TT.in clude "/home/fzu/example/zuoye/opa. net".param rzv=0xa1 vip vin vo 0 vdd opa vdd vdd 0 5vin1 vin 0 dc 2.4876vip1 vip 0 dc 2.4876 ac 1 0.ac dec 100 100 200meg.print ac vdb(vo) vp(vo).endSHCF FxpIfflFr ^n-Kinn 7HC-. I Cn^iljhi "z 呼n I nr. P^ip^nal hi■叭yTags ia r:nfis ssss(,仇•”:ma■M"S- HWViH J? «I*^|HW 的HMWIM 3S i I : I--Fi* *J M¥T**iR +1 "iLI! : I'M*!* <? WYV^iM +] >I MPW3*I> *A , WV^jlH *E 壬,b«Vr>iW 4? VVWi* 国tawjR[d£d E<J■- ] cimril hrtm:* | . J R, jhmuhMnJrrij 讥■皿摯>| 呼SR 匚 E Ev 加百Vim ns 2DC 序呼List文件截图:23.44229x2・9183m -110.3815由上图有,该放大器单位增益带宽(GWB为:23.44229MHz,相位裕度为:180-110.3815=79.6185②分析没有补偿电阻,补偿电容在(0~5pf)变化的时候对GWB口相位裕度的影响;网表如下:*opa fivec.sp.optio ns post=2.lib 7home/fzu/hspice/models/cz6h_v28.lib' TT.in clude "/home/fzu/example/zuoye/opa. net".param rzv=0xa1 vip vin vo 0 vdd opavdd vdd 0 5vin1 vin 0 dc 2.4876vip1 vip 0 dc 2.4876 ac 1 0.ac dec 100 10 200meg sweep ccv 0 5p 0.5p.print ac vdb(vo) vp(vo).end:* | 在“口.巾w章他卫hui.、j B? SF1 C£ Exdni V rn』母hu "List文件截图:ccv=0pf ccv=0.5pf165.958693(48.2706m161.8799|42.65795X93-S095m-122.3574 ccv=1pf ccv=1.5pf23.44229X 1.1939m-1 10.3fi2715.84893x8jD. 7018m-105.5736 ccv=2pf ccv=2.5pf12 022fi4K«5.9371m-IDS.19339.5499SX175.8782m-101.5&22 ccv=3pf ccv=3.5pf&.12831X20.4489m-100.S029 6.91&31X102.5128m-99.9992 ccv=4pf ccv=4.5pf6.0256QX155.0402m-99.4129 5.37032X144.4577m-99.015S ccv=5pf4.B9779x37.0887m-98.7967由上知随着电容增大,单位增益带宽减小,相位裕度增大③ 分析补偿电阻在(0~2K变化,补偿电容为1pf的时候对GWB口相位裕度的影响。

运算放大器参数的基本仿真方法示例(2nd edition)刘泰源,LTC1733 GROUPROOM 237,SOC DESIGN CENTRE目的:仿真一个两级的运放,熟悉模拟电路仿真软件的使用。

采用软件:workview ,hspice 2005.03工艺库的说明:采用韩国MagnaChip 0.5umCMOS工艺库对所采用电路描述:首先在workview中生成一个两级的运算放大器,并导出网表,第一级是差分的输入放大器,其作用是放大差模信号,抑制共模信号,第二级是一个共源放大器,提供更大的增益。

在第一级里,m1、m2为差动输入管,m5提供由基准电压产生的偏置电流,m3、m4两管是一对电流镜,保证m3,m4两管为两个输入端提供相等的电流。

第二级m8是负载管,m7是倒相器的输入管。

主要仿真的运算放大器特性:增益,增益带宽,建立时间,摆率,ICMR,CMRR,PSRR,输出摆幅,失调电压 运放电路结构图:图1运放电路静态工作点的调节在整个模拟电路的设计中是非常重要的,因为不同功能的模块对器件的工作状态有不同的要求,在电路设计初期确定下的管子的工作状态就在这个阶段与以实现。

实现的语句在hspice里面是.op语句。

这个语句会在仿真生成的.lis文件里面形成一个关于管子工作状态的理解,查找.lis文件中的region关键字,就能找到各个管子工作点的列表。

静态工作点的调节:采用的方法,先设计第一级的的工作点,再设计第二级的工作点。

第一级工作点设计要求五个管子都工作在饱和区,并且保证电路的对称,在vcc,in1,in2和bias上要加上适当的偏置电压。

我设定的bias为 1.5v,in1=in2=2.5v,这个时候要注意调节各管子的宽长比使管子达到饱和,如果m3,m4是线形区,则应该调节减小m3,m4的宽长比,同时通过增加m5的宽长比增大偏置电流,如果m5处于线形区,则应该采取与上面所说的相反的方法,如果输入管处于线形区,要考虑输入的偏置电压是否合适,同时折中上面的调节方法。

在调整第一级进入管子都饱和后,加上第二级一起调整,目的是使两级的管子都进入饱和区,这里遇到的一个问题,就是第二级的两个管子很难同时到达饱和区,发现问题在于m3,m4管的vds太小,使第二级的m7管只能在线形区,减小m3,m4的宽长比和调节m5的偏置电流后,可以使两管都饱和。

在整个过程中,都需要保持偏置管和电流镜对管的对称性。

NOTE:(上述调节过程仅是一个参考,实际电路中BIAS电流不可能这么精确,所以,在实际情况中,调试电路的中的偏置电压更多的由实际偏置电路提供。

) 1.开环增益:1)输入差模信号,调节使各晶体管的工作点都处在饱和区,在输入端in1加入交流信号,in2加上偏置信号。

2)输入激励:vcc vcc 0 5vbias bias 0 1.2vin1 in1 0 2.5vin2 in2 0 2.5 ac 1.ac dec 10 1 1200meg图2:开环增益的输入激励3)仿真结果:图3:开环增益图2.频率响应和相位裕度:1)频率响应和相位裕度反映了运放正常工作的范围和工作的稳定性,相位裕度至少大于45度。

可以看见通过增加弥勒电容和弥勒电阻的频率补偿回路,电路的相位裕度达到了要求。

2)输入激励:vcc vcc 0 5vbias bias 0 1.2vin1 in1 0 2.5vin2 in2 0 2.5 ac 1.ac dec 10 1 1200meg图4:频率响应仿真激励3)仿真结果:在增加补偿回路前,在增益低至0前,相位已经超过-180度,工作不稳定。

图5:补偿前的频率响应加入补偿后,相位裕度已经超过60度,运放可以稳定工作。

图6:补偿后的频率响应图3.输入失调电压1)由于运放的电路不对称和工艺制造的误差造成的输出电压为0时,输入in1,in2有一个小的失调电压。

而对于单端输出运放来说,根据GRAY对单端输出的运放输入失调电压的界定:当vout=vcc/2时,两个输入输出端的电压的差值。

本仿真就是采用GRAY的界定。

2)仿真方法:使负端接直流偏置,正端在偏置电压附近做直流扫描,在-40度到120度的范围内,取vout=vcc/2 的点,得到不同温度下的失调电压。

仿真失调电压不一定要仿真随温度的变化,也可以仿真随电源电压的变化,也可以单取一点,而不做曲线。

另外一种可选的方法就是把电路连接成单位增益形式,然后再从正端做稍描,看vout输出曲线和输入之间平行段的垂直电压差值。

这个方法不甚严密,但是也可以仿真出和上面一种方法相近似的结果。

vcc vcc 0 5vbias bias 0 1.5.temp xpvin1 in1 0 2.5vin2 in2 0.DC VIN2 2.3V 2.7V 0.1m sweep xp -40 125 1.MEAS DC Y1 WHEN V(OUT2)=par('V(Vcc)/2').MEAS DC VOS param='Y1-V(IN1)'.end图7 offset 仿真激励3)结果分析图8 失调电压由于在偏置管是直接加的一个直流偏置,而在实际的工作中,偏置电压是由基准模块提供的,此电压会随着温度和vcc的变化而变化,所以在实际的工作中失调电压会比这次的值更大一些。

NOTE:实际的失调电压是没有办法从仿真中获得的,上面仿真出来的大多是系统失调电压,这个数值一般从uV级到mV级之间,现在在工程上有一种模拟仿真系统失调电压的方法,就是把运放的输入对管分别向相反方向改变最小线宽长度,比如说有一运放,其输入对管为M1,M2, W/L=10/5 M=5 ,那么在仿真的时候可以做可以的拉偏处理,使(W/L)M1= 9.5/5 M=5 ,(W/L)M2=10.5/5 M=5 ,再反向拉偏,就可以得到两组模拟实际情况的失调电压值。

注意,这里只是模拟,不是实际的失调电压。

4.共模输入电压范围和共模输出电压范围1)共模输入范围是指运放正常工作时输入电压的范围,如果过高会造成连接vcc的m3,m4进入线形区,同理,如果输入电压过低,会造成连接gnd的m5进入线形区。

输出范围是指在输入的激励下,输出电压可以达到的摆幅。

2)激励:仿真是通过对运放进行单位增益连接实现,共模输入正常工作范围内,输入和输出电压基本相等,并且电流镜的偏置电流在共模输入范围内应该保持一个大致恒定的值。

图9 共模输入输出仿真激励图vcc vcc 0 5vbias bias 0 1.2vin2 in2 0 2.5.dc vin2 -2 5 0.1.print v(*) i(*)3)仿真结果:从图中可以看出,闭环条件下,满足上述条件的共模输入和输出电压范围在1.6v到4.4v之间。

图10 共模输入输出电压范围5.共模增益1)共模信号的放大系数,因为运放需要抑制共模信号,所以此增益越小越好。

2)激励:把in1和in2连接到一起,加上交流信号。

vcc vcc 0 5vbias bias 0 1.2vin2 in2 0 2.5 ac 1.ac dec 10 1 200meg.print ac vdb(*).print v(*) i(*)图11 共模输入增益的激励4)仿真结果:图12:共模增益4)共模增益的抑制和改进如上图所示,共模增益在低频的时候接近10分贝,这样电路抑制共模信号的能力是比较差的,所以要通过增加输入管的宽长比的方法,这样会使对共模信号的抑制能力增强。

图12:改进后的共模增益图6.共模抑制比1)反映对输入噪声的抑制能力,是差模的增益除共模增益的值,此值越大越好。

2)激励:vcc vcc 0 5vbias bias 0 1.5vin1 in1 out2 0 ac 1vin2 in2 0 2.5 ac 1.ac dec 10 1 200meg.print ac vdb(*)图13,共模抑制比激励图4)仿真结果和分析改进图14,共模抑制比最初仿真出来的共模抑制比比较小,这里做了两个改进,一,如上面说的,调节了输入管减小了共模的增益,第二,根据共模抑制比的计算公式分析,要加大抑制比,还需要增加m3,m4的等效电阻和减小m5的等效电阻值,这个需要调节第一级的各管的宽长比实现,并且在调节过程中,要注意保证各管的静态工作点仍然在饱和区。

7.电源抑制比1)反映电路对电源噪声的抑制能力,对vcc和gnd分别有psrr+和psrr-。

2)仿真激励vcc vcc 0 5 ac 1vbias bias 0 1.5vin2 in2 0 2.5.ac dec 10 1 1200meg.print ac vdb(*)图15:Psrr=+仿真激励图3)仿真结果图16:Psrr+仿真可见电路对电源抑制达到了90分贝。

8.摆率和建立时间1)摆率反映的是大信号的参数,是反映输出电压变换的速率的限制。

建立时间:是运放受到小信号激励时达到输出的稳定值所需要的时间。

在仿真时,需要在输出节点接入实际的负载电容Cload,这个电容需要利用仿真的LIS文件out节点的实际电容来估算。

2)仿真激励:vcc vcc 0 5vbias bias 0 1.5vplus in2 0 pwl 1n 0 10n 0 11n 2 500n 2 501n 0.tran 2n 700n.print v(*) i(*)图17 摆率和建立时间仿真激励 3)仿真结果和讨论图18 SLEW RATE AND SETUP TIME建立时间为70ns,摆率为2.4e7v/s。

9环路增益1)这是反映电路的反馈性能的参数,当环路增益较大时,电路进入深度负反馈。

2)仿真激励:如图所示,out2的直流分量通过反馈回路的电阻送回运放的负输入端。

而测试的交流信号通过r3加入到反馈回路,最后观察out2点的电压增益。

vcc vcc 0 5vbias bias 0 1.5vin2 in2 0 2.5vin2 in2 0 2.5vin a 0 3 ac -1.ac dec 10 1 1200meg.print ac vdb(*).print v(*) i(*)图19仿真激励图3)仿真结果;图20 环路增益仿真结果环路增益大于90分贝,可以判断电路可以进入深度负反馈。

仿真中还有一个重要的问题就是工艺角仿真问题,这个将在第三版中叙述。