第11章 组合逻辑电路

- 格式:ppt

- 大小:3.27 MB

- 文档页数:67

第11章数字电路综合案例内容提要前面的章节介绍了数字电路的基本知识、基本理论、常用器件,以及数字电路分析和设计的基本方法。

本章涉及到复杂数字系统的设计。

数设计对象从译码器、计数器等这些基本逻辑功能电路到了数字钟等综合的数字逻辑系统的设计;设计方法也由采用真值表到求逻辑表达式、画出电路图的方式到通过确定总体方案,采取从局部到整体,用各种中、大规模集成电路来满足要求的数字电路系统的方式。

本章结合数字钟这一实际的案例来介绍数字电路系统的设计方法,进一步提高学生的综合能力和解决实际问题的能力。

基本教学要求1.了解中小规模集成电路的作用及实用方法。

2.了解数字钟电路的原理。

3.掌握综合数字电路系统的设计流程和设计方法。

11.1概述数字系统的设计,采用从整体到局部,再从局部到整理的设计方法。

首先对系统的目标、任务、指标要求等进行分析,确定系统的总体方案;然后把系统的总体方案分成若干功能部件,绘出系统的方框图;之后运用数字电路的分析和设计方法分别进行设计,或者是直接选用集成器件去构成功能部件;最后把这些功能部件连接组合起来,便构成了完整的数字系统,通过对电路的分析和测试修改,完善与优化整个系统。

这是传统的数字系统的设计方法,也是下面要介绍的内容。

随着计算机技术的发展,电子设计自动化EDA成为了现代电子系统设计与仿真的重要手段,对于复杂系统的设计十分有效,尤其是硬件描述语言的使用,使硬件软件化,让数字系统的设计更加方便、高效。

下面以数字钟系统设计为例,介绍综合数字电路系统的设计方法。

数字钟是一种用数字电子技术实现时、分、秒计时的装置,与传统的机械式时钟相比具准确、直观、寿命长等特点。

目前广泛用于个人家庭以及车站、码头、剧场、办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大的方便。

数字钟也是一种典型的数字电路,其中包括了组合逻辑电路和时序逻辑电路。

通过数字钟的设计进一步了解数字系统设计时用到的中小规模集成电路的使用方法,进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法。

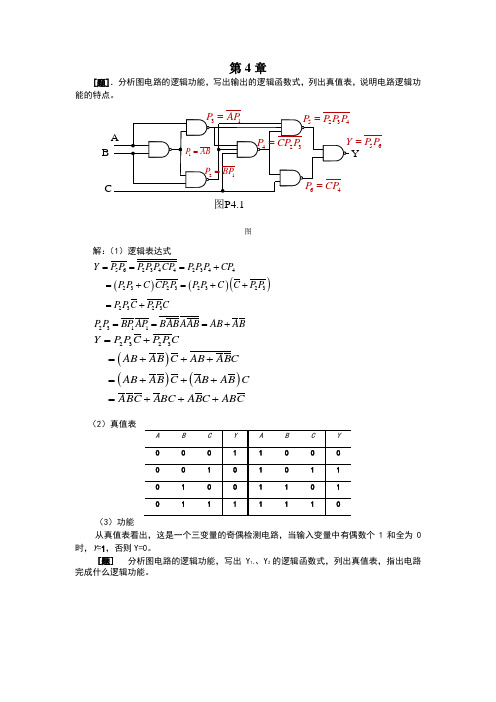

第4章[题].分析图电路的逻辑功能,写出输出的逻辑函数式,列出真值表,说明电路逻辑功能的特点。

图P4.1B YAP 56P P =图解:(1)逻辑表达式()()()5623442344232323232323Y P P P P P CP P P P CP P P C CP P P P C C P P P P C P PC ===+=+=++=+ 2311P P BP AP BABAAB AB AB ===+()()()2323Y P P C P P CAB AB C AB ABC AB AB C AB AB CABC ABC ABC ABC=+=+++=+++=+++(2)真值表(3)功能从真值表看出,这是一个三变量的奇偶检测电路,当输入变量中有偶数个1和全为0时,Y =1,否则Y=0。

[题] 分析图电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

图P4.3B1Y 2[解]解: 2Y AB BC AC =++12Y ABC A B C Y ABC A B C AB BC AC ABC ABC ABC ABC =+++=+++++=+++()())由真值表可知:、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[题] 图是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

图P4.4[解](1)COMP=1、Z=0时,TG1、TG3、TG5导通,TG2、TG4、TG6关断。

,(2)COMP=0、Z=0时,Y1=A1,Y2=A2,Y3=A3,Y4=A4。

、COMP=1、Z=0时的真值表、Z=0的真值表从略。

[题] 用与非门设计四变量的多数表决电路。

当输入变量A、B、C、D有3个或3个以上为1时输出为1,输入为其他状态时输出为0。

[解] 题的真值表如表所示,逻辑图如图(b)所示。