IDDQ测试原理与方法

- 格式:docx

- 大小:3.28 MB

- 文档页数:14

半导体测试公司简介Integrated Device Manufacturer (IDM):半导体公司,集成了设计和制造业务。

IBM:(International Business Machines Corporation)国际商业机器公司,总部在美国纽约州阿蒙克市。

Intel:英特尔,全球最大的半导体芯片制造商,总部位于美国加利弗尼亚州圣克拉拉市。

Texas Instruments:简称TI,德州仪器,全球领先的数字信号处理与模拟技术半导体供应商。

总部位于美国得克萨斯州的达拉斯。

Samsung:三星,韩国最大的企业集团,业务涉及多个领域,主要包括半导体、移动电话、显示器、笔记本、电视机、电冰箱、空调、数码摄像机等。

STMicroelectronics:意法半导体,意大利SGS半导体公司和法国Thomson半导体合并后的新企业,公司总部设在瑞士日内瓦。

是全球第五大半导体厂商。

Strategic Outsourcing Model(战略外包模式):一种新的业务模式,使IDM厂商外包前沿的设计,同时保持工艺技术开发Motorola:摩托罗拉。

总部在美国伊利诺斯州。

是全球芯片制造、电子通讯的领导者。

ADI:(Analog Devices, Inc)亚德诺半导体技术公司,公司总部设在美国,高性能模拟集成电路(IC)制造商,产品广泛用于模拟信号和数字信号处理领域。

Fabless:是半导体集成电路行业中无生产线设计公司的简称。

专注于设计与销售应用半导体晶片,将半导体的生产制造外包给专业晶圆代工制造厂商。

一般的fabless公司至少外包百分之七十五的晶圆生产给别的代工厂。

Qualcomm:高通,公司总部在美国。

以CDMA(码分多址)数字技术为基础,开发并提供富于创意的数字无线通信产品和服务。

如今,美国高通公司正积极倡导全球快速部署3G网络、手机及应用。

Broadcom:博通,总部在美国,全球领先的有线和无线通信半导体公司。

基于CMOS电路的IDDQ测试电路设计来源:中电网引言测试CMOS电路的方法有很多利测试逻辑故障的一•般方法是采用逻辑响应测试,即通常所说的功能测试。

功能测试可诊断出逻辑错误,但不能检查出晶体管常开故障、晶体管常闭故障、晶体管栅氧化层短路,互连桥短路等物理缺陷引发的故障,这些缺陷并不会立即影响电路的逻辑功能,通常要在眠件工作一•段时间后才会影响其逻辑功能。

功能测试是基于逻辑电平的故障检测,通过测景原始输出的电压来确定逻辑电平,因此功能测试实际上是电压测试。

电压测试对于检测固定型故障,特别是双极型工艺中的固定型故障是有效的,但对于检测CMOS I艺中的其他类型故障则显得有些不足,而这些故障类型在CMOS 电路测试中却是常见的。

对于较大规模电路,电压测试测试集的生成相当复杂且较长,需要大量的实验数据样本。

1DDQ测试是对功能测试的补充。

通过测试静态电流1DDQ可检测出电路中的物理缺陷所引发的故障。

TDDQ测试还可以检测出那些尚未引起逻辑错误,但在电路初期会转换成逻辑错误的缺陷。

本文所设计的IDDQ电流测试电路对CMOS被测电路进行检测,通过观察测试电路输出的高低电平可知被测电路是否有物理缺陷。

测试电路的核心是电流差分放大电路,其输出一个与被测电路IDDQ电流成正比的输出。

测试电路出联在被测电路与地之间,以检测异常的1DDQ 电流01 IDDQ测试原理电流IDDQ是指当CMOS集成电路中的所有管子都处于静止状态时的电源总电流。

对于中小规模集成电路,正常状态时无故障的电源总电流为微安数量级;当电路出现桥接或栅源短接等故障时,会在静态CMOS电路中形成一条从正电源到地的低阻通路,会导致电源总电流超过毫安数量级。

所以静态电源电流IDDQ测试原理是:无故障CMOS电路在静态条件下的漏电流非常小,而故障条件下漏电流变得非常大,可以设定一•个阈值作为电路有无故障的判据。

CMOS集成电路不论其形式和功能如何,都可以用-•个反向器的模型来表示。

IDDQ测试在大规模集成电路测试中尤为重要,本文将详细阐述IDDQ测试原理,测试方法。

IDDQ TUTORIALGoals:To show how a quiescent current supply test, Iddq, contributes to ICdefect isolation. To understand the challenges of the Iddq measurement.To select from the available Iddq test methods, the ones which mostpractically reduce test time.To Identify and validate circuit defect using failures analysistechniques and relate Iddq anomalies to the circuit flaw cause.Objectives:List the circuit requirements and test conditions for Iddq and describehow Iddq limit is derived.Write the advantages and disadvantages of the three main categoriesof electrical tests DC, Function Iddq and AC in isolating defects.List the order of defect types and their related symptoms and the characteristics of a valid Iddq failure.Topics:Iddq ConceptsDefects and FaultsIddq Test Pattern GenerationTesting MethodsFailure AnalysisReview QuestionsIddq Concepts13.0IntroductionCMOS IC makers were frustrated, because, oddly, some parts which were successfully tested failed to function in the field, while some other parts suffered performance degradation. Two peculiarities were common to these escape (bad) parts:(1) Iddq is several order of magnitude higher than the normal expected residual value of less than 1uA.(2) Iddq value varies with the applied pattern between normal to abnormal.A circuit defect, such as a short or partial transistor saturation, was suspected since CMOS is a nanowatt logic. See the example below for explanation of such case where a defective device eludes screening.13.1 ExampleAn embedded inverter is shown in Figure 13.1 in which the source and drain of the p-FET are shorted.Ans (1): When an input logic 0 pattern is applied at A, the n-FET is turned off and the voltage appearing at the output correspond to logic1. The value of Iddq is residual despite the existence of the short.However, when an input logic 1 pattern is applied, the n-FET is turned on elevating Iddq. Ans (2): Assume that the short is resistive. The equivalent circuit of the elevated Iddq is the voltage divider shown in Figure 13.2.Rs is the short resistance and Rn is the output ON resistance of then-FET.By assuming that Rs/Rn is greater than 3, Vo turns to be logically correct for the subsequent gate. Although weak, this logic level allows function test to pass. Flaws due to one type of defects called bridging have impedances that could easily meet the previous assumption of Rs/Rn > 3.If Iddq was monitored during logic 1 application, that defect would have been found. There would be no need to propagate and validate, as in conventional function, any signal at the primary outputs.13.2 What is Iddq Testable?To be able to use this powerful, and at first glance simple, detection method some requisites are needed namely:The device circuitry must be CMOS.The magnitude of background current from voltage dividers, embedded RAMs, pull-up or pull-down resistors, etc., must not be high enough to swamp the minuscule Iddq measurement. The voltage applied to any part of the circuit must not partially turn on the p or the n-FETs. Refer to the CMOS Transfer Characteristics.The part is rested from all external as well as internal transients at time of measurement.13.3 The Advantages of IddqDiagnosing defects using Iddq offers several advantages because:Iddq is a cost-effective test method indispensable to identify some defects which are indiscernible by the conventional functional tests.The applied pattern needs only sensitize the node. This offers an immense computational reduction (1:7) over the conventional function test in pattern generation.It has been proven that the number of Iddq measurements required to reach a fault coverage greater than 90% is relatively small (2 digits).Iddq performs, to some extent, the job of burn-in by isolating those devices which will not survive in the field; the walking-wounded ones.Iddq enhances quality, shortens time-to-market and provides an efficient SPMC (Statistical Process Monitor and Control) for yield enhancement.The types of potential problems detected by Iddq include:Process flaws: bridging, deformed traces, mask problems, incomplete etching, logically redundant defects.Design flaws: Floating gates, logic contention, mask generation errors.13.4 Why doesn’t Iddq replace Function?Iddq is intended to complement and not replace function for several reasons:Neither conventional function nor Iddq alone detects 100% of the defects.The Iddq timing is not set to run at the max specified frequency all the times due to test method constrains.The voltages and currents requirements Vil/Vih, Iol/Ioh, Vdd are different in conventional function than those in Iddq.13.5 What Iddq does not detectIddq does not detect any defect which does not lead to an appreciable increase in the supply current such as:Highly resistive interconnects and open defects which do not elevate Iddq.Defects which inhibit the transistor from being conductive.Transmission gate defects which lead to weak logic.Dynamic interconnects such as capacitive and inductive coupling.。

基于小波变换的ADC电流测试方法∗朱彦卿1 , 何怡刚1 , 阳辉1,2(1. 湖南大学电气与信息工程学院湖南长沙,410082;2.信息产业部电子第五研究所元器件检测中心广东广州,510610)摘要:本文提出了一种基于小波分析的混合信号电流测试方法,该方法通过小波变换对电路的动态电流信号I dd进行分解来诊断电路是否存在故障。

对示例ADC电路的仿真结果表明,该方法不仅能够有效检测出电路中的各种缺陷,而且比积分法和傅立叶分析方法对故障有更高的灵敏度。

关键词:混合信号, 电流测试, 动态电流,小波变换中图分类号:TN431.1 文献标识码: AA Novel Wavelet Transform Based Current Testing for A/D ConvertersZhu Yan-qing1 , He Yi-gang1 , Yang Hui1,2(1.College of Electrical and Information Engineering, Hunan University, Changsha, 410082, China;2.China Electronic Product Reliability and Environmental Testing Research Institute, Guangzhou, 510610)Abstract: In this paper, a novel wavelet analysis based dynamic current(I dd) testing method for mixed signal fault detection is presented. The simulation result for a ADC circuit present that the wavelet method not only can effectively detect all the fault, but also have higher sensitivity than integral and FFT method.Keywords: mixed signal, current testing, I dd, wavelet transform1引言随着VLSI的飞速发展特别是SOC的出现,产生了混合信号测试的概念。

IDDQ测试技术及其实现方法Iddq testing techniqure and its implementation谭超元 钟征宇(电子部五所 广州1501信箱05分箱 510610)摘要:IDDQ(即静态电源电流)测试是近几年来国外比较流行的CMOS集成电路测试技术。

IDDQ测试能够检测出传统的固定值故障电压测试(即SAF功能测试)所无法检测的CMOS集成电路内部的缺陷(如氧化层短路,穿通等),所以,能够明显提高CMOS集成电路的使用可靠性。

本文叙述了IDDQ测试的基本原理和IDDQ测试在集成电路测试系统上的实现方法及测试实例。

主题词:IDDQ 电流测试 CMOS 缺陷 可靠性1 前 言IDDQ测试技术是在CMOS集成电路静态功耗电流参数测试的基础上发展来的一种测试技术,它将电流测试与电压测试有机地结合在一起,大大提高了故障覆盖率[1]。

然而,由于电流测试的速度远远低于电压测试的速度,如果对大规模CMOS集成电路的每一个功能测试向量都进行一次IDDQ测试,将需要很长的测试时间。

为了使IDDQ 测试技术实用化,缩短IDDQ测试的时间, 1990年前后国外在精简IDDQ测试向量的IDDQ测试算法研究方面和提高IDDQ测试的速度和精度方面做了大量的工作,并取得了明显的进展,如QU IETEST能够将ID2 DQ测试向量精简到SAF功能测试向量的1%[2],而在电流检测方面已经达到15kHz-1MHz的电流检测速度,1μA的电流检测精度[3]。

21IDDQ测试原理传统的电压测试是将测试图形加到基本输入端,并在基本输出端与期望值相比较,如果结果一致,则电路合格,结果不一致,则电路不合格。

如果缺陷出现在电路内部,则必须把它“传递”到基本输出端才能被检测出来。

IDDQ是指当CMOS集成电路中的所有节点都处于静止状态时的电源电流。

IDDQ 测试与电压测试一样将测试图形加到基本输入端,与电压测试的不同之处在于它不是在基本输出端进行电压测试,而是在电源端或地端进行电流测试。

基于SCAN的IDDQ设计:新思科技基于SCAN的IDDQ设计荣海涛haitao.rong.aj@瑞萨电⼦(中国)有限公司摘要IDDQ测试在集成电路测试中是⼀种重要的⽅法。

随着集成电路SOC(System On Chip ⽚上系统)时代的到来,基于SCAN的 IDDQ⾃动测试向量⽣成成为SOC设计中IDDQ测试中常⽤的⽅法。

Synopsys Tetramax 就是可以实现基于SCAN IDDQ ⾃动测试向量⽣成的EDA⼯具之⼀。

如何利⽤EDA⼯具⽣成合适的IDDQ 测试向量是SOC测试过程中的⼀个挑战。

本⽂基于在⼯作中使⽤Synopsys Tetramax ⾃动⽣成IDDQ 测试向量的实践,介绍了基于SCAN的IDDQ 测试原理,测试电路设计,IDDQ ⾃动测试向量⽣成流程及IDDQ 测试向量验证。

在实践中证明我们所采⽤的基于 Synopsys Tetramax⼯具的 IDDQ ⾃动测试向量⽣成的流程和⽅法⽣成的IDDQ 测试向量顺利的完成SOC的IDDQ测试。

同时也证明Synopsys Tetramax 是⼀个⾮常好⽤的IDDQ ATPG EDA⼯具。

关键字:静态电流测试⾃动测试向量⽣成故障覆盖率AbstractThe IDDQ test is one of the important technologies of IC test. The SCAN IDDQ ATPG plays a significant role in the SOC IDDQ test. Synopsys Tetramax is one of the EDA tools which can realize SCAN IDDQ ATPG. How to generate good quality IDDQ pattern using EDA tool is the challenge in the SOC test.This paper is based on our IDDQ ATPG experience using Synopsys Tetramax. IDDQ ATPG theory, circuit design, ATPG design flow and verification are introduced in this paper.It has been proved that Synopsys Tetramax is a very good IDDQ ATPG EDA tool and our IDDQ pattern, which generated by Synopsys Tetramax, has good test result in our IDDQ test.Key words: IDDQ ATPG Fault Coverage1. 简介IDDQ 测试提出到现在已经有30多年了。

深亚微米工艺下芯片的IDDQ测试技术的研究及应用的开题报告一、研究背景与意义集成电路(ID)在现代社会中扮演着越来越重要的角色,它的应用已经涵盖到了生活中的各个方面。

在制造一个稳定、可靠、高质量的芯片过程中,有一个必要的步骤:IDDQ测试。

测试芯片的异常电流能够直接反映芯片制造中是否存在缺陷,因此它是保证芯片质量的重要手段。

随着技术的不断进步,芯片制造工艺已经进入了深亚微米的时代。

而在这种技术下,芯片制造面临着越来越多的挑战,比如工艺复杂、设计精度高等。

因此,针对深亚微米工艺下的IDDQ测试技术研究,对于保证芯片制造的可靠性和高性能至关重要。

本课题旨在对深亚微米工艺下芯片的IDDQ测试技术进行研究与应用,进一步完善芯片制造质量的保障措施。

二、研究内容和方案1. 研究现状及分析通过文献调研和案例分析,了解IDDQ测试技术在深亚微米工艺下的应用现状和存在的问题。

2. IDDQ测试原理及技术方案分析IDDQ测试原理和技术方案,包括测试寄存器设计、测试流程设计、测试数据分析等,提出基于深亚微米工艺下的IDDQ测试方案。

3. 芯片实验测试实验验证所提出的IDDQ测试方案,将该方案应用于芯片制造过程中。

通过测试数据的分析,对方案进行优化和改进,逐步完善芯片制造质量的保障措施。

4. 结果分析与总结对实验数据进行分析和比较,并对实验结果提出总结和对方案的改进建议,为进一步提高芯片制造质量提供参考。

三、预期成果1. 研究出深亚微米工艺下的IDDQ测试方案。

2. 对所提出的方案进行实验验证,获得实验数据并进行分析和总结。

3. 提出草案,为进一步完善芯片制造质保措施提供参考。

四、预期工作进度安排1. 第一阶段:文献调研与现状分析(一个月)。

2. 第二阶段:提出基于深亚微米工艺下的IDDQ测试方案(一个月)。

3. 第三阶段:进行芯片实验测试,并对方案进行优化和改进(两个月)。

4. 第四阶段:对实验结果进行分析与总结,并提出草案(一个月)。

iddq测试原理iddq测试原理是一种集成电路(IC)测试方法,用于检测芯片内部的电流。

它是一种零漏电流测试技术,通过检测芯片在静态状态下的电流来判断芯片的可靠性和质量。

iddq测试原理是基于CMOS(互补金属氧化物半导体)技术的电路测试方法。

CMOS电路是一种低功耗、高集成度的电路技术,广泛应用于各种集成电路中。

CMOS电路由N型MOS(NMOS)和P型MOS(PMOS)两种类型的MOSFET(金属氧化物半导体场效应晶体管)组成。

在CMOS电路中,NMOS和PMOS是互补的,当一个导通时,另一个处于截止状态。

iddq测试原理利用CMOS电路中的互补特性,通过测量芯片在静态状态下的电流来判断芯片是否正常。

在正常情况下,静态电流应该非常小,接近于零,因为CMOS电路在静态状态下是不消耗功耗的。

而当芯片存在缺陷时,例如晶体管漏电流过大、晶体管通道短路等,会导致芯片内部的电流明显增加。

iddq测试就是通过测量芯片的静态电流来检测这些缺陷。

iddq测试方法可以分为两种:全芯片iddq测试和局部iddq测试。

全芯片iddq测试是在芯片的所有输入和输出端口都关闭的情况下进行的,这样可以确保测量到的电流是芯片内部的电流。

而局部iddq测试则是在具体的电路模块上进行的,通过选择性地关闭部分输入和输出端口,可以更精确地定位电流缺陷。

iddq测试在集成电路制造过程中具有重要的意义。

它可以帮助制造商及时发现芯片的制造缺陷,提高芯片的质量和可靠性。

在芯片设计阶段,iddq测试也可以用来评估芯片的功耗和电流泄漏情况,优化电路设计。

虽然iddq测试方法简单有效,但也存在一些应用限制。

首先,iddq测试只能检测到静态电流缺陷,对于动态电流缺陷无能为力。

其次,iddq测试需要芯片处于静态状态,对于一些高速运行的芯片来说,测试过程可能会影响芯片的正常工作。

因此,在实际应用中,还需要结合其他测试方法来全面评估芯片的性能和可靠性。

总结起来,iddq测试原理是一种通过测量芯片的静态电流来检测电流缺陷的方法。

数模混合电路故障诊断方法的研究孔东明;史贤俊【摘要】With the fast development of electronic technology,the complexity of the circuit system increased sharply,more and more electric circuits include the digital and analog signal simultaneously,resulting in greater testing difficulty in circuit system and larger challenges in circuit testing.The present methods to test the electric circuits are mainly for digital or analog circuits,but testing of mixed-signal circuits is still a young field.At present,based on the developing actuality of circuits testing,the basic idea of various methods in fault diagnosis is introduced.The mixed-signed circuit fault diagnosis based on the discrete event system theory is recommended importantly.%随着电子技术的迅猛发展,电路系统的复杂程度急剧增加,越来越多的电路同时包含了数字信号和模拟信号,使得电路系统的测试难度越来越大,电路测试也因此面临着更大的挑战。

目前的电路故障方法主要还是针对数字电路和模拟电路的,但是数模混合电路的测试仍然是一个很年轻的领域。

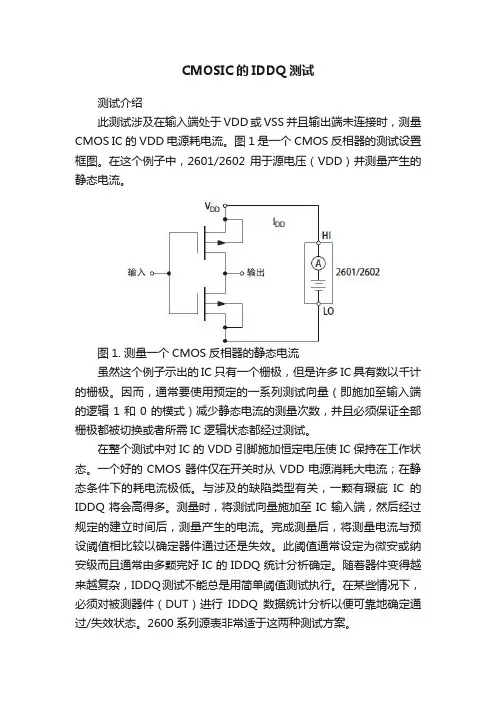

CMOSIC的IDDQ测试测试介绍此测试涉及在输入端处于VDD或VSS并且输出端未连接时,测量CMOS IC的VDD电源耗电流。

图1是一个CMOS反相器的测试设置框图。

在这个例子中,2601/2602用于源电压(VDD)并测量产生的静态电流。

图1. 测量一个CMOS反相器的静态电流虽然这个例子示出的IC只有一个栅极,但是许多IC具有数以千计的栅极。

因而,通常要使用预定的一系列测试向量(即施加至输入端的逻辑1和0的模式)减少静态电流的测量次数,并且必须保证全部栅极都被切换或者所需IC逻辑状态都经过测试。

在整个测试中对IC的VDD引脚施加恒定电压使IC保持在工作状态。

一个好的CMOS器件仅在开关时从VDD电源消耗大电流;在静态条件下的耗电流极低。

与涉及的缺陷类型有关,一颗有瑕疵IC的IDDQ将会高得多。

测量时,将测试向量施加至IC输入端,然后经过规定的建立时间后,测量产生的电流。

完成测量后,将测量电流与预设阈值相比较以确定器件通过还是失效。

此阈值通常设定为微安或纳安级而且通常由多颗完好IC的IDDQ统计分析确定。

随着器件变得越来越复杂,IDDQ测试不能总是用简单阈值测试执行。

在某些情况下,必须对被测器件(DUT)进行IDDQ数据统计分析以便可靠地确定通过/失效状态。

2600系列源表非常适于这两种测试方案。

测试系统配置图2是面向CMOS IC,基于2600系列的IDDQ测试系统。

图2. IDDQ测试系统配置如图2所示,260X的HI和LO端子连至CMOS IC的VDD和VSS端子。

在整个测试过程中,260X为IC提供恒定的直流电压。

IC 的输入端连至“数字测试系统”,这确保切换了全部栅极或实现了要求的逻辑状态。

假设此测试系统还控制着机械位置、DUT探测和处置好/坏器件。

对260X的控制可以像标准可编程仪器那样,通过IEEE-488总线(GPIB)或者RS-232发送独立指令实现。

260X上的这两种通信接口都是标准的。

电流测试1 电流测试简介功能测试是基于逻辑电平的故障检测,逻辑电平值通过测量原始输出的电压来确定,因此功能测试实际上是电压测试.电压测试对于检测固定型故障特别是双极型工艺中的固定型故障是有效的,但对于检测CMOS 工艺中的其他类型故障则显得有些不足,而这些故障类型在CMOS 电路测试中是常见的对于较大电路,电压测试由于测试图形的生成相当复杂且较长,因而电流测试方法被提出来电流测试的测试集相当短,这种测试方式对于固定型故障也有效.CMOS 电路具有低功耗的优点,静态条件下由泄漏电流引起的功耗可以忽略,仅表示,Q 代表静态在转换期间电路从电源消耗较大的电流。

电源电压用VDD(quiescent) ,则IDDQ 可用来表示MOS电路静态时从电源获取的电流,对此电流的测试称为IDDQ 测试,这是一种应用前景广泛的测试。

IDDQ 测试概念的提出时间并不很长,但自半导体器件问世以来,基于电流的测量一直是测试元器件的一种方法,这种方法即所谓的IDDQ 测试,用在常见的短接故障检测中。

自从Wanlsaa 于1961 年提出CMOS 概念, 1968 年RCA 制造出第一块CMOS IC 和1974 年制造出第一块MOS 微处理器以来,科研人员一直研究CMOS 电路的测试,而静态电流测试则作为一项主要的参数测量1975 年Nelson 提出了IDDQ 测试的概念和报告,1981 年M.W Levi 首次发表了关于VLSI CMOS 的测试论文,这就是IDDQ 测试研究的开端。

其后,IDDQ 测试用来检测分析各种DM0S 缺陷,包括桥接故障和固定型故障1988 年W.Maly 首次发表了关于电流测试的论文, Levi, Malaiya, C。

Crapuchettes, M.Patyra , A .Welbers 和S。

Roy等也率先进行了片内电流测试的研究开发工作,这些研究奠定了IDDQ 测试的基础、1981 年Philips semiconductor 开始在SRAM 产品测试中采用片内IDDQ 检测单元,其后许多公司把片内IDDQ 检测单元用在ASIC产品中,但早期的IDDQ 测试基本上只为政府、军工资助的部门或项目所应用。

.DC参数测试摘要本章节我们来说说DC参数测试,大致有以下内容,⏹欧姆定律等基础知识⏹DC测试的各种方法⏹各种DC测试的实现⏹各类测试方法的优缺点基本术语在大家看DC测试部分之前,有几个术语大家还是应该知道的,如下:Hot Switching 热切换,即我们常说的带电操作,在这里和relay(继电器)有关,指在有电流的情况下断开relay或闭合relay的瞬间就有电流流过(如:闭合前relay两端的电位不等)。

热切换会减少relay的使用寿命,甚至直接损坏relay,好的程序应避免使用热切换。

Latch-up 闩锁效应,由于在信号、电源或地等管脚上施加了错误的电压,在CMOS器件内部引起了大电流,造成局部电路受损甚至烧毁,导致器件寿命缩短或潜在失效等灾难性的后果。

BinningBinning(我很苦恼这玩意汉语怎么说——译者)是一个按照芯片测试结果进行自动分类的过程。

在测试程序中,通常有两种Binning的方式——hard binning 和soft binning. Hard binning控制物理硬件实体(如机械手)将测试后的芯片放到实际的位置中去,这些位置通常放着包装管或者托盘。

Soft binning控制软件计数器记录良品的种类和不良品的类型,便于测试中确定芯片的失效类别。

Hard binning的数目受到外部自动设备的制约,而Soft binning的数目原则上没有限制。

下面是一个Binning的例子:Bin# 类别01 100MHz下良品02 75MHz下良品10 Open-Short测试不良品11 整体IDD测试不良品12 整体功能测试不良品13 75MHz功能测试不良品14 功能测试VIL/VIH不良品15 DC测试VOL/VOH不良品16 动态/静态IDD测试不良品17 IIL/IIH漏电流测试不良品从上面简单的例子中我们可以看到,Hard bin 0,Soft bin 01-02是良品,是我们常说的GoodBin;而Hard bin 1,Soft bin 10-17是不良品,也就是我们常说的FailedBin。

CMOS 电路IDDQ 测试电路设计

引言

测试CMOS 电路的方法有很多种,测试逻辑故障的一般方法是采用逻辑响应测试,即通常所说的功能测试。

功能测试可诊断出逻辑错误,但不能检查出晶体管常开故障、晶体管常闭故障、晶体管栅氧化层短路,互连桥短路等物理缺陷引发的故障,这些缺陷并不会立即影响电路的逻辑功能,通常要在器件工作一段时间后才会影响其逻辑功能。

功能测试是基于逻辑电平的故障检测,通过测量原始输出的电压来确定逻辑电平,因此功能测试实际上是电压测试。

电压测试对于检测固定型故障,特别是双极型工艺中的固定型故障是有效的,但对于检测CMOS 工艺中的其他类型故障则显得有些不足,而这些故障类型在CMOS 电路测试中却是常见的。

对于较大规模电路,电压测试测试集的生成相当复杂且较长,需要大量的实验数据样本。

IDDQ 测试是对功能测试的补充。

通过测试静态电流IDDQ 可检测出电路中的物理缺陷所引发的故障。

华宇测试机:诚质-TQT500,长川CTA-8200,Accoust-8107,友能-DTS1000测试项目:OS<输入电流量电压>漏电流<IiL,IiH>电源电流IDD AC/DC Function Spd读写ViH ViL IOH IOL VOH VOL IiH IiLFT测试:测试向量(核心)和真值表(侦错错误能力能被计算出来,且涵盖错误的范围)会在输入端输入资料,送入DUT,检查输出脚的电压、时序、逻辑状态来判断测试结果是PASS or Fail从PE上的driver输入资料;从比较器输出资料功能测试包含两种不同的组合:测试向量和测试主程式中的指令;测试向量包括DUT的输入输出的逻辑状态;测试主程式包括控制硬体的资讯,创造出所需要电压、时序、波形等。

Test Vector(真值表)提供DUT的输入输出逻辑状态0 输入逻辑低 1 输入逻辑高Driver on 比较器off L 输出逻辑低H 输出逻辑高Driver off 比较器on Z 输出高阻抗X没有输入驱动Driver off 比较器on 定义测试周期输入资料:包括测试向量资料,输入讯号格式,输入讯号时序,V iL/V iH输入准位与时间设定选择最简单的输入资料为0 1输入讯号的格式:允许保证所有的AC参数被测试到,定义出输入DUT的讯号波形;讯号的格式有很多种输入讯号分为控制讯号与资料讯号;先决定好周期时间,再决定控制讯号的边沿触发的位置,决定控制讯号在一个周期的位置,设定资料讯号的保持时间,再定义讯号的格式;控制讯号决定资料讯号的读取或栓锁在锁存器中时间,资料讯号提供资料;时钟脉冲通常为RZ/RO;高动作控制讯号为RZ;低动作为RO;准备时间与保持时间用SBC;其他可用NRZ 或DNRZ格式输出资料:包括测试向量资料、输出抓取时间、V ol/V oh、I ol/I oh若输出电压在V ol与V oh之间,则判定Fail然而在高阻抗状态Z,输出电压在V ol与V oh之间则判定为PASS在功能测试中,电流负载施加一定的电流给输出端口,I ol/I oh电流,来测试V ol/V oh要注意输出时间应和测试时间在同一个周期内完成,并要确定输出时间在测试周期结束之前有足够的时间传输出来测试向量可改变DUT脚位从输入变成输出切换,被罩住的输出脚,不管其输出是在一个什么样的状态,也可忽略PASS或FAil的结果;当一个DUT的输出脚位逻辑状态是确定的,则可以被测试。

哇哈哈PMSM 参数测量实验测量永磁同步电机定子电阻、交轴电感、直轴电感、转子磁链以及转动惯量。

1. 定子电阻的测量采用直流实验的方法检测定子电阻。

通过逆变器向电机通入一个任意的空间电压矢量U i (例如U 1)和零矢量U 0,同时记录电机的定子相电流,缓慢增加电压矢量U i 的幅值,直到定子电流达到额定值。

如图1所示为实验的等效图,A 、B 、C 为三相定子绕组,U d 为经过斩波后的等效低压直流电压。

I d 为母线电流采样结果。

当通入直流时,电机状态稳定以后,电机转子定位,记录此时的稳态相电流。

因此,定子电阻值的计算公式为:1,2a d b c d I I I I I ===- (1) 23d s d U R I = (2)图1 电路等效模型2. 直轴电感的测量在做直流实验测量定子电阻时,定子相电流达到稳态后,永磁转子将旋转到和定子电压矢量重合的位置,也即此时的d 轴位置。

测定定子电阻后,关断功率开关管,永磁同步电机处于自由状态。

向永磁同步电机施加一个恒定幅值,矢量角度与直流实验相同的脉冲电压矢量(例如U 1),此时电机轴不会旋转(ω=0),d 轴定子电流将建立起来,则d 轴电压方程可以简化为:d d d q q d di u Ri L i L dt ω=-+d d d d di u Ri L dt =+ (3)对于d 轴电压输入时的电流响应为:()(1)d R t L U i t e R -=- (4) 利用式(4)以及测量得到的定子电阻值和观测的电流响应曲线可以计算得到直轴电感值。

其中U /R 为稳态时的电流反应,R 为测得的电机定子电阻。

由上式可知电流上升至稳态值的0.632倍时,1dRt L -=-,电感与电阻的关系式可以写成:0.632d L t R =• (5) 其中t 0.632为电流上升至稳态值0.632倍时所需的时间.3. 交轴电感的测量测出L d 之后,在q 轴方向(d 轴加90°)施加一脉冲电压矢量。

电流测试1电流测试简介功能测试是基于逻辑电平的故障检测,逻辑电平值通过测量原始输出的电压来确定,因此功能测试实际上是电压测试。

电压测试对于检测固定型故障特别是双极型工艺中的固定型故障是有效的,但对于检测CMOS工艺中的其他类型故障则显得有些不足,而这些故障类型在CMOS电路测试中是常见的对于较大电路,电压测试由于测试图形的生成相当复杂且较长,因而电流测试方法被提出来电流测试的测试集相当短,这种测试方式对于固定型故障也有效。

CMOS电路具有低功耗的优点,静态条件下由泄漏电流引起的功耗可以忽略,仅在转换期间电路从电源消耗较大的电流。

电源电压用V DD表示,Q代表静态(quiescent),则IDDQ可用来表示MOS电路静态时从电源获取的电流,对此电流的测试称为IDDQ测试,这是一种应用前景广泛的测试。

IDDQ测试概念的提出时间并不很长,但自半导体器件问世以来,基于电流的测量一直是测试元器件的一种方法,这种方法即所谓的IDDQ测试,用在常见的短接故障检测中。

自从Wanlsaa于1961年提出CMOS概念,1968年RCA制造出第一块CMOSIC和1974年制造出第一块MOS微处理器以来,科研人员一直研究CMOS电路的测试,而静态电流测试则作为一项主要的参数测量1975年Nelson提出了IDDQ测试的概念和报告,1981年M.WLevi 首次发表了关于VLSICMOS的测试论文,这就是IDDQ测试研究的开端。

其后,IDDQ测试用来检测分析各种DM0S缺陷,包括桥接故障和固定型故障1988年W.Maly首次发表了关于电流测试的论文,Levi,Malaiya,C.Crapuchettes,M.Patyra,A.Welbers和S.Roy等也率先进行了片内电流测试的研究开发工作,这些研究奠定了IDDQ测试的基础、1981年Philipssemiconductor开始在SRAM产品测试中采用片内IDDQ检测单元,其后许多公司把片内IDDQ检测单元用在ASIC产品中,但早期的IDDQ 测试基本上只为政府、军工资助的部门或项目所应用。

直到20世纪80年代后期,半导体厂商认识到IDDQ测试是检测芯片物理缺陷的有效方法,IDDQ测试才被普遍应用,CAD工具也开始集成此项功能。

目前,IDDQ测试也逐渐与其他DFT结构,例如扫描路径测试、内建自测试、存储器测试等,结合在一起应用。

20世纪80年代,电流测量基本上是基于片外测量电路的,80年代末片上电流传感器的理论和设计方法得以提出,随后这方面所开展的理论和方法研究纷纷出现,IEEETechnicalCommitteeonTestTechnology于1994年成立一个称做QTAG(QualityTestActionGroup)的技术组织,其任务是研究片上电流传感器的标准化问题,但该组织得出了电流传感器不经济的结论,因此,1996年结束标准化研究工作,目前电流传感器的研究主要针对高速片外传感器。

IDDQ测试是源于物理缺陷的测试,也是可靠性测试的一部分1996年SRC (SemiconductorResearchCorporation)认定IDDQ测试是20世纪90年代到21世纪主要的测试方法之一。

IDDQ测试已成为IC测试和CAD工具中一个重要内容,许多Verilog/HDL模拟工具包含IDDQ测试生成和故障覆盖率分析的功能。

IDDQ测试引起重视主要是测试成本非常低和能从根本上找出电路的问题(缺陷)所在。

例如,在电压测试中,要把测试覆盖率从80%提高10%,测试图形一般要增加一倍,而要从95%每提高一个百分点,测试图形大约要在前面的基础上提高一倍,但若在电压测试生成中加入少量的IDDQ测试图形,就可能达到同样的效果。

另外,即使电路功能正常,IDDQ测试仍可检测出桥接、短路、栅氧短路等物理缺陷。

但是IDDQ测试并不能代替功能测试,一般只作为辅助性测试。

IDDQ测试也有其不足之处,一是前面提到的需要选择合适的测量手段,二是对于深亚微米技术,由于亚阂值元件的增加,静态电流已高得不可区分。

IDDQ测试的原理就是检测CMOS电路静态时的漏电流,电路正常时静态电流非常小(nA级),而存在缺陷时(如栅氧短路或金属线短接)静态电流就大得多如果用IDDQ法测出某一电路的电流超常,则意味着此电路可能存在缺陷。

图1以CMOS反相器中栅氧短路和金属线桥接形成的电流通道为例,对这一概念进行了进一步阐述对于正常的器件,因制造工艺的改变或测量的不准确,也可能得出IDDQ电流过大的判断,这种情况应先予以排除。

图1CMOS反向器中形成的电流通道虽然IDDQ的概念比较直观,但对于VLSI而言,IDDQ测试并不简单,关键问题是如何从量值上区分正常电路的电流和有缺陷电路的电流。

1996年WillamsT.E.提出了用静态电流分布来区分电路“好坏”的概念,采用静态电流分布曲线来描述,如图2所示。

图2左半部分是正常的CMOS反相器的静态电流分布曲线,其均值为Mg,右半部分是有缺陷的CMOS反相器的静态电流分布曲线,其均值为Md。

如果Mg和Md的差值比较大,就可以比较容易地选择一个静态电流上限值来区分电路的“好坏”。

区分开正常电路的电流和有缺陷电路的电流限值,不但与电路的设计参数、制造工艺有关,还与电流的测试手段有关。

图2IDDQ值的典型分布2IDDQ测试机理2.1基本概念一个数字IC可能包含上百万个晶体管,这些晶体管形成不同的逻辑门,不管这些门电路形式和实现功能如何,都可以把它们用一个反相器的模型来表达。

首先研究CMOS反相器及其在有故障和无故障条件下的转换电流,在输入电压从O转换到VDD的过程中,PMOS管会由导通转换为截止,而NMOS管则会从截止转换为导通,但在转换时间tf内,栅极所具有的电压会使两管同时导通,也正是在这段时间内电源和地回路中形成比较大的电流,对其用SPICE模拟所得的波形如图3所示图3CMOS反相器转换电流的SPICE模拟图4绘出0.6um工艺,NMOS管W=L=0.6um,PMOS管W=2.5um、L=0.6um的CMOs反相器的SPICE模拟图。

上部分图形是CMOS反相器无故障时输入电压Vgs和电源电流的SPICE模拟图,下部分图形是有故障时(输入输出短接)输入电压和电源电流的SPICE模拟图。

从此图中可以看出,对于有故障的电路,当输入电压Vgs为高电平时,电源电流维持在一固定的、比较大的值,这是因为输出经NMOS拉低到地电平。

但当输入电压Vgs=0时,PMOS导通,而NMOS也固定在输入端,因此地与电源之间就有稳定的电流,此电流比正常的反相器的转换电流要大得多。

显然,通过观察电源电流的大小就可区分器件的正常与否。

图4无故障时和有故障时CMOS反相器的SPICE模拟图IDDQ测试与有故障的门在电路中的位置无关,因此不必像电压测试那样把故障传播到原始输出。

一般情况下,给CMOS电路施加测试图形后,其中的门不止一个进行状态转换,这此转换过程可能是同时完成,也可能非同时完成,这种情况下必须等到所有的门都转换结束后才可进行电流测试。

如图5所示的NAND电路树,a=b=c=d=1,当s从低电平转换到高电平时,最左边的NAND门先转换,最右边的门最后转换,因此在最右边的门还未转换完毕前进行的电流测量肯定是不准确的,也就不能很好地进行故障分析。

图5NAND电路树2.2无故障电路的电流分析CMOS反相器的转换电流由Ids决定(1)式中(2)以上两式中,是MOS器件的电导系数,和分别是介电常数和栅氧厚度,是载流子迁移率,和分别是沟道宽度和长度,k分别代表N沟道和P沟道。

由式(1)可以看出,当Vds=Vgs-Vt时转换电流最大,因为这种情况下电源和地之间存在一个电流直接导通路径,此时的电流也远远大于静态电流。

当晶体管不处于转换过程时,其中之一处于导通状态,而另一个处于截止状态,实际上可能处于亚阈电流状态,而不是完全截止。

当MOS管的尺寸缩小到亚微米以下时,按比例下降的阈值电压和短沟道效应会使亚阈电流增大,这个因素以及芯片上集成管的增加,会使无故障器件的IDDQ值增加。

图6表示栅长与IDDQ的关系。

表1列出了不同工艺下的IDDQ值。

图6栅长与IDDQ的关系表1不同工艺下的IDDQ值实际上的静态电流是所有处于截止状态的晶体管的电流之和,研究表明此电流与晶休管的数目有关系,表2列出了IDDQ的典型值。

表2IDDQ的典型值2.3转换延迟虽然MOS管一般可以当做转换管使用,但其导通或截止不是即时的,而是有一段延迟时间。

造成延迟的主要原因,一是每个逻辑门的负载是一容性负载,后一级的输入端或输出端需经过一定时间的充、放电才能使容性负载上的电压达到稳定,二是MOS沟道的形成和关闭也需一定的时间。

容性负载C上的电压认流过的电流i及切换时间t之间的关系为:(3)式中,为负载上的电压从V1切换到V2所用的时间。

当负载上电压从低电平值转换到高电平值时,通过P沟道充电;当负载上电压从高电平值转换到低电平值时,通过N沟道放电;根据Vl和V2值,可以定义不同的延迟时间,主要有:-高到低延迟时间(thl);-低到高延迟时间(tlh);-上升时间(tr);-下降时间(tf);-延迟时间(td);关于这些时间的定义及其图形描述可参考有关资料。

3IDDQ测试方法IDDQ的测试是基于静态电流的测试,在每一个IDDQ测试图形施加后再等待一段时间才进行测量,因此其测试速度比较慢。

进行IDDQ测试的必要条件是:状态切换所造成的电流“火花”必须消失掉,另外考虑电流测量设备也需一定的等待时间一般来说,测试生成完成以后,IDDQ测试基本的过程是:(l)测试图形施加;(2)等待瞬变过程消失;(3)检查静态IDDQ是否超过阈值。

电流测量可以在芯片外部进行,也可以在芯片内部进行。

在芯片内部进行的IDDQ测量一般是同内建自测试结构结合在一起的。

电流测量的难处在于测试结构可能对被测量的数值有影响,因此应采取措施排除此影响。

为了正确进行电流测量,有以下要求:-在电源引出线端所接的旁路电容和CUT之间,容易布置测量结构;-能够测量小的静态电流;-测量不致引起电源电压几十微伏的变化;-快速测试―每一个测试图形下测试时间小于5O0ns。

3.1片外测试片外测试是常用的电流测量方法,其原理如图7所示。

在这种结构中,供电电源端增加一旁路电容,原因是受到CMOS中比较大的转换电流以及封装的限制,会在电源和地回路间造成比较大的涌流,此电容具有抑制涌流作用。

如果涌流比较大,会淹没静态电流,必须等到瞬变过程完毕后才可进行电流测量。

图7电流测试方法示意图片外电流测量的方案可分为直流和交流两种,分别见图7(a)和图7(b)。

最基本的问题是测量探头所引入的电感问题(典型值是10-50nH),对于100A/nS的尖脉冲电流,10nH的探头可造成100V的电压降,因此这样的探头不可用。