11 12 -Verilog的可综合描述风格

- 格式:pdf

- 大小:516.38 KB

- 文档页数:77

Unit1V ocabulary41.他们利用我们求助无门的困境把我们公司接管了。

They took advantage of our hopeless situation and took over our company.2.虽然我们前面仍有困难,但我肯定我们中国人有智慧靠自己实现国家的和平统一。

Although there are still difficulties lay ahead of us, I’m sure that we Chinese people have the wisdom to bring about the peaceful unification of our country on our own.3.只强调国内生产总值是错误的,它会引起很多严重的问题。

It is wrong to stress/emphasize/put emphasis on GDP. It will bring about/give rise to many serious problems.4.他喜欢炫耀他的财富,但这完全是徒劳的,人们仍然像躲避毒药那样躲他。

He loves to show off his wealth, but that is all in vain. People still avoid him as he were poison.5.他不久就爱上了这个村子。

他决心和村名一起把这个地方变成一个花园。

He soon fell in love with the village and was determined to make it a beautiful garden together with the villagers.6.我们必须花更多的钱来和全球气温上升作斗争。

另外,我认为我们应该采取严厉的法律措施。

这不是一个钱的问题。

We must spend much more money fighting against global warming. In addition, we must resort to tough laws. It is not just a matter of money.7.当警察到达学校的时候,学生和教师还在一种茫然不知所措的状态。

数字11代表什么是什么意思11这个数字是2位数中最小的奇数、质数。

但在其他领域中,11的含义也是不同的。

今天,店铺为大家整理了数字11的含义。

数字11的含义在数学中的,11的进制是1011,八进制是13,十六进制是B;它是最小的循环单位质数,是一个简单的阿拉伯数字;在数字中,除了1和11外,如果各个位数的数字都是1,那么这个数字如果位数是2的倍数(例如1111是4位数、111111是6位数等),均为合数。

因为它们都能被11整除;在化学中,钠的院子序数是11。

在欧洲,数字11是魔鬼的数字,圣奥古斯丁认为11刚好比象征完美的10多出一点,因此常和危险、冲突和反叛联系在一起,但在非洲的萨满教巫师们娿认为11是一个吉祥的数字,是多产和富饶的象征。

从易经数理来说,11的含义是如草木受春光,慈雨沾恩萌芽,伸长枝叶渐渐茂荣,乃阴阳重新和合,天赋幸运,万事顺利,有得富贵荣誉再兴家的暗示,得挽回家运平静和顺的最大吉数。

在基业方面:财星、天佑、暗禄、文昌、技艺、田宅;家庭方面:家庭:养蜂结蜜,事事和顺,处处温和;健康方面:健康:河川永在,可望健康长寿。

梦见写数字十一的代表含义梦见写数字十一,这两天外出运很旺,不要再窝在室内了。

志同道合的朋友有机会再进一步发展。

外出开销大,让你心理也有点压力。

找人一同合作会为你带来好运。

上学的人梦见写数字十一,意味着文科成绩欠理想,要录取应多加努力。

做生意的人梦见写数字十一,代表行情价涨,利小,先损后得,从新整顿营业。

恋爱中的人梦见写数字十一,说明眼光看远些,人无十全十美,互相体谅,婚姻可成。

本命年的人梦见写数字十一,意味着先苦后甘,付出辛劳的代价,往后回收。

慎防官讼。

怀孕的人梦见写数字十一,预示生女,冬占生男。

慎防动胎流产。

出行的人梦见写数字十一,建议延后出发,有风。

梦见写数字十一,按周易五行分析,幸运数字是7,桃花位在正西方向,财位在西北方向,吉祥色彩是紫色,开运食物是青菜。

就在今天,全球华人世界里大约有9077人跟你一样也梦见写数字十一。

小学一年级数学上《11—20各数的认识》教学反思作为一名人民老师,课堂教学是我们的任务之一,对学到的教学技巧,我们可以记录在教学反思中,快来参考教学反思是怎么写的吧!下面是小编收集整理的小学一年级数学上《11—20各数的认识》教学反思,仅供参考,大家一起来看看吧。

小学一年级数学上《11—20各数的认识》教学反思篇111~20各数的认识这一内容的教学,我认为应重视学生的生活经验和已有的知识,并把这份经验作为教学的起点。

在这节课里,学生已基本上能数出数量在11~20之间的物体个数,读数,数的顺序和大小,因此确定这节课重点辅导直观地了解11~20各数都是由一个十和几个一组成的,以及灵活运用所学知识解决实际问题,发展学生的数感。

建构主义学习理论认为学生已有知识和经验对建构新知识起着重要作用。

在上面的教学设计中,力求从学生熟悉的生活情境中提出有关的数学问题。

我班学生中午由路队长带领下排队回家,每天放学,班主任老师领着他们排队出校门,穿过马路,这是多么熟悉的情景啊,一下子激发了学生的兴趣,使学生感受到数学与日常生活的密切联系。

小学一年级的思维以具体形象思维为主,学生的学习要通过大量的操作活动,使所学的新知识不断内化到已有的认知结构中,因此本节课特别注重使学生通过操作(摆小棒)进行学习活动,促进独立思考以及在小组中的合作与交流。

重视培养学生应用数学的意识和能力。

教师应该引导学生把所学的数学知识应用到现实中去,以体会数学在现实生活中的应用价值。

平时我发现我班学生在翻书时速度较慢,一页一页地翻,有的甚至不知往前还是往后。

学了20以内数的顺序后,让学生翻翻书,根据数的顺序来确定往哪边翻;体验一下10张、20张的厚度增强数感来确定大概还要翻多厚增快翻书的速度。

小学一年级数学上《11—20各数的认识》教学反思篇211—20各数的认识,它既是10以内数的认识和延续,又是100以内乃至更大的数的认识的基础,同时也为20以内的进位加法的学习打下算理基础。

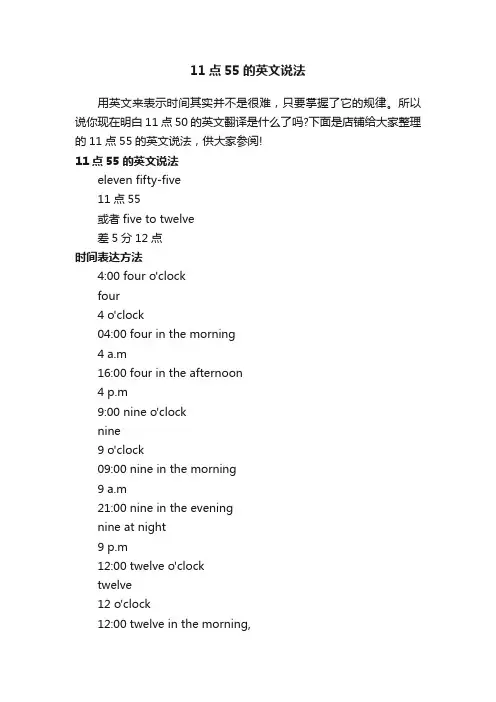

11点55的英文说法用英文来表示时间其实并不是很难,只要掌握了它的规律。

所以说你现在明白11点50的英文翻译是什么了吗?下面是店铺给大家整理的11点55的英文说法,供大家参阅!11点55的英文说法eleven fifty-five11点55或者five to twelve差5分12点时间表达方法4:00 four o'clockfour4 o'clock04:00 four in the morning4 a.m16:00 four in the afternoon4 p.m9:00 nine o'clocknine9 o'clock09:00 nine in the morning9 a.m21:00 nine in the eveningnine at night9 p.m12:00 twelve o'clocktwelve12 o'clock12:00 twelve in the morning,12 a.mmidday00:00 twelve at night12 p.mmidnight12:15,00:15 a quarter past twelvequarter past twelvetwelve fifteena quarter after twelve02:25,14:25 twenty-five past two twenty-five minutes past twotwo twenty-fivetwenty-five after two11:30,23:30 half past eleveneleven-thirtyhalf elevenhalf after eleven12:45,00:45 a quarter to onequarter to onetwelve forty-five07:50,19:50 ten to eightten minutes to eightseven fifty表达时间英语例句What time is it, Gordon? 几点了,戈登?Just after five. 刚过5点。

11月12号是什么节日孙中山(1866.11.12~1925.3.12),中国近代民主革命的伟大先行者。

每年的11月12日便是孙中山先生诞辰纪念日。

下面由店铺给大家整理了11月12月是什么节日相关知识,希望可以帮到大家!11月12月是孙中山诞辰纪念日孙中山(1866.11.12~1925.3.12),本名孙文,谱名德明,字载之,号日新,又号逸仙,幼名帝象,广东中山人,中国近代民主革命的伟大先行者。

每年的11月12日便是孙中山先生诞辰纪念日。

孙中山诞辰纪念日基本介绍孙中山(1866.11.12~1925.3.12),本名孙文,谱名德明,字载之,号日新,又号逸仙,幼名帝象,广东中山人,中国近代民主主义革命先驱,中华民国和中国国民党创始人,三民主义的倡导者。

首举彻底反封建的旗帜,“起共和而终帝制”。

1905年成立中国同盟会。

1911年辛亥革命后被推举为中华民国临时大总统。

1929年6月1日,根据其生前遗愿,陵墓永久迁葬于南京钟山中山陵。

1940年,国民政府通令全国,尊称其为“中华民国国父”。

他是一位在海峡两岸都受到敬重的革命家,中国国民党尊其为,中国共产党尊称孙中山为“中国近代民主革命的伟大先行者”。

每年的11月12日便是孙中山先生诞辰纪念日。

[1]孙中山诞辰纪念日相关习俗与活动每年的孙中山先生诞辰日,全国各地都会开展各种活动纪念孙中山诞辰。

南京建有孙中山纪念馆。

2013年11月12日,全国政协在北京中山公园中山堂举行仪式,纪念中国民主革命的伟大先行者孙中山先生诞辰147周年。

孙中山诞辰纪念日补充毛泽东主席在《纪念孙中山先生》一文中,高度地评价了孙中山先生的一生。

他说:孙中山是“中国革命民主派的旗帜”,强调纪念他在辛亥革命时期,领导人民推翻帝制建立共和国的丰功伟绩。

纪念他在第一次国共合作时期,把旧三民主义发展为新三民主义的丰功伟绩。

毛泽东:“将来我们的力量越大,我们就越要孙中山,就越有好处,没有坏处。

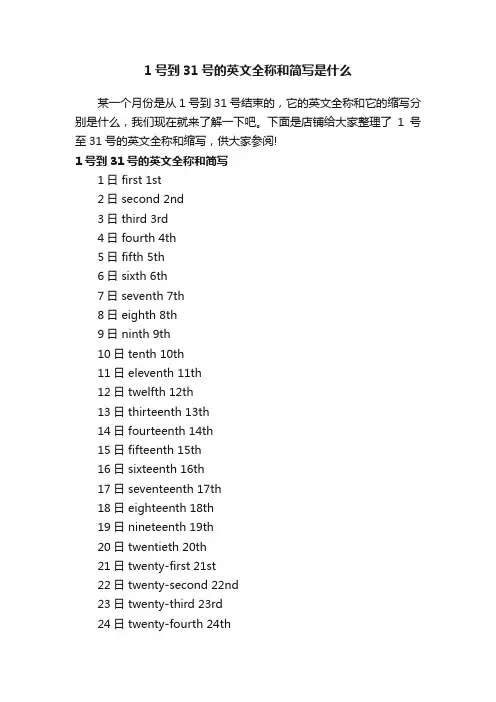

1号到31号的英文全称和简写是什么某一个月份是从1号到31号结束的,它的英文全称和它的缩写分别是什么,我们现在就来了解一下吧。

下面是店铺给大家整理了1号至31号的英文全称和缩写,供大家参阅!1号到31号的英文全称和简写1日 first 1st2日 second 2nd3日 third 3rd4日 fourth 4th5日 fifth 5th6日 sixth 6th7日 seventh 7th8日 eighth 8th9日 ninth 9th10日 tenth 10th11日 eleventh 11th12日 twelfth 12th13日 thirteenth 13th14日 fourteenth 14th15日 fifteenth 15th16日 sixteenth 16th17日 seventeenth 17th18日 eighteenth 18th19日 nineteenth 19th20日 twentieth 20th21日 twenty-first 21st22日 twenty-second 22nd23日 twenty-third 23rd24日 twenty-fourth 24th25日 twenty-fifth 25th26日 twenty-sixth 26th27日 twenty-seventh 27th28日 twenty-eighth 28th29日 twenty-ninth 29th30日 thirtieth 30th31日 thirty-first 31st1号的英语例句1. In 1957, the Soviets launched Sputnik 1 into outer space.1957年,苏联人将“斯普特尼克1号”人造卫星送入了外层空间。

2. Open 1 April to 31 October incl.从4月1号到10月31号每天营业。

3. On 1 October the US suspended a proposed $574 million aid package for 1991. Of this amount, $250 million is for military purchases.10月1号,美国暂停了拟议中的一项1991年度总计5.74亿美元的一揽子援助方案,这其中有2.5亿美元是用于军事采购的。

神盾11第一季第11集科尔森被蜈蚣组织带走,蜈蚣组织为了得到关于他死而复生的原因,将它带到沙漠之中进行拷问与实验。

在科尔森被抓走后,神盾局上下对科尔森实行了大营救。

在其过程中,斯凯被特工汉德赶下了飞机,而正是这契机,斯凯在城市中假扮成特工梅,“威逼”一个大富豪给予帮助,并找到了蜈蚣组织的交易记录,从而找到了科尔森的确定位置。

特别行动小组在得到了斯凯的消息后,赶忙前往荒漠之中营救科尔森。

与此同时,科尔森正在被波先生拷打,企图逼迫他使用恢复记忆的机器,而在长时间的拷打未得效果后,千里眼对波的能力失去信心,蕾娜与千里眼通话中,千里眼指示蕾娜取代波的位置并将其杀死,,蕾纳对科尔森进行“糖衣炮弹”。

在她的富有诱惑力的话语下,抓住了科尔森也想要知道答案的弱点使科尔森自愿使用了机器。

在他的回忆中,他看见自己在手术室,脑壳被割了开来,许多的机器爪在他的脑子里刺来刺去。

看到如此景象他痛苦的大喊:“Let me die(让我死)”随后,特别行动小组赶来,将痛苦中的科尔森给救了回去并且逮捕了蕾纳。

在神盾局的全力围捕下,大部分的蜈蚣组织土崩瓦解,但千里眼仍然逍遥在外。

事后,科尔森找到了给他做手术的博士,博士只得将事实告诉了科尔森。

原来,在纽约事件之后,科尔森已经死去了许多天,但弗瑞局长把他从天堂拉回了人间,通过不断的手术将科尔森给救了回来。

而为了他还能恢复最佳的工作水平,不再痛苦,给他植入了一段在塔希提的美好记忆。

听完这番话,科尔森愤然离去。

尾声,皮特森醒来,发现自己浑身是伤,掀开盖在身上的被子,发现自己已成残废,在他大声呼喊之时,他的“眼球”中出现了几个字:早上好,皮特森先生。

Episode 11 First QuarterColson was taken away centipede organization , centipede organizations in order to get him back from the dead on the reason , it would be torture to the desert with the experiment. Colson was arrested after Aegis Bureau Colson implemented and down on the big rescue. In the process , the agents Hande Skye was driven off the plane , and it is this opportunity, Skye posing as agents plum in the city, " coercion" a big spender for help, and found the transaction centipede organization in order to determine the position of Colson 's found . Special Operations Group in Skye got the news , rushed to the rescue of the desert into Colson . At the same time , Mr. Colson wave being tortured in an attempt to force him to use the recovered memory of the machine, but after prolonged torture,without effect , clairvoyance lose confidence in the ability of the wave , Lena conversation with clairvoyance , clairvoyance instructions Lena replace the position of wave and kill , Leina on Colson a " sugar-coated bullets ." In the words of her tempting and grabbed Colson also want to know the answer weaknesses Colson voluntarily make use of the machine . In his memories, he saw himself in the operating room, the skull was cut open, many machines claw thorn in his mind to striking . His painful to see such a scene shouted : "Let me die ( let me die ) " Subsequently , special operations group arrived, the pain in the back of Colson to save and arrested Leina . In the effort to round up the Aegis Board, most of the centipede organization fell apart , but still Happy clairvoyance out .Later, Colson found the surgery to his doctor, Dr. Colson had told the truth . Originally, after the New York event , Colson has been dead for many days , but the Secretary Winfrey him back to earth from heaven , through continuous surgery to save the Colson back . In order to recover his best level of work can no longer suffering, give him some memories implanted in T ahiti . After hearing these words, Colson stormed off . End, Peterson woke up and found himself badly bruised , opened the quilt cover the body and found that he had become crippled when he cries , he 's "eyeball " appears in a few words : Good morning , Pete Mr. Mori .词汇练习111.He accepted the invitation, but was later forced to ---------- himself.他接受了邀请,但后来被迫失约。

十一月再见十二月你好文案句子十一月已经结束,十二月已经来临,新的月份意味着新的开始,过去的终将成为过去,与其羡慕别人的现在,不如过好自己的今天。

下面是本店铺精心推荐的十一月再见十二月你好文案句子,仅供参考,欢迎阅读!十一月再见十二月你好文案1、幸福就是在明媚的阳光里,遇到比阳光明媚一百倍的你。

十二月,早安!2、睁开明亮的双眼,除去睡意的干扰,舒展美丽的笑脸,拥抱快乐的一天。

早安,朋友,愿你今天好心情,生活工作都舒心!十二月,早安!3、新的一月开始了,也是今年最后一个月,今早依旧雾霾没看到阳光,只有心中充满阳光了。

4、十一月再见,十二月请对我好点,再不想折腾了,望所有的事与愿违都能顺我心意。

5、坚持把简单的事情做好就是不简单,坚持把平凡的事情做好就是不平凡。

所谓成功,就是在平凡中做出不平凡的坚持。

愿十二月遇见更好的自己!早安!6、成长道路谁都会受伤,我们才刚刚起航,必须学会坚强。

十二月你好,早安!7、十一月已逝,不管过得怎样,不必太在意。

若是美好,叫做精彩;若是糟糕,叫做经历。

十二月,请对我温柔些!8、十二月,请对我好一些,希望这个月欢乐多一些,无论酸甜苦辣,不好的都会过去,好的都留在我身边。

十二月你好。

9、十二月你好,十一月再见。

要过一点属于自己的生活。

为自己改变一次。

10、真正的幸福是一点一点争取的,是一天一天积累的。

十二月你好,早安!11、十一月再见了,十二月你好!在今年仅剩的一个月里,想要做的要赶紧去做,不要留下遗憾。

12、树不曾再见人,人亦不能再见人,不敢想,也不曾忘,十一月底感怀。

13、时间不是用来冲淡一切的,而是让我们去找到我们所要的一切的答案。

十二月你好,早安!14、没什么值得畏惧,你唯一需要担心的是,你配不上自己的梦想,也辜负了曾经的苦难。

十二月你好!15、十二月快乐,今年最后一个月,希望你爱的到想爱的人,赚的到想赚的钱,脚踏实地的去努力完成目标。

即使很累也不轻易放弃,一直相信自己可以。

英文十一到二十怎么写十一至二十的英语单词:11 eleven、12 twelve、13 thirteen、14 fourteen、15 fifteen、16 sixteen、17 seventeen 、18 eighteen、19 nineteen、20 twenty。

词汇解析:一、eleven英[ɪ'lev(ə)n] 美[ɪ'lɛvn]1、n. 十一;十一个2、adj. 十一的;十一个的3、num. 十一;十一个He wants you to call him back at eleven.他要你在十一点给他回电话。

二、twelve英[twelv] 美[twɛlv]1、n. 十二;十二个2、num. 十二;十二个3、adj. 十二的;十二个的In all, we stayed atthe park for about twelve hours.我们总共在公园呆了大约十二个小时。

三、thirteen英[θɜː'tiːn; 'θɜːtiːn] 美['θɝ'tin]1、n. 十三;十三岁;十三个2、num. 十三3、adj. 十三的;十三个的I have thirteen cows. I have sixteen turkeys.我有十三头奶牛。

我有十六只火鸡。

四、fourteen英[fɔː'tiːn; 'fɔːtiːn] 美[,fɔr'tin]1、n. 十四的记号;十四岁;十四点钟;十五世纪2、num. 十四;十四个;第十四3、adj. 十四的;十四个的I left the orphanage when I was about fourteen.我大约十四岁时离开了孤儿院。

五、twenty英['twentɪ] 美['twɛnti]1、n. 二十;二十年代2、num. 二十3、adj. 二十的I know you have the twenty dollars.我知道你有这二十元的。

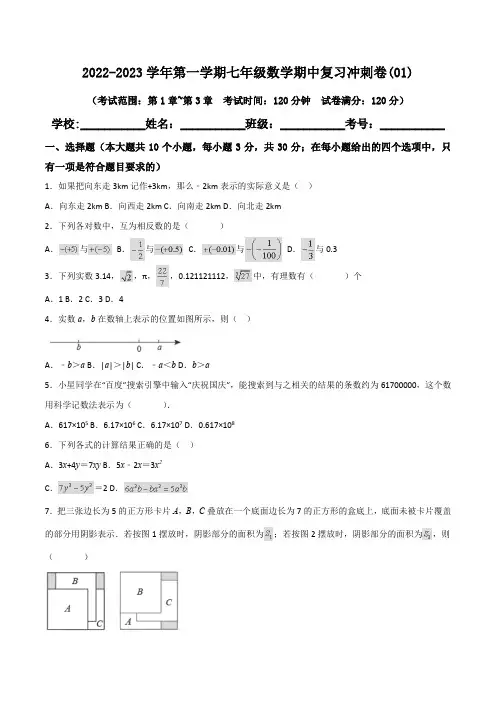

2022-2023学年第一学期七年级数学期中复习冲刺卷(01)(考试范围:第1章~第3章考试时间:120分钟试卷满分:120分)学校:___________姓名:___________班级:___________考号:___________ 一、选择题(本大题共10个小题,每小题3分,共30分;在每小题给出的四个选项中,只有一项是符合题目要求的)1.如果把向东走3km记作+3km,那么﹣2km表示的实际意义是()A.向东走2km B.向西走2km C.向南走2km D.向北走2km2.下列各对数中,互为相反数的是()A.与B.与C.与D.与0.33.下列实数3.14,,π,,0.121121112,中,有理数有()个A.1 B.2 C.3 D.44.实数a,b在数轴上表示的位置如图所示,则()A.﹣b>a B.|a|>|b| C.﹣a<b D.b>a5.小星同学在“百度”搜索引擎中输入“庆祝国庆”,能搜索到与之相关的结果的条数约为61700000,这个数用科学记数法表示为().A.617×105 B.6.17×106 C.6.17×107 D.0.617×1086.下列各式的计算结果正确的是()A.3x+4y=7xy B.5x﹣2x=3x2C.=2 D.7.把三张边长为5的正方形卡片A,B,C叠放在一个底面边长为7的正方形的盒底上,底面未被卡片覆盖的部分用阴影表示.若按图1摆放时,阴影部分的面积为;若按图2摆放时,阴影部分的面积为,则()A.B.C.D.无法判断8.甲乙两地相距,某人计划到达,现在因为路上发生事故,延后了到达,相比于原计划,平均每小时会少走()A.B.C.D.9.把黑色三角形按如图的规律进行拼图,其中第①个图案有1个黑色三角形,第②个图案有3个黑色三角形,第③个图案有6个黑色三角形,…,按此规律排列下去,则第⑨个图案黑色三角形的个数为()A.21 B.28 C.36 D.4510.把两张形状大小完全相同的小长方形卡片(如图1)不重复地放在一个底面为长方形(长为,宽为)的盒子底部(如图2),盒子底面未被卡片覆盖的部分用阴影表示,则图2中两块阴影部分周长的和是()A.B.C.D.二、填空题(本大题共8个小题,每题3分,共24分)11.在,,,,,,中非负数有_____个12.单项式的次数为_____,系数为_____.13.比较大小:_____(填“>”,“=”或“>”).14.一个零件的内径尺寸在图上标注的是20﹣0.03+0.05(单位mm),表示这种零件的标准尺寸是______mm,加工要求最大不超过标准尺寸______mm,最小不超过标准尺寸______mm.15.有理数a,b,c在数轴上的位置如图,试化简:|a|+|b|-|c|=___________.16.下图显示的填数幻方只填了一部分,将下列九个数:,,1,2,4,8,16,32,64填入方格中,使得所有行、列及对角线上各数的乘积相等.则填“x”格中的数应是________.17.已知数,,在数轴上的对应点的位置如图所示,化简的结果为______.18.下图是在正方形网格中按规律填成的阴影,根据此规律,则第个图中阴影部分小正方形的个数是________(用含的代数式表示).三、解答题(本大题共8小题,共66分;第19-22每小题6分,第23-24每小题8分,第25小题12分,第26小题14分)19.把下面的有理数填在相应的横线上,将各数用逗号分开:15,,0,-30,-0.15,-128,,+20,-2.6,0.333 3…正数:;负数:;整数:;非负数:.20.计算(1)(2)(3)(4)21.先化简,再求值.(1),其中a=;(2),其中x=-2,y=.22.如图,学校要利用专款建一长方形的自行车停车场,其他三面用护栏围起,其中与围墙平行的边长为米,与围墙垂直的边长比少米.(1)用、表示边的长;(2)求护栏的总长度;(3)若,,每米护栏造价80元,求建此停车场所需的费用.23.写出数轴上点、表示的数,并且在数轴上分别画出点、,点表示数;点表示数,最后将点、、、所表示的数用“”连接.解:点表示数,点表示数;.24.按如下规律摆放五角星:(1)填写表格:(2)请用含n的代数式表示出第n个图案中五角星的个数;(3)求第200个图案中五角星的个数.25.某口罩加工厂计划每名工人每天生产300个医用口罩,一周生产2100个医用口罩.由于种种原因,实际每天生产量与计划量相比有出入,工人小贤9月份第2周周日生产了300个医用口罩,9月份第3周的生产情况如下表,正号表示产量比前一天增产,负号表示产量比前一天减产.(1)根据记录的数据可知,小贤9月份第3周产量最多的一天是星期__________.(2)根据表格记录的数据,求出小贤本周实际生产的口罩数量.(3)若该厂实行每周计件工资制,每生产一个口罩可得0.8元,若超额完成周计划工作量,则超过部分每个另外奖励1.2元;若完不成每周的计划量,则少生产一个扣0.3元.问小贤这一周的工资总额是多少元?(4)若该厂实行每日计件工资制,每生产一个口罩可得0.8元,若超额完成每日计划工作量,则超过部分每个另外奖励1.2元;若完不成每天的计划量,则少生产一个扣0.3元,请直接写出小贤这一周的工资总额.26.已知多项式的常数项是a,次数是b,a、b在数轴上分别表示的点是A、B(如图),点A与点B之间的距离记作.(1)求a,b的值;(2)动点P从数1对应的点开始向右运动,速度为每秒1个单位长度.同时点A,B在数轴上运动,点A,B 的速度分别为每秒2个单位长度,每秒3个单位长度,运动时间为t秒.①若点A向右运动,点B向左运动,,求t的值;②若点A向左运动,点B向右运动,问是否存在常数m,使得的值为定值?若存在,求出m 的值,且定值为多少?若不存在,说明理由.答案与解析一、选择题(本大题共10个小题,每小题3分,共30分;在每小题给出的四个选项中,只有一项是符合题目要求的)1.如果把向东走3km记作+3km,那么﹣2km表示的实际意义是()A.向东走2km B.向西走2km C.向南走2km D.向北走2km【答案】B【分析】首先审清题意,明确“正”和“负”所表示的意义;再根据题意作答.【详解】解:向东走3km记作+3km,那么-2km表示向西走2km,故选:B.【点睛】本题考查了正负数的意义,解题的关键是理解“正”和“负”的相对性,明确什么是一对具有相反意义的量.在一对具有相反意义的量中,先规定其中一个为正,则另一个就用负表示.2.下列各对数中,互为相反数的是()A.与B.与C.与D.与0.3【答案】C【分析】先化简各数,再根据只有符号不同的两个数互为相反数判断即可.【详解】解:A. ,,不互为相反数;B. 与,不互为相反数;C. 与,互为相反数;D. 与0.3,不互为相反数;故选:C.【点睛】本题考查了相反数的识别,解题关键是理解相反数的意义,会利用相反数的意义化简各数.3.下列实数3.14,,π,,0.121121112,中,有理数有()个A.1 B.2 C.3 D.4【答案】D【分析】整数与分数称为有理数,其中分数指有限小数和无限循环小数,无限不循环小数叫做无理数,根据有理数与无理数的概念即可完成.【详解】∵,∴有理数有:3.14,,0.121121112,,而,π是无理数,故选:D.【点睛】本题考查了有理数,掌握有理数与无理数的概念是关键.4.实数a,b在数轴上表示的位置如图所示,则()A.﹣b>a B.|a|>|b| C.﹣a<b D.b>a【答案】A【分析】根据数轴的特点确定出a、b的正负情况以及绝对值的性质对各选项分析判断后利用排除法求解.【详解】解:由图可知,a>0,b<0,|a|<|b|,A、-b>a,故本选项正确,符合题意;B、|a|<|b|,故本选项错误,不符合题意;C、-a>b,故本选项错误,不符合题意;D、b<a,故本选项错误,不符合题意.故选:A.【点睛】本题考查了实数与数轴的关系,绝对值的定义,是基础题,准确识图是解题的关键.5.小星同学在“百度”搜索引擎中输入“庆祝国庆”,能搜索到与之相关的结果的条数约为61700000,这个数用科学记数法表示为().A.617×105 B.6.17×106 C.6.17×107 D.0.617×108【答案】C【分析】科学记数法的表示形式为的形式,其中1≤|a|<10,n为整数.确定n的值时,要看把原数变成a时,小数点移动了多少位,n的绝对值与小数点移动的位数相同.当原数绝对值>10时,n是正数;当原数的绝对值<1时,n是负数.【详解】解:61700000用科学记数法表示为,故选:C.【点睛】此题考查科学记数法的表示方法.科学记数法的表示形式为的形式,其中1≤|a|<10,n为整数,表示时关键要正确确定a的值以及n的值.6.下列各式的计算结果正确的是()A.3x+4y=7xy B.5x﹣2x=3x2C.=2 D.【答案】D【分析】利用合并同类项法则对每个选项进行分析,即可得出答案.【详解】解:A.3x与4y不是同类项,所以不能合并,故本选项不合题意;B.5x﹣2x=3x,故本选项不合题意;C.,故本选项不合题意;D.,故本选项符合题意;故选:D.【点睛】本题考查了合并同类项,掌握合并同类项法则是解决问题的关键.7.把三张边长为5的正方形卡片A,B,C叠放在一个底面边长为7的正方形的盒底上,底面未被卡片覆盖的部分用阴影表示.若按图1摆放时,阴影部分的面积为;若按图2摆放时,阴影部分的面积为,则()A.B.C.D.无法判断【答案】A【分析】根据正方形的性质,可以把两块阴影部分合并后计算面积,然后,比较S1和S2的大小.【详解】解:由图1,得:S1=(75)×(75)=4,由图2,得S2=(75)×(75)=4,∴.故选:A.【点睛】本题主要考查了有理数的混合运算的应用,分别得出S1和S2的面积是解题关键.8.甲乙两地相距,某人计划到达,现在因为路上发生事故,延后了到达,相比于原计划,平均每小时会少走()A.B.C.D.【答案】D【分析】根据速度=路程÷时间,分别表示出原计划的速度和实际的速度即可得出答案.【详解】解:原计划的速度=km/h,实际行走的速度=km/h,所以相比于原计划,平均每小时会少走.故选D.【点睛】本题考查了列代数式的知识,属于基础题型,用含s、a的代数式表示出原计划的速度和实际的速度是解题的关键.9.把黑色三角形按如图的规律进行拼图,其中第①个图案有1个黑色三角形,第②个图案有3个黑色三角形,第③个图案有6个黑色三角形,…,按此规律排列下去,则第⑨个图案黑色三角形的个数为()A.21 B.28 C.36 D.45【答案】D【分析】根据所给出的图案找出规律即可求解.【详解】解:第①个图案有1=1个黑色三角形,第②个图案有3=1+2个黑色三角形,第③个图案有6=1+2+3个黑色三角形,…,第⑨个图案黑色三角形的个数为,故选:D【点睛】本题考查了图形变化的规律,找出规律是解题的关键.10.把两张形状大小完全相同的小长方形卡片(如图1)不重复地放在一个底面为长方形(长为,宽为)的盒子底部(如图2),盒子底面未被卡片覆盖的部分用阴影表示,则图2中两块阴影部分周长的和是()A.B.C.D.【答案】D【分析】设小长方形卡片的长为m cm,宽为n cm,由图形分别表示阴影部分两长方形的长与宽,进而表示出阴影部分的周长和,去括号合并后,即可得到结果.【详解】解:设图1小长方形卡片的长为m cm,宽为n cm,根据题意得:两块阴影部分的周长和为2[m+(y-n)]+2[n+(y-m)]=2(m+y-n+n-m+y)=2×2y=4y(cm).故选:D.【点睛】此题考查了代数式及整式加减运算的应用,关键是设小长方形卡片的长和宽,将阴影部分的周长用设好的未知数的代数式表示.二、填空题(本大题共8个小题,每题3分,共24分)11.在,,,,,,中非负数有_____个【答案】4【分析】根据非负数的定义,非负数指大于等于0的数,即可求解.【详解】在,,,,,,中,是非负数故答案为4.【点睛】本题考查非负数的概念,属于简单题.12.单项式的次数为_____,系数为_____.【答案】 6【分析】根据单项式系数及次数的定义进行解答即可.【详解】解:根据单项式定义得:次数是三个字母的次数和,即3+2+1=6,单项式的系数是,故答案为:6;【点睛】本题主要考查的是单项式,熟知单项式中的数字因数叫做单项式的系数,一个单项式中所有字母的指数的和叫做单项式的次数是解答此题的关键.13.比较大小:_____(填“>”,“=”或“>”).【答案】>【分析】先通分,然后比较即可.【详解】解:∵,,.∴.故答案为:>.【点睛】本题考查了有理数大小的比较,将两分数正确通分是解答本题的关键.14.一个零件的内径尺寸在图上标注的是20﹣0.03+0.05(单位mm),表示这种零件的标准尺寸是______mm,加工要求最大不超过标准尺寸______mm,最小不超过标准尺寸______mm.【答案】20 0.05 0.03【分析】根据20﹣0.03+0.05所表示的含义,最多不能超过20+0.05,最少不低于20+(﹣0.03).【详解】这种零件的标准尺寸是20mm,最大不超过标准尺寸0.05mm,最小不超过标准尺寸0.03mm,故答案为:20;0.05;0.03.【点睛】本题考查了正负数在实际生活的应用,解题的关键是理解“正”、“负”的相对性,确定一对具有相反意义的量.15.有理数a,b,c在数轴上的位置如图,试化简:|a|+|b|-|c|=___________.【答案】-a+b+c【分析】由数轴可知,再去掉绝对值即可.【详解】解:由数轴可得:,∴,故答案为:.【点睛】本题主要考查数轴及绝对值的化简,解题的关键是通过数轴得到字母的正负.16.下图显示的填数幻方只填了一部分,将下列九个数:,,1,2,4,8,16,32,64填入方格中,使得所有行、列及对角线上各数的乘积相等.则填“x”格中的数应是________.【答案】8【详解】将未填各空格标注字母,如下图.九个已知数的乘积是.所以,每行、每列、每条对角线上三个数的乘积等于64.因为乘积等于64,所以从第二列和第三行分别得到.由此得到,a,c,e,f分别是,,2,4中的某个数.考虑第一行的乘积,得.这样一来,x只可能是1或8.考虑到对角线的乘积,得.若,则,不可能.唯一可能是.故答案为:8.这时的填法是17.已知数,,在数轴上的对应点的位置如图所示,化简的结果为______.【答案】2a【分析】根据数轴判断出a、b、c的符号和绝对值的大小,根据绝对值的意义脱去绝对值,去括号合并同类项即可求解.【详解】解:由数轴可得b<a<0<c,且,所以a+c>0,b+c<0,a+b<0,所以===.故答案为:2a【点睛】本题考查了数轴上点的意义,绝对值的意义,去括号,合并同类项等知识,根据数轴上点的位置,判断出绝对值内的式子的符号是解题关键.18.下图是在正方形网格中按规律填成的阴影,根据此规律,则第个图中阴影部分小正方形的个数是________(用含的代数式表示).【答案】【分析】根据第1、2、3个图中阴影部分小正方形的个数归纳类推出一般规律即可得.【详解】第1个图中阴影部分小正方形的个数,第2个图中阴影部分小正方形的个数,第3个图中阴影部分小正方形的个数,归纳类推得:第个图中阴影部分小正方形的个数是,其中n为正整数,故答案为:.【点睛】本题考查了列代数式表示图形的规律,根据前3个图形正确发现一般规律是解题关键.三、解答题(本大题共8小题,共66分;第19-22每小题6分,第23-24每小题8分,第25小题12分,第26小题14分)19.把下面的有理数填在相应的横线上,将各数用逗号分开:15,,0,-30,-0.15,-128,,+20,-2.6,0.333 3…正数:;负数:;整数:;非负数:.【答案】见解析【分析】根据有理数的分类逐项填写即可.【详解】解:正数:15,,+20,0.333 3…;负数:,-30,-0.15,-128,-2.6;整数:15,0,-30,-128,+20;非负数:15,0,,+20,0.333 3….【点睛】本题考查了有理数的分类,掌握有理数的分类是解题的关键.20.计算(1)(2)(3)(4)【答案】(1)28(2)17(3)23(4)【解析】(1)解:==28(2)解:===17(3)解:====23(4)解:===【点睛】本题考查了有理数的混合运算,解题关键是熟练掌握有理数运算法则和运算顺序,准确进行计算.21.先化简,再求值.(1),其中a=;(2),其中x=-2,y=.【答案】(1)-a-2;(2);【分析】(1)先根据整式加减运算法则进行化简,然后再代入数据进行计算即可;(2)先根据去括号,合并同类项法则进行化简,然后再代入数据进行计算即可.【详解】(1)解:=-a-2,当a=时,原式=.(2)解:===当x=-2,y=时,原式.【点睛】本题主要考查了整式的化简计算,熟练掌握去括号法则和合并同类项法则,是解题的关键.22.如图,学校要利用专款建一长方形的自行车停车场,其他三面用护栏围起,其中与围墙平行的边长为米,与围墙垂直的边长比少米.(1)用、表示边的长;(2)求护栏的总长度;(3)若,,每米护栏造价80元,求建此停车场所需的费用.【答案】(1)(米)(2)(米)(3)建此车场所需的费用是18400元【分析】(1)根据题意,即可得出边的长;(2)根据题意,结合(1)中的长,利用护栏的长度=2×与围墙垂直的边的长+与围墙平行的一边长进行计算即可;(3)把的值代入(2)中的代数式进行计算即可.【详解】(1)解:∵与围墙平等的边长为米,与围墙垂直的边长比少米,∴米;(2)解:∵长方形的自行车停车场其他三面用护栏围起,∴根据题意,可得:护栏的总长度米,答:护栏的总长度为米.(3)解:∵由(2)可得:护栏的总长度米,又∵,,∴护栏的总长度(米),又∵每米护栏造价80元,∴停车场所需的费用为:(元).答:若,,每米护栏造价80元,建此车场所需的费用是18400元【点睛】本题考查了列代数式、代数式求值以及整式的运算,解本题的关键是根据数量关系,列出代数式.23.写出数轴上点、表示的数,并且在数轴上分别画出点、,点表示数;点表示数,最后将点、、、所表示的数用“”连接.解:点表示数,点表示数;.【答案】画图见解析;,;,,,【分析】利用数轴表示各数,然后再根据在数轴上表示的两个有理数,右边的数总比左边的数大将点A、B、C、D所表示的数用“>”连接.【详解】解:如图所示,点表示数,点表示数,故.故答案为:;;;;;.【点睛】本题主要考查了数轴以及有理数大小比较,理解每个分数表示的意义,然后正确在数轴上表示出各个数是解决本题的关键,另外也要明确:数轴上右边的数大于左边的数.24.按如下规律摆放五角星:(1)填写表格:(2)请用含n的代数式表示出第n个图案中五角星的个数;(3)求第200个图案中五角星的个数.【答案】(1)10,13(2)3n+1(3)601【分析】(1)观察图形规律数出个数即可;(2)把五角星分成两部分,顶点处的一个不变,其它的分三条线,每一条线上后一个图形比前一个图形多一个,根据此规律找出第n个图形中五角星的个数的关系式为3n+1;(3)将n=20代入3n+1解答即可;【详解】(1)解:观察图形规律:第一个图形有4个五角星,第二个图形比第一个图形多3个五角星,即有4+3=7个五角星,第三个图形比第二个图形多3个五角星,即有4+3+3=10个五角星,故答案为:10,13;(2)解:观察图形规律:第一个图形有4个五角星,第二个图形比第一个图形多3个五角星,即有4+3=7个五角星,第三个图形比第二个图形多3个五角星,即有4+3+3=10个五角星,第四个图形比第三个图形多3个五角星,即有4+3+3+3=13个五角星,…………以此类推,第n个图形中的五角星有4+3(n﹣1)=(3n+1)个五角星,(3)解:将n=200代入3n+1中,得3×200+1=601(个).【点睛】本题考查了图形变化规律的问题,把五角星分成两部分进行考虑,并找出第n个图形五角星的个数的表达式是解题的关键.25.某口罩加工厂计划每名工人每天生产300个医用口罩,一周生产2100个医用口罩.由于种种原因,实际每天生产量与计划量相比有出入,工人小贤9月份第2周周日生产了300个医用口罩,9月份第3周的生产情况如下表,正号表示产量比前一天增产,负号表示产量比前一天减产.(1)根据记录的数据可知,小贤9月份第3周产量最多的一天是星期__________.(2)根据表格记录的数据,求出小贤本周实际生产的口罩数量.(3)若该厂实行每周计件工资制,每生产一个口罩可得0.8元,若超额完成周计划工作量,则超过部分每个另外奖励1.2元;若完不成每周的计划量,则少生产一个扣0.3元.问小贤这一周的工资总额是多少元?(4)若该厂实行每日计件工资制,每生产一个口罩可得0.8元,若超额完成每日计划工作量,则超过部分每个另外奖励1.2元;若完不成每天的计划量,则少生产一个扣0.3元,请直接写出小贤这一周的工资总额.【答案】(1)六(2)2152个(3)1784元(4)元【分析】(1)分别求出小贤9月份第3周每天的产量,即可求解;(2)把小贤9月份第3周每天的产量加起来,即可求解;(3)用小贤9月份第3周的产量总和乘以0.8再加上超出的奖励,即可求解;(4)分别求出小贤9月份第3周每天的超过部分另外奖励或扣费,再加起来,然后加上产量总和乘以0.8的积,即可求解.【详解】(1)解:根据题意得:星期一:300+5=305个,星期二:305-2=303个,星期三:303-4=299个,星期四:299+13=312个,星期五:312-9=303个,星期六:303+16=319个,星期日:319-8=311个,所以小贤9月份第3周产量最多的一天是星期六;(2)解:个答:小贤本周实际生产的口罩数量为2152个;(3)解:根据题意得:元,答:小贤这一周的工资总额是1784元;(4)解:根据题意得:星期一:元,星期二:元,星期三:元,星期四:元,星期五:元,星期六:元,星期日:元,所以元,答:小贤这一周的工资总额为元.【点睛】本题主要考查了有理数的实际应用,明确题意,准确得到数量关系是解题的关键.26.已知多项式的常数项是a,次数是b,a、b在数轴上分别表示的点是A、B(如图),点A与点B之间的距离记作.(1)求a,b的值;(2)动点P从数1对应的点开始向右运动,速度为每秒1个单位长度.同时点A,B在数轴上运动,点A,B的速度分别为每秒2个单位长度,每秒3个单位长度,运动时间为t秒.①若点A向右运动,点B向左运动,,求t的值;②若点A向左运动,点B向右运动,问是否存在常数m,使得的值为定值?若存在,求出m的值,且定值为多少?若不存在,说明理由.【答案】(1)a=-20,b=30;(2)①或10;②存在常数m=3,使得的值为定值,定值为-45.【分析】(1)根据多项式的常数项与多项式的次数的定义即可求出答案;(2)①分两类情况来讨论∶点A、B在相遇前时;点A、B在相遇时;依此可求t的值;②当运动t秒时,A点表示的数为-20-2t,B点表示的数为30+3t,P点表示的数为1+t,可得2AP-m×PB=(6-2m)t+(42-29m),依此可求m的值.【详解】(1)解∶∵多项式的常数项是-20,次数是30.∴a=-20,b=30;(2)解:①如下图所示∶当t=0时,AP=21,BP=29,若点A向右运动,点B向左运动,则运动t秒时,A点表示的数为-20+2t,B点表示的数为30-3t.∵动点P从数1对应的点开始向右运动,速度为每秒1个单位长度,∴运动t秒时,P点表示的数为1+t;下面分两类情况来讨论∶点A、B在相遇前时,∵AP=PB,∴1+t-(-20+2t)=30-3t-(1+t),解得;点A、B在相遇时,AP=PB,此时A与B重台,则-20+2t=30-3t,解得t=10;显然,点A,B在相遇后,BP大于AP,不符合条件.综上所述,或10;②当运动t秒时,A点表示的数为-20-2t,B点表示的数为30+3t,P点表示的数为1+t,2AP-m×PB=2[(1+t)-(-20-2t)]-m[(30+3t)-(1+t)]=(6-2m)t+(42-29m),当6-2m=0时,上式的值不随时间t的变化而改变.∴存在常数m=3,使得的值为定值,此时.【点睛】本题考查了一元一次方程的应用、数轴以及多项式的定义,根据多项式的定义,找出a,b的值以及找准等量关系,正确列出一元一次方程是解题的关键.。

概括西游记11到20回的主要情节摘要:I.前言II.第11 回如意金箍棒的来历III.第12 回悟空降妖IV.第13 回太宗游地府V.第14 回真假美猴王VI.第15 回悟空三打白骨精VII.第16 回乌鸡国救主VIII.第17 回悟空降魔IX.第18 回悟空三调花果山X.第19 回悟空大战黑熊精XI.第20 回悟空降妖宝物正文:西游记是中国古代文学名著之一,其中第11 回至20 回的主要情节如下:在第11 回中,讲述了如意金箍棒的来历。

如意金箍棒是悟空在东海龙宫所得,它原本是东海龙王的镇海之宝。

悟空得到金箍棒后,便可以使用它来降妖除魔。

第12 回中,讲述了悟空降妖的故事。

在这一回中,悟空与三妖大战,最终将它们降服,并得到了它们的宝物。

在第13 回中,讲述了太宗游地府的故事。

太宗在阴间遇到了自己的判官,被告知自己的寿命已尽,于是太宗便请求悟空前往阴间,帮助自己延长寿命。

第14 回中,讲述了真假美猴王的故事。

在这一回中,出现了一个与悟空长得一模一样的美猴王,它假冒悟空,扰乱了天庭的秩序。

最终,在如来佛祖的帮助下,悟空战胜了美猴王。

在第15 回中,讲述了悟空三打白骨精的故事。

白骨精是妖怪中的佼佼者,它三次变化成不同的形象,企图陷害悟空。

最终,在观音菩萨的帮助下,悟空成功将白骨精降服。

第16 回中,讲述了乌鸡国救主的故事。

在这一回中,悟空帮助乌鸡国国王打败了妖怪,救出了国王。

第17 回中,讲述了悟空降魔的故事。

在这一回中,悟空与牛魔王展开了一场激烈的战斗,最终将牛魔王降服。

在第18 回中,讲述了悟空三调花果山的故事。

在这一回中,悟空前往花果山,调解了群猴之间的纷争。

第19 回中,讲述了悟空大战黑熊精的故事。

黑熊精是妖怪中的强者,它企图占据花果山。

最终,在悟空的帮助下,花果山群猴成功将黑熊精赶走。

在第20 回中,讲述了悟空降妖宝物的故事。

在这一回中,悟空得到了一件名为“降妖宝物”的法宝,它可以用来降服妖怪。