数字逻辑第二三章

- 格式:docx

- 大小:53.68 KB

- 文档页数:8

数字逻辑知到章节测试答案智慧树2023年最新江西理工大学第一章测试1.四位二进制数的最大数是()。

参考答案:11112.将数1101.11B转换为十六进制数为()。

参考答案:D.CH3.十数制数2006.375转换为二进制数是()。

参考答案:11111010110.0114.将十进制数130转换为对应的八进制数()。

参考答案:2025.四位二进制数0111加上0011等于1010。

()参考答案:对6.16进制数2B等于10进制数()。

参考答案:437.16进制数3.2等于2进制数()。

参考答案:11.0018.十进制数9比十六进制数9小。

()参考答案:错9.与八进制数(47.3)8等值的数为()参考答案:(100111.011)2;(27.6)1610.有符号数10100101的补码是()。

参考答案:1101101111.[X]补+[Y]补=()。

参考答案:[X+Y]补12.十进制数7的余3码是()。

参考答案:101013.以下代码中为无权码的为()。

参考答案:余三码;格雷码14.格雷码具有任何相邻码只有一位码元不同的特性。

()参考答案:对第二章测试1.逻辑函数的表示方法中具有唯一性的是()。

参考答案:卡诺图;真值表2.在何种输入情况下,“与非”运算的结果是逻辑0。

()参考答案:全部输入是13.逻辑变量的取值1和0可以表示()。

参考答案:电位的高、低;真与假;开关的闭合、断开;电流的有、无4.A’+B’等于()。

参考答案:(AB)’5.以下表达式中符合逻辑运算法则的是()。

参考答案:A+1=16.逻辑函数两次求反则还原,逻辑函数的对偶式再作对偶变换也还原为它本身。

()参考答案:对7.求Y=A(B+C)+CD的对偶式是()。

参考答案:(A+BC)(C+D)8.已知逻辑函数Y的波形图如下图,该逻辑函数式是Y=()。

参考答案:A’BC+AB’C+ABC’9.任意函数的全体最大项之积为1。

()参考答案:错10.下列哪些项属于函数Y(A、B、C、D)=(A’B+C)’D+AB’C’的最小项()。

数字逻辑第四版课后练习题含答案1. 第一章1.1 课后习题1. 将十进制数22转换为二进制数。

答:22 = 101102. 将二进制数1101.11转换为十进制数。

答:1101.11 = 1 x 2^3 + 1 x 2^2 + 0 x 2^1 + 1 x 2^0 + 1 x 2^(-1) + 1 x 2^(-2) = 13.753. 将二进制数1101.01101转换为十进制数。

答:1101.01101 = 1 x 2^3 + 1 x 2^2 + 0 x 2^1 + 1 x 2^0 + 0 x 2^(-1)+ 1 x 2^(-2) + 1 x 2^(-4) + 0 x 2^(-5) + 1 x 2^(-6) = 13.406251.2 实验习题1. 合成与门电路设计一个合成与门电路,使得它的输入A,B和C,只有当A=B=C=1时输出为1,其他情况输出为0。

答:下面是一个合成与门电路的示意图。

合成与门电路示意图其中,S1和S2是两个开关,当它们都被打开时,电路才会输出1。

2. 第二章2.1 课后习题1. 将十进制数168转换为八进制数和二进制数。

答:168 = 2 x 8^3 + 1 x 8^2 + 0 x 8^1 + 0 x 8^0 = 250(八进制)。

168 = 10101000(二进制)。

2. 将八进制数237转换为十进制数和二进制数。

答:237 = 2 x 8^2 + 3 x 8^1 + 7 x 8^0 = 159(十进制)。

237 = 010111111(二进制)。

2.2 实验习题1. 全加器电路设计一个全加器电路,它有三个输入A,B和C_in,两个输出S和C_out。

答:下面是一个全加器电路的示意图。

C_in|/ \\/ \\/ \\/ \\/ \\A|________ \\| | AND Gate______| |B|__| XOR |_| S\\\\ /\\ /\\ /\\ /| | OR Gate| ||_| C_out其中,AND Gate表示与门,XOR Gate表示异或门,OR Gate表示或门。

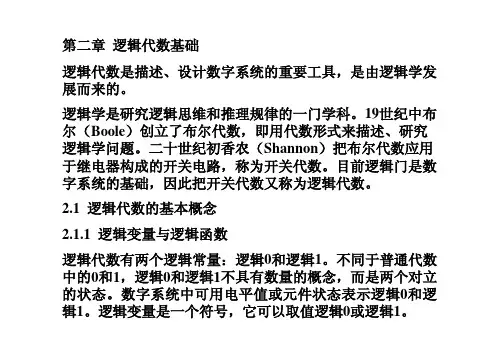

第二章逻辑代数基础逻辑代数是描述、设计数字系统的重要工具,是由逻辑学发展而来的。

逻辑学是研究逻辑思维和推理规律的一门学科。

19世纪中布尔(Boole)创立了布尔代数,即用代数形式来描述、研究逻辑学问题。

二十世纪初香农(Shannon)把布尔代数应用于继电器构成的开关电路,称为开关代数。

目前逻辑门是数字系统的基础,因此把开关代数又称为逻辑代数。

2.1 逻辑代数的基本概念2.1.1 逻辑变量与逻辑函数逻辑代数有两个逻辑常量:逻辑0和逻辑1。

不同于普通代数中的0和1,逻辑0和逻辑1不具有数量的概念,而是两个对立的状态。

数字系统中可用电平值或元件状态表示逻辑0和逻辑1。

逻辑变量是一个符号,它可以取值逻辑0或逻辑1。

逻辑代数中,若某逻辑变量F 的取值唯一地由一组变量A 1, A 2, …, A n 的取值确定,则称这样的逻辑关系为逻辑函数关系,可表示为:F = f ( A 1, A 2, …, A n )其中,称逻辑变量F 为逻辑因变量或输出变量,多用于描述数字系统的输出状态;变量组A 1, A 2, …, A n 称为逻辑自变量或输入变量,常用于描述数字系统的输入状态。

与普通代数中的函数不同,逻辑函数中的变量仅能取离散值逻辑0、逻辑1,逻辑函数中的运算可分解为与、或、非这三种逻辑运算。

逻辑函数相同的概念为,若有逻辑函数F 1= f 1( A 1, A 2, …, A n )F 2= f 2( A 1, A 2, …, A n )且对于A 1, A 2, …, A n 的所有取值组,F 1 、F 2的取值都相同,则认为逻辑函数F 1 、F 2相同。

2.1.2 逻辑运算逻辑代数中有“与”、“或”、“非”三种逻辑运算。

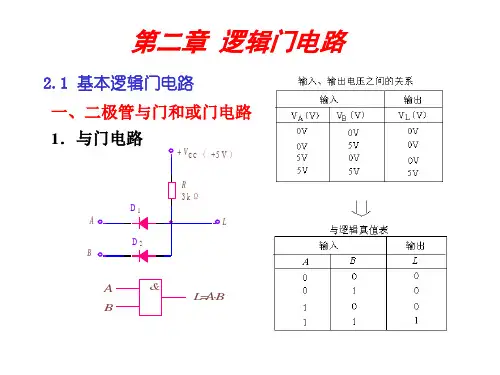

1. “与”运算若决定某事件发生的多个条件同时满足时,该事件才能发生,称这样的逻辑关系为“与”逻辑。

逻辑代数中用“与”运算描述“与”逻辑,其运算符为“·”或“∧”。

“与”运算式可表示为:F = A ·B或F = A∧B“与”运算也称为逻辑乘。

第一章开关理论基础1.将下列十进制数化为二进制数和八进制数十进制二进制八进制49 110001 6153 110101 65127 1111111 177635 1001111011 11737.493 111.1111 7.7479.43 10011001.0110111 231.3342.将下列二进制数转换成十进制数和八进制数二进制十进制八进制1010 10 12111101 61 751011100 92 1340.10011 0.59375 0.46101111 47 5701101 13 153.将下列十进制数转换成8421BCD码1997=0001 1001 1001 011165.312=0110 0101.0011 0001 00103.1416=0011.0001 0100 0001 01100.9475=0.1001 0100 0111 01014.列出真值表,写出X的真值表达式A B C X0 0 0 00 0 1 00 1 0 00 1 1 11 0 0 01 0 1 11 1 0 11 1 1 1 X=A BC+A B C+AB C+ABC5.求下列函数的值当A,B,C为0,1,0时:A B+BC=1(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,1,0时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=1当A,B,C为1,0,1时:A B+BC=0(A+B+C)(A+B+C)=1(A B+A C)B=06.用真值表证明下列恒等式(1) (A⊕B)⊕C=A⊕(B⊕C)A B C (A⊕B)⊕C A⊕(B⊕C)0 0 0 0 00 0 1 1 10 1 0 1 10 1 1 0 01 0 0 1 11 0 1 0 01 1 0 0 01 1 1 1 1所以由真值表得证。

(2)A⊕B⊕C=A⊕B⊕CA B C A⊕B⊕C A⊕B⊕C0 0 0 1 10 0 1 0 00 1 0 0 00 1 1 1 11 0 0 0 01 0 1 1 11 1 0 1 11 1 1 0 07.证明下列等式(1)A+A B=A+B证明:左边= A+A B=A(B+B)+A B=AB+A B+A B=AB+A B+AB+A B=A+B=右边(2)ABC+A B C+AB C=AB+AC证明:左边= ABC+A B C+AB C= ABC+A B C+AB C+ABC=AC(B+B)+AB(C+C)=AB+AC=右边(3)EDCCDACBAA)(++++=A+CD+E证明:左边=EDCCDACBAA)(++++=A+CD+A B C+CD E=A+CD+CD E=A+CD+E=右边(4)C B A C B A B A ++=CB C A B A ++证明:左边=CB AC B A B A ++=CB AC AB C B A B A +++)(=C B C A B A ++=右边8.用布尔代数化简下列各逻辑函数表达式(1) F=A+ABC+A C B +CB+C B = A+BC+C B(2) F =(A+B+C )(A+B+C) = (A+B)+C C = A+B(3) F =ABC D +ABD+BC D +ABCD+B C = AB+BC+BD(4) F=C AB C B BC A AC +++= BC(5) F=)()()()(B A B A B A B A ++++=BA 9.将下列函数展开为最小项表达式(1) F(A,B,C) = Σ(1,4,5,6,7)(2) F(A,B,C,D) = Σ(4,5,6,7,9,12,14)10.用卡诺图化简下列各式(1)CAB C B BC A AC F +++=0ABC00 01 11 1011111化简得F=C(2)CB A D A B A DC AB CD B A F++++=111111ABCD 00 01 11 1000011110化简得F=DA B A +(3) F(A,B,C,D)=∑m (0,1,2,5,6,7,8,9,13,14)1111111111AB CD 00 01 11 1000011110化简得F=DBC D C A BC A C B D C ++++(4) F(A,B,C,D)=∑m (0,13,14,15)+∑ϕ(1,2,3,9,10,11)Φ1ΦΦ1ΦΦ1Φ1AB CD 00 01 11 1000011110化简得F=ACAD B A ++11.利用与非门实现下列函数,并画出逻辑图。

第二章 组合逻辑1. 分析图中所示的逻辑电路,写出表达式并进行化简2. 分析以下图所示逻辑电路,其中S3、S 二、S 一、S0为操纵输入端,列出真值表,说明 F 与 A 、B 的关系。

F1=BF = AB + B = ABA F = AB BABC CABC = AB + AC + BC + BC = AB + BC + BC1S B BS A ++F2=F=F 1F 2=3. 分析以下图所示逻辑电路,列出真值表,说明其逻辑功能。

解: F1==真值表如下:当B ≠C 时, F1=A 当B=C=1时, F1=A 当B=C=0时, F1=032S B A ABS +1S B BS A ++CB BC A C AB C B A +++ABC C B A ABC C B A C B A +⊕=++)(A B C F 0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 100000111裁判裁决电路,A 为主裁判,在A 同意的前提下,只要有一名副裁判(B ,C )同意,成绩就有效。

F2=真值表如下:当A 、B 、C 三个变量中有两个及两个以上同时为“1”时,F2 = 1 。

4.图所示为数据总线上的一种判零电路,写出F 的逻辑表达式,说明该电路的逻辑功能。

解:F=只有当变量A0~A15全为0时,F = 1;不然,F = 0。

因此,电路的功能是判定变量是不是全数为逻辑“0”。

5. 分析以下图所示逻辑电路,列出真值表,说明其逻辑功能解: 真值表如下:因此,这是一个四选一的选择器。

AC BC AB C A C B B A ++=++A B C F 0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1000011111514131211109876543210A A A A A A A A A A A A A A A A +++301201101001X A A X A A X A A X A A F +++=6. 以下图所示为两种十进制数代码转换器,输入为余三码,输出什么缘故代码?解:这是一个余三码 至8421 BCD 码转换的电路7. 以下图是一个受 M 操纵的4位二进制码和格雷码的彼此转换电路。

第一章数制与代码进位计数制的基本概念,进位基数和数位的权值。

常用进位计数制:十进制二进制八进制十六进制数制转换:把非十进制数转换成十进制数:按权展开相加。

十进制数转换成其它进制数:整数转换,采用基数连除法。

纯小数转换,采用基数连乘法。

二进制数转换成八进制数或十六进制数:以二进制数的小数点为起点,分别向左、向右,每三位(或四位)分一组。

对于小数部分,最低位一组不足三位(或四位)时,必须在有效位右边补0,使其足位。

然后,把每一组二进制数转换成八进制(或十六进制)数,并保持原排序。

对于整数部分,最高位一组不足位时,可在有效位的左边补0,也可不补。

八进制(或十六进制)数转换成二进制数:只要把八进制(或十六进制)数的每一位数码分别转换成三位(或四位)的二进制数,并保持原排序即可。

整数最高位一组左边的0,及小数最低位一组右边的0,可以省略。

常用代码:二-十进制码(BCD码Binary Coded Decimal)——用二进制码元来表示十进制数符“0 ~ 9”主要有:8421BCD码2421码余3码(注意区分有权码和无权码)可靠性代码:格雷码和奇偶校验码具有如下特点的代码叫格雷码:任何相邻的两个码组(包括首、尾两个码组)中,只有一个码元不同。

格雷码还具有反射特性,即按教材表中所示的对称轴,除最高位互补反射外,其余低位码元以对称轴镜像反射。

格雷码属于无权码。

在编码技术中,把两个码组中不同的码元的个数叫做这两个码组的距离,简称码距。

由于格雷码的任意相邻的两个码组的距离均为1,故又称之为单位距离码。

另外,由于首尾两个码组也具有单位距离特性,因而格雷码也叫循环码。

奇偶校验码是一种可以检测一位错误的代码。

它由信息位和校验位两部分组成。

(要掌握奇偶校验原理及校验位的形成及检测方法)字符代码:ASCII码(American Standard Code for Information Interchange,美国信息交换标准代码)第二章 基本逻辑运算及集成逻辑门基本逻辑运算: 与逻辑、或逻辑、非逻辑常用复合逻辑:“与非”逻辑、“或非”逻辑、“与或非”逻辑“异或”逻辑 及“同或”逻辑两变量的“异或逻辑”和“同或逻辑”互为反函数。

第二章 组合逻辑

1. 分析图中所示的逻辑电路,写出表达式并进行化简

2. 分析下图所示逻辑电路,其中S3、S2、S1、S0为控制输入端,列出真值表,说明 F 与 A 、B 的关系。

F1= F2=

F=F 1F 2=

3. 分析下图所示逻辑电路,列出真值表,说明其逻辑功能。

解:

F1== 真值表如下:

当B ≠C 时, F1=A 当B=C=1时, F1=A 当B=C=0时, F1=0

裁判判决电路,A 为主裁判,在A 同意的前提下,只要有一位副裁判(B ,C )同意,成绩就有效。

F2=

真值表如下:

当A 、B 、C 三个变量中有两个及两个以上同时为“1”时,F2 = 1 。

4.图所示为数据总线上的一种判零电路,写出F 的逻辑表达式,说明该电路的逻辑功能。

解:F=

只有当变量A0~A15全为0时,F = 1;否则,F = 0。

因此,电路的功能是判断变量是否全部为逻辑“0”。

5. 分析下图所示逻辑电路,列出真值表,说明其逻辑功能

解: 真值表如下:

因此,这是一个四选一的选择器。

6. 下图所示为两种十进制数代码转换器,输入为余三码,输出为什么代码?

解:

1

S B BS A ++3

2

S B A ABS +1

S B BS A ++C B BC A C AB C B A +++ABC C B A ABC C B A C B A +⊕=++)(AC BC AB C A C B B A ++=++1514131211109876543210A A A A A A A A A A A A A A A A +++301201101001X A A X A A X A A X A A F +++=

这是一个余三码 至8421 BCD 码转换的电路7. 下图是一个受 M 控制的4位二进制码和格雷码的相互转换电路。

M=1 时,完成自然二进制码至格雷码转换;M=0 时,完成相反转换。

请说明之

解:Y3=X3

当M=1时 Y3=X3

Y2=X2⊕X3 Y1=X1⊕X2 Y0=X0⊕X1 当M=0时 Y3=X3

Y2=X2⊕X3

Y1=X1⊕Y2=X1⊕X2⊕X3 Y0=X0⊕Y1=X0⊕X1⊕X2⊕X3

由真值表可知:M=1 时,完成8421 BCD 码到格雷码的转换;

M=0 时,完成格雷码到8421 BCD 码的转换。

8. 已知输入信号A,B,C,D 的波形如下图所示,选择适当的集成逻辑门电路,设计产生输出 F 波形的组合电路(输入无反变量) 解:

列出真值表如下:

9. 用红、黄、绿三个指示灯表示三台设备的工作情况:绿灯亮表示全部正常;红灯亮表示有一台不正常;黄灯亮表示有两台不正常;红、黄灯全亮表示三台都不正常。

列出控制电路真值表,并选出合适的集成电路来实现。

解:

设:三台设备分别为 A 、B 、C : “1”表示有故障,“0”表示无故障;红、黄、绿灯分别为Y1、Y2、Y3:“1”表

示灯亮;“0”表示灯灭。

据题意列出真值表如下: 于是得:

10. 用两片双四选一数据选择器和与非门实现循环码至8421BCD 码转换。

解:(1)画函数卡诺图; (2)写逻辑函数表达式: (1) 画逻辑图:

11. 用一片74LS148和与非门实现8421BCD 优先编码器

12. 用适当门电路,设计16位串行加法器,要求进位琏速度最快,计算一次加法时间。

C B A C B A Y C B A BC Y C B A Y ++==⊕+=⊕⊕=3)

(21

要使进位琏速度最快,应使用“与或非”门。

具体连接图如下。

若“与或非”门延迟时间为t1,“非门”延迟时间为t2,则完成一次16位加法运算所需时间为:

13.用一片4:16线译码器将8421BCD 码转换成余三码,写出表达式 解: 14. 使用一个4位二进制加法器设计8421BCD 码转换成余三码转换器: 解:15. 用74LS283加法器和逻辑门设计实现一位8421 BCD 码加法器电路。

解:

16. 设计二进制码/格雷码转换器 解:真值表

得:

17. 设计七段译码器的内部电路,用于驱动共阴极数码管。

解:七段发光二极管为共阴极电路,各段为“1”时亮。

七段译码器真值表如下:

18.

用XY A 型A 型

01 B 型

10 AB 型 10 AB 型 11 O 型 11 O 型

得:F 1 = Σ(0,2,5,6,10,12,13,14,15)

1002

1132233B B G B B G B B G B G ⊕=⊕=⊕==

19. 设计保密锁。

解: 设A,B,C 按键按下为1,F 为开锁信号(F=1为打开),G 为报警信号(G=1为报警)。

F 的卡诺图:

化简得:

G 的卡诺图

化简得:

第三章 时序逻辑

1.写出触发器的次态方程,并根据已给波形画出输出 Q 的波形。

解:

2. 说明由RS 触发器组成的防抖动电路的工作原理,画出对应输入输出波形

解:

3. 已知JK 信号如图,请画出负边沿JK 触发器的输出波形(设触发器的初态为0)

4. 写出下图所示个触发器次态方程,指出CP 脉冲到来时,触发器置“1”的条件。

解:(1)

,若使触发器置“1”,则A 、B 取值相异。

(2),若使触发器置“1”,则A 、B 、C 、D 取值为奇数个1。

5.写出各触发器的次态方程,并按所给的CP 信号,画出各触发器的输出波形(设初态为0)

解:

AC AB F +=C A B A G +=1

)(1

=+++=+c b a Q

a c

b Q n

n B A B A D +=D C B A K J ⊕⊕⊕==

6.

7. 8.

9. 规律工作的六进制同步计数器

解:先列出真值表,然后求得激励方程

PS NS

输出

N

0 0 0 0 0 1 0 0 0 1 0 1 1 0 0 1 1 1 1 1 0 1 1 1 1 0 1 0 1 0 1 1 0 0 0 1 0 0 0 0 0 1

化简得:

10. 用D 触发器设计3位二进制加法计数器,并画出波

形图。

解: 真值表如下

n Q 2n Q 1n Q 012+n Q 11+n Q 10+n Q Q A

Q B Q D Q C Q E Q F Q G Q H

OE

建立激励方程:

11. 用下图所示的电路结构构成五路脉冲分配器,试分别用简与非门电路及74LS138集成译码器构成这个译码器,并画出连线图。

解:先写出激励方程,然后求得状态方程

得真值表

得状态图

若用与非门实现,译码器输出端的逻辑函数为:

若用译码器74LS138实现,译码器输出端的逻辑函数为:

12 若将下图接成12进制加法器,预置值应为多少?画出状态图及输出波形图。

解:预置值应C=0,B=1,A=1。

13. 分析下图所示同步时序逻辑电路,作出状态转移表和状态图,说明它是Mealy型电路还是Moore 型电路以及电路的功能。

解:电路的状态方程和输出方程为:

该电路是Moore型电路。

当X=0时,电路为模4加法计数器;

当X=1时,电路为模4减法计数器

14.分析下图所示同步时序逻辑电路,作出状态转移表和状态图,说明这个电路能对何种序列进行检测?解:电路的状态方程和输出方程为:由此可见,凡输入序列“110”,输出就为“1”。

15. 作“101”序列信号检测器的状态表,凡收到输入序列101时,输出为 1 ;并规定检测的101序列不重叠。

解:根据题意分析,输入为二进制序列x,输出为Z;且电路应具有3个状态:

S0、S1、S2。

列状态图和状态表如下:

(3)得状态方程、激励方程

17. 对状态表进行编码,并做出状态转移表,用D触发器和与非门实现。

解:{B,F},{D,E}为等价状态,化简后的状态表为

若状态编码A=00,B =01,C=10,D=11,则 电路的状态方程和输出方程为

18. 某时序机状态图如下图所示。

请用“一对一法”设计其电路解: 19.某时序机状态图如下所示,用“计数器法”设计该电路 解:

若编码为: S0=00 S1=01 S2=11 S3=10: 则

次态方程为:

n

n

n

n

n n n n Q Q KQ Q K Q KQ Q K Q 21211

22

111

++=+=++。