桂林电子科技大学试题

2010-2011 学年第一学期

课程名称:电子设计自动化(A卷)适用班级:2008级本科

学号姓名机号

一、考试要求:1.本次考试为开卷上机考试,考试时间为120分钟。考试完成后将试卷留于桌面上。

2.考生应严格按照各项题意要求作题,如在题意要求的路径下没有考生文件,将视为白卷。

3.画图过程中请注意及时存档,以免文件意外丢失!由于误操作引起的死机由考生自己负责。

二、考试内容:

1.(5分)在E:\盘下新建一文件夹F:\□□□□□□□□□□,其中□□□□□□□□□□为考生学号。然后启动Protel 99并新建一设计项目文件test.DDB,存放于F:\□□□□□□□□□□\文件夹下。

2.(5分)在Documents文件夹中新建一原理图文件,将其命名为test1.SCH,同时将原理图幅面大小设置为650×550(自定义),按照所提供原理图进行编辑。

3.(10分)在Documents文件夹中新建原理图库文件,将其命名为test2.Lib,在原理图中T1和IC1是库中没有的,在test2.lib中做出T1和IC1两个元件,注意不要改动99se系统所带的库。并把做好的库添加到做原理图的操作库中(注意IC1为分部分元件,分六部分,电源14、地脚7为引藏脚。)

4.(10分)在原理图中所有电阻封装为AXIAL0.3, 电容为RAD0.2, 电解电容为RB.2/.4, 二极管为RB.2/.4, 三极管为TO-92A, IC1为DIP14, T1为GYB(需自己做封装),PLUG为PLUG(实验时所做)。原理图完成后,利用整体修改将所有电阻封装改为AXIAL0.5,并将原理图另存为:test3.sch,

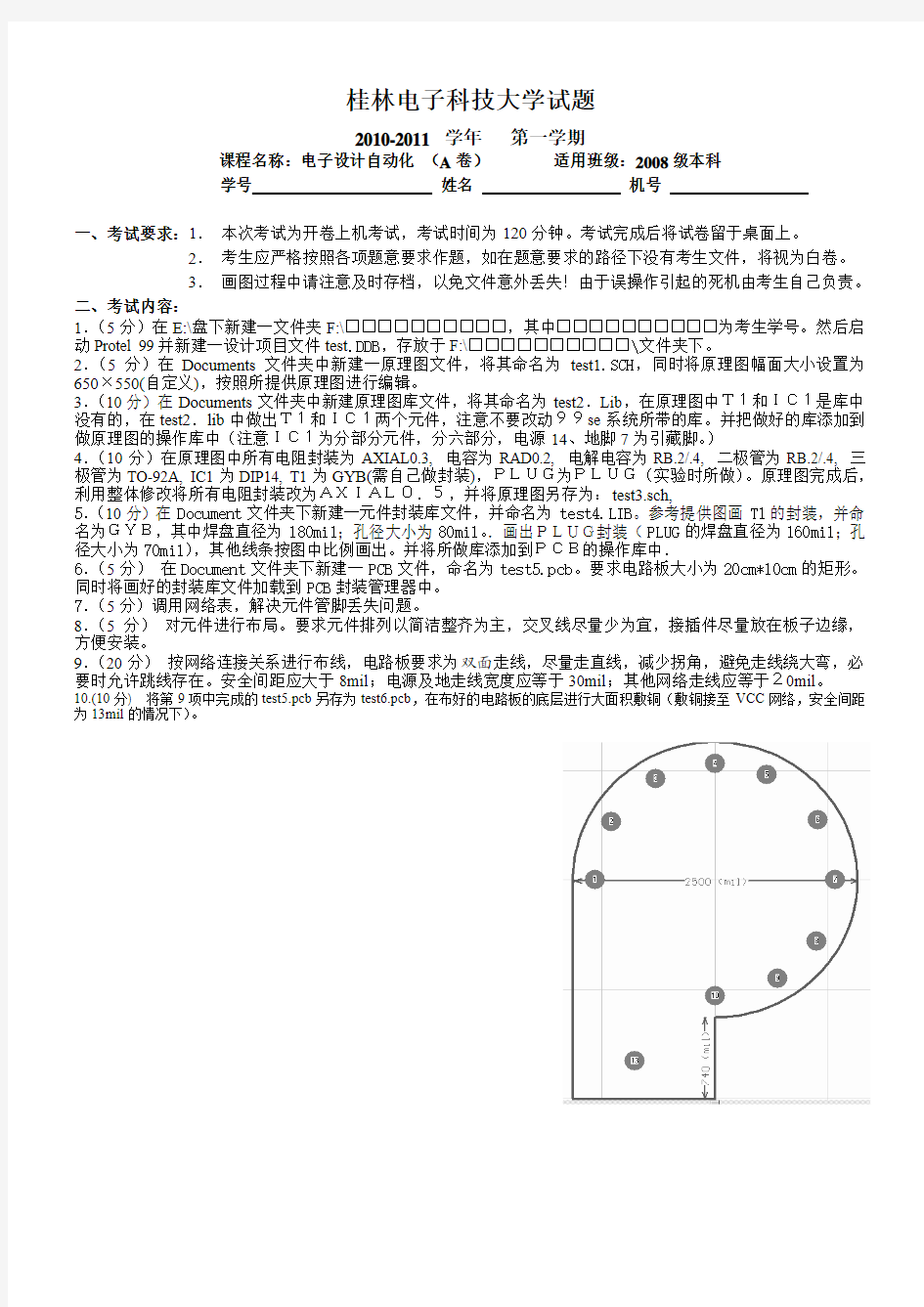

5.(10分)在Document文件夹下新建一元件封装库文件,并命名为test4.LIB。参考提供图画T1的封装,并命名为GYB,其中焊盘直径为180mil;孔径大小为80mil。.画出PLUG封装(PLUG的焊盘直径为160mil;孔径大小为70mil),其他线条按图中比例画出。并将所做库添加到PCB的操作库中.

6.(5分)在Document文件夹下新建一PCB文件,命名为test5.pcb。要求电路板大小为20cm*10cm的矩形。同时将画好的封装库文件加载到PCB封装管理器中。

7.(5分)调用网络表,解决元件管脚丢失问题。

8.(5分)对元件进行布局。要求元件排列以简洁整齐为主,交叉线尽量少为宜,接插件尽量放在板子边缘,方便安装。

9.(20分)按网络连接关系进行布线,电路板要求为双面走线,尽量走直线,减少拐角,避免走线绕大弯,必要时允许跳线存在。安全间距应大于8mil;电源及地走线宽度应等于30mil;其他网络走线应等于20mil。

10.(10分) 将第9项中完成的test5.pcb另存为test6.pcb,在布好的电路板的底层进行大面积敷铜(敷铜接至VCC网络,安全间距为13mil的情况下)。

quartusII部分(40分)

1.在学号文件夹内新建quartusII文件夹

2.题目要求如下:

①新建一个以“kaoshi”命名的工程文件。

②定义器件型号为EPF10K10LC84-4。

③在工程文件下建立一个dfq的顶层实体文件,采用Verilog语言编写一个D触发器程序,要求如下:

A、输入信号为d,时钟触发信号为clk,输出信号为q(同相输出端)和nq(反相输出端)

B、触发器采用时钟下降沿进行触发

④在同一工程文件下建立一个comp的顶层实体文件,采用Verilog语言编写一个1位的数据比较器程序,要求如下:

A、输入信号为a和b(均为1位二进制数),输出信号为y

B、当a=b时,输出信号y=0,否则y=1

⑤在同一工程文件下建立一个文件名为“ylt”的顶层原理图文件,在原理图上放置以上所生成的D触发器和数据比较器,按

照下图进行连接。

⑥在原理图上放置输入端口[端口名为:code和clk],输出端口[(端口名为:a、b、c和y)],按照下图进行连接。

⑦建立一个文件名为“ylt”的仿真文件对原理图进行波形仿真,仿真结束时间为1秒,单位时间长度为10ms,输入时钟信号

clk为20ms周期的时钟,code为50ms周期的随机信号,所有引脚均采用二进制方式显示。

Mutisim部分(20分)

1.在学号文件夹内新建mutisim文件夹

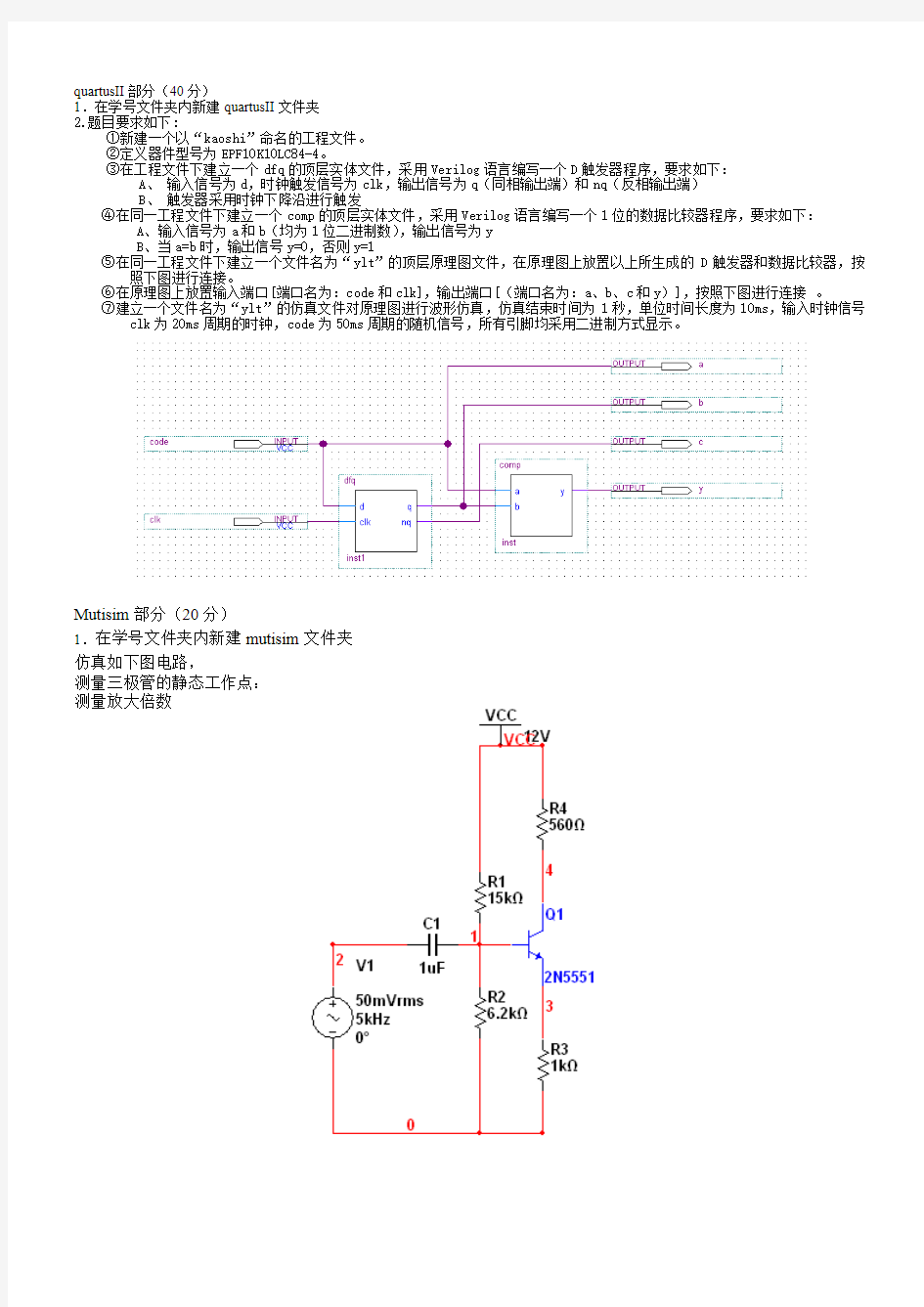

仿真如下图电路,

测量三极管的静态工作点:

测量放大倍数

桂林电子科技大学文件 桂电教﹝2008﹞9号 ??????????????????????! 第一条 根据《中华人民共和国学位条例》、《中华人民共和国学位条例暂行实施办法》,结合我校实际情况,制定本实施细则。 第二条 我校有学士学位授权的普通本科专业中,凡是拥护中国共产党的领导,拥护社会主义制度的毕业生,成绩优良,较好地掌握了本学科的基础理论、专门知识和基本技术,并具有从事科学研究工作或担负专门技术工作的初步能力的,可申请相应学科的学士学位。 第三条 学业成绩符合下列条件的,可授予学士学位。 (一)非艺术类及非英语专业本科毕业生符合下列条件之一者,可授予学士学位: 1、大学英语四级≥45分,学分绩达到70,并且两项之和≥125。 2、在校学习期间大学英语课程平均成绩达到75分,学分绩达到70。 (二)艺术类专业本科毕业生符合下列条件之一者,可授予学士学位: 1、大学英语三级(英语应用能力考试B级)≥45分,学分绩

达到70,并且两项之和≥125。 2、在校学习期间大学英语课程平均成绩达到75分,学分绩达到70。 (三)英语专业本科毕业生符合下列条件之一者,可授予学士学位: 1、英语专业四级≥45分,学分绩达到70,并且两项之和≥125。 2、在校学习期间第二外语课程平均成绩达到75分,学分绩达到70。 2005年6月以后参加大学英语四级考试的,按现行的大学英语四级标准分折合成百分制后计算英语四级成绩。计算学分绩和英语四级标准分折合成百分制时,均保留小数点后一位。 以上各单项成绩均含四舍五入。但在计算大学英语四级(大学英语三级、英语专业四级)和学分绩两项之和时,应按原已取得的保留小数点后一位的大学英语四级(大学英语三级、英语专业四级)和学分绩相加后再四舍五入,若两项之和大于等于125,方可授予学士学位。 第四条 有下列情况之一者,不能授予学士学位: 1、因考试作弊曾受过“留校察看”处分的; 2、结业后经补考或补作毕业设计(毕业论文)取得毕业证书的。 第五条 为鼓励学生积极参加各类学科性竞赛或各类发明、创新实践活动,对参加经学位评定委员会认定的项目获奖的学生,在计算其学士学位成绩时给予加分。 (一)竞赛项目 1、全国大学生电子设计竞赛、全国大学生数学建模竞赛、“挑战杯”全国大学生课外学术科技作品竞赛、全国大学生广告艺术大赛等。

桂林电子科技大学信息科技学院试卷 2009-2010 学年第 1 学期课号 课程名称单片机原理与应用技术( A卷; 笔试, 闭卷)适用班级(或年级、专业) 07级电信、信息 一、单项选择题(每小题3分,共45分) 1、 - 10的补码为()。 A: F5H B:F6H C:0AH D:0BH 2、单片机复位后的SP与P0的内容是()。 A:SP=00H,P0=00H B: SP=00H,P0=FFH C:SP=07H,P0=00H D:SP=07H,P0=FFH 3、单片机中WR的功能是选通是()。 A:片外数据RAM B:片内数据RAM C:片外程序ROM D:片内程序ROM 4、在下列指令中,正确的MCS-51单片机指令是()。 A:INC C B: ADD A,B C:SUB A , R2 D:MOVX @R2, A 5、能同时将TF0清零的跳转指令是()。 A:JB TF0,LOOP B:JBC TF0,LOOP C:JNB TF0,LOOP D:JZ LOOP 6、当R0的地址为10H时,PSW中的RS1、RS0两位是()。 A:00 B:01 C:10 D:11 7、片内没有上拉电阻的并口是()。 A:P3 B:P2 C:P1 D:P0 8、外部中断1的中断服务程序入口地址是()。 A:0003H B:000BH C:0013H D:0023H 9、用12MHz晶体时,T1做一次定时的最长时间为()。 A:256 μS B:512 μS C: 65536μS D:131072 μS 10、在串口控制寄存器SCON中,REN是()。

A:串行接收中断标志位B:串行接收允许位 C:串行发送中断标志位D:串行发送允许位 11、定时器T1的溢出中断标志是()。 A:IT1 B:TI C:TF1 D:IE1 12、EOC信号在ADC0809中起到的作用是() A.启动AD转换 C. ADC0809的片选信号 B. AD转换结束标志 D. 不能确定 13、已知(00H)= 06H, (01H) = 08H, 有这样的定义char data *p; 其中p = 0x01;则*p = () A.00H C.01H B.06H D.08H 14、已知C语言程序 p = 0x30; *p = 0x48与之等价的汇编语言程序为() A.MOV 30H,#48H C.MOV 30H,48H B.MOV 30H,#48 D.MOV 30H,48 15、DAC0832的工作方式不包括以下哪一种() A.直通C.单缓冲 B.双缓冲D.双极性 二、阅读程序填空(每小题5分,共25分) 1、设PSW=00H, R0=49H、B=0EDH,问:执行下列程序后PSW= ?R0= ?B= ? MOV SP, #6FH PUSH 0F0H PUSH 00H PUSH PSW POP PSW POP 0F0H POP 00H 2、分别写出若A=57H,执行下列程序后A= ?若A=0F2H, 执行下列程序后 A= ? CJNE A, #80H , LOOP1 ;

(A卷) 赣南师范学院 2010—2011学年第一学期期末考试试卷(A卷)(闭卷)年级 2008 专业电子科学与技术(本)课程名称 EDA技术基础 2、学生答题前将密封线外的内容填写清楚,答题不得超出密封线; 3、答题请用蓝、黑钢笔或圆珠笔。 一、单项选择题(30分,每题2分) 1.以下关于适配描述错误的是 B A.适配器的功能是将综合器产生的网表文件配置于指定的目标器件中,使之产生最终的下载文件 B.适配所选定的目标器件可以不属于原综合器指定的目标器件系列 C.适配完成后可以利用适配所产生的仿真文件作精确的时序仿真 D.通常,EDAL软件中的综合器可由专业的第三方EDA公司提供,而适配器则需由FPGA/CPLD供应商提供 2.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。 A.器件外部特性B.器件的综合约束 C.器件外部特性与内部功能D.器件的内部功能 3.下列标识符中, B 是不合法的标识符。 A.State0 B.9moon C.Not_Ack_0 D.signall 4.以下工具中属于FPGA/CPLD集成化开发工具的是 D A.ModelSim B.Synplify Pro C.MATLAB D.QuartusII 5.进程中的变量赋值语句,其变量更新是 A 。 A.立即完成B.按顺序完成 C.在进程的最后完成D.都不对 6.以下关于CASE语句描述中错误的是 A A.CASE语句执行中可以不必选中所列条件名的一条 B.除非所有条件句的选择值能完整覆盖CASE语句中表达式的取值,否则最末一个条件句的选择必须加上最后一句“WHEN OTHERS=><顺序语句>” C.CASE语句中的选择值只能出现一次 D.WHEN条件句中的选择值或标识符所代表的值必须在表达式的取值范围 7.以下哪个程序包是数字系统设计中最重要最常用的程序包 B A.STD_LOGIC_ARITH B.STD_LOGIC_1164 C.STD_LOGIC_UNSIGNED D.STD_LOGIC_SIGNED 8.基于EDA软件的FPGA / CPLD设计流程为:原理图/HDL文本输入→A →综合→适配→时序仿真→编程下载→硬件测试。 A.功能仿真B.逻辑综合C.配置D.引脚锁定 9.不完整的IF语句,其综合结果可实现 D A.三态控制电路B.条件相或的逻辑电路 C.双向控制电路D.时序逻辑电路 10.下列语句中,属于并行语句的是A A.进程语句B.IF语句C.CASE语句D.FOR语句11.综合是EDA设计流程的关键步骤,综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;在下面对综合的描述中, C 是错误的。 A.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件 B.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系不是唯一的 C.综合是纯软件的转换过程,与器件硬件结构无关 D.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束 12.CPLD的可编程是主要基于什么结构 D 。 A.查找表(LUT)B.ROM可编程 C.PAL可编程D.与或阵列可编程 13.以下器件中属于Altera 公司生产的是 B A.ispLSI系列器件B.MAX系列器件 C.XC9500系列器件D.Virtex系列器件 14.在VHDL语言中,下列对时钟边沿检测描述中,错误的是 D A.if clk'event and clk = '1' then B.if clk'stable and not clk = '1' then C.if rising_edge(clk) then D.if not clk'stable and clk = '1' then 15.以下关于状态机的描述中正确的是 B A.Moore型状态机其输出是当前状态和所有输入的函数 B.与Moore型状态机相比,Mealy型的输出变化要领先一个时钟周期C.Mealy型状态机其输出是当前状态的函数

武科大EDA系统设计试卷及答案 一、单项选择题:(20分) 1.IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为_____ D_____。 A .瘦IP B.固IP C.胖IP D.都不是 2.综合是EDA设计流程的关键步骤,在下面对综合的描述中,____ D _____是错误的。 A.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程; B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件; C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束; D.综合可理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。 3.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是__C__。 A. FPGA全称为复杂可编程逻辑器件; B. FPGA是基于乘积项结构的可编程逻辑器件; C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置; D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。 4.进程中的信号赋值语句,其信号更新是___C____。 A.按顺序完成; B.比变量更快完成; C.在进程的最后完成; D.都不对。 5. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述_____B______。 A.器件外部特性; B.器件的内部功能; C.器件的综合约束; D.器件外部特性与内部功能。 6.不完整的IF语句,其综合结果可实现____ A ____。 A. 时序逻辑电路 B. 组合逻辑电路 C. 双向电路 D. 三态控制电路 7.子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化_____ B____。 ①流水线设计②资源共享③逻辑优化④串行化⑤寄存器配平⑥关键路径法 A. ①③ ⑤ B. ②③④ C. ②⑤ ⑥ D. ①④⑥ 8.下列标识符中,_____B_____是不合法的标识符。 A. State0 B. 9moon C. Not_Ack_0 D.

桂林电子科技大学各专业与对应学院一览表学院专业名称 1院 机电工程学院机械设计制造及其自动化 机电工程学院电气工程及其自动化 机电工程学院机械电子工程 机电工程学院电子封装技术 2院 信息与通信学院通信工程 信息与通信学院电子信息工程 信息与通信学院电子科学与技术 信息与通信学院微电子科学与工程 信息与通信学院信息对抗技术 3院 计算机科学与工程学院计算机科学与技术 计算机科学与工程学院信息管理与信息系统 计算机科学与工程学院软件工程 计算机科学与工程学院信息安全 计算机科学与工程学院数字媒体技术 计算机科学与工程学院网络工程 计算机科学与工程学院物联网工程 4院 艺术与设计学院工业设计 艺术与设计学院产品设计 艺术与设计学院视觉传达设计 艺术与设计学院环境设计 艺术与设计学院服装与服饰设计 艺术与设计学院动画 艺术与设计学院书法学 5院 商学院会计学 商学院市场营销 商学院工业工程 商学院电子商务 商学院工商管理 商学院财务管理 商学院国际经济与贸易 商学院物流管理 商学院人力资源管理 6院 外国语学院英语

外国语学院日语 7院 数学与计算科学学院信息与计算科学 数学与计算科学学院统计学 数学与计算科学学院数学与应用数学 8院 电子工程与自动化学院测控技术与仪器 电子工程与自动化学院光电信息科学与工程电子工程与自动化学院电子信息科学与技术电子工程与自动化学院自动化 电子工程与自动化学院智能科学与技术 9院 法学院法学 法学院知识产权 10院 材料科学与工程学院材料科学与工程 材料科学与工程学院材料成型及控制工程 材料科学与工程学院应用物理学 材料科学与工程学院高分子材料与工程 11院 公共事务学院公共事业管理 公共事务学院行政管理 12院 生命与环境科学学院环境工程 生命与环境科学学院生物工程 生命与环境科学学院生物医学工程 13院 建筑与交通工程学院交通工程 建筑与交通工程学院建筑环境与能源应用工程建筑与交通工程学院土木工程 建筑与交通工程学院建筑电气与智能化 14院 国际学院汉语国际教育

EDA期末试卷 一、填空题 1.一般把EDA技术的发展分为MOS时代、CMOS 代和ASIC 三个阶段。 2.EDA设计流程包括设计输入、设计实现、实际设计检验和下载编程四个步骤。 3.EDA设计输入主要包括图形输入、HDL文本输入和状态机输入。 4.时序仿真是在设计输入完成之后,选择具体器件并完成布局、布线之后进行的时序关系仿真,因此又称为功能仿真。5.VHDL的数据对象包括变量、常量和信号,它们是用来存放各种类型数据的容器。 6.图形文件设计结束后一定要通过仿真,检查设计文件是否正确。 7.以EDA方式设计实现的电路设计文件,最终可以编程下载 到FPGA 和CPLD 芯片中,完成硬件设计和验证。 8.MAX+PLUS的文本文件类型是(后缀名).VHD 。9.在PC上利用VHDL进行项目设计,不允许在根目 录下进行,必须在根目录为设计建立一个工程目录(即文件夹)。

10.VHDL源程序的文件名应与实体名相同,否则无法通过编译。 二、选择题:。 11.在EDA工具中,能完成在目标系统器件上布局布线软件称为(C )A.仿真器 B.综合 器 C.适配器 D.下载器12.在执行MAX+PLUSⅡ的(D )命令,可以精确分析设计电路输入与输出波形间的延时量。 A .Create default symbol B. Simulator C. Compiler D. Timing Analyzer 13.VHDL常用的库是(A ) A. IEEE B.STD C. WORK D. PACKAGE 14.下面既是并行语句又是串行语句的是( C ) A.变量赋值 B.信号赋值 C.PROCESS语 句 D.WHEN…ELSE语句 15.在VHDL中,用语句(D )表示clock的下降沿。

桂林电子科技大学文件 桂电研〔2014〕10号 桂林电子科技大学 硕士学位授予工作实施细则 第一章 总 则 第一条 根据《中华人民共和国学位条例》、《中华人民共和国学位条例暂行实施办法》,结合学校实际情况,制定本实施细则。 第二条 学校按照国务院学位委员会批准的权限,具有硕士学位授予权的各学科、专业均可按照本细则授予相应学科门类的硕士学位。 第三条 学位授予工作,每年定期举行两次。

第二章 硕士学位授予的条件 第四条 学制与学习年限 硕士研究生学制为3年,学习优秀者可以申请提前毕业,特殊情况经批准可延迟毕业,但学习年限最短不低于2年、最长不超过5年。 研究生必须在规定的学习年限内申请和完成学位论文答辩,超过期限不受理论文答辩和学位申请,做结业或肄业处理。 第五条 课程学习考核要求 硕士研究生的课程学习应满足以下条件方可参加论文答辩:1.硕士研究生须在规定的学习年限内,修完培养计划规定的课程。 2.课程学习考核成绩合格,且学位课程考试成绩的加权平均不低于75分。 3.完成培养计划规定的各个环节,满足培养方案规定的学分要求。 学位课成绩未达到规定要求,但每门课的成绩合格并取得规定的总学分,完成必修环节者,可参加毕业论文答辩,答辩通过者,准予毕业,但不能申请学位。 第六条 学术活动要求 硕士研究生在学期间,必须参加10次以上(含10次)学术活动,包括学术报告、讲座等。

第七条 科研成果要求 为提高研究生培养质量,在研究生学习期间,研究生须参与科研工作并完成学位论文工作。因此,硕士研究生在论文答辩前必须达到下列条件之一,方可参加学位论文答辩: 1.结合导师正式立项国防保密科研项目撰写并提交该项目《技术报告》,并需经课题组认定同意。 2.作为项目负责人完成1项研究生教育创新项目并通过验收。 3.结合导师正式立项科研项目,参与完成与学位论文有关并经过鉴定或验收的科研成果1项(省部级及以上排序为前8名,其他排名要求前5名),且桂林电子科技大学必须为署名单位之一。 4.以桂林电子科技大学为第一署名单位,并以第一作者或第二作者(导师是第一作者)身份在学校科技处认定的中文核心期刊及以上学术期刊(增刊除外)或桂林电子科技大学学报(增刊除外)或高水平学术会议(SCI、EI、ISTP检索) 发表(或已录用)1篇以研究生学位论文工作成果为主要内容的学术论文。录用论文须提交相关的录用证明和版面费付款证明。 5.作为主要人员获得与学位论文有关的专利(排序为前2名)或软件著作权(排序为前2名)1项(须已公开),且桂林电子科技大学必须为署名单位之一,每项专利成果只能使用1

桂林电子科技大学试卷 2009-2010 学年第 2 学期课号 课程名称c语言程序设计A(B卷; 开、闭卷)适用班级(或年级、专业)7院09级 考试时间120 分钟班级学号姓名 题号一二三四五六七八九十成绩满分 得分 评卷人 一、单选题(每空2分,共50分) 1、以下所列的C语言常量中,错误的是()。 A) 0xFF B) 1.2e0.5 C) 2L D) '\72' 2、以下4组用户定义标识符中,全部合法的一组是()。 A) _main B) If C) txt D) int Enclude -max REAL k_2 sin turbo 3COM _001 3、若有定义:int a=8, b=5, c;执行语句c = a/b+0.4 ;后,c的值为()。 A) 1.4 B) 1 C) 2.0 D) 2 4、以下程序中,while 循环的次数是()。 #include

班级 学号 姓名 密 封 线 内 不 得 答 题 一、单项选择题(30分) 1.以下描述错误的是 C A .QuartusII 是Altera 提供的FPGA/CPLD 集成开发环境 B .Altera 是世界上最大的可编程逻辑器件供应商之一 C .MAX+plusII 是Altera 前一代FPGA/CPL D 集成开发环境QuartusII 的更新换代新产品 D .QuartusII 完全支持VHDL 、Verilog 的设计流程 2.以下工具中属于FPGA/CPLD 开发工具中的专用综合器的是 B A .ModelSim B .Leonardo Spectrum C .Active HDL D .QuartusII 3.以下器件中属于Xilinx 公司生产的是 C A .ispLSI 系列器件 B .MAX 系列器件 C .XC9500系列器件 D .FLEX 系列器件 4.以下关于信号和变量的描述中错误的是 B A .信号是描述硬件系统的基本数据对象,它的性质类似于连接线 B .信号的定义范围是结构体、进程 C .除了没有方向说明以外,信号与实体的端口概念是一致的 D .在进程中不能将变量列入敏感信号列表中 5.以下关于状态机的描述中正确的是 B A .Moore 型状态机其输出是当前状态和所有输入的函数 B .与Moore 型状态机相比,Mealy 型的输出变化要领先一个时钟周期 C .Mealy 型状态机其输出是当前状态的函数 D .以上都不对 6.下列标识符中, B 是不合法的标识符。 A .PP0 B .END C .Not_Ack D .sig 7.大规模可编程器件主要有FPGA 、CPLD 两类,下列对CPLD 结构与工作原理的描述中,正确的是 C 。 A .CPLD 即是现场可编程逻辑器件的英文简称 B .CPLD 是基于查找表结构的可编程逻辑器件 C .早期的CPL D 是从GAL 的结构扩展而来 D .在Altera 公司生产的器件中,FLEX10K 系列属CPLD 结构 8.综合是EDA 设计流程的关键步骤,在下面对综合的描述中, D 是错误的。 A .综合就是把抽象设计层次中的一种表示转化成另一种表示的过程 B .综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD 的基本结构相映射的网表文件 C .为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束 D .综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的) 9.嵌套使用IF 语句,其综合结果可实现 A 。 A .带优先级且条件相与的逻辑电路 B .条件相或的逻辑电路 C .三态控制电路 D .双向控制电路 10.在VHDL 语言中,下列对时钟边沿检测描述中,错误的是 D 。 A .if clk'event and clk = ‘1’ then B .if falling_edge(clk) then C .if clk’event and clk = ‘0’ then D .if clk’stable and not clk = ‘1’ then 11.下列那个流程是正确的基于EDA 软件的FPGA / CPLD 设计流程 B A .原理图/HDL 文本输入→适配→综合→功能仿真→编程下载→硬件测试 B .原理图/HDL 文本输入→功能仿真→综合→适配→编程下载→硬件测试 C .原理图/HDL 文本输入→功能仿真→综合→编程下载→→适配硬件测试; D .原理图/HDL 文本输入→功能仿真→适配→编程下载→综合→硬件测试 12.在VHDL 语言中,下列对进程(PROCESS )语句的语句结构及语法规则的描述中,正确的是 A 。 A .PROCESS 为一无限循环语句;敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动 B .敏感信号参数表中,应列出进程中使用的所有输入信号 C .进程由说明部分、结构体部分、和敏感信号参数表三部分组成 D .当前进程中声明的变量也可用于其他进程 13.下列语句中,不属于并行语句的是 B A .进程语句 B .CAS E 语句 C .元件例化语句 D .WHEN …ELSE …语句 14.VHDL 语言共支持四种常用库,其中哪种库是用户的VHDL 设计现行工作 库 D A .IEEE 库 B .VITAL 库 C .STD 库 D .WORK 库 15.VHDL 语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述 D 。 A .器件外部特性 B .器件的综合约束 C .器件外部特性与内部功能 D .器件的内部功能 二、EDA 名词解释,写出下列缩写的中文含义(10分) 1.CPLD :复杂可编程逻辑器件 2.ASIC :专用集成电路 3.LUT :查找表 4.EDA :电子设计自动化 5.ROM :只读存储器 三、程序填空题(20分) 以下是一个模为24(0~23)的8421BCD 码加法计数器VHDL 描述,请补充完整

2007 至2008学年度第二学期期末考核 《EDA》试题(开卷) 卷号:B 时间:120 分钟 2008 年6 月 专业:电子信息工程学号:姓名: 一填空题(20分) 1、VHDL 2、DEVICE.LIB SYMBOLS.LIB 3、实际零件焊接到电路板时所指示的外观和焊点的位置 4、电子设计自动化电子CAD技术 5、A L T E R A,X I L I N X 6、WAIT 7、电路连接 8、SRAM-BASE 9、2.54mm 300mil 10、元件外观和元件引线端子的图形 二名词解释(20分) 1 PLD/FPGA PLD是可编程逻辑器件(Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field Programable Gate Array)的简称,两者的功能基本相同,只是实现原理略有不同,所以我们有时可以忽略这两者的区别,统称为可编程逻辑器件或PLD/FPGA。 2.过孔 当需要连接两个层面上的铜膜走线时就需要过孔(Via),过孔 又称为贯孔、沉铜孔和金属化孔。 过孔分为穿透式(Through)、半隐藏式(Blind)和隐藏式(Buried) 3.铜膜线 就是连接两个焊盘的导线,称为Track,一般铜膜线走线在不 同层面取不同的走向,例如顶层走水平线,则底层走垂直线。顶 层和底层走线之间的连接采用过孔(Via)连接。 4 PROM、PAL和PLA PROM:与阵列固定,或阵列可编程,一般用作存储器,其输入为存储器的地址,输出为存储器单元的内容。但输入的数目太大时,器件功耗增加,其局限性大。 PLA:与或阵列均可编程,但是其慢速特性和相对PAL、PROM而高得多的价格妨碍了它被广泛使用。PAL:或阵列固定,与阵列可编程,其第二代产品GAL具有了可电擦写、可重复编程、可设置加密的功能。 5 自顶向下的/自下而上的设计方法 自下而上的设计方法,使用该方法进行硬件设计是从选择具体元器件开始,并用这些元器件进行逻辑电路设计,从而完成系统的硬件设计,然后再将各功能模块连接起来,完成整个系统的硬件设计,自顶向下的设计方法就是从系统的总体要求出发,自顶向下分三个层次对系统硬件进行设计。 第一个层次是行为描述第二个层次是数据流描述第三个层次为逻辑综合

毕业论文 题目:中小企业财务管理的现状,问题及对策院(系):成人教育学院 专业:会计学 学生姓名:吴明婵 班级:20112497511 学号:2011249751135 指导教师:黄琨 2013年03月16日

中小企业是国民经济的重要组成部分,对经济发展和社会稳定起着举足轻重的促进作用。由于国家政策及企业自身方面的问题,中小企业在财务管理上主要存在筹资渠道窄、资金严重不足、经营者财务管理意识淡薄、企业财务核算制度不健全等问题。为了更好地发挥中小企业的作用,在此建议采取国家出台相关政策、拓展融资渠道、严格财务管理、加强外部监管力度、引进职业经理队伍等措施,提高中小企业的经营管理水平。我国中小企业在国民经济和社会成长中发挥着不可替代的作用,因此,我国中小企业不仅满足人们的多样化需要、培养企业家、进行技术创新、参与专业协作等方面发挥重要作用,而且对国家的稳定、社会的和谐、经济的繁荣发展做出了极其重要的贡献。分析中小企业财务管理中存在的问题并探讨解决问题的对策,以促进中小企业的改革与发展,是当前会计界需要思考和解决的问题。 关键词:中小企业;财务管理;财务问题;对策

引言 (1) 1中小企业财务管理现状 (1) 1.1中小企业融资现状 (1) 1.2内部因素影响 (2) 1.3外部因素影响 (2) 2中小企业财务管理存在的问题 (3) 2.1中小企业财务管理中遇到的问题 (3) 2.2中小企业财务管理问题的原因分析 (4) 2.3缺乏明确的产业发展方向,对项目投资缺乏科学论证 (4) 2.4财务风险意识淡薄,企业始终在高风险区运行 (5) 2.5财务控制薄弱 (5) 2.6财务会计工作流程不规范、不严格 (5) 3解决中小企业财务管理问题的具体途径 (6) 3.1解决财务管理问题的对策分析 (6) 3.2严格财务控制 (7) 3.3积极推进产权改革 (7) 3.4经营者必须树立理财观念 (7) 3.5建立财务管理制度 (8) 3.6提高会计人员的素质 (8) 3.7财务资金管理活动的外包 (8) 结论 (9) 参考文献 (10) 致谢 (11) 附录 (12)

桂林电子科技大学应用科技学院试卷 课程名称工程力学(闭卷) 题号一二三四五六七八九十成绩满分30 10 30 30 100 得分 (注:请将答案直接写在试卷上,写在其它纸上无效。) 一、填空题(30分,每空1.5分) 1. 作用于刚体上的二力,使刚体保持平衡状态的必要与充分条件是:此二 力大小______、方向______、且在________; 2. 力偶对刚体的(平动或旋转)______运动不会产生任何影响,力与力偶相互(能或不能)______平衡; 3. 力偶的三要素是______、______、______; 4. 平面汇交力系平衡的几何条件是_____________________________; 5. 二矩式方程∑Y=0,∑M A(F)=0,∑M B(F)=0 的使用补充条件为 __________________________; 6. 静不定指的是____________________________________; 7. 平面三力汇交定理是指________________________________________; 8. 约束基本类型为______、______、______、______; 9. 摩擦按运动类型可分为______、______、______; 10. 倾角为α的斜面,其最大静摩擦系数为fs,则其自锁条件为______; 二、是非题(10分,每题1分) 1. 二力杆指的是直杆(); 2. 约束反力总是与其所能阻碍的物体的运动方向相反(); 3. 力系平衡的几何条件是具有封闭的力的多边形(); 4. 力偶是一对平行力(); 5. 力对点的矩在某轴上的投影就是力对该轴的矩(); 6. 桁架分析时其中所有杆件都是二力杆(); 7.一般情况下,摩擦系数排序为fs≥fd≥δ(); 8. 分力就是投影(); 9. 作用与反作用力是一对平衡力(); 10. 柔性体约束的约束反力总是指向受力体()。 三、作图题(30分,每题10分) 1.作下图所示各构件的受力图,并用几何法求解约束反力。

1.一个项目的输入输出端口是定义在( A )1-5 ACDCD 6-10 CCACA A. 实体中;. B. 结构体中; C. 任何位置; D. 进程中。 2. MAXPLUS2中编译VHDL源程序时要求( C ) A. 文件名和实体可以不同名; B. 文件名和实体名无关; C. 文件名和实体名要相同; D. 不确定。 3. VHDL语言中变量定义的位置是(D ) A. 实体中中任何位置; B. 实体中特定位置; C. 结构体中任何位置; D. 结构体中特定位置。 4.可以不必声明而直接引用的数据类型是(C ) A. STD_LOGIC ; B. STD_LOGIC_VECTOR; C. BIT; D. ARRAY。 5. MAXPLUS2不支持的输入方式是(D ) A 文本输入;.B. 原理图输入;C. 波形输入;D. 矢量输入。 6.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是( C ) A. FPGA全称为复杂可编程逻辑器件; B. FPGA是基于乘积项结构的可编程逻辑器件; C. 基于SRAM的FPGA器件,在每次上电后必须进行一次配置; D. 在Altera公司生产的器件中,MAX7000系列属FPGA结构。 7.下面不属于顺序语句的是( C ) A. IF语句; B. LOOP语句; C. PROCESS语句; D. CASE语句。 8. VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,实体体描述的是( A ) A. 器件外部特性; B. 器件的内部功能; C. 器件的综合约束; D. 器件外部特性与内部功能。 9. 进程中的信号赋值语句,其信号更新是( C ) A. 按顺序完成; B. 比变量更快完成; C. 在进程的最后完成; D. 都不对。 10. 嵌套使用IF语句,其综合结果可实现:(A ) A. 带优先级且条件相与的逻辑电路; B. 条件相或的逻辑电路; C. 三态控制电路; D. 双向控制电路。 一、单项选择题:(20分) 1. IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述

这是长期总结的EDA期末考试试题 试题一 1-2与软件描述语言相比,VHDL有什么特点? P6 答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。 l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么? P5 什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。 有哪些类型? 答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。 (2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。 (3)从RTL级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。 (4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。 综合在电子设计自动化中的地位是什么? 答:是核心地位(见图1-3)。综合器具有更复杂的工作环境,综合器在接受VHDL程序并准备对其综合前,必须获得与最终实现设计电路硬件特征相关的工艺库信息,以及获得优化综合的诸多约束条件信息;根据工艺库和约束条件信息,将VHDL程序转化成电路实现的相关信息。 1-4在EDA技术中,自顶向下的设计方法的重要意义是什么? P7~10 答:在EDA技术应用中,自顶向下的设计方法,就是在整个设计流程中各设计环节逐步求精的过程。 1-5 IP在EDA技术的应用和发展中的意义是什么? P11~12 答:IP核具有规范的接口协议,良好的可移植与可测试性,为系统开发提供了可靠的保证。 2-1 叙述EDA的FPGA/CPLD设计流程。 P13~16 答:1.设计输入(原理图/HDL文本编辑);2.综合;3.适配;4.时序仿真与功能仿真;5.编程下载;6.硬件测试。 2-2 IP是什么?IP与EDA技术的关系是什么? P24~26 IP是什么? 答:IP是知识产权核或知识产权模块,用于ASIC或FPGA/CPLD中的预先设计好的电路功能模块。 IP与EDA技术的关系是什么? 答:IP在EDA技术开发中具有十分重要的地位;与EDA技术的关系分有软IP、固IP、硬IP:软IP是用VHDL等硬件描述语言描述的功能块,并不涉及用什么具体电路元件实现这些功能;软IP通常是以硬件描述语言HDL源文件的形式出现。固IP是完成了综合的功能块,具有较大的设计深度,以网表文件的形式提交客户使用。硬IP提供设计的最终阶段产品:掩模。 3-1 OLMC(输出逻辑宏单元)有何功能?说明GAL是怎样实现可编程组合电路与时序电路的。 P34~36 答:OLMC单元设有多种组态,可配置成专用组合输出、专用输入、组合输出双向口、寄存器输出、寄存器输出双向口等。 说明GAL是怎样实现可编程组合电路与时序电路的? 答:GAL(通用阵列逻辑器件)是通过对其中的OLMC(输出逻辑宏单元)的编程和三种模式配置(寄存器模式、复合模式、简单模式),实现组合电路与时序电路设计的。 3-2 什么是基于乘积项的可编程逻辑结构? P33~34,40 答:GAL、CPLD之类都是基于乘积项的可编程结构;即包含有可编程与阵列和固定的或阵列的PAL(可编程阵列逻辑)器件构成。 3-3 什么是基于查找表的可编程逻辑结构? P40~41 答:FPGA(现场可编程门阵列)是基于查找表的可编程逻辑结构。 3-7 请参阅相关资料,并回答问题:按本章给出的归类方式,将基于乘积项的可编程逻辑结构的PLD器件归类为CPLD;将基于查找表的可编程逻辑结构的PLD器什归类为FPGA,那么,APEX系列属于什么类型PLD器件? MAX II系列又属于什么类型的PLD器件?为什么? P54~56 答:APEX(Advanced Logic Element Matrix)系列属于FPGA类型PLD器件;编程信息存于SRAM中。MAX II系列属于CPLD类型的PLD器件;编程信息存于EEPROM中。 4-3. 图3-31所示的是双2选1多路选择器构成的电路MUXK,对于其中MUX21A,当s='0'和'1'时,分别有y<='a'和y<='b'。试在一个结构体中用两个进程来表达此电路,每个进程中用CASE语句描述一个2选1多路选择器MUX21A。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY MUX221 IS PORT(a1,a2,a3:IN STD_LOGIC_VECTOR(1 DOWNTO 0); --输入信号 s0,s1:IN STD_LOGIC; outy:OUT STD_LOGIC);--输出端 END ENTITY; ARCHITECTURE ONE OF MUX221 IS SIGNAL tmp : STD_LOGIC; BEGIN

桂林电子科技大学2016年毕业生就业质量年度报告一、学校简介 桂林电子科技大学是全国四所电子科技大学之一,是工业和信息化部与广西壮族自治区共建高校,广西壮族自治区重点建设高校。中国绕月探测工程总设计师、国家最高科学技术奖获得者、中国科学院孙家栋院士为学校名誉校长。 学校始建于1960年,1980年经国务院批准成立桂林电子工业学院,2006 年更名为桂林电子科技大学。学校先后隶属于第四机械工业部、电子工业部、机械电子工业部、中国电子工业总公司、信息产业部。2000年管理体制转为中央与地方共建、以地方管理为主。1990年,时任中共中央总书记江泽民同志亲临学校视察,并为学校亲笔题词“为发展电子工业培养更多的合格人才”。 学校现有金鸡岭校区、六合路校区、花江校区、北海校区(高职),分别位于桂林国家高新技术开发区、桂林市尧山风景区、北海市银海区,校园总面积4153亩。学校图书馆建筑面积4.5万余平方米。馆藏纸质图书186.4万册、电子图书150.8万种、高品质外文学术数据库32个、中文数据库42个、中外文期刊(含电子期刊)34997种。具有先进的网络信息平台和智慧校园平台。 学校开设有本科专业63个,其中,国家综合改革试点专业1个、国家级特色专业5个,通过工程教育认证专业1个;现有国家级精品课程3门、国家级双语教学示范课程1门、国家级精品资源共享课2门。学校获得“十一五”和“十二五”国家级规划教材9种。学校获得高等教育国家级教学成果奖4项。学校现有博士后科研流动站1个;一级学科博士学位授权点3个;一级学科硕士学位授权点11个、一级学科未覆盖的二级学科硕士学位授权点3个;工程、工商管理、会计、法律、翻译等5个硕士专业学位授权点,其中,工程硕士授权领域11个。 学校是教育部卓越工程师教育培养计划高校、国家大学生创新性实验计划实施高校、教育部大学英语教学改革示范点学校,学校是国防生培养单位、全军边防军人子女预科生培养单位。现有国家人才培养模式创新实验区1个、国家级实验教学示范中心5个、国家级工程实践教学中心2个、国家级大学生校外实践教育基地1个;全国首批大学生“小平科技创新团队”1个;全国学校共青团新媒体运营中心专业工作室支持单位1个;教育部大学生网络文化工作室1个。 学校承担了国家科技重大支撑计划项目、国家“973”重点项目、国家863计划重大项目、国家自然科学基金重点项目、国家自然科学基金重大仪器专项、国家自然科学基金面上项目、国家重点研发计划、国家社会科学基金特别委托项目等。近五年,新增国家级科研项目306项;发表SCI、EI收录论文2060篇,出版学术著作112部。学校长期从事国防科学研究,是总装备部通信装备预研项目定向发布的30所高校之一和北斗ICD授权的高校之一。承担了军队“973计划”、

桂林电子科技大学信息科技学院试卷2009-2010 学年第1 学期课号 课程名称单片机原理与应用技术(A卷; 笔试, 闭卷)适用班级(或年级、专业)07级电信、信息 一、单项选择题(每小题3分,共45分) 1、- 10的补码为()。 A: F5H B:F6H C:0AH D:0BH 2、单片机复位后的SP与P0的内容是()。 A:SP=00H,P0=00H B: SP=00H,P0=FFH C:SP=07H,P0=00H D:SP=07H,P0=FFH 3、单片机中WR的功能是选通是()。 A:片外数据RAM B:片内数据RAM C:片外程序ROM D:片内程序ROM 4、在下列指令中,正确的MCS-51单片机指令是()。 A:INC C B:ADD A,B C:SUB A , R2 D:MOVX @R2, A 5、能同时将TF0清零的跳转指令是()。 A:JB TF0,LOOP B:JBC TF0,LOOP C:JNB TF0,LOOP D:JZ LOOP 6、当R0的地址为10H时,PSW中的RS1、RS0两位是()。 A:00 B:01 C:10 D:11 7、片内没有上拉电阻的并口是()。 A:P3 B:P2 C:P1 D:P0 8、外部中断1的中断服务程序入口地址是()。 A:0003H B:000BH C:0013H D:0023H 9、用12MHz晶体时,T1做一次定时的最长时间为()。 A:256 μS B:512 μS C:65536μS D:131072 μS 10、在串口控制寄存器SCON中,REN是()。

A:串行接收中断标志位B:串行接收允许位 C:串行发送中断标志位D:串行发送允许位 11、定时器T1的溢出中断标志是()。 A:IT1 B:TI C:TF1 D:IE1 12、EOC信号在ADC0809中起到的作用是() A.启动AD转换 C. ADC0809的片选信号 B.AD转换结束标志 D. 不能确定 13、已知(00H)= 06H, (01H) = 08H, 有这样的定义char data *p; 其中p = 0x01;则*p = () A.00H C.01H B.06H D.08H 14、已知C语言程序p = 0x30; *p = 0x48与之等价的汇编语言程序为() A.MOV 30H,#48H C.MOV 30H,48H B.MOV 30H,#48 D.MOV 30H,48 15、DAC0832的工作方式不包括以下哪一种() A.直通C.单缓冲 B.双缓冲D.双极性 二、阅读程序填空(每小题5分,共25分) 1、设PSW=00H, R0=49H、B=0EDH,问:执行下列程序后PSW= ?R0= ?B= ? MOV SP, #6FH PUSH 0F0H PUSH 00H PUSH PSW POP P SW POP 0F0H POP 00H 2、分别写出若A=57H,执行下列程序后A= ?若A=0F2H, 执行下列程序后 A= ? CJNE A, #80H , LOOP1 ; LJMP NEXT