原理图checklist

- 格式:doc

- 大小:141.50 KB

- 文档页数:12

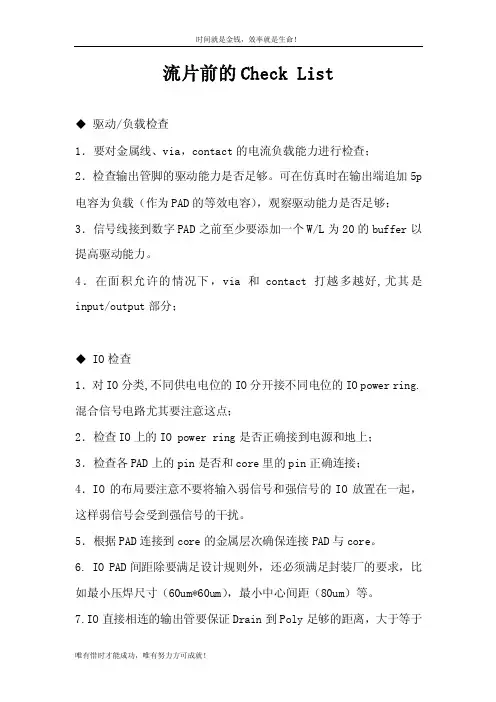

流片前的Check List◆驱动/负载检查1.要对金属线、via,contact的电流负载能力进行检查;2.检查输出管脚的驱动能力是否足够。

可在仿真时在输出端追加5p 电容为负载(作为PAD的等效电容),观察驱动能力是否足够;3.信号线接到数字PAD之前至少要添加一个W/L为20的buffer以提高驱动能力。

4.在面积允许的情况下,via和contact打越多越好,尤其是input/output部分;◆IO检查1.对IO分类,不同供电电位的IO分开接不同电位的IO power ring.混合信号电路尤其要注意这点;2.检查IO上的IO power ring是否正确接到电源和地上;3.检查各PAD上的pin是否和core里的pin正确连接;4.IO的布局要注意不要将输入弱信号和强信号的IO放置在一起,这样弱信号会受到强信号的干扰。

5.根据PAD连接到core的金属层次确保连接PAD与core。

6. IO PAD间距除要满足设计规则外,还必须满足封装厂的要求,比如最小压焊尺寸(60um*60um),最小中心间距(80um)等。

7.IO直接相连的输出管要保证Drain到Poly足够的距离,大于等于1.5um为宜,或者加上SAB层,以保证足够的ESD可靠性。

8.数字要通过带IO的后仿真,防止发生IO上使能端的连接错误。

9.从自动布局布线软件(如Astro)导出GDS文件,再导入Virtuso 做DRC前,要将版图中得IO替换为Foundry(如smic)提供的完整的IO gds文件导出来的IO库单元中的IO(包括PADFILLER),防止出现额外的逻辑操作层,如HTNWL。

走线检查1.金属连线不宜过长,如果不得已需要长连线可以在中间添加buffer 提高驱动能力;2.数字电路的走线不要经过模拟电路的器件,否则容易引入强干扰,影响模拟电路正常工作。

反之模拟电路走线也不要经过数字电路。

3.数模混合信号电路中模拟电路外边最好加入隔离环,必要时需要用单独的管脚为隔离环接地或接电源电压。

关于模拟设计的基本考虑Basic Precautions and Tips that an Analog Designer Should Know.很多时候,我们在初期设计或者优化电路时,满脑子想的都是性能如何能一点一点提高,而忽略了所谓的模拟设计的一些基本考虑;待到版图设计时已经晚矣。

那个时候再去修改基本设计无疑是不值得,要么耗费精力,要们前功尽弃。

作为教训,如果我们能够在设计初期,就带着这些基本考虑,那么在选择基本器件的时候,就会有的放矢,知道一个大概的合理的选取范围,有利于版图设计和优化。

1. Minimum channel length of the transistor should be four to five times the minimum feature size of the process. We do it, to make the lambda of the transistor low i.e. the rate of change of Id w.r.t to Vds is low.晶体管最小沟长为工艺最小特征尺寸的4-5倍,用来减小沟长调制效应。

2. Present art of analog design still uses the transistor in the saturation region. So one should always keep Vgs of the Transistor 30% above the Vt.目前模拟设计仍然是使晶体管工作在饱和区,故应使Vgs大于Vt约30%。

3. One should always split the big transistor into small transistors having width or length feature size < or = 15um.应把大管分成小晶体管,使其宽/长特征尺寸<或=15um。

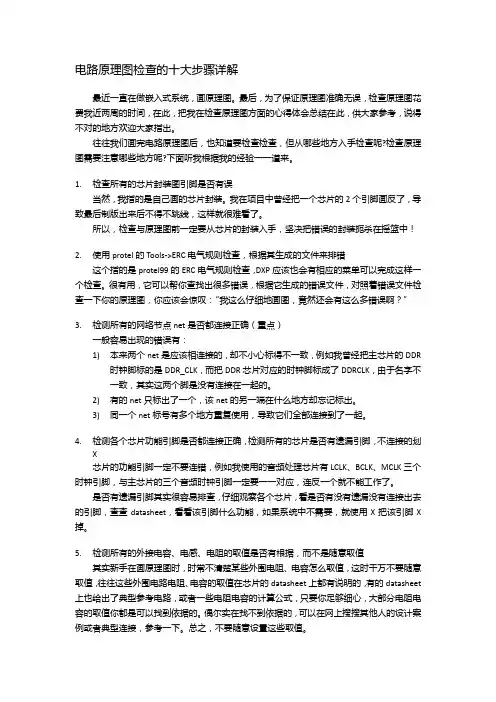

电路原理图检查的十大步骤详解最近一直在做嵌入式系统,画原理图。

最后,为了保证原理图准确无误,检查原理图花费我近两周的时间,在此,把我在检查原理图方面的心得体会总结在此,供大家参考,说得不对的地方欢迎大家指出。

往往我们画完电路原理图后,也知道要检查检查,但从哪些地方入手检查呢?检查原理图需要注意哪些地方呢?下面听我根据我的经验一一道来。

1.检查所有的芯片封装图引脚是否有误当然,我指的是自己画的芯片封装。

我在项目中曾经把一个芯片的2个引脚画反了,导致最后制版出来后不得不跳线,这样就很难看了。

所以,检查与原理图前一定要从芯片的封装入手,坚决把错误的封装扼杀在摇篮中!2.使用protel的Tools->ERC电气规则检查,根据其生成的文件来排错这个指的是protel99的ERC电气规则检查,DXP应该也会有相应的菜单可以完成这样一个检查。

很有用,它可以帮你查找出很多错误,根据它生成的错误文件,对照着错误文件检查一下你的原理图,你应该会惊叹:“我这么仔细地画图,竟然还会有这么多错误啊?”3.检测所有的网络节点net是否都连接正确(重点)一般容易出现的错误有:1)本来两个net是应该相连接的,却不小心标得不一致,例如我曾经把主芯片的DDR时钟脚标的是DDR_CLK,而把DDR芯片对应的时钟脚标成了DDRCLK,由于名字不一致,其实这两个脚是没有连接在一起的。

2)有的net只标出了一个,该net的另一端在什么地方却忘记标出。

3)同一个net标号有多个地方重复使用,导致它们全部连接到了一起。

4.检测各个芯片功能引脚是否都连接正确,检测所有的芯片是否有遗漏引脚,不连接的划X芯片的功能引脚一定不要连错,例如我使用的音频处理芯片有LCLK、BCLK、MCLK三个时钟引脚,与主芯片的三个音频时钟引脚一定要一一对应,连反一个就不能工作了。

是否有遗漏引脚其实很容易排查,仔细观察各个芯片,看是否有没有遗漏没有连接出去的引脚,查查datasheet,看看该引脚什么功能,如果系统中不需要,就使用X把该引脚X 掉。

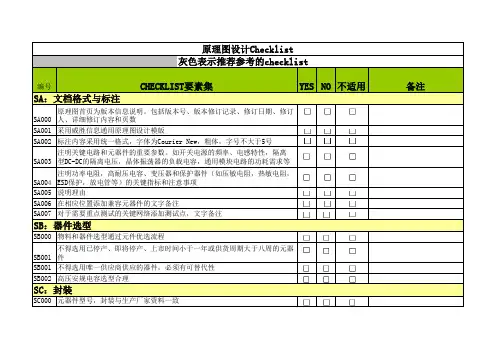

编号YES NO 不适用备注SA000SA001SA002SA003SA004SA005SA006SA007SB000SB001SB001SB002SC000对于不焊接、选择焊接或可调器件在其附近加文字备注并说明理由在相应位置添加兼容元器件的文字备注SB:器件选型原理图设计Checklist 灰色表示推荐参考的checklist 注明功率电阻,高耐压电容、变压器和保护器件(如压敏电阻,热敏电阻,ESD保护,放电管等)的关键指标和注意事项CHECKLIST要素集SA:文档格式与标注注明关键电路和元器件的重要参数。

如开关电源的频率、电感特性,隔离型DC-DC的隔离电压,晶体振荡器的负载电容,通用模块电路的功耗需求等原理图首页为版本信息说明。

包括版本号、版本修订记录、修订日期、修订人、详细修订内容和页数采用威胜信息通用原理图设计模版标注内容采用统一格式,字体为Courier New,粗体,字号不大于5号对于需要重点测试的关键网络添加测试点,文字备注不得选用已停产、即将停产、上市时间小于一年或供货周期大于八周的元器件物料和器件选型通过元件优选流程高压安规电容选型合理SC:封装不得选用唯一供应商供应的器件,必须有可替代性元器件型号,封装与生产厂家资料一致SC001SC002SD000SD001SD002SD003SD004SD005SD006SD007SD008SD009SD010SD011SD012SD013SD014SD015SD016SD017CPU的核心电源由LDO器件提供复位时,受控电源的电压不大于20%的额定电压值电源回路的电压范围设计合理电源回路各个电压的功率设计合理各类逻辑电平(如CMOS、TTL和LVTTL等)必须匹配CPU I/0、LED、继电器控制信号设计必须考虑芯片上电、复位时的状态电路设计有一定的扩展性器件原理图封装中,电源和地引脚不得隐藏如果硬件设计(或变更)涉及内核驱动设计(或相应变更)(如专用硬件资源分配、I/O功能定义、外部扩展地址分配等),硬件设计人员必须与内核组充分沟通、确认并达成共识。

华为-原理图绘制评审规范-checklist原理图绘制评审规范前⾔本技术规范根据国家标准和原邮电部标准以及国际标准系列标准编制⽽成。

本规范于。

本规范起草单位:本规范主要起草⼈:本规范批准⼈:本规范修改记录:⽬次1、⽬的 12、范围 13、定义 14、引⽤标准和参考资料 15、原理图绘制评审内容 15.1图纸幅⾯及格式 15.2标题栏 25.3项⽬代号 25.4标称值 25.5原理图布局 35.6 层次化电路的设计 45.7项⽬代号 45.8注释和解释 65.9电源及地⽹络 65.10去耦电容的放置7原理图绘制评审规范1、⽬的本规范规定产品原理图绘制中符合原理图绘制评审的要素,旨在统⼀绘制的评审要素。

2、范围本规范适⽤于公司产品中所有具有符合原理图绘制规范的原理图绘制评审,⽤于指导原理图绘制、中试审查。

3、定义⽆4、引⽤标准和参考资料下列标准包含的条⽂,通过在本标准中引⽤⽽构成本标准的条⽂。

在标准出版时,所⽰版本均为有效。

所有标准都会被修订,使⽤本标准的各⽅应探讨,使⽤下列标准最新版本的可能1、原理图绘制评审内容本审查内容表审查的某些项⽬如果与设计的单板⽆关则填“不评审”,如果符合或不符则必须填“是”或“否”。

对于填“否”的项必须说明原因,否则不能通过评审。

对于必须审查⽽没有进⾏审查的项⽬,设计审查⼈要承担设计的全部责任。

1.1图纸幅⾯及格式(1)选择图纸幅⾯尺⼨未超出A0幅⾯。

□是□否□不评审(2)图纸的任何内容没有超出外框线之外,也没有叠加在外框线上。

□是□否□不评审(3)除带有图幅分区的VIEWDRAW图框使⽤模板a3.1,a4.1外,其余采⽤软件⾃带的图框。

□是□否□不评审(4)图幅分区数⽬取偶数。

每⼀分区的长度在25~75mm之间选择。

□是□否□不评审(5)分区的编号,沿⽔平⽅向⽤阿拉伯数字从左向右顺序编写,由1开始⾃左向右排列,最多到6;沿垂直⽅向⽤⼤写拉丁字母从上到下从A开始填写,最多到H。

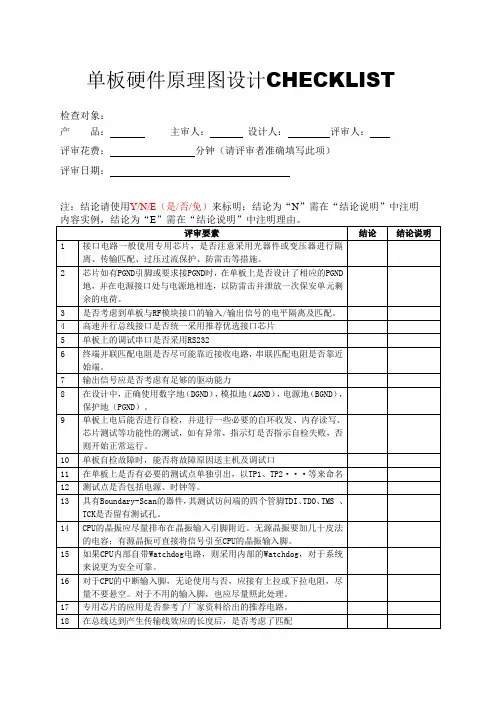

类别描述检视规则原理图需要进行检视,提交集体检视是需要完成自检,确保没有低级问题。

检视规则原理图要和公司团队和可以邀请的专家一起进行检视。

检视规则第一次原理图发出进行集体检视后所有的修改点都需要进行记录。

检视规则正式版本的原理图在投板前需要经过经理的审判。

差分网络原理图中差分线的网络,芯片管脚处的P 和N 与网络命令的P 和N 应该一一对应。

单网络原理图中所有单网络需要做一一确认。

空网络原理图中所有空网络需要做一一确认。

1、原理图绘制中要确认网格设置是否一致。

2、原理图中没有网格最小值设置不一致造成网络未连接的情况。

网络属性确认网络是全局属性还是本地属性1、原理图中器件的封装与手册一致。

2、原理图器件是否是标准库的symbol 。

绘制要求原理图中器件的封装与手册一致。

指示灯设计默认由电源点亮的指示灯和由MCU 点灭的指示灯,便于故障时直观判断电源问题还是MCU 问题网口连接器确认网口连接器的开口方向、是否带指示灯以及是否带PoE 网口变压器确认变压器选型是否满足需求,比如带PoE 按键确认按键型号是直按键还是侧按键电阻上下拉同一网络避免重复上拉或者下拉OD 门芯片的OD 门或者OC 门的输出管脚需要上拉匹配高速信号的始端和末端需要预留串阻三极管三极管电路需要考虑通流能力可测试性在单板的关键电路和芯片附近增加地孔,便于测试连接器防呆连接器选型时需要选择有防呆设计的型号仿真低速时钟信号,一驱动总线接口下挂器件的驱动能力、匹配方式、接口时序必须经过仿真确认,例如MDC/MDIO 、IIC 、PCI 、Local bus 仿真电路中使用电感、电容使用合适Q 值,可以通过仿真。

时序确认上电时序是否满足芯片手册和推荐电路要求。

时序确认下电时序是否满足芯片手册和推荐电路要求。

时序确认复位时序是否满足芯片手册和推荐电路要求。

复位开关单板按键开关设计,要防止长按按键,单板挂死问题,建议按键开关设计只产生一段短脉宽低电平。

【值得收藏】射频电路设计PCB审查checklist 2016-05-18硬件十万个为什么大小编下图所示为PCB 设计完成后的结构轮廓图:我们将布局成“U”形。

布局成U 形并不是不可以,但需要在中间加隔腔将其左右进行隔离,做好屏蔽。

还有一种在横向也需要添加隔腔。

即,用隔腔把一字形左右进行隔离。

这主要是因为需要隔离部分非常敏感或易干扰其它电路;另外,还有一种可能就是一字形输入端到输出端这段电路的增益过大,也需要用隔腔将其分开(若增益过大,腔体太大,可能会引起自激。

)。

B 芯片外围电路布局射频器件外围电路布局严格参照datasheet 上面的要求进行布局,受空间限制可以进行调整;数字芯片外围电路布局就不多讲了。

二、布线注意事项根据50 欧姆阻抗线宽进行布线,尽量从焊盘中心出线,线成直线,尽量走在表层。

在需要拐弯的地方做成45 度角或圆弧走线,推荐在电容或电阻两边进行拐弯。

如果遇到器件走线匹配要求的,请严格按照datasheet 上面的参考值长度走线。

比如,一个放大管与电容之间的走线长度(或电感之间的走线长度)要求等等。

在进行PCB 设计时,为了使高频电路板的设计更合理,抗干扰性能更好,应从以下几方面考虑(通用做法):(1)合理选择层数在PCB 设计中对高频电路板布线时,利用中间内层平面作为电源和地线层,可以起到屏蔽的作用,有效降低寄生电感、缩短信号线长度、降低信号间的交叉干扰。

(2)走线方式走线必须按照45°角拐弯或圆弧拐弯,这样可以减小高频信号的发射和相互之间的耦合。

(3)走线长度走线长度越短越好,两根线并行距离越短越好。

(4)过孔数量过孔数量越少越好。

(5)层间布线方向层间布线方向应该取垂直方向,就是顶层为水平方向,底层为垂直方向,这样可以减小信号间的干扰。

(6)敷铜增加接地的敷铜可以减小信号间的干扰。

(7)包地对重要的信号线进行包地处理,可以显著提高该信号的抗干扰能力,当然还可以对干扰源进行包地处理,使其不能干扰其他信号。