四位二进制全加全减器

- 格式:docx

- 大小:250.91 KB

- 文档页数:4

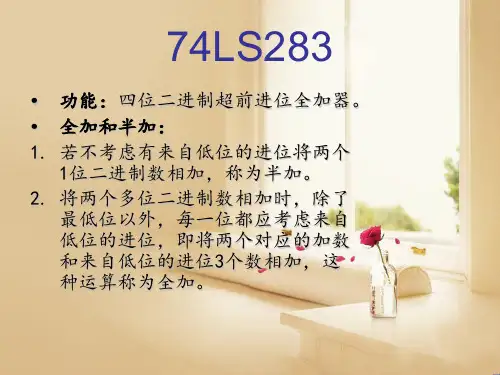

四位二进制全加器设计(总3页) -CAL-FENGHAI.-(YICAI)-Company One1-CAL-本页仅作为文档封面,使用请直接删除组合逻辑电路课程设计题目:用74ls283构成四位二进制全加/减器一、设计思路74ls283为四位加法器,而如果希望进行减法运算,则需要将其转化为加法,而之前学到,二进制运算,一个数减去另一个数,即等于加上其补码。

于是得到如下公式,A-B=A+(-B)=A+B’+1。

将其全部视为加法运算,即一个数加上一个正数或者一个负数,这个数为加数B。

那么,需要将加数增添一位符号位,以区分正负。

因为74ls283芯片的引脚为低位向正在运算的数的进位,所以可以将其作为加数的符号位。

当其为正数时,输入为0,即计算A+B。

而当加数为负数时候,使其输入为1,并将B取反,再加上进位1,正好与公式相符。

根据以上原理,应用输入作为符号位,进行4位被加(减)数与5位加(减)数的加法运算。

设A3-A0为被加(减)数,B3-B0为加(减)数,M0为符号位。

当M0为0时表示正数,为1时表示负数。

而当B为负数需要取反时,刚好可以利用异或门的特性来进行,即1异或B等于B’,0异或B等于B即将B的各个数位和M0通过异或门相连,即可以做到负数取反。

二、电路图如图,输入输出ABC都用LED来指示二进制的数值,开关S2控制A的数值,S1控制B的数值以及符号位。

BX1指示灯指示的是输入B经过异或门作用后的电平。

三、由于此电路进行的是加法运算,两个加数一共2的9次方中组合,所以真值表又多又显而易见,此处将不给出。

四、举例演示:(1)5+6=11如图拨动开关,A=5,B=6,可见C为11的二进制表示1011。

(2)7-3=4如图,将M0置为1以表示负数。

BX1表示的是3的反码,在74283中进行了加1的运算即变成了补码,输出结果为0100(2)=4(10)(3)1000+1000=10000由于输出只有四位,而1000+1000会产生进位。

4bitalu加法器工作原理

4位二进制加法器(4-bit binary adder)是一种电子电路,用于将两个4位二进制数相加。

最常见的4位二进制加法器是基于全加器(Full Adder)的设计。

以下是4位二进制加法器的工作原理:

输入:

4位二进制加法器有两个4位的输入,通常表示为A和B。

每一位都可以是0或1。

全加器:

4位二进制加法器由4个全加器组成,每个全加器都用于处理对应位的加法。

全加器的结构:

每个全加器包括三个输入:A的对应位(Ai)、B的对应位(Bi)和前一位的进位(Ci-1)。

输出包括两个部分:当前位的和(Si)和传递到下一位的进位(Ci)。

第一位的处理:

第一位的全加器只有两个输入,即A0和B0,因为没有前一位的进位。

输出为第一位的和(S0)和传递到第二位的进位(C1)。

中间位的处理:

对于中间的三位,每个全加器都有三个输入(Ai、Bi、Ci-1)和两个输出(Si、Ci)。

输出的和(Si)作为当前位的二进制和。

输出的进位(Ci)传递到下一位的进位输入(Ci-1)。

最后一位的处理:

最后一位的全加器输出的和(S3)和进位(C4)即为4位二进制数相加的结果。

进位检测:

如果最后一位的全加器输出的进位(C4)为1,则表示溢出。

输出:

4位二进制加法器的输出为一个4位的二进制数,其中每一位都是相应位的和。

总体而言,4位二进制加法器通过级联多个全加器,逐位相加并处理进位,实现对两个4位二进制数的加法运算。

这种结构也可以扩

展到更多位数的二进制加法器。

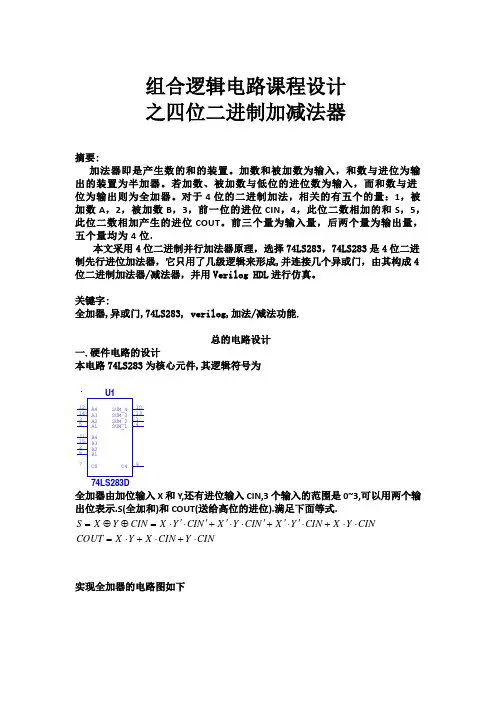

组合逻辑电路课程设计之四位二进制加减法器摘要:加法器即是产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

对于4位的二进制加法,相关的有五个的量:1,被加数A ,2,被加数B ,3,前一位的进位CIN ,4,此位二数相加的和S ,5,此位二数相加产生的进位COUT 。

前三个量为输入量,后两个量为输出量,五个量均为4位.本文采用4位二进制并行加法器原理,选择74LS283,74LS283是4位二进制先行进位加法器,它只用了几级逻辑来形成,并连接几个异或门,由其构成4位二进制加法器/减法器,并用Verilog HDL 进行仿真。

关键字:全加器,异或门,74LS283, verilog,加法/减法功能.总的电路设计 一.硬件电路的设计本电路74LS283为核心元件,其逻辑符号为U174LS283DSUM_410SUM_313SUM_14SUM_21C49B411A412B315A314B22A23B16A15C07全加器由加位输入X 和Y ,还有进位输入CIN,3个输入的范围是0~3,可以用两个输出位表示.S(全加和)和COUT(送给高位的进位).满足下面等式.CINY CIN X Y X COUT CINY X CIN Y X N CI Y X N CI Y X CIN Y X S ⋅+⋅+⋅=⋅⋅+⋅'⋅'+'⋅⋅'+'⋅'⋅=⊕⊕=实现全加器的电路图如下74LS08D本电路还需要4个异或门,要实现加法器和减法器的双重功能,需要有选择功能端,设A为四位二进制被加数,B为二进制被减数.当使能端为0时,电路实现加法运算,当使能端为1时电路实现减法运算.电路原理图如下1.Multisim原理图2.MAX plus2原理图当A口输入为0011,B口输入为0001,使能端为0时.输出为0100.电路图如下当A口输入为0011,B口输入为0001,使能端输入为1时.输出为0010.电路图如下二.软件程序设计Verilog HDL语言程序module b(A,B,C,D,E);input[3:0] A,B;input C;output[3:0] D;output E;assign {E,D}=C?(A+B):(A-B);endmodule当A口输入为0011,B口输入为0001,使能端输入为0,输出为0010,仿真图如下.当A口输入为0011,B口输入为0001,使能端输入为1时.输出为0010.仿真图如下三.总结及心得体会1.通过本次课题设计,自学了一些相关的Verilog语言和MAX+plusII,Multisim 软件的使用方法.2.基本掌握了74LS283的基本原理及使用方法.。

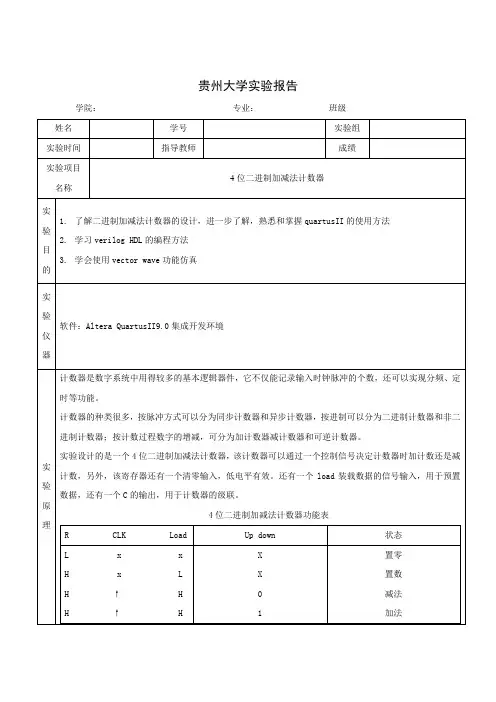

贵州大学实验报告学院:专业:班级设计原理框图从原理图中可见,需要有1bit装载位(load)、1bit清零位(clr)、方向控制位up_down和4bit数据选择位DIN[3..0]。

装载位我们采用SW0,清零位采用SW1,方向控制位为SW2。

SW3-SW6作为数据输入端,LED1-LED4显示数据的输出,LED5为溢出标志位。

实验内容编写一个带预置输入,清零输入,可加可减计数器的verilog代码或VHDL代码并仿真,编译下载验证module counter4(load,clr,c,DOUT,clk,up_down,DIN);//定义模块input load;//定义输入信号input clk;//wire load;//定义线网型input clr;//wire clr;//input up_down;//wire up_down;//input [3:0]DIN;//定义4位二进制输入信号wire [3:0]DIN;// 定义4位二进制线网型信号output c;//定义输出信号reg c;//定义寄存器类型信号output [3:0]DOUT;//wire [3:0]DOUT;reg [3:0]data_r;assign DOUT=data_r;always@(posedge clk or posedge clr or posedge load)//检测clk,clr,load的上升沿beginif(clr)//当clr=1的时候进行下面的运行程序data_r<=0;//将data_r置零else if(load) //当load=1的时候进行下面的运行程序data_r<=DIN;//将DIN的值赋给data_relse begin if(up_down)//load=0的时候进行下面的操作beginif(data_r==4'b1111)begin///当data_r==4'b1111的时候进行下面的运行程序data_r<=4'b0000;c=1;endelse begin//当data_r不等于4'b1111的时候进行下面的运行程序data_r<=data_r+1;//进行加法计数c=0;endendelsebeginif(data_r==4'b0000)begin//当data_r==4'b0000的时候进行下面的运行程序data_r<=4'b1111;c=1;endelse begin//当data_r不等于4'b1111的时候进行下面的运行程序data_r<=data_r-1;//进行减法计数c=0;endendendendendmodule//结束模块实验数据如图为波形仿真结果,当clr为1的时候,输出结果为0000;当clr为0,load为1时,输出结果为输入数据DIN的值,当up_down为1时,加法进位,进行加1运算,当data_r达到1111时,data_r变为0000,级零信号c为1;当up_down为0时,减法进位,进行减1运算,当data_r达到0000时,data_r变为1111,级零信号c为0。

4位同步二进制加法计数器是一种常见的数字电路,用于实现二进制计数。

它可以将二进制数字表示为电信号,并且在每次输入脉冲时进行递增。

下面将详细介绍4位同步二进制加法计数器及其计数的最大值。

一、4位同步二进制加法计数器的原理1. 4位同步二进制加法计数器由4个触发器组成,每个触发器对应一个二进制位。

当输入一个脉冲时,每个触发器根据前一位的状态以及输入脉冲的信号进行状态转换。

这样就实现了二进制数的递增。

2. 触发器之间通过门电路连接,用于控制触发器状态的变化。

这些门电路可以根据具体的设计选择不同的逻辑门,常见的有AND门、OR 门、NOT门等。

3. 4位同步二进制加法计数器是同步计数器,即所有触发器同时接收输入脉冲,确保计数的同步性。

二、4位同步二进制加法计数器的计数最大值1. 4位二进制数的表示范围是0~15,因此4位同步二进制加法计数器的计数最大值为15。

2. 在计数到15后,再输入一个脉冲,计数器将重新从0开始计数,即实现了循环计数。

三、4位同步二进制加法计数器的应用1. 4位同步二进制加法计数器常用于数字电子钟、信号发生器等数字电路中,用于实现计数和定时功能。

2. 它还可以作为其他数字电路的组成部分,用于构建更复杂的逻辑功能。

3. 在数字系统中,计数器是十分重要的组件,它能够实现数字信号的计数和控制,广泛应用于各种数字系统中。

4位同步二进制加法计数器是一种重要的数字电路,通过它可以实现对二进制数的递增计数。

其计数的最大值为15,应用领域广泛。

希望本文内容能够对读者有所启发。

四、4位同步二进制加法计数器的工作原理4位同步二进制加法计数器是一种晶体管数字集成电路,它利用触发器和逻辑门等基本元件构成,能够实现二进制数字的加法计数。

在4位同步二进制加法计数器中,每个触发器代表一个二进制位,通过输入脉冲的控制,能够实现对二进制数的递增计数。

具体来说,当输入一个脉冲信号时,4位同步二进制加法计数器会根据触发器之间的连线和逻辑门的作用,根据之前的状态和输入脉冲的信号进行状态转换,从而实现二进制数的递增。

全加器全减器设计实验报告1. 引言全加器和全减器是数字电路中常用的基本电路模块之一。

全加器用于将两个二进制数相加,全减器用于将两个二进制数相减。

在本实验中,我们将设计并实现一个4位的全加器和一个4位的全减器电路。

2. 原理2.1 全加器全加器是由两个半加器和一个或门组成的电路。

一个半加器用于计算两个输入位的和,另一个半加器用于计算进位值。

将两个半加器的结果和进位值通过或门进行运算,即可得到全加器的输出。

如下图所示为全加器的逻辑电路图:其中,A和B为输入信号,用于表示待相加的两个二进制数的对应位;S为输出信号,表示两个输入数的对应位相加的结果;C为进位信号,表示相加时产生的进位。

2.2 全减器全减器是由两个半减器和一个与非门组成的电路。

与全加器类似,一个半减器用于计算两个输入位的差,另一个半减器用于计算借位值。

将两个半减器的结果和借位值通过与非门进行运算,即可得到全减器的输出。

如下图所示为全减器的逻辑电路图:其中,A和B为输入信号,用于表示待相减的两个二进制数的对应位;D为输出信号,表示两个输入数的对应位相减的结果;B为借位信号,表示相减时需要借出的位。

3. 设计和实现3.1 全加器设计根据2.1中的原理,我们可以使用两个半加器和一个或门来实现一个4位的全加器电路。

根据全加器的逻辑电路图,我们可以将四个输入位(A0, A1, A2, A3)依次与另外四个输入位(B0, B1, B2, B3)连接到两个半加器中,然后将两个半加器的和(S0, S1, S2, S3)通过或门进行运算。

此外,计算进位值需要使用到四个位的与门(And)。

具体电路图如下:3.2 全减器设计根据2.2中的原理,我们可以使用两个半减器和一个与非门来实现一个4位的全减器电路。

根据全减器的逻辑电路图,我们可以将四个输入位(A0, A1, A2, A3)依次与另外四个输入位取反连接到两个半减器中,然后将两个半减器的差(D0, D1, D2, D3)通过与非门进行运算。

组合逻辑电路课程设计——4位二进制全加器/全减器作者:学号:课程设计题目要求:1)使用74LS283构成4位二进制全加/全减器。

2)阐述设计思路。

3)列出真值表。

4)画出设计的逻辑图。

5)用VHDL对所画电路进行仿真。

目录摘要 (1)1总电路设计 (2)1.1硬件电路的设计 (2)1.2全加器(full-adder ) (3)1.2.1四位二级制加法器 (4)1.2.1.1串行进位加法器 (4)1.2.1.2超前进位加法器 (5)1.2.1.3超前位链结构加法器 (5)1.3全减器(full-substracter ) (5)1.4总电路设计 (6)2设计思路 (7)2.1全加器 (7)2.2全减器 (7)3真值表 (8)4逻辑图与仿真 (9)5软件程序的设计 (13)6结果分析与总结 (15)摘要加法器是数字系统中产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

例如:为了节省资源,减法器和硬件乘法器都可以用加法器来构成。

但宽位加法器的设计是很耗资源的,因此在实际的设计和相关饿得设计与开发中需要注意资源的利用率和进位速度两方面的问题,多位加法器的构成主要有两种:并行进位和串行进位。

并行进位加法器设有并行进位产生逻辑,运行速度比串行进位快;串行进位是将全加器采取并行级联或菊花链式级联构成多位加法器。

加法器也是常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

此外还可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二进制作运算。

本文将采用4位二进制并行加法器作为折中选择,所选加法器为74LS283,74LS283是4位二进制先行进位的加法器,它只用了几级逻辑来形成和及进位输出,故由其构成4位二进制全加器;而四位全减器可以用加法器简单的改造而来,最后本文采用 VHDL对四位全加器/全减器进行仿真。

关键字74LS283全加器、四位二进制、迭代电路、并行进位、串行进位、VHDL1总电路设计1.1硬件电路的设计该4位二进制全加器以74LS283为核心,74LS283芯片引脚图如下图,本文采用先行进位方式,极大地提高了电路运行速度,下面是对4位全加器电路设计的具体分析。

《电工与电子技术基础》课程设计报告题目四位二进制加法计数器学院(部)汽车学院专业汽车运用工程班级22020903学生姓名郭金宝学号220209031006 月12 日至06 月22 日共 1.5 周指导教师(签字)评语评审人:四位二进制加法器一.技术要求1.四位二进制加数与被加数输入2.二位显示二.摘要本设计通过逻辑开关将A3,A2,A1,A0和B3,B2,B1,B0信号作为加数和被加数输入到超前进位加法器74LS283中进行四位二进制相加,将输出信号S4,S3,S2,S1和向高位的进位C1输入一个译码器译码。

再将输出信号X4,X3,X2,X1和Y4,Y3,Y2,Y1分别输入一个74LS247型的七段显示译码器译码,最后分别接一个BS204数码管进行二位显示。

关键字:74LS283 74LS247 BS204三.总体设计方案的论证及选择1.加法器的选取加法器有两种,分别是串行进位加法器和超前进位加法器。

串行进位加法器由全加器级联构成,高位的运算必须等到低位加法完成送来进位时才能进行。

它虽然电路简单,但运算速度较慢,而且位数越多,速度就越慢。

T692型集成全加器就是这种四位串行加法器。

超前进位加法器由逻辑电路根据输入信号同时形成各位向高位的进位。

使各位的进位直接由加数和被加数来决定,而不需依赖低位进位,这就省去了进位信号逐级传送所用的时间,所以这种加法器能够快速进位。

因为它的这个优点我们选取超前进位加法器。

超前进位加法器的型号有多种,由于我们是非电专业,对电子器件的选取要求不高,为使设计简单所以选74LS283型加法器。

2.译码器的选取译码器的功能是将二进制代码(输入)按其编码时的原意翻译成对应的信号或十进制数码(输出)。

译码器是组合逻辑电路的一个重要器件,其可以分为:变量译码和显示译码两类。

译码器的种类很多,但它们的工作原理和分析设计方法大同小异,其中二进制译码器、二-十进制译码器和显示译码器是三种最典型,使用十分广泛的译码电路。

组合逻辑电路的课程设计之4位二进制全加\全减器(改进版——加法器与减法器的复合器)自动化工程学院摘要:加法器是产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

常用作计算机算算术逻辑部件,执行逻辑操作、移位与指指令调用。

在电子学中,加法器是一种数位电路,其可进行数字的加法计算。

在现代的电脑中,加法器存在于算术逻辑单元(ALU)之中。

加法器可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二进制作运算。

简介:对于简单的四位二进制全加器,本文只做简要介绍,因为对于单一的加法器,显然是不够实用的,本文将着重就一种加法器与减法器的组合,即设计电路一个电路实现2个4位符号数(原码表示)的加减运算。

另有一个控制信号select 选择加法运算或减法运算。

若有溢出则产生溢出指示信号。

这种加法器与减法器的复合器将在实际操作中表现的更加的适用。

关键字:四位二进制全加器,四位二进制全减器,原理图Verilog HDL仿真电路的设计:常见的四位二进制全加器,通过两片74 283可以实现全加器的功能,即如下图所示:单一加法器的真值表如图所示:A3 A2 A1 A0 B3 B2 B1 B0 CIN S3 S2 S1 S0 COUT而详细的电路图为:加法器与减法器的复合器:接下来,我将对于这种加法器与减法器的复合器做详细介绍。

对于这种复合器,通过两个片子来实现。

而详细的电路如图所示:通过select作为选择端口,控制select的电平即可对加减复合器的加减功能进行选择,本电路中当当select接高电平是,选择的是加法器,当select接低电平时选择的是减法器,通过改变select的电平,可以轻松实现加法器和减法器的转换。

在用select选择了加法或是减法功能后,在输入端A3A2A1A0与B3B2B1B0分别为两个运算数的二进制代码,以高低电平来代表1或0,实现了目标数的输入。

数字逻辑设计及应用课程设计组合逻辑电路课程设计四位二进制全加/全减器姓名:学号:指导教师:一、任务与要求使用74LS83构成4位二进制全加/全减器。

具体要求:1)列出真值表;2)画出逻辑图3)用Verilog HDL进行仿真二、设计思路1)原理分析:74LS83是四位二进制先行加法器,所以直接接入输入可以得到全加器,下面主要讨论四位二进制全减器的构造。

对于减法,可以作相应的代数转换编程加法,二进制减法也是如此,原理如下:这样就把减法变为了加法,而[]=,这里利用补码性质,具体实现方法就是:逐位取反并在最低权一位加上1。

在全减器中,进位输入Cin变为借位输出,所以要减去Cin,且全加器的输出端Cout为进位输出,全减器为借位输出,所以将So取反后即可得到全减器的借位输出。

在以上分析基础可知,可在全加器的基础上设计全减器。

四位二进制全加/全减器真值表如下:(因原始真值表行数太过庞大,列出部分真值的例子)真值表A3 A2 A1 A0 B3 B2 B1 B0 Co Bo S0 S1 S2 S3C/B0 0 1 0 0 1 0 1 0 1 0/1 1/1 1/0 1/1 01 0 1 1 1 1 1 0 1 1 1/1 0/1 0/0 1/1 00 1 1 0 0 0 1 1 0 0 1/0 0/0 0/1 1/1 01 1 1 1 0 0 1 1 1 0 0/1 0/1 1/0 0/0 00 0 1 0 0 1 0 1 0 1 1/1 0/1 0/0 0/0 11 0 1 1 1 1 1 0 1 1 1/1 0/1 1/0 0/0 10 1 1 0 0 0 1 1 0 0 1/0 0/0 1/1 0/0 11 1 1 1 0 0 1 1 1 0 0/1 0/0 1/1 1/1 1*表格后半部分内容,斜线前为全加结果,斜线后为全减结果*XOR门的函数为:,所以当EN=A=0时,得到F=B与第二输入相同,当EN=A=1时,F=B’与第二输入相反。

© 2000 Fairchild Semiconductor Corporation DS006401August 1986Revised April 2000DM74LS169A Synchronous 4-Bit Up/Down Binary CounterDM74LS169ASynchronous 4-Bit Up/Down Binary CounterGeneral DescriptionThis synchronous presettable counter features an internal carry look-ahead for cascading in high-speed counting applications. Synchronous operation is provided by having all flip-flops clocked simultaneously, so that the outputs all change at the same time when so instructed by the count-enable inputs and internal gating. This mode of operation helps eliminate the output counting spikes that are nor-mally associated with asynchronous (ripple clock)counters. A buffered clock input triggers the four master-slave flip-flops on the rising edge of the clock waveform.This counter is fully programmable; that is, the outputs may each be preset either HIGH or LOW. The load input cir-cuitry allows loading with the carry-enable output of cas-caded counters. As loading is synchronous, setting up a low level at the load input disables the counter and causes the outputs to agree with the data inputs after the next clock pulse.The carry look-ahead circuitry permits cascading counters for n-bit synchronous applications without additional gating.Both count-enable inputs (P and T) must be LOW to count.The direction of the count is determined by the level of the UP/DOWN input. When the input is HIGH, the counter counts UP; when LOW, it counts DOWN. Input T is fed for-ward to enable the carry outputs. The carry output thus enabled will produce a low-level output pulse with a dura-tion approximately equal to the high portion of the Q A out-put when counting UP, and approximately equal to the low portion of the Q A output when counting DOWN. This low-level overflow carry pulse can be used to enable succes-sively cascaded stages. Transitions at the enable P or T inputs are allowed regardless of the level of the clock input.All inputs are diode clamped to minimize transmission-line effects, thereby simplifying system design.This counter features a fully independent clock circuit.Changes at control inputs (enable P, enable T, load, UP/DOWN), which modify the operating mode, have no effect until clocking occurs. The function of the counter (whether enabled, disabled, loading, or counting) will be dictated solely by the conditions meeting the stable setup and hold times.Featuress Fully synchronous operation for counting and programming.s Internal look-ahead for fast counting.s Carry output for n-bit cascading.s Fully independent clock circuitOrdering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X” to the ordering code.Connection DiagramOrder Number Package NumberPackage DescriptionDM74LS169AM M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow DM74LS169ANN16E16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide 2D M 74L S 169ALogic Diagram DM74LS169ATiming DiagramTypical Load, Count, and Inhibit Sequences 4D M 74L S 169AAbsolute Maximum Ratings (Note 1)Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings.The “Recommended Operating Conditions” table will define the conditions for actual device operation.Recommended Operating ConditionsNote 2: C L = 15 pF, R L = 2 k Ω, T A = 25°C and V CC = 5V.Note 3: C L = 50 pF, R L = 2 k Ω, T A = 25°C and V CC = 5V.Note 4: T A = 25°C and V CC = 5V.Electrical Characteristicsover recommended operating free air temperature range (unless otherwise noted)Note 5: All typicals are at V CC = 5V and T A = 25°C.Note 6: Not more than one output should be shorted at a time, and the duration should not exceed one second.Note 7: I CC is measured after a momentary 4.5V, then ground, is applied to the CLOCK with all other inputs grounded and all the outputs OPEN.Supply Voltage 7V Input Voltage7VOperating Free Air Temperature Range 0°C to +70°C Storage Temperature Range−65°C to +150°CSymbol ParameterMin Nom Max Units V CC Supply Voltage4.7555.25V V IH HIGH Level Input Voltage 2V V IL LOW Level Input Voltage 0.8V I OH HIGH Level Output Current −0.4mA I OL LOW Level Output Current 8mA f CLK Clock Frequency (Note 2)025MHz Clock Frequency (Note 3)020MHz t W Clock Pulse Width (Note 4)25nst SUSetup Time Data 20(Note 4)Enable 20T or P nsLoad 25U/D30t H Hold Time (Note 4)0ns T AFree Air Operating Temperature70°C Symbol ParameterConditionsMinTyp Max Units (Note 5)V I Input Clamp Voltage V CC = Min, I I = −18 mA −1.5V V OH HIGH Level V CC = Min, I OH = Max 2.73.4VOutput Voltage V IL = Max, V IH = Min V OLLOW Level V CC = Min, I OL = Max 0.350.5Output VoltageV IL = Max, V IH = Min VI OL = 4 mA, V CC = Min 0.250.4I I Input Current @ Max V CC = Max Enable T 0.2mA Input Voltage V I = 7V Others 0.1I IH HIGH Level V CC = Max Enable T 40µA Input Current V I = 2.7V Others 20I IL LOW Level V CC = Max Enable T −0.8mA Input CurrentV I = 0.4VOthers−0.4I OS Short Circuit Output Current V CC = Max (Note 6)−20−100mA I CCSupply CurrentV CC = Max (Note 7)2034mADM74LS169ASwitching Characteristicat V CC = 5V and T A = 25°CNote 8: The propagation delay from UP/DOWN to RIPPLE CARRY must be measured with the counter at either a minimum or a maximum count. As the logic level of the UP/DOWN input is changed, the ripple carry output will follow. If the count is minimum, the RIPPLE CARRY output transition will be in phase. If the count is maximum, the RIPPLE CARRY output will be out of phase.From (Input)R L = 2 k ΩSymbol ParameterTo (Output)C L = 15 pF C L = 50 pF UnitsMin MaxMin Maxf MAX Maximum Clock Frequency 2520MHz t PLH Propagation Delay Time Clock to 3539ns LOW-to-HIGH Level Output Ripple Carry t PHL Propagation Delay Time Clock to 3544ns HIGH-to-LOW Level Output Ripple Carry t PLH Propagation Delay Time Clock to 2024ns LOW-to-HIGH Level Output Any Q t PHL Propagation Delay Time Clock to 2332ns HIGH-to-LOW Level Output Any Q t PLH Propagation Delay Time Enable T to 1824ns LOW-to-HIGH Level Output Ripple Carry t PHL Propagation Delay Time Enable T to 1828ns HIGH-to-LOW Level Output Ripple Carry t PLH Propagation Delay Time Up/Down to 2530ns LOW-to-HIGH Level Output Ripple Carry (Note 8)t PHLPropagation Delay Time Up/Down to 2938ns HIGH-to-LOW Level OutputRipple Carry (Note 8) 6D M 74L S 169APhysical Dimensionsinches (millimeters) unless otherwise noted16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 NarrowPackage Number M16APhysical Dimensions inches (millimeters) unless otherwise noted (Continued)16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePackage Number N16EFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life supportdevice or system whose failure to perform can be rea-sonably expected to cause the failure of the life supportdevice or system, or to affect its safety or effectiveness. DM74LS169A Synchronous 4-Bit Up/Down Binary Counter。

数字逻辑设计及应用课程设计报告

组合逻辑设计

题目:使用74LS83构成4位二进制全加\全减器。

具体要求:1)列出真值表;

2)画出逻辑图;

3)用Verilog HDL 进行仿真;

1.设计思路及原理分析

全加器是除本位数字相加外,还考虑进位输入和进位输出的加法器,全减器同理,考虑借位输入和借位输出。

本次主要应用74LS83来实现设计要求,74LS83是四位二进制先行进位加法器,可以直接接入输入获得全加器,所以设计重点在于四位全减器的设计。

对于串行进位加法器,可略加改进获得相应的减法器,基本原理如下式:

2'2'2'2'[]s s s s X Y X Y -=+-

'2'2[]2n s s Y Y -=-

这里利用了补码的基本性质,具体实现时可以将减数逐位取反,然后最低位加1。

又因为全加器时in C 为为进位输入,全减器时应变为借位输入,所以要减去in C ,且全加器的输出端out C 为进位输出,而全减法器应该输出借位输出,而进位输出与借位输出恰好是反向的关系,所以将0S 取反后即得到全减器的借位输出out B ,据此,可以在全加器的基础上设计全减器。

其中表中输出部分上行为全加输出,下行为全减输出。

2 逻辑电路图

3 电路实现和仿真

3.1 verilog HDL设计代码如下:

module add(s,out,a,b,in,EN);

output[0:3] s;

output out;

input[0:3] a,b;

input in;

input EN;

reg out;

reg[0:3] s,c;

always@(*)

if (EN==0)

begin

{out,s}=a+b+in;

end

else

begin

c=10000-b;

{out,s}=a+c-in;

out=~out;

end

endmodule

3.2 仿真波形图

4 结果分析

由波形图可知,仿真结果与真值表完全吻合,说明本次设计的可行性和正确性,至此,我们完成了基于74LS83构成4位二进制全加\全减器的分析、设计、仿真,而且达到了预期的设计要求。

5 总结

此次课程选取的题目较为简单,容易操作,但与平时课上所学习的基础知识联系紧密,是对课上所学理论知识很好的应用和检验。

过程中最大的感受是体会到了如何用课本所学的理论设计所需的电路,而理论和实践起来是不同的,即使理论很扎实,而实际用verilog HDL语言来写时也会遇到很多困难。

但是在设计时能对所学的东西有更好的理解,这也更激起了我对数字设计这门课程的兴趣,以后一定会继续好好学习这门课程,课下将书本上的verilog HDL程序用Quartus仿真出来,以加深对知识的理解。

6 参考文献

《数字设计—原理与实践》 John F.Wakerly

《基于Quartus II的数字系统Verilog HDL设计实例详解》周景润。