MSP430F2XX中文手册(加了标签) 14.运算放大器

- 格式:pdf

- 大小:506.16 KB

- 文档页数:30

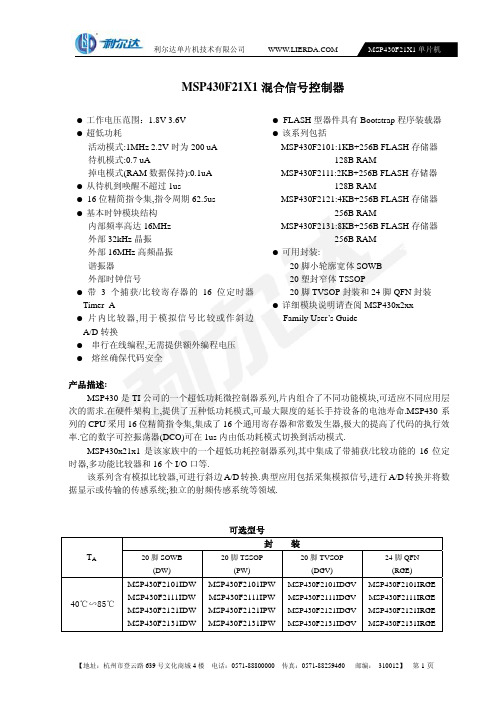

MSP430混合信号微控制器数据手册产品特性●低电压范围:2.5V~5.5V 超低功耗●超低功耗——活动模式:330μA at 1MHz, 3V——待机模式:0.8μA——掉电模式(RAM数据保持):0.1μA ●从待机模式唤醒响应时间不超过6μs ●16位精简指令系统,指令周期200ns ●基本时钟模块配置基本时钟模块配置——多种内部电阻——多种内部电阻——单个外部电阻——单个外部电阻——32kHz晶振晶振——高频晶体——高频晶体——谐振器——谐振器——外部时钟源——外部时钟源●带有三个捕获/比较寄存器的16位定时器(Timer_A)串行在线可编程●串行在线可编程●采用保险熔丝的程序代码保护措施采用保险熔丝的程序代码保护措施该系列产品包括●该系列产品包括——MSP430C111:2K字节ROM,128字节RAM ——MSP430C112:4K字节ROM,256字节RAM ——MSP430P112:4K字节OTP,256字节RAM 原型●EPROM原型——PMS430E112:4KB EPROM, 256B RAM ●20引脚塑料小外形宽体(SOWB)封装,20引脚陶瓷双列直插式(CDIP)封装(仅EPROM)●如需完整的模块说明,请查阅MSP430x1xx系列用户指南(文献编号:SLAU049 产品说明TI公司的MSP43O系列超低功耗微控制器由一些基本功能模块按照不同的应用目标组合而成。

在便携式测量应用中,这种优化的体系结构结合五种低功耗模式可以达到延长电池寿命的目的。

以达到延长电池寿命的目的。

MSP430MSP430系列的CPU 采用16位精简指令系统,集成有16位寄存器和常数发生器,发挥了最高的代码效率。

它采用数字控制振荡器(DCO DCO)),使得从低功耗模式到唤醒模式的转换时间小于6μs.MSP430x11x 系列是一种超低功耗的混合信号微控制器,系列是一种超低功耗的混合信号微控制器,它拥有一个内置的它拥有一个内置的16位计数器和14个I/0引脚。

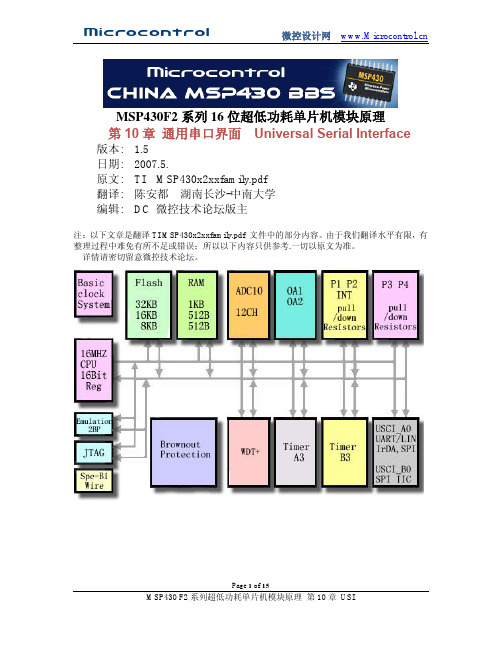

MSP430F2系列16位超低功耗单片机模块原理第10章通用串口界面Universal Serial Interface 版本: 1.5日期: 2007.5.原文: TI MSP430x2xxfamily.pdf翻译: 陈安都湖南长沙-中南大学编辑: DC 微控技术论坛版主注:以下文章是翻译TI MSP430x2xxfamily.pdf 文件中的部分内容。

由于我们翻译水平有限,有整理过程中难免有所不足或错误;所以以下内容只供参考.一切以原文为准。

详情请密切留意微控技术论坛。

Page 1 of 15通用串行接口模块(USI)提供与硬件模块的SPI和I2C串行通信。

本章讨论这两种模式。

USI模块包含在MSP420X20XX系列中。

主题10.1 USI的介绍10.2 USI的使用10.3 USI的寄存器10.1 USI的介绍USI模块提供支持同步串行通信的基本功能。

一般地,一个8、16位移位寄存器能用来输出数据流,少许的几条指令就可以执行串行通信。

另外,USI包含的内置硬件可以模拟SPI和I2C通信。

USI模块还包括中断,可以进一步减少串行通信的通用程序并且保持MSP430的低功耗特性。

USI模块的特性包括:支持三线SPI模式支持I2C模式可变的数据长度在LPM4方式下不需要内部时钟MSB或LSB指令可选在I2C模式下能控制SCL打开、停止监测在主机模式下的仲裁丢失监测可编程的时钟发生器可选择的钟极性和相位控制Page 2 of 15表10-1展示了SPI模式下的USI模块Page 3 of 15表10-2展示了I2C模式下的USI模块10.2 USI的操作USI模块主要由移位寄存器和位计数器组成,通过逻辑控制来支持SPI和I2C 通信。

USI的移位寄存器为USISR,通过软件直接控制数据的移入和移出。

位计数器计算采样位的数目以及在USICNTX位写零时设置USI中断标志位Page 4 of 15USIIFG。

MSP430AFE2x3MSP430AFE2x2MSP430AFE2x1 ZHCS136A–NOVEMBER2010–REVISED MARCH2011混合信号微控制器特性•低电源电压范围:1.8V至3.6V•多达3个具有差分可编程增益放大器(PGA)输入的24位三角积分模数(A/D)转换器•超低功耗•具有3个捕获/比较寄存器的16位Timer_A –激活模式:220μA(在1MHz频率和2.2V电压条件下)•串行通信接口(USART),可用软件来选择异步UART或同步SPI–待机模式:0.5μA•16位硬件乘法器–关闭模式(RAM保持):0.1μA•欠压检测器•5种节能模式•具有可编程电平检测功能的电源电压监控器/监视器•可在不到1μs的时间里超快速地从待机模式唤醒•串行板上编程,无需从外部进行电压编程,利用安•16位精简指令集(RISC)架构,高达12MHz系统时全熔丝实现可编程代码保护钟•片上仿真模块•基本时钟模块配置•系列成员汇总于表1。

–带有两个已校准频率的高达12MHz的内部频率•如需了解完整的模块说明,请参阅《MSP430x2xx –内部超低功耗低频(LF)振荡器系列用户指南》,文献编号SLAU144–高达16MHz的高频(HF)晶振–谐振器–外部数字时钟源说明德州仪器(TI)MSP430™系列超低功率微控制器包含几个器件,这些器件特有针对多种应用的不同的外设集。

这种架构与5种低功耗模式相组合,专为在便携式测量应用中延长电池使用寿命而优化。

该器件具有一个强大的16位RISC CPU,16位寄存器和有助于获得最大编码效率的常数发生器。

数字控制振荡器(DCO)可在不到1µs 的时间里完成从低功耗模式至运行模式的唤醒。

MSP430AFE2x3器件是超低功耗混合信号微控制器,集成了三个独立的24位三角积分A/D转换器、一个16位定时器、一个16位硬件乘法器、USART通信接口、安全装置定时器和11个I/O引脚。

1.数据传送指令MOV 源操作数移至目的操作数MOV.B scr,dst /MOV[.W] scr,dst CLR 清除目的操作数CLR.B dst /CLR[.W] dstPOP 字从堆栈弹出至目的操作数POP.B dst /POP[.W] dstPUSH 将字压进堆栈PUSH.B src /PUSH[.W] src SWPB 交换字节SWPB dstSXT 扩展符号SXT dst2.数据运算指令ADC 将进位位加至目的操作数ADC.B dst /ADC dst或ADC[.W] dst ADD 源操作数加至目的操作数ADD src,dst /ADD[.W] src,dst ADDC 原操作数和进位加至目的操作数ADDC.B src,dst /ADDC[.W] src,dst DADC 加上十进制的进位位DADC.B dst /DADC [.W] src,dst DADD 将十进制的进位位和源操作数加至目的操作数DADD.B src,dst /DADD[.W] src,dst INC 目的操作数加1 INC.B dst /INC[.W] dstINCD 目的操作数加2 INCD.B dst /INCD[.W] dstSUB 从目的操作数中减去源操作数SUB src,dst /SUB[.W] src,dst SUBC 从目的操作数中减去源操作数和借位/非进位SUBC src,dst /SUBC[.W] src,dst DEC 目的操作数减1 DEC.B dst /DEC[.W] dstDECD 目的操作数减2 DECD.B dst /DECD[.W] dstSBC 从目的操作数减去借位SBC.B dst /SBC[.W] dstCMP 比较源操作数和目的操作数CMP.B src,dst /CMP[.W] src,dst TST 测试目的操作数TST.B dst /TST[.W] dst3.逻辑运算和位操作类指令AND 源操作数和目的操作数与AND.B src,dst /AND[.W] src,dstBIC清除目的操作数的各位BIC.B src,dst /BIC [.W] src,dstBIS 设置目的操作数的各位BIS.B src,dst /BIS[.W] src,dstBIT 测试目的操作数的各位BIT.B src,dst /BIT[.W] src,dstXOR 源操作数和目的操作数异或XOR.B src,dst /XOR[.W] src,dstINV 目的操作数求反INV.B dst /INV[.W] dstRLA 算数左移RLA.B dst /RLA[.W] dstRLC 通过进位位左移RLC.B dst /RLC[.W] dstRRA 算数右移RRA.B dst /RRA[.W] dstRRC 通过进位位右移RRC.B dst /RRC[.W] dstCLRC 清除进位位CLRCCLRN 清除负位CLRNCLRZ 清除零位CLRZSETC 设置进位位SETCSETN 设置负位SETNSETZ 设置零位SETZDINT 禁止(一般)中断DINTEINT 使能(一般)中断EINT4.跳转与程序流程的控制类指令BR 转移至目的操作数BR dstCALL 调用子程序CALL dstJC/JHS JC 设置进位位时程序跳转JC 标号JHS 大于和等于时程序跳转JHS 标号JEQ/JZ JEQ 等于时程序跳转JEQ 标号JZ 为零时程序跳转JZ标号JGE 大于等于时程序跳转JGE 标号JL 小于时程序跳转JL 标号JMP 程序无条件跳转JMP 标号JN 为负时程序跳转JN标号JNC/JLO JNC 进位未设置时程序跳转JNC 标号JLO 小于时程序跳转JLO 标号JNE/JNZ JNE 不等时程序跳转JNE 标号JNZ 不为零时程序跳转JNZ 标号RET 从子程序返回RETRETI 从中断返回RETINOP 空操作NOP。

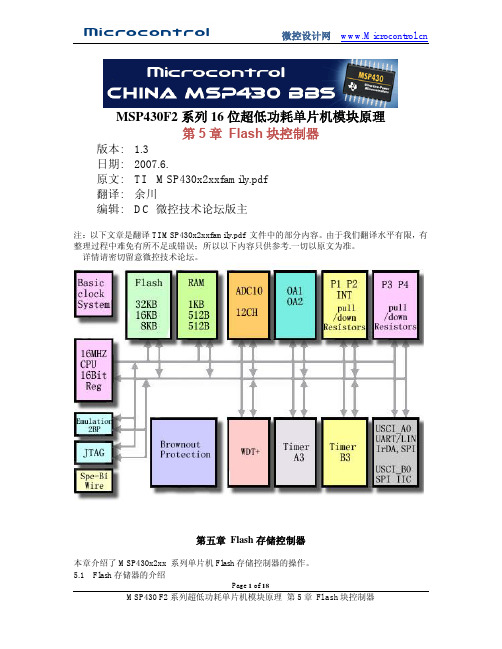

Page 1 of 18MSP430F2系列16位超低功耗单片机模块原理第5章 Flash 块控制器版本: 1.3日期: 2007.6.原文: TI MSP430x2xxfamily.pdf翻译: 余川编辑: DC 微控技术论坛版主注:以下文章是翻译TI MSP430x2xxfamily.pdf 文件中的部分内容。

由于我们翻译水平有限,有整理过程中难免有所不足或错误;所以以下内容只供参考.一切以原文为准。

详情请密切留意微控技术论坛。

第五章 Flash 存储控制器本章介绍了MSP430x2xx 系列单片机Flash 存储控制器的操作。

5.1 Flash 存储器的介绍Page 2 of 18 5.2 Flash 存储器的分段结构5.3 Flash 存储器的操作5.4 Flash 存储器的控制寄存器5.1 Flash 存储器的介绍MSP430 的F lash 存储器是可位/字节/字寻址和编程的存储器。

该模块由一个集成控制器来控制编程和擦除的操作。

控制器包括三个寄存器,一个时序发生器及一个提供编程/擦除电压的电压发生器。

MSP430 的F lash 存储器的特点有:● 产生内部编程电压● 可位/字节/字编程● 超低功耗操作● 支持段擦除和多段模块擦除F lash 存储器和控制器的结构框图如图5−1所示。

注意:F lash 写入和擦除操作期间的最小电压值V CC 应为2.2V 。

如果在操作期间V CC 低于2.2V ,写入或擦除的结果将是不确定的。

图5−1 F lash 存储器框图Page 3 of 185.2 Flash 存储器的分段结构MSP430 F lash 存储器分成多个段。

可对其进行单个位/字节/字的写入,但是最小的擦除单位是段。

F lash 存储器分为主存储器和信息存储器两部分,在操作上两者没有什么区别,程序代码和数据可以存储于任意部分。

两部分的区别在于段的大小和物理地址。

信息存储器有四个64字节的段,主存储器有两个或更多的512字节的段。

MSP430x13x , MSP430x14x , MSP430x14x1混合信号微控制器低电源电压范围:1.8~3.6V超低功耗:待机模式:1.6uA关闭模式 (RAM保持 :0.1uA活动模式:280uA at 1MHz, 2.2V5种省电模式6us 内从待机模式唤醒16位 RISC 结构, 125ns 指令周期带内部参考,采样保持和自动扫描特性的 12位 A/D转换器有 7个捕获 /比较寄存器的 16位定时器 Timer_B有 3个捕获 /比较寄存器的 16位定时器 Timer_A片内集成比较器串行在线编程,无需外部编程电压,安全熔丝可编程代码保护 .器件系列包括:–MSP430F133:8KB+256B闪速存储器, 256B 的 RAM–MSP430F135:16KB+256B闪速存储器, 512B 的 RAM–MSP430F147, MSP430F1471:32KB+256B闪速存储器, 1KB 的 RAM –MSP430F148, MSP430F1481:48KB+256B闪速存储器, 2KB 的 RAM–MSP430F149, MSP430F1491:60KB+256B闪速存储器, 2KB 的 RAM可用封装:64脚方形扁平封装 (QFP.描述德州仪器的 MSP430系列是一种超低功耗微控制器系列,由针对各种不同应用模块组合特性的多种型号组成.微控制器可设计成使用电池长时间工作.由于其 16位的体系结构, 16位的 CPU 集成寄存器和常数发生器, 可使 MSP430实现了最大化的代码效率。

数字控制振荡器使所有低功率模式唤醒到运行模式小于 6us 的唤醒时间。

MSP430x13x 和 MSP430x14x 系列是有两个内置 16位定时器,一个快速 12位 A/D转换器,一或两个通用串行同步 /异步通信接口 (USART和 48个 I/O引脚构造的微控制器。

典型应用为传感器系统,把模拟信号转换成数字值,处理并发送数据到主系统。

MSP432 产品培训目录第一章MSP432™ MCU概览 (2)第二章 Cortex-M4F内核和中断 (14)第三章电源系统 (20)未完待续MSP432 Microcontroller WorkshopRevision 1.02015. 03第一章MSP432™ MCU概览本章节将主要对MSP432系列MCU的性能和特色进行一个概括性的介绍。

MSP432 系列MCU属于低功耗、高性能的微控制器。

这个系列产品是TI的 MSP 低功耗微控制器系列中的产品,MSP系列产品还包括我们的 FRAM 产品和安全与互联型 MCU (例如RF430 产品)。

MSP432系列是最新的更高主频和更丰富外设通用微控制器产品。

在实际应用中,客户通常希望能解决哪些问题?很多时候,我们发现首先客户希望能提高处理能力。

他们希望能进一步增强器件的功能、对数据的吞吐能力或模拟方面的性能,或许他们也正在进行 ARM 内核的标准化工作。

同时,他们还需要低功耗,尤其是采用电池供电的应用,或一些只需极少电量的应用情况下。

第三,他们也希望工具和软件能方便易用,并能帮助他们优化性能及功耗。

最后,他们还需要产品拥有一个可扩展的平台,让他们能够在低功耗产品与高性能产品之间自由切换。

MSP432 凭借 32 位的48 MHz Cortez -M4F 内核让这些问题迎刃而解。

此处理器可提供更高性能,比如是 M3 内核的两倍性能,而同时功耗只有一半。

大家应该知道低功耗的概念根植于 MSP 的 DNA 中。

我们已将此MSP432器件设计成超低功耗的通用型Cortex-M 微控制器。

在工作模式下功耗仅为 95 uA/MHz,而待机功耗仅为 850nA,其中包括了RTC的功耗。

同时,我们希望用户能充分利用MSP430 的工具链,以及ARM 的工具链,以获得最佳的高性能和低功耗。

现在,由于MSP430平台的延伸,用户可以在16位内核产品和32位内核产品之间自由选择,所有这些产品之间均具有无缝移植能力。

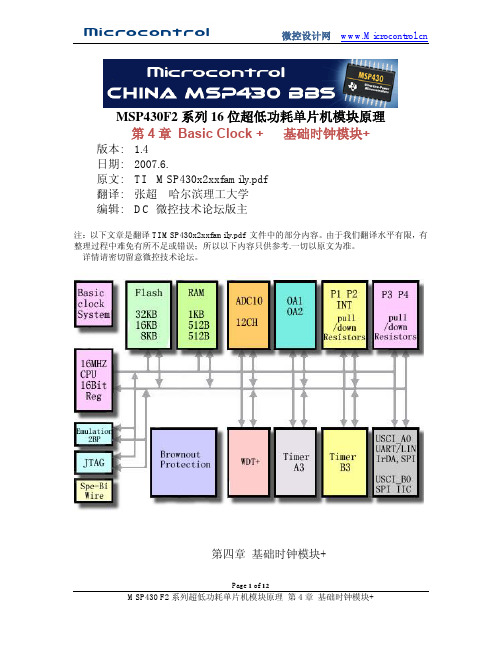

Page 1 of 12MSP430F2系列16位超低功耗单片机模块原理第4章 Basic Clock + 基础时钟模块+版本: 1.4日期: 2007.6.原文: TI MSP430x2xxfamily.pdf翻译: 张超 哈尔滨理工大学编辑: DC 微控技术论坛版主注:以下文章是翻译TI MSP430x2xxfamily.pdf 文件中的部分内容。

由于我们翻译水平有限,有整理过程中难免有所不足或错误;所以以下内容只供参考.一切以原文为准。

详情请密切留意微控技术论坛。

第四章 基础时钟模块+4.1基础时钟模块+介绍基础时钟模块+支持低系统消耗和超低功耗。

采用三种片内时钟信号,用户可以选择合适的性能和低功耗。

基础时钟模块只需接一个外部电阻、一个或两个外部晶体、或者用振荡器,通过软件控制。

基础时钟模块+有4个时钟源:LFXT1CLK:由低频时钟晶体或外接32768Hz时钟源产生的低频/高频振荡器或由标准晶体、振荡器,或外部400KH z~16M Hz的外部时钟源提供。

XT2CLK:可供选择的高频振荡器,由标准晶体、振荡器,或外部400KH z~16M Hz的外部时钟源提供。

DCOCLK:片内可数字控制的振荡器。

VLOCLK:片内超低功耗、12KH z的低频振荡器。

基础时钟模块可提供的三种时钟信号:ACLK:辅助时钟。

ACLK由软件选择来自LFXT1CLK和VLOCLK之一的时钟信号。

ACLK 经1,2,4,8分频后得到。

ACLK可由软件选作各个外围模块。

MCLK:主时钟。

MCLK由软件选择来自LFXT1CLK,VLOCLK,XT2CLK(如果片内提供),DCOCLK之一的时钟信号。

MCLK由1,2,4,8分频得到。

MCLK用于CPU和系统。

SMCLK:子系统时钟。

SMCLK由软件选择来自LFXT1CLK,VLOCLK,XT2CLK(片内提供),DCOCLK之一的时钟信号。

SMCLK由1,2,4,8分频得到。

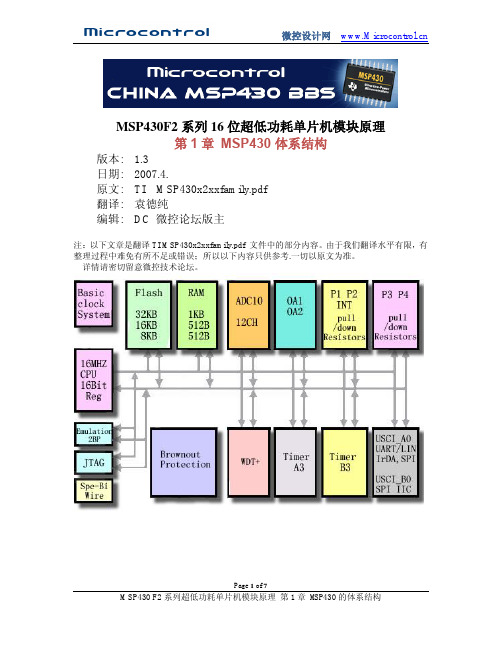

MSP430F2系列16位超低功耗单片机模块原理第1章MSP430体系结构版本: 1.3日期: 2007.4.原文: TI MSP430x2xxfamily.pdf翻译: 袁德纯编辑: DC 微控论坛版主注:以下文章是翻译TI MSP430x2xxfamily.pdf 文件中的部分内容。

由于我们翻译水平有限,有整理过程中难免有所不足或错误;所以以下内容只供参考.一切以原文为准。

详情请密切留意微控技术论坛。

Page 1 of 7第一章 MSP430的体系结构本章主要描述了MSP430的体系结构本章内容目录1.1MSP430的体系结构1.2可编程时钟系统1.3嵌入式仿真环境1.4地址空间1.5MSP430X2XX系列的提高1.1MSP430的体系结构将MSP430内部的16位精简指令集的CPU通过冯.诺依曼结构的地址总线和数据总线连接到外围设备和可编程时钟系统。

由于有一个先进的CPU配合具有标准组件存储印象的模拟和数字的外围设备,使得MSP430可用于处理混合信号。

MSP430x2xx系列的主要特性如下:◆超低功耗延长了电池的使用寿命●保持RAM 0.1uA●实时时钟模式 0.8uA●MIPS运行 250uA◆理想精确的模拟信号测量●门控比较定时器测量电阻类元件◆16位的精简指令集的CPU全新应用●更大的寄存器空间消除了运行空间的瓶颈●紧凑的核结构设计减少了功耗、降低了成本●使得高水平的编程更优化●27条核心指令和7种寻址方式●强大的矢量中断能力◆系统内的可编程FLASH使改变代码、在线升级和数据载入更灵活1.2 可编程时钟系统时钟系统是为电池供电系统而特别设计的。

只需要一个32KHZ的晶振就可以直接驱动一个低频的辅助时钟(ACLK)。

ACLK可工作于实时时钟模式,并具能够自我唤醒。

内部集成了一个DCO使主时钟(MCLK)可以被CPU和其他的高速外围设备所使用。

由于有了DCO,使得一个窄脉冲在少于2US 的时间内就可以将MSP430唤醒CPU工作。

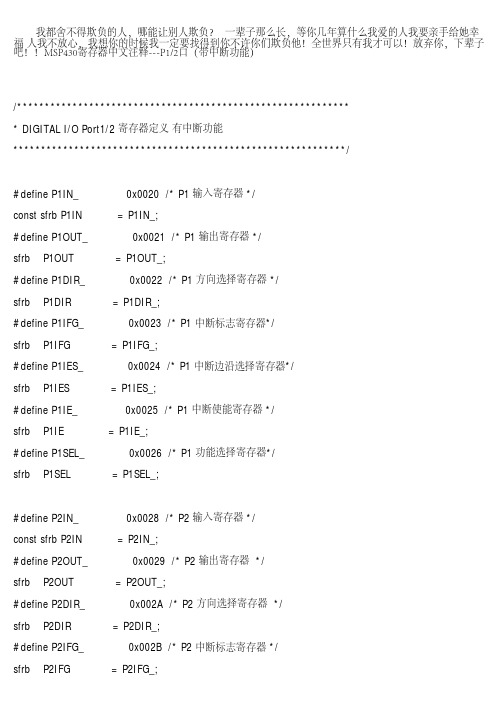

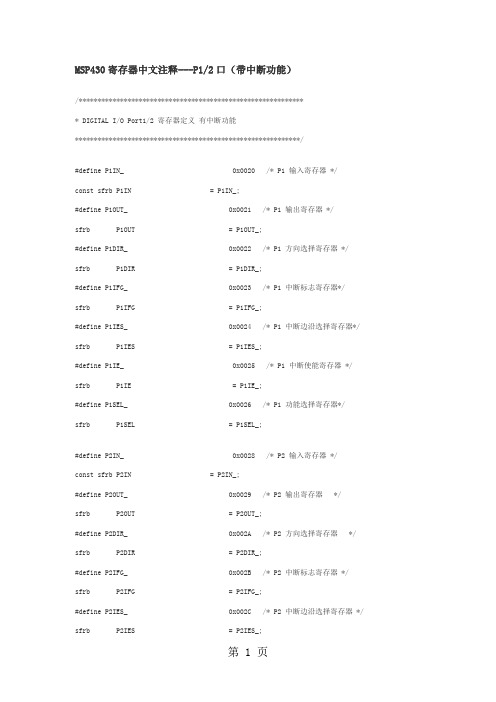

MSP430寄存器中文注释---P1/2口(带中断功能)/************************************************************* DIGITAL I/O Port1/2 寄存器定义有中断功能************************************************************/#define P1IN_ 0x0020 /* P1 输入寄存器 */const sfrb P1IN = P1IN_;#define P1OUT_ 0x0021 /* P1 输出寄存器 */sfrb P1OUT = P1OUT_;#define P1DIR_ 0x0022 /* P1 方向选择寄存器 */sfrb P1DIR = P1DIR_;#define P1IFG_ 0x0023 /* P1 中断标志寄存器*/sfrb P1IFG = P1IFG_;#define P1IES_ 0x0024 /* P1 中断边沿选择寄存器*/ sfrb P1IES = P1IES_;#define P1IE_ 0x0025 /* P1 中断使能寄存器 */ sfrb P1IE = P1IE_;#define P1SEL_ 0x0026 /* P1 功能选择寄存器*/sfrb P1SEL = P1SEL_;#define P2IN_ 0x0028 /* P2 输入寄存器 */const sfrb P2IN = P2IN_;#define P2OUT_ 0x0029 /* P2 输出寄存器 */sfrb P2OUT = P2OUT_;#define P2DIR_ 0x002A /* P2 方向选择寄存器 */ sfrb P2DIR = P2DIR_;#define P2IFG_ 0x002B /* P2 中断标志寄存器 */sfrb P2IFG = P2IFG_;#define P2IES_ 0x002C /* P2 中断边沿选择寄存器 */ sfrb P2IES = P2IES_;#define P2IE_ 0x002D /* P2 中断使能寄存器 */ sfrb P2IE = P2IE_;#define P2SEL_ 0x002E /* P2 功能选择寄存器 */ sfrb P2SEL = P2SEL_;MSP430寄存器中文注释---P3/4口(无中断功能)/************************************************************* DIGITAL I/O Port3/4寄存器定义无中断功能************************************************************/#define P3IN_ 0x0018 /* P3 输入寄存器 */ const sfrb P3IN = P3IN_;#define P3OUT_ 0x0019 /* P3 输出寄存器 */sfrb P3OUT = P3OUT_;#define P3DIR_ 0x001A /* P3 方向选择寄存器 */ sfrb P3DIR = P3DIR_;#define P3SEL_ 0x001B /* P3 功能选择寄存器*/ sfrb P3SEL = P3SEL_;#define P4IN_ 0x001C /* P4 输入寄存器 */ const sfrb P4IN = P4IN_;#define P4OUT_ 0x001D /* P4 输出寄存器 */sfrb P4OUT = P4OUT_;#define P4DIR_ 0x001E /* P4 方向选择寄存器 */ sfrb P4DIR = P4DIR_;#define P4SEL_ 0x001F /* P4 功能选择寄存器 */ sfrb P4SEL = P4SEL_;/************************************************************* DIGITAL I/O Port5/6 I/O口寄存器定义PORT5和6 无中断功能#define P5IN_ 0x0030 /* P5 输入寄存器 */ const sfrb P5IN = P5IN_;#define P5OUT_ 0x0031 /* P5 输出寄存器*/sfrb P5OUT = P5OUT_;#define P5DIR_ 0x0032 /* P5 方向选择寄存器*/ sfrb P5DIR = P5DIR_;#define P5SEL_ 0x0033 /* P5 功能选择寄存器*/ sfrb P5SEL = P5SEL_;#define P6IN_ 0x0034 /* P6 输入寄存器 */ const sfrb P6IN = P6IN_;#define P6OUT_ 0x0035 /* P6 输出寄存器*/sfrb P6OUT = P6OUT_;#define P6DIR_ 0x0036 /* P6 方向选择寄存器*/ sfrb P6DIR = P6DIR_;#define P6SEL_ 0x0037 /* P6 功能选择寄存器*/ sfrb P6SEL = P6SEL_;MSP430寄存器中文注释--- 硬件乘法器/************************************************************硬件乘法器的寄存器定义************************************************************/#define MPY_ 0x0130 /* 无符号乘法 */ sfrw MPY = MPY_;#define MPYS_ 0x0132 /* 有符号乘法*/sfrw MPYS = MPYS_;#define MAC_ 0x0134 /* 无符号乘加 */ sfrw MAC = MAC_;#define MACS_ 0x0136 /* 有符号乘加 */sfrw MACS = MACS_;#define OP2_ 0x0138 /* 第二乘数 */sfrw OP2 = OP2_;#define RESLO_ 0x013A /* 低6位结果寄存器 */sfrw RESLO = RESLO_;#define RESHI_ 0x013C /* 高6位结果寄存器 */sfrw RESHI = RESHI_;#define SUMEXT_ 0x013E /*结果扩展寄存器 */const sfrw SUMEXT = SUMEXT_;MSP430寄存器中文注释---看门狗和定时器/************************************************************* 看门狗定时器的寄存器定义************************************************************/#define WDTCTL_ 0x0120sfrw WDTCTL = WDTCTL_;#define WDTIS0 0x0001 /*选择WDTCNT的四个输出端之一*/#define WDTIS1 0x0002 /*选择WDTCNT的四个输出端之一*/#define WDTSSEL 0x0004 /*选择WDTCNT的时钟源*/#define WDTCNTCL 0x0008 /*清除WDTCNT端: 为1时从0开始计数*/#define WDTTMSEL 0x0010 /*选择模式 0: 看门狗模式; 1: 定时器模式*/#define WDTNMI 0x0020 /*选择NMI/RST 引脚功能 0:为 RST; 1:为NMI*/#define WDTNMIES 0x0040 /*WDTNMI=1时.选择触发延 0:为上升延 1:为下降延*/#define WDTHOLD 0x0080 /*停止看门狗定时器工作 0:启动;1:停止*/#define WDTPW 0x5A00 /* 写密码:高八位*//* SMCLK= 1MHz定时器模式 */#define WDT_MDLY_32 WDTPW+WDTTMSEL+WDTCNTCL /* TSMCLK*2POWER15=32ms 复位状态 */#define WDT_MDLY_8 WDTPW+WDTTMSEL+WDTCNTCL+WDTIS0 /* TSMCLK*2POWER13=8.192ms " */#define WDT_MDLY_0_5 WDTPW+WDTTMSEL+WDTCNTCL+WDTIS1 /* TSMCLK*2POWER9=0.512ms " */#define WDT_MDLY_0_064 WDTPW+WDTTMSEL+WDTCNTCL+WDTIS1+WDTIS0 / * TSMCLK*2POWER6=0.512ms " *//* ACLK=32.768KHz 定时器模式*/#define WDT_ADLY_1000 WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL /* TACLK*2POWER15=1000ms " */#define WDT_ADLY_250 WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL+WDTIS0/* TACLK*2POWER13=250ms " */#define WDT_ADLY_16 WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL+WDTIS1 /* TACLK*2POWER9=16ms " */#define WDT_ADLY_1_9 WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL+WDTIS1+WDTIS0 /* TACL K*2POWER6=1.9ms " *//* SMCLK=1MHz看门狗模式 */#define WDT_MRST_32 WDTPW+WDTCNTCL /* TSMCLK*2POWER15=32ms 复位状态 */#define WDT_MRST_8 WDTPW+WDTCNTCL+WDTIS0 /* TSMCLK*2POWER13=8.192ms " */#define WDT_MRST_0_5 WDTPW+WDTCNTCL+WDTIS1 /* TSMCLK*2POWER9=0.512ms " */ #define WDT_MRST_0_064 WDTPW+WDTCNTCL+WDTIS1+WDTIS0 /* TSMCLK*2POWER6=0.512ms " *//* ACLK=32KHz看门狗模式 */#define WDT_ARST_1000 WDTPW+WDTCNTCL+WDTSSEL /* TACLK*2POWER15=1000ms " */#define WDT_ARST_250 WDTPW+WDTCNTCL+WDTSSEL+WDTIS0 /* TACLK*2POWER13=250ms " */#define WDT_ARST_16 WDTPW+WDTCNTCL+WDTSSEL+WDTIS1 /* TACLK*2POWER9=16ms " */#define WDT_ARST_1_9 WDTPW+WDTCNTCL+WDTSSEL+WDTIS1+WDTIS0 /* TACLK*2POWER6=1.9ms " */MSP430寄存器中文注释---A/D采样寄存器定义/************************************************************* ADC12 A/D采样寄存器定义************************************************************//*ADC12转换控制类寄存器*/#define ADC12CTL0_ 0x0;' /* ADC12 Control 0 */sfrw ADC12CTL0 = ADC12CTL0_;#define ADC12CTL1_ 0x01A2 /* ADC12 Control 1 */sfrw ADC12CTL1 = ADC12CTL1_;/*ADC12中断控制类寄存器*/#define ADC12IFG_ 0x01A4 /* ADC12 Interrupt Flag */sfrw ADC12IFG = ADC12IFG_;#define ADC12IE_ 0x01A6 /* ADC12 Interrupt Enable */sfrw ADC12IE = ADC12IE_;#define ADC12IV_ 0x01A8 /* ADC12 Interrupt Vector Word */sfrw ADC12IV = ADC12IV_;/*ADC12存贮器类寄存器*/#define ADC12MEM_ 0x0140 /* ADC12 Conversion Memory */#ifndef __IAR_SYSTEMS_ICC#define ADC12MEM ADC12MEM_ /* ADC12 Conversion Memory (for assembler) */#else#define ADC12MEM ((int*) ADC12MEM_) /* ADC12 Conversion Memory (for C) */#endif#define ADC12MEM0_ ADC12MEM_ /* ADC12 Conversion Memory 0 */sfrw ADC12MEM0 = ADC12MEM0_;#define ADC12MEM1_ 0x0142 /* ADC12 Conversion Memory 1 */sfrw ADC12MEM1 = ADC12MEM1_;#define ADC12MEM2_ 0x0144 /* ADC12 Conversion Memory 2 */sfrw ADC12MEM2 = ADC12MEM2_;#define ADC12MEM3_ 0x0146 /* ADC12 Conversion Memory 3 */sfrw ADC12MEM3 = ADC12MEM3_;#define ADC12MEM4_ 0x0148 /* ADC12 Conversion Memory 4 */sfrw ADC12MEM4 = ADC12MEM4_;#define ADC12MEM5_ 0x014A /* ADC12 Conversion Memory 5 */sfrw ADC12MEM5 = ADC12MEM5_;#define ADC12MEM6_ 0x014C /* ADC12 Conversion Memory 6 */sfrw ADC12MEM6 = ADC12MEM6_;#define ADC12MEM7_ 0x014E /* ADC12 Conversion Memory 7 */sfrw ADC12MEM7 = ADC12MEM7_;#define ADC12MEM8_ 0x0150 /* ADC12 Conversion Memory 8 */sfrw ADC12MEM8 = ADC12MEM8_;#define ADC12MEM9_ 0x0152 /* ADC12 Conversion Memory 9 */sfrw ADC12MEM9 = ADC12MEM9_;#define ADC12MEM10_ 0x0154 /* ADC12 Conversion Memory 10 */sfrw ADC12MEM10 = ADC12MEM10_;#define ADC12MEM11_ 0x0156 /* ADC12 Conversion Memory 11 */sfrw ADC12MEM11 = ADC12MEM11_;#define ADC12MEM12_ 0x0158 /* ADC12 Conversion Memory 12 */sfrw ADC12MEM12 = ADC12MEM12_;#define ADC12MEM13_ 0x015A /* ADC12 Conversion Memory 13 */sfrw ADC12MEM13 = ADC12MEM13_;#define ADC12MEM14_ 0x015C /* ADC12 Conversion Memory 14 */sfrw ADC12MEM14 = ADC12MEM14_;#define ADC12MEM15_ 0x015E /* ADC12 Conversion Memory 15 */sfrw ADC12MEM15 = ADC12MEM15_;/*ADC12存贮控制类寄存器*/#define ADC12MCTL_ 0x0080 /* ADC12 Memory Control */#ifndef __IAR_SYSTEMS_ICC#define ADC12MCTL ADC12MCTL_ /* ADC12 Memory Control (for assembler) */ #else#define ADC12MCTL ((char*) ADC12MCTL_) /* ADC12 Memory Control (for C) * /#endif#define ADC12MCTL0_ ADC12MCTL_ /* ADC12 Memory Control 0 */sfrb ADC12MCTL0 = ADC12MCTL0_;#define ADC12MCTL1_ 0x0081 /* ADC12 Memory Control 1 */sfrb ADC12MCTL1 = ADC12MCTL1_;#define ADC12MCTL2_ 0x0082 /* ADC12 Memory Control 2 */sfrb ADC12MCTL2 = ADC12MCTL2_;#define ADC12MCTL3_ 0x0083 /* ADC12 Memory Control 3 */sfrb ADC12MCTL3 = ADC12MCTL3_;#define ADC12MCTL4_ 0x0084 /* ADC12 Memory Control 4 */sfrb ADC12MCTL4 = ADC12MCTL4_;#define ADC12MCTL5_ 0x0085 /* ADC12 Memory Control 5 */sfrb ADC12MCTL5 = ADC12MCTL5_;#define ADC12MCTL6_ 0x0086 /* ADC12 Memory Control 6 */sfrb ADC12MCTL6 = ADC12MCTL6_;#define ADC12MCTL7_ 0x0087 /* ADC12 Memory Control 7 */sfrb ADC12MCTL7 = ADC12MCTL7_;#define ADC12MCTL8_ 0x0088 /* ADC12 Memory Control 8 */sfrb ADC12MCTL8 = ADC12MCTL8_;#define ADC12MCTL9_ 0x0089 /* ADC12 Memory Control 9 */sfrb ADC12MCTL9 = ADC12MCTL9_;#define ADC12MCTL10_ 0x008A /* ADC12 Memory Control 10 */sfrb ADC12MCTL10 = ADC12MCTL10_;#define ADC12MCTL11_ 0x008B /* ADC12 Memory Control 11 */sfrb ADC12MCTL11 = ADC12MCTL11_;#define ADC12MCTL12_ 0x008C /* ADC12 Memory Control 12 */sfrb ADC12MCTL12 = ADC12MCTL12_;#define ADC12MCTL13_ 0x008D /* ADC12 Memory Control 13 */sfrb ADC12MCTL13 = ADC12MCTL13_;#define ADC12MCTL14_ 0x008E /* ADC12 Memory Control 14 */sfrb ADC12MCTL14 = ADC12MCTL14_;#define ADC12MCTL15_ 0x008F /* ADC12 Memory Control 15 */sfrb ADC12MCTL15 = ADC12MCTL15_;/* ADC12CTL0 内8位控制寄存器位*/#define ADC12SC 0x001 /*采样/转换控制位*/#define ENC 0x002 /* 转换允许位*/#define ADC12TOVIE 0x004 /*转换时间溢出中断允许位*/#define ADC12OVIE 0x008 /*溢出中断允许位*/#define ADC12ON 0x010 /*ADC12内核控制位*/#define REFON 0x020 /*参考电压控制位*/#define REF2_5V 0x040 /*内部参考电压的电压值选择位 ' 0'为1.5V; '1'为2.5V*/#define MSH 0x080 /*多次采样/转换位*/#define MSC 0x080 /*多次采样/转换位*//*SHT0 采样保持定时器0 控制ADC12的结果存贮器MEM0~MEM7的采样周期*/#define SHT0_0 0*0x100 /*采样周期=TADC12CLK*4 */#define SHT0_1 1*0x100 /*采样周期=TADC12CLK*8 */#define SHT0_2 2*0x100 /*采样周期=TADC12CLK*16 */ #define SHT0_3 3*0x100 /*采样周期=TADC12CLK*32 */ #define SHT0_4 4*0x100 /*采样周期=TADC12CLK*64 */ #define SHT0_5 5*0x100 /*采样周期=TADC12CLK*96 */ #define SHT0_6 6*0x100 /*采样周期=TADC12CLK*128 */ #define SHT0_7 7*0x100 /*采样周期=TADC12CLK*192 */ #define SHT0_8 8*0x100 /*采样周期=TADC12CLK*256 */ #define SHT0_9 9*0x100 /*采样周期=TADC12CLK*384 */ #define SHT0_10 10*0x100 /*采样周期=TADC12CLK*512 */#define SHT0_11 11*0x100 /*采样周期=TADC12CLK*768 */#define SHT0_12 12*0x100 /*采样周期=TADC12CLK*1024 */ #define SHT0_13 13*0x100 /*采样周期=TADC12CLK*1024 */ #define SHT0_14 14*0x100 /*采样周期=TADC12CLK*1024 */ #define SHT0_15 15*0x100 /*采样周期=TADC12CLK*1024 */ /*SHT1 采样保持定时器1 控制ADC12的结果存贮器MEM8~MEM15的采样周期*/#define SHT1_0 0*0x100 /*采样周期=TADC12CLK*4 */#define SHT1_1 1*0x100 /*采样周期=TADC12CLK*8 */#define SHT1_2 2*0x100 /*采样周期=TADC12CLK*16 */ #define SHT1_3 3*0x100 /*采样周期=TADC12CLK*32 */ #define SHT1_4 4*0x100 /*采样周期=TADC12CLK*64 */#define SHT1_5 5*0x100 /*采样周期=TADC12CLK*96 */ #define SHT1_6 6*0x100 /*采样周期=TADC12CLK*128 */ #define SHT1_7 7*0x100 /*采样周期=TADC12CLK*192 */ #define SHT1_8 8*0x100 /*采样周期=TADC12CLK*256 */ #define SHT1_9 9*0x100 /*采样周期=TADC12CLK*384 */ #define SHT1_10 10*0x100 /*采样周期=TADC12CLK*512 */ #define SHT1_11 11*0x100 /*采样周期=TADC12CLK*768 */ #define SHT1_12 12*0x100 /*采样周期=TADC12CLK*1024 */ #define SHT1_13 13*0x100 /*采样周期=TADC12CLK*1024 */ #define SHT1_14 14*0x100 /*采样周期=TADC12CLK*1024 */ #define SHT1_15 15*0x100 /*采样周期=TADC12CLK*1024 *//* ADC12CTL1 内8位控制寄存器位*/#define ADC12BUSY 0x0001 /*ADC12忙标志位*/#define CONSEQ_0 0*2 /*单通道单次转换*/#define CONSEQ_1 1*2 /*序列通道单次转换*/#define CONSEQ_2 2*2 /*单通道多次转换*/#define CONSEQ_3 3*2 /*序列通道多次转换*/#define ADC12SSEL_0 0*8 /*ADC12内部时钟源*/#define ADC12SSEL_1 1*8 /*ACLK*/#define ADC12SSEL_2 2*8 /*MCLK*/#define ADC12SSEL_3 3*8 /*SCLK*/#define ADC12DIV_0 0*0x20 /*1分频*/#define ADC12DIV_1 1*0x20 /*2分频*/#define ADC12DIV_2 2*0x20 /*3分频*/#define ADC12DIV_3 3*0x20 /*4分频*/#define ADC12DIV_4 4*0x20 /*5分频*/#define ADC12DIV_5 5*0x20 /*6分频*/#define ADC12DIV_6 6*0x20 /*7分频*/#define ADC12DIV_7 7*0x20 /*8分频*/#define ISSH 0x0100 /*采样输入信号反向与否控制位*/#define SHP 0x0200 /*采样信号(SAMPCON)选择控制位*/#define SHS_0 0*0x400 /*采样信号输入源选择控制位 A DC12SC*/#define SHS_1 1*0x400 /*采样信号输入源选择控制位 T IMER_A.OUT1*/#define SHS_2 2*0x400 /*采样信号输入源选择控制位 T IMER_B.OUT0*/#define SHS_3 3*0x400 /*采样信号输入源选择控制位 T IMER_B.OUT1*//*转换存贮器地址定义位*/#define CSTARTADD_0 0*0x1000 /*选择MEM0首地址*/#define CSTARTADD_1 1*0x1000 /*选择MEM1首地址*/#define CSTARTADD_2 2*0x1000 /*选择MEM2首地址*/#define CSTARTADD_3 3*0x1000 /*选择MEM3首地址*/#define CSTARTADD_4 4*0x1000 /*选择MEM4首地址*/#define CSTARTADD_5 5*0x1000 /*选择MEM5首地址*/#define CSTARTADD_6 6*0x1000 /*选择MEM6首地址*/#define CSTARTADD_7 7*0x1000 /*选择MEM7首地址*/#define CSTARTADD_8 8*0x1000 /*选择MEM8首地址*/#define CSTARTADD_9 9*0x1000 /*选择MEM9首地址*/#define CSTARTADD_10 10*0x1000 /*选择MEM10首地址*/#define CSTARTADD_11 11*0x1000 /*选择MEM11首地址*/#define CSTARTADD_12 12*0x1000 /*选择MEM12首地址*/#define CSTARTADD_13 13*0x1000 /*选择MEM13首地址*/#define CSTARTADD_14 14*0x1000 /*选择MEM14首地址*/#define CSTARTADD_15 15*0x1000 /*选择MEM15首地址*//* ADC12MCTLx */#define INCH_0 0 /*选择模拟量通道0 A0 */#define INCH_1 1 /*选择模拟量通道0 A1*/#define INCH_2 2 /*选择模拟量通道0 A2*/#define INCH_3 3 /*选择模拟量通道0 A3*/#define INCH_4 4 /*选择模拟量通道0 A4*/#define INCH_5 5 /*选择模拟量通道0 A5*/#define INCH_6 6 /*选择模拟量通道0 A6*/#define INCH_7 7 /*选择模拟量通道0 A7*/#define INCH_8 8 /*VEREF+*/#define INCH_9 9 /*VEREF-*/#define INCH_10 10 /*片内温度传感器的输出*/#define INCH_11 11 /*(AVCC-AVSS)/2*/ #define INCH_12 12 /*(AVCC-AVSS)/2*/ #define INCH_13 13 /*(AVCC-AVSS)/2*/ #define INCH_14 14 /*(AVCC-AVSS)/2*/ #define INCH_15 15 /*(AVCC-AVSS)/2*/ /*参考电压源选择位*/#define SREF_0 0*0x10 /*VR+ = AVCC; VR- = AVSS*/#define SREF_1 1*0x10 /*VR+ = VREF+; VR- = AVSS*/#define SREF_2 2*0x10 /*VR+ = VEREF+; VR- = AVSS*/#define SREF_3 3*0x10 /*VR+ = VEREF+; VR- = AVSS*/#define SREF_4 4*0x10 /*VR+ = AVCC; VR- = VREF-*/#define SREF_5 5*0x10 /*VR+ = VREF+; VR- = VREF-*/#define SREF_6 6*0x10 /*VR+ = VEREF+; VR- = VREF-*/#define SREF_7 7*0x10 /*VR+ = VEREF+; VR- = VREF-*/#define EOS 0x80 /*序列结束选择位*/MSP430寄存器中文注释----串口寄存器/************************************************************* USART 串口寄存器"UCTL","UTCTL","URCTL"定义的各个位可串口1 串口2公用************************************************************//* UCTL 串口控制寄存器*/#define PENA 0x80 /*校验允许位*/#define PEV 0x40 /*偶校验为0时为奇校验*/ #define SPB 0x20 /*停止位为2 为0时停止位为1* /#define CHAR 0x10 /*数据位为8位为0时数据位为7位*/#define LISTEN 0x08 /*自环模式(发数据同时在把发的数据接收回来)*/#define SYNC 0x04 /*同步模式为0异步模式*/#define MM 0x02 /*为1时地址位多机协议(异步)主机模式(同步);为0时线路空闲多机协议(异步) 从机模式(同步)*/#define SWRST 0x01 /*控制位*//* UTCTL 串口发送控制寄存器*/#define CKPH 0x80 /*时钟相位控制位(只同步方式用)为1时时钟UCLK延时半个周期*/#define CKPL 0x40 /*时钟极性控制位为1时异步与U CLK相反;同步下降延有效*/#define SSEL1 0x20 /*时钟源选择位:与SSEL0组合为0, 1,2,3四种方式*/#define SSEL0 0x10 /*"0"选择外部时钟,"1"选择辅助时钟,"2","3"选择系统子时钟 */#define URXSE 0x08 /*接收触发延控制位(只在异步方式下用)*/#define TXWAKE 0x04 /*多处理器通信传送控制位(只在异步方式下用)*/#define STC 0x02 /*外部引脚STE选择位为0时为4线模式为1时为3线模式*/#define TXEPT 0x01 /*发送器空标志*//* URCTL 串口接收控制寄存器同步模式下只用两位:FE和OE*/#define FE 0x80 /*帧错标志*/#define PE 0x40 /*校验错标志位*/#define OE 0x20 /*溢出标志位*/#define BRK 0x10 /*打断检测位*/#define URXEIE 0x08 /*接收出错中断允许位*/#define URXWIE 0x04 /*接收唤醒中断允许位*/ #define RXWAKE 0x02 /*接收唤醒检测位*/#define RXERR 0x01 /*接收错误标志位*//************************************************************* USART 0 串口0寄存器定义************************************************************/#define U0CTL_ 0x0070 /* UART 0 Control */sfrb U0CTL = U0CTL_;#define U0TCTL_ 0x0071 /* UART 0 Transmit Control */sfrb U0TCTL = U0TCTL_;#define U0RCTL_ 0x0072 /* UART 0 Receive Control */sfrb U0RCTL = U0RCTL_;#define U0MCTL_ 0x0073 /* UART 0 Modulation Control */sfrb U0MCTL = U0MCTL_;#define U0BR0_ 0x0074 /* UART 0 Baud Rate 0 */sfrb U0BR0 = U0BR0_;#define U0BR1_ 0x0075 /* UART 0 Baud Rate 1 */sfrb U0BR1 = U0BR1_;#define U0RXBUF_ 0x0076 /* UART 0 Receive Buffer */const sfrb U0RXBUF = U0RXBUF_;#define U0TXBUF_ 0x0077 /* UART 0 Transmit Buffer */sfrb U0TXBUF = U0TXBUF_;/* Alternate register names */#define UCTL0_ 0x0070 /* UART 0 Control */sfrb UCTL0 = UCTL0_;#define UTCTL0_ 0x0071 /* UART 0 Transmit Control */sfrb UTCTL0 = UTCTL0_;#define URCTL0_ 0x0072 /* UART 0 Receive Control */ sfrb URCTL0 = URCTL0_;#define UMCTL0_ 0x0073 /* UART 0 Modulation Control */ sfrb UMCTL0 = UMCTL0_;#define UBR00_ 0x0074 /* UART 0 Baud Rate 0 */sfrb UBR00 = UBR00_;#define UBR10_ 0x0075 /* UART 0 Baud Rate 1 */sfrb UBR10 = UBR10_;#define RXBUF0_ 0x0076 /* UART 0 Receive Buffer */ const sfrb RXBUF0 = RXBUF0_;#define TXBUF0_ 0x0077 /* UART 0 Transmit Buffer */ sfrb TXBUF0 = TXBUF0_;#define UCTL_0_ 0x0070 /* UART 0 Control */sfrb UCTL_0 = UCTL_0_;#define UTCTL_0_ 0x0071 /* UART 0 Transmit Control */ sfrb UTCTL_0 = UTCTL_0_;#define URCTL_0_ 0x0072 /* UART 0 Receive Control */sfrb URCTL_0 = URCTL_0_;#define UMCTL_0_ 0x0073 /* UART 0 Modulation Control */ sfrb UMCTL_0 = UMCTL_0_;#define UBR0_0_ 0x0074 /* UART 0 Baud Rate 0 */sfrb UBR0_0 = UBR0_0_;#define UBR1_0_ 0x0075 /* UART 0 Baud Rate 1 */sfrb UBR1_0 = UBR1_0_;#define RXBUF_0_ 0x0076 /* UART 0 Receive Buffer */ const sfrb RXBUF_0 = RXBUF_0_;#define TXBUF_0_ 0x0077 /* UART 0 Transmit Buffer */sfrb TXBUF_0 = TXBUF_0_;/************************************************************* USART 1 串口1寄存器定义************************************************************/#define U1CTL_ 0x0078 /* UART 1 Control */sfrb U1CTL = U1CTL_;#define U1TCTL_ 0x0079 /* UART 1 Transmit Control */ sfrb U1TCTL = U1TCTL_;#define U1RCTL_ 0x007A /* UART 1 Receive Control */ sfrb U1RCTL = U1RCTL_;#define U1MCTL_ 0x007B /* UART 1 Modulation Control */ sfrb U1MCTL = U1MCTL_;#define U1BR0_ 0x007C /* UART 1 Baud Rate 0 */sfrb U1BR0 = U1BR0_;#define U1BR1_ 0x007D /* UART 1 Baud Rate 1 */sfrb U1BR1 = U1BR1_;#define U1RXBUF_ 0x007E /* UART 1 Receive Buffer */ const sfrb U1RXBUF = U1RXBUF_;#define U1TXBUF_ 0x007F /* UART 1 Transmit Buffer */sfrb U1TXBUF = U1TXBUF_;#define UCTL1_ 0x0078 /* UART 1 Control */sfrb UCTL1 = UCTL1_;#define UTCTL1_ 0x0079 /* UART 1 Transmit Control */ sfrb UTCTL1 = UTCTL1_;#define URCTL1_ 0x007A /* UART 1 Receive Control */ sfrb URCTL1 = URCTL1_;#define UMCTL1_ 0x007B /* UART 1 Modulation Control */ sfrb UMCTL1 = UMCTL1_;#define UBR01_ 0x007C /* UART 1 Baud Rate 0 */sfrb UBR01 = UBR01_;#define UBR11_ 0x007D /* UART 1 Baud Rate 1 */sfrb UBR11 = UBR11_;#define RXBUF1_ 0x007E /* UART 1 Receive Buffer */ const sfrb RXBUF1 = RXBUF1_;#define TXBUF1_ 0x007F /* UART 1 Transmit Buffer */ sfrb TXBUF1 = TXBUF1_;#define UCTL_1_ 0x0078 /* UART 1 Control */sfrb UCTL_1 = UCTL_1_;#define UTCTL_1_ 0x0079 /* UART 1 Transmit Control */ sfrb UTCTL_1 = UTCTL_1_;#define URCTL_1_ 0x007A /* UART 1 Receive Control */ sfrb URCTL_1 = URCTL_1_;#define UMCTL_1_ 0x007B /* UART 1 Modulation Control */ sfrb UMCTL_1 = UMCTL_1_;#define UBR0_1_ 0x007C /* UART 1 Baud Rate 0 */sfrb UBR0_1 = UBR0_1_;#define UBR1_1_ 0x007D /* UART 1 Baud Rate 1 */sfrb UBR1_1 = UBR1_1_;#define RXBUF_1_ 0x007E /* UART 1 Receive Buffer */ const sfrb RXBUF_1 = RXBUF_1_;#define TXBUF_1_ 0x007F /* UART 1 Transmit Buffer */ sfrb TXBUF_1 = TXBUF_1_;。

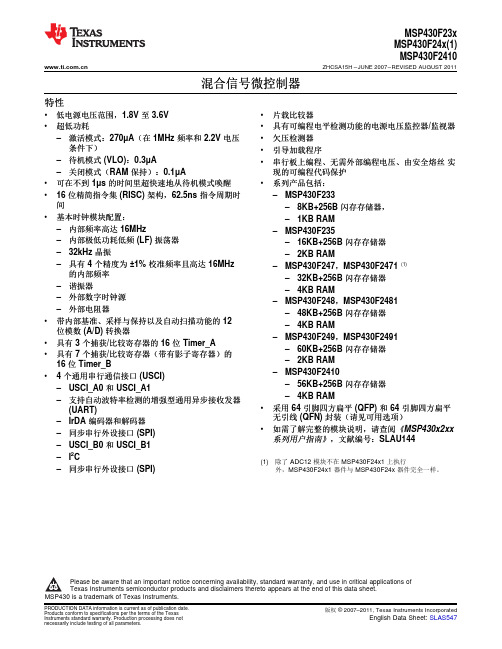

MSP430F23xMSP430F24x(1)MSP430F2410 ZHCSA15H–JUNE2007–REVISED AUGUST2011混合信号微控制器特性•低电源电压范围,1.8V至3.6V•片载比较器•超低功耗•具有可编程电平检测功能的电源电压监控器/监视器–激活模式:270μA(在1MHz频率和2.2V电压•欠压检测器条件下)•引导加载程序–待机模式(VLO):0.3μA•串行板上编程、无需外部编程电压、由安全熔丝实–关闭模式(RAM保持):0.1μA现的可编程代码保护•可在不到1μs的时间里超快速地从待机模式唤醒•系列产品包括:•16位精简指令集(RISC)架构,62.5ns指令周期时–MSP430F233间–8KB+256B闪存存储器,•基本时钟模块配置:–1KB RAM–内部频率高达16MHz–MSP430F235–内部极低功耗低频(LF)振荡器–16KB+256B闪存存储器–32kHz晶振–2KB RAM–具有4个精度为±1%校准频率且高达16MHz–MSP430F247,MSP430F2471(1)的内部频率–32KB+256B闪存存储器–谐振器–4KB RAM–外部数字时钟源–MSP430F248,MSP430F2481–外部电阻器–48KB+256B闪存存储器•带内部基准、采样与保持以及自动扫描功能的12–4KB RAM位模数(A/D)转换器–MSP430F249,MSP430F2491•具有3个捕获/比较寄存器的16位Timer_A–60KB+256B闪存存储器•具有7个捕获/比较寄存器(带有影子寄存器)的–2KB RAM16位Timer_B–MSP430F2410•4个通用串行通信接口(USCI)–56KB+256B闪存存储器–USCI_A0和USCI_A1–4KB RAM–支持自动波特率检测的增强型通用异步接收发器•采用64引脚四方扁平(QFP)和64引脚四方扁平(UART)无引线(QFN)封装(请见可用选项)–IrDA编码器和解码器•如需了解完整的模块说明,请查阅《MSP430x2xx –同步串行外设接口(SPI)系列用户指南》,文献编号:SLAU144–USCI_B0和USCI_B1–I2C(1)除了ADC12模块不在MSP430F24x1上执行–同步串行外设接口(SPI)外,MSP430F24x1器件与MSP430F24x器件完全一样。

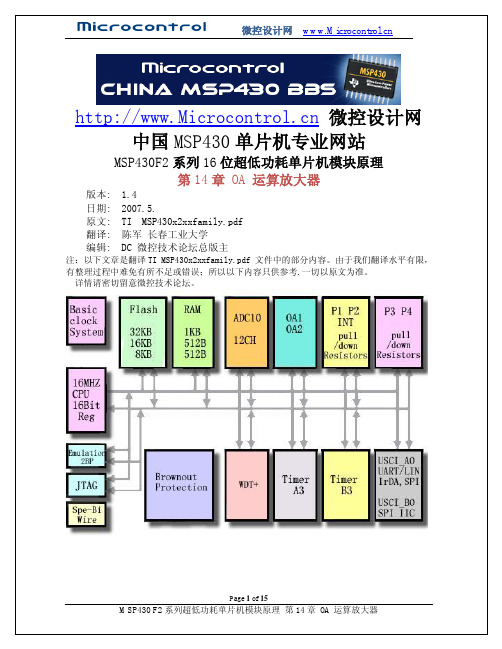

Page 1 of 15MSP430F2系列16位超低功耗单片机模块原理第14章 OA 运算放大器版本: 1.4 日期: 2007.5.原文: TI MSP430x2xxfamily.pdf 翻译: 陈军 长春工业大学 编辑: DC 微控技术论坛版主注:以下文章是翻译TI MSP430x2xxfamily.pdf 文件中的部分内容。

由于我们翻译水平有限,有整理过程中难免有所不足或错误;所以以下内容只供参考.一切以原文为准。

详情请密切留意微控技术论坛。

第14章 OAOA 是通用运算放大器。

本章描述了OA 。

在MSP430x22x4配置了两个OA 模块。

14.1 OA简介OA可用于在AD转换前的模拟信号调理。

OA特征如下:l单电源供电,工作电流低;l轨对轨输出;l可通过程序设置稳定时间;l可通过软件选择配置模式;l可通过软件选择反馈电阻,以应用在PGA(比例增益放大器)上。

注意:多OA模块有些芯片内置了一个以上的OA模块。

在这种情况下,各OA模块独立工作。

在本节里,会出现如OAxCTL0这样的用来描述寄存器名字的术语。

这时,x常用来表示讨论的是哪个OA模块。

独立工作时,寄存器像OAxCTL0这样简写。

Page 2 of 15图14-1 OA模块框图14.2 OA操作OA模块由用户通过软件设置。

下面部分将讨论OA的设置和操作。

Page 3 of 15Page 4 of 1514.2.1 OA 放大器OA 是可配置、低电流、轨对轨输出的运算放大器。

它可以被配置成反相放大器,或同相放大器,或与其它OA 模块组合形成差分放大器。

OA 的输出反馈速率可以用OAPMx 位配置成最佳的稳定时间。

当OAPMx = 00时,OA 关闭,输出为高阻态。

当OAPMx > 0时, OA 打开。

参数见具体的模块数据手册。

14.2.2 OA 输入OA 具有可配置的输入选择。

+和-端输入可以通过OANx and OAPx 位进行独立选择,可以选择为外部信号或内部信号。

OA0I1提供一个同相输入,在所有OA 模块的内部都有同相输入。

OAxIA 和OAxIB 提供依赖器件的输入。

信号连接参考器件数据手册。

当外部反相输入不需要时,置位OANEXT 位,可以使内部反相输入用于外部。

14.2.3 OA 输出和反馈线路OA 具有可配置的输出选择,由OAADCx 位和OAFCx 位控制。

OA 输出信号可以在内部供给ADC10输入的A12(OA0), A13 (OA1)和A14 (OA2),或者连接到这些ADC 的输入和其外部引脚。

OA 输出也可以通过设置OAFCx 位连接到一个内部梯形电阻网络。

梯形电阻网络抽头可由OAFBRx 位选择,具有可编程增益放大功能。

表14-1 表明了OA 输出和反馈线路配置。

当OAFCx = 0时,OA 为通用模式,器件的反馈在外部完成。

当OAFCx > 0 和OAADCx = 00 或11时,OA 的输出通过内部路径连接到器件。

当OAFCx > 0 和OAADCx= 01或10, OA 输出由内部和外部路径连接到器件。

表14-1 OA 输出配置OAFCx OAADCx OA 输出和反馈线路 = 0 x0 OAxOUT 连接到外部引脚和ADC 输入的 A1, A3或 A5. = 0 x1 OAxOUT 连接到外部引脚和ADC 输入的 A12, A13或A14. > 0 00 OAxOUT 只用作内部线路. > 0 01 OAxOUT 连接到外部引脚和ADC 输入的 A12, A13或A1 > 0 10 OAxOUT 连接到外部引脚和ADC 输入的 A1, A3或 A5.> 0 11OAxOUT 通过内部连接到ADC 输入的 A12, A13或 A14。

外部A12,A13或 A14 引脚与ADC 连接断开。

14.2.4 OA 配置OA 可以通过OAFCx 位配置具有不同的放大功能,见表14-2。

表14-2 OA 模式选择OAFCx OA 模式 000 通用运算放大器 001 用于三运放差分放大器的单位增益缓冲器 010 单位缓冲器(相当于电压跟随器) 011 比较器 100 同相PGA(比例放大)放大器 101 级连同相PGA 放大器 110 反相PGA 放大器 111 差分放大器通用运算放大器模式在该模式下,反馈梯形电阻网络与OAx是独立的,由OAxCTL0位定义信号路径。

OAx输入由OAPx和OANx位选择。

OAx输出可以通过OAxCTL0位来选择连接到ADC10输入通道。

用于差分放大器的单位增益模式该模式下,OAx的输出连接到OAx的反相输入端,OAx提供一个单位增益缓冲器。

同相输入由OAPx位选择。

连接到反相输入端的外部连接禁止,OANx位无需关注(状态任意)。

OAx的输出连接到梯形电阻网络,作为三运放差分放大器的一部分。

该模式只用于三运放差分放大器结构。

单位增益模式该模式下,OAx的输出连接到OAx的反相输入端,OAx提供一个单位增益缓冲器(也称为电压跟随器)。

同相输入由OAPx位选择。

连接到反相输入端的外部连接禁止,OANx位无需关注。

OAx输出可以通过OAxCTL0位来选择连接到ADC10输入通道。

比较器模式该模式下,反馈梯形电阻网络与OAx是独立的。

当OARRIP = 0时,RTOP连接到AVSS,RBOTTOM 连接到AVCC。

当OARRIP = 1时,梯形电阻网络的连接反相,RTOP连接到AVCC,RBOTTOM 连接到AVSS。

OAxTAP信号连接到OAx的反相输入端,OAx提供一个具有可编程门限电压的比较器,该电压由OAFBRx位确定。

同相输入端由OAPx位确定。

通过外部反相反馈电阻可以增加延迟。

反相输入端的外部连接被禁止,OANx位无需关注。

OAx输出可以通过OAxCTL0位来选择连接到ADC10输入通道。

同相PGA模式该模式下,OAx的输出连接到RTOP,RBOTTOM连接到AVSS。

OAxTAP连接到OAx的反相输入端。

OAx提供一个具有[1+OAxTAP比值]增益的可编程同相放大器。

OAxTAP 比值由OAFBRx选择,如果OAFBRx=0,增益是1。

同相输入由OAPx位选择。

反相输入引脚上的外部连接被禁止,OANx 位无需关注(状态任意)。

OAx输出可以通过OAxCTL0位来选择连接到ADC10输入通道。

级联同相PGA模式该模式允许OA信号在内部按照反相模式级联2个或3个OA。

该模式下,当OAPx = 11时,OAx的反相输入连接到OA2OUT (OA0), OA0OUT (OA1)或OA1OUT (OA2)。

OAx输出可以通过OAxCTL0位来选择连接到ADC10输入通道。

反相PGA模式该模式下,OAx的输出连接到RTOP, RBOTTOM连接到一个模拟多路复用器,它可以复用OAxI0, OAxI1, OAxIA或由OANx位选择的剩余的一个OAs的输出。

OAxTAP信号连接到OAx的反相输入端。

OAx提供一个具有-OAxTAP比值增益的反相放大器。

OAxTAP比值由OAFBRx位选择。

OAPx位确定同相输入。

OAx输出可以通过OAxCTL0位来选择连接到ADC10输入通道。

注意:使用OAx负输入同时用作ADC输入当引脚连接到反相输入多路复用器时,也被用作了ADC的输入,由于内部线路上的压降,转换结果的误差可能上升到5mV。

差分放大器模式该模式允许OA信号在内部连接形成一个两运放或三运放的仪表放大器。

图14-2表示了OA0和OA1构成的两运放配置。

该模式下,通过经由反相PGA模式下的另一OAx,OAx的输出连接到Page 5 of 15Page 6 of 15RTOP 。

RBOTTOM 断开,提供一个单位增益缓冲器。

该缓冲器与1到2个剩下的OAx 组合形成差分放大器。

OAx 输出可以通过OAxCTL0位来选择连接到ADC10输入通道。

图14-2表示了一个由OA0和OA1构成的两运放差分放大器。

控制寄存器设置见表14-3。

放大器的增益由OA1的OAFBRx 位决定,见表14-4。

OAx 的相互连接见图14-3。

表14-3 两运放差分放大器控制寄存器设置寄存器 设置(二进制) OA0CTL0 xx xx xx 0 0 OA0CTL1 000 111 0 x表14-3 两运放差分放大器增益设置OA1 OAFBRxGain 0000 001 1/3 010 1 011 1 2/3 100 3 101 4 1/3 110 7 11115图14-2 两运放差分放大器图14-3 两运放差分放大器OAx相互连接图14-4表示了使用OA0,OA1,OA2构成的三运放差分放大器。

(三运放不是在所有的器件中都具有,参见具体的器件数据手册)。

控制寄存器的设置见表14-5。

其增益由OA0,OA2的OAFBRx 位确定。

OA0,OA2的OAFBRx位的设定必须相同。

增益设置见表14-6。

OAx相互连接见表14-5。

Page 7 of 15Page 8 of 15表14-5 三运放差分放大器控制寄存器设置寄存器 设置(二进制) OA0CTL0 xx xx xx 0 0 OA0CTL1 xxx 001 0 x OA1CTL0 xx xx xx 0 0表14-6 三运放差分放大器增益设置 OA0/OA2 OAFBRx Gain000 0001 1/3 010 1 011 1 2/3 100 3 101 4 1/3 110 7 11115图14-4 三运放差分放大器图14-5 三运放差分放大器OAx相互连接14.3 OA寄存器寄存器格式寄存器类型地址初始化状态OA0控制寄存器0 OA0CTL0 读/写0C0h 复位和POR OA0控制寄存器1 OA0CTL1 读/写0C1h 复位和PORPage 9 of 15Page 10 of 15OA1 控制寄存器0 OA1CTL0 读/写 0C2h 复位和POR OA1控制寄存器1 OA1CTL1 读/写 0C3h 复位和POR OA2控制寄存器0 OA2CTL0 读/写 0C4h 复位和POR OA2控制寄存器1 OA2CTL1读/写 0C5h 复位和POROAxCTL0, 运放控制寄存器0OANx Bits7-6 反相输入选择。

这两位用于选择OA 反相输入端的输入信号。

00 OAxI0 01 OAxI110 OAxIA -连接信号参考数据手册 11 OAxIB -连接信号参考数据手册OAPx Bits5-4 同相输入选择。

这两位用于选择OA 同相输入端的输入信号。

00 OAxI0 01 OA0I110 OAxIA -连接信号参考数据手册 11 OAxIB -连接信号参考数据手册OAPMx Bits3-2 反馈速率选择。