实现Folded—Cascode放大器快速建立的时钟馈通频率补偿

- 格式:pdf

- 大小:187.61 KB

- 文档页数:5

折叠式共源-共栅运算跨导放大器姓名:刘淑杰学号:U200714149班级:2007级2班院系:控制系专业:测控技术与仪器同组人姓名:黄大龙葛金炬目录1设计目标 02相关背景知识 (1)(1)课题背景 (1)(2)题目理解 (1)3设计过程 (2)3.1 电路结构设计 (2)3.2 主要电路参数的手工推导 (2)3.3计算DC 增益 (3)3.4计算GBW (5)3.5实际计算 (7)3.6参数验证 (9)4 电路仿真 (10)4.1 用于仿真的电路图 (10)4.2 仿真网表 (10)4.3 仿真波形 (12)5 讨论 (14)收获和建议 (15)参考文献 (17)1设计目标设计一款折叠式共源-共栅跨导运算放大器(Design a Folded Cascode OTA),其设计指标见下表,参考电路原理图如下图所示,用0.35um coms工艺。

Cload DC Gain GBW Vdd Idd3pF 40dB~50dB 300MHz 3V Don’t Care图:折叠式共源-共栅跨导运算放大器设计步骤与要点:1.直流工作点的分析与设计(DC operation point design and analysis)1) 假设所有的MOS管均工作在饱和区,VGS-VT=200mV,VDD=3V,VSS= 0V,计算OTA的最大输出摆幅。

2) 基于0.35 um CMOS工艺,计算和设计MOS管的尺寸,使OTA电路满足最大输出摆幅的要求。

3) 以下数据可供设计参考L1,2,3,4 = Lmin; Lmin= 1μm。

2.在HSpice电路仿真软件,对所设计的电路进行模拟仿真与设计2相关背景知识(1)课题背景共源共栅级的普及有两个主要原因。

第一个主要原因是它们由于大输入阻抗,对单级有相当大的增益。

为了得到这个高增益,与输出节点相连的镜像电流源可以用高质量共源共栅镜像电流源实现。

通常,得到这个高增益不会导致任何速度降低,而且有时还会提高速度。

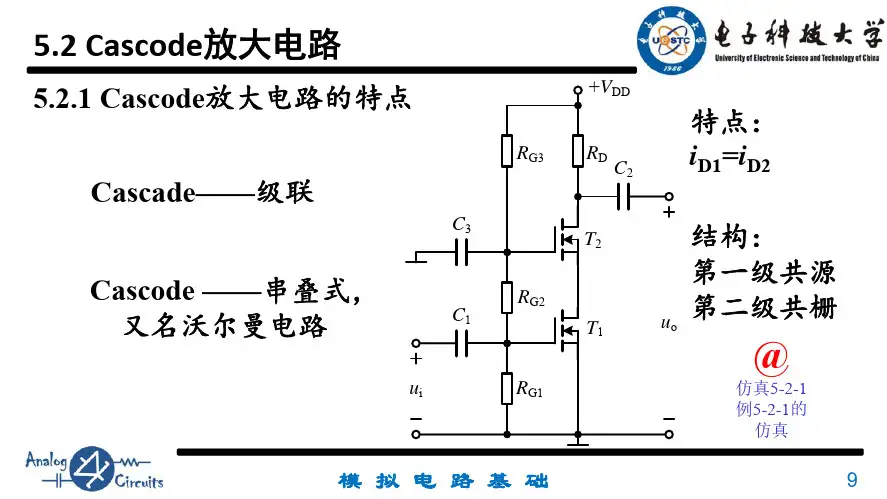

5.2.1 Cascode 放大电路的特点C 1C 2+V DD R DR G1T 2T 1R G2R G3u ou iC 3Cascode ——串叠式,又名沃尔曼电路Cascade——级联特点:i D1=i D2结构:第一级共源第二级共栅@仿真5-2-1例5-2-1的仿真5.2.2中频段动态参数D1m 1gs D1gs 1m i o up R g u R u g u u A -=-== 2G G1i //R R R = Do R R =与单管共源放大电路一致!2gs 2m 1gs 1m u g u g =假设两个管子特性一致!2gs 1gs u u =单看第一级放大倍数1up -=A 第一级不提供电压放大,放大倍数由第二级共栅放大提供5.2.3 Cascode 放大电路的频率响应1、下限频率()1G2G11i L1//π21π21C R R C R f ==()()0π21π212L D 2L o L2=+=+=C R R C R R f ()33G G2L3//π21C R R f =R G1R G2u i u gs1g m1u gs1g m2u gs2u gs2R Du oC gd1C gs1C ds1C gs2 C ds2 C gd2C 1C 2C 3R G35.2 Cascode 放大电路5.2.3 Cascode 放大电路的频率响应gdD gd2D H π21π21C R C R f ==2、上限频率R G1R G2u i u gs1g m1u gs1g m2u gs2u gs2R Du oC gs2 C ds2C gd2 C gd1+C ds1 R G1R G2u i u gs1g m1u gs1g m2u gs2u gs2R Du oC ds2 C gd2第一级近似第二级近似∵第一级|A up |=1忽略电容忽略电容@仿真5-2-2Cascode 电路与单级共源放大电路比较。

摘 要随着电路系统数字化程度的不断提高,尤其是片上系统(SOC)的快速发展,作为连接模拟信号与数字信号的桥梁的高性能模数转换器的需求日益增强。

与其它结构相比,流水线ADC因其在高精度、高速度与低功耗之间拥有良好的折中而备受青睐。

本文采用韩国东部半导体dongbu013工艺,设计研究了一个50MSample/s的12位的流水线ADC。

在查阅大量文献的前提下,本文根据模拟IC设计流程,以高速、低压、低功耗为目标,逐步完成了各个模块电路以及整体电路的设计。

主要工作包括:(1)完成两相不交叠时钟电路的设计;自举开关电路(为消除开关电荷注入误差)设计;为保证开关电容电路的速度和精度设计了增益增强型折叠共源共栅运算放大器;动态锁存比较器电路设计。

(2)由单元电路完成各个子模块电路的设计,并对各个模块和整体系统进行详细仿真。

(3)为降低功耗采用电容和运算放大器逐级递减技术,为克服比较器失调误差设计了数字校正电路。

本设计在Cadence工作平台下,使用Spectre仿真器进行模拟验证。

模拟仿真结果表明,在+1.2V电源电压下,ADC的模拟信号输入范围为0.4V~0.8V,分辨率为12位,采样速率达50MHz,功耗约为84mW。

该流水线ADC的性能指标达到了设计要求。

关键词:流水线ADC;自举开关;开关电容电路;数字校正AbstractAs a bridge connecting the analog signal and digital signal, the demand of the high-performance analog-to-digital converter has growing rapidly with the digitalization of the circuit system, especially the rapid development of the system on chip. Compared with other structures, the pipeline ADC has a good favor because of its good compromise between the high resolution, high speed and low power consumption. In this thesis, a 50MSPS, 12bit ADC was designed in dongbu 0.13um process.Access to a large number of documents, this paper completes the design of each module circuit and the overall circuit step by step with the goal of high speed, low voltage and low power consumption, according to the Analog IC design flow. The main work of this paper is as follows. Firstly, completing the circuit design of the two-phase non-overlapping clock generator; the bootstrapped switch, which can eliminate the switch charge injection error; the gain enhanced folded cascode operational amplifier, which can ensure the speed and accuracy of the switch capacitor circuits, and the dynamic latch comparator. Secondly, completing the circuit design of each sub-module by the unit circuit, and simulating each module and the overall system in detail. Thirdly, in order to reduce the power consumption of the system, scaling down technique of the capacitor and operation amplifier was used, and a digital calibration circuit was designed to overcome the comparator offset error.This design works in the Cadence platform, the simulating tool is Cadence Spectre. The simulating results show that, with a power supply of 1.2V, the input voltage range of the ADC is between 0.4V and 0.8V, its resolution is 12 bits and sample rate is 50MHz, the power consumption is about 84mW. The parameters of this pipeline ADC meet the design requirements.Keywords: pipeline ADC, bootstrapped switch, switch capacitor circuit, digital calibration目录摘要 (I)Abstract (II)第一章绪论 (1)1.1课题研究的背景及意义 (1)1.2国内外研究现状 (1)1.3本文主要研究内容和结构安排 (4)第二章流水线ADC的基本原理 (5)2.1模数转换器的基本概念 (5)2.2模数转换器的性能参数 (5)2.3流水线ADC的结构和工作原理 (7)2.4非线性因素及其影响 (8)2.4.1热噪声 (8)2.4.2电荷注入和时钟馈通 (10)2.4.3运放有限开环增益和带宽 (12)2.5数字校正技术 (13)2.6本章小结 (15)第三章流水线ADC单元电路的分析与设计 (16)3.1MOS开关电路 (16)3.2运算放大器 (19)3.2.1增益增强原理 (19)3.2.2主运放和共模反馈电路设计 (21)3.2.3辅助运放设计 (23)3.2.4最终放大器电路验证 (25)3.3比较器 (27)3.4本章小结 (30)第四章模块和系统电路设计与仿真 (31)4.1C LOCK G ENERATOR (31)4.2采样保持电路 (33)4.3 1.5BIT/STAGE ADC (37)4.3.1Sub-ADC (37)4.3.2Sub-DAC (39)4.3.3Gain-stage (41)4.4数字校正电路 (43)4.5本章小结 (45)总结 (46)参考文献 (47)哈尔滨工业大学硕士学位论文原创性声明 (51)哈尔滨工业大学硕士学位论文使用授权书 (51)致谢 (52)第一章 绪 论1.1课题研究的背景及意义现实世界中的物理量大部分是随时间连续变化的量,即大都是模拟量,如光、电、声音、速度等[1]。

带cascode 补偿的两级放大器设计原理图和小信号分析M10M11M9M8M5M4M7M6M13C LV OUTM1M2M3VDDM12CcVB4VB3VB2VB1VSSVipVin小信号等效电路:g m1V inC n1g ds1+g ds5 v n1g m12V n2CcV outC n2g ds7g m7V n1v n2C LR LR n2g m7Cn1=Cgs5+Cgd5+Cgd1, Cn2=Cgs12+Cgd7+Cgd9,RL=rds12//rds13, Rn2= (gm9*rds9*rds11)//(gm7*rds7*rds5) 列写节点方程得:+++++--=-⎧⎪-+++=-⎨⎪-+++=⎩n11577n1C n27out C m1in n1C out C L m12n2n17n2n272m7n1()(1/)(1/)ds ds ds m ds L ds ds n v g g g g C s C s v g v C s g v v C s v C s C s R g v v g v C s g R g v求得直流增益以及零极点:01212m n m L A g R g R = (1) 7121,22m m n Cg g z C C =±(2)15112ds ds m L Cg g p g R C +=-(3)1222m CL C n g C p C C C ≈-+ (4)731(//)m L C n g p C C C ≈-+ (5)2. 带宽以及相位裕度带宽的定义是,增益降低到直流值的2/2时,对应的频率。

那么,带宽约为p1:15112ds ds m L Cg g BW p g R C +==-(6)单位增益带宽的定义是增益为1时对应的频率。

可以证明,单位增益带宽等于带宽与直流增益的乘积。

因此,cm C g p A GBW 110=≈ (7) 相位裕度的定义是,用180减去增益为0dB 时,对应的总相移。

cascode电路密勒补偿-概述说明以及解释1.引言1.1 概述概述cascode电路是一种常用的放大电路结构,广泛应用于射频和高频放大器设计中。

它通过将两个晶体管级联,形成一个高增益的放大器,具有良好的抗干扰能力和线性性能。

cascode电路的基本原理是将一个功率放大晶体管(被驱动晶体管)和一个电压放大晶体管(驱动晶体管)级联。

被驱动晶体管作为负载,增强了整个电路的增益。

驱动晶体管负责控制被驱动晶体管的电流,从而实现对整个电路的放大功能。

然而,cascode电路在实际应用中也存在一些问题,例如频率响应不稳定和阻抗匹配困难等。

为了解决这些问题,密勒补偿技术被引入到cascode电路中。

密勒补偿是指通过添加合适的电容来提高电路的频率响应和稳定性。

在cascode电路中,通过在驱动晶体管的源极和栅极之间添加一个补偿电容,可以有效提高电路的带宽和相位裕度。

这样可以使得cascode电路在高频段保持较好的性能。

总之,cascode电路作为一种常用的放大电路结构,在射频和高频放大器设计中起着重要的作用。

通过以概述介绍cascode电路的基本原理和问题,并引入密勒补偿技术,有助于读者更好地理解cascode电路的应用和优势。

在接下来的章节中,将详细介绍cascode电路的基本原理和密勒补偿方法,以及密勒补偿对cascode电路性能的影响。

1.2文章结构文章结构部分的内容可以参考以下写法:文章结构部分主要是对整篇文章的章节结构进行介绍,方便读者了解全文的组织框架。

本文主要分为引言、正文和结论三个部分。

引言部分首先对文章的主题进行概述,简要介绍了cascode电路的基本原理和密勒补偿方法。

接着,明确了整篇文章的目的,即探讨密勒补偿对cascode电路性能的影响。

正文部分将分为两个主要章节。

首先,会详细介绍cascode电路的基本原理,包括其特点、工作原理和优点等内容。

然后,会重点介绍cascode 电路的密勒补偿方法,详细阐述其原理、实现方式和应用场景等。

共模反馈笔记Return To Innocence咳咳,为了坚持更新,贴一篇以前对全差分运放的共模反馈的小结..关于全差分放大器对于全差分放大器,一般可以得到更大的swing (由于差分信号),同时可以实现对共模干扰、噪声以及偶数阶的非线性的抑制;但其需要有两个匹配的反馈网络,以及共模反馈电路顺便提一下,对于全差分的折叠共源共栅(folded cascode)放大器,需要注意转换速率(正向与负向)对输入对差分对的尾电流源和cascode电流源的考虑非主极点的位置–输入对管的drain节点(注意全差分没有镜像极点的问题..),如果考虑PMOS输入的结构,将会折叠到n管的cascode,从而减小此节点阻抗,提高此非主极点的频率;但是P输入结构亦有其问题,如直流增益和cmfb电路的速度(考虑cmfb控制的为cascode的pmos电流源)关于共模反馈CMFB从反馈环路来看,共模的稳定问题来源于闭环的共模增益:由于输入差分对的尾电流源的local-feedback,通常共模增益较小,导致运放无法控制其输出共模点;通过CMFB共模反馈电路,可以提高共模反馈环路的增益,以稳定共模信号。

设计CMFB需考虑补偿以减小环路的稳定时间(settling time)和提高稳定性。

从性能上,我们希望共模反馈的单位增益带宽足够大,但由于cmfb的环路相较于差模通路可能有更多高频极点,故此在一定的功耗要求下其UGB一般比较难做的高,有书中提到可以将其设计为差模UGB 的1/3一般共模反馈的方法是控制放大器的电流源,这里如果是folded-cascode的结构,可以考虑用cmfb控制cascode的电流源而不是输入差分对的电流源—-因其在共模环路中有较少的节点–>更容易补偿等..(另一种考虑是控制尾电流源可能导致共模增益的问题)另外,对于cmfb控制的尾电流源,常见将尾电流源分为两半,其中之一由cmfb控制,另一半接恒定偏置电流;这种结构的具体分析可见Gray书12.4.2节的内容,简单来说,single-stage的opamp中控制尾电流源的cmfb结构,其UGB 主要为gmt/CL, 其中gmt为尾电流源的跨导,这里拆分尾电流源来减半cmc共模控制的部分,这样UGB减小,即缩减带宽来提升共模反馈环路的相位裕度,当然cmfb的增益相应也减小了;另外恒定偏置部分也可帮助共模电压的初始建立,减小cmfb大的扰动。

全差分折叠共源共栅全差分折叠共源共栅(Fully Differential Folded Cascode)是一种常用的电路结构,在集成电路设计中被广泛应用。

它是一种运算放大器的结构,能够实现高增益、高带宽和高共模抑制比等优势。

全差分折叠共源共栅电路的基本结构由差分对、折叠电流镜、共源共栅级和输出级组成。

差分对由两个共源放大器组成,输入信号被分别接到两个共源放大器的栅极上。

折叠电流镜用来提供稳定的偏置电流,使得整个电路工作在恒流模式下。

共源共栅级由两个共源共栅放大器组成,其中一个作为主放大器,另一个作为负反馈放大器。

输出级由两个共栅放大器组成,输出信号由主放大器的漏极输出。

全差分折叠共源共栅电路具有以下优点。

首先,由于采用了全差分结构,能够有效抵消共模干扰,提高共模抑制比。

其次,折叠电流镜使得电路的输出电流与输入电流保持一致,增强了电路的线性度。

此外,共源共栅级和输出级的级联结构,使得电路具有较高的增益和带宽。

在实际应用中,全差分折叠共源共栅电路常用于模拟电路的设计,如运算放大器、滤波器等。

在运算放大器中,全差分折叠共源共栅电路能够实现高增益和高带宽,满足了信号放大和信号处理的需求。

在滤波器中,电路的高增益和高带宽能够提高滤波器的性能,使其具有更好的滤波效果。

然而,全差分折叠共源共栅电路也存在一些问题。

首先,由于电路结构复杂,布局和布线困难,对工艺要求较高。

其次,由于电路中存在多个级联放大器,噪声会被级联放大,影响电路的信噪比。

此外,电路的共模抑制比和增益对温度和工作电压的变化敏感,需要进行相应的补偿和校准。

全差分折叠共源共栅是一种常用的电路结构,在集成电路设计中具有重要的应用价值。

它通过差分结构、折叠电流镜、共源共栅级和输出级等组成,能够实现高增益、高带宽和高共模抑制比。

然而,电路的复杂结构和对工艺要求较高是需要注意的问题。

在实际应用中,需要根据具体的需求和设计要求,合理选择电路结构和参数,以获得最佳性能和可靠性。

对于全差分放大器,一般可以得到更大的swing (由于差分信号),同时可以实现对共模干扰、噪声以及偶数阶的非线性的抑制;但其需要有两个匹配的反馈网络,以及共模反馈电路顺便提一下,对于全差分的折叠共源共栅(folded cascode)放大器,需要注意转换速率(正向与负向)对输入对差分对的尾电流源和cascode电流源的考虑非主极点的位置–输入对管的drain节点(注意全差分没有镜像极点的问题..),如果考虑PMOS输入的结构,将会折叠到n管的cascode,从而减小此节点阻抗,提高此非主极点的频率;但是P输入结构亦有其问题,如直流增益和cmfb电路的速度(考虑cmfb控制的为cascode的pmos电流源)关于共模反馈CMFB从反馈环路来看,共模的稳定问题来源于闭环的共模增益:由于输入差分对的尾电流源的local-feedback,通常共模增益较小,导致运放无法控制其输出共模点;通过CMFB共模反馈电路,可以提高共模反馈环路的增益,以稳定共模信号。

设计CMFB需考虑补偿以减小环路的稳定时间(settling time)和提高稳定性。

从性能上,我们希望共模反馈的单位增益带宽足够大,但由于cmfb的环路相较于差模通路可能有更多高频极点,故此在一定的功耗要求下其UGB一般比较难做的高,有书中提到可以将其设计为差模UGB 的1/3一般共模反馈的方法是控制放大器的电流源,这里如果是folded-cascode的结构,可以考虑用cmfb控制cascode的电流源而不是输入差分对的电流源—-因其在共模环路中有较少的节点–>更容易补偿等..(另一种考虑是控制尾电流源可能导致共模增益的问题)另外,对于cmfb控制的尾电流源,常见将尾电流源分为两半,其中之一由cmfb控制,另一半接恒定偏置电流;这种结构的具体分析可见Gray书12.4.2节的内容,简单来说,single-stage的opamp中控制尾电流源的cmfb结构,其UGB主要为gmt/CL, 其中gmt为尾电流源的跨导,这里拆分尾电流源来减半cmc共模控制的部分,这样UGB减小,即缩减带宽来提升共模反馈环路的相位裕度,当然cmfb的增益相应也减小了;另外恒定偏置部分也可帮助共模电压的初始建立,减小cmfb大的扰动。

GMID折叠共源共栅运放1. 什么是GMID折叠共源共栅运放?GMID折叠共源共栅运放(Folded Cascode Operational Amplifier with Gain Boosting)是一种常用的运算放大器电路,主要用于信号放大和处理。

它采用了折叠式的电路结构,通过共源共栅(Cascode)连接以增加增益和带宽。

2. GMID折叠共源共栅运放的特点GMID折叠共源共栅运放具有以下几个特点:2.1 高增益GMID折叠共源共栅运放通过使用多级级联的结构,可以实现较高的增益。

其中,折叠式结构可以提供更高的输出阻抗,从而减小负载影响;而利用多级级联可以进一步提高整体增益。

2.2 宽带宽GMID折叠共源共栅运放通过采用Cascode连接方式,可以有效地减小输入和输出电容之间的Miller效应,并提高带宽。

此外,通过合理设计电路参数和引入补偿电容等手段,还可以进一步扩展带宽。

2.3 低功耗GMID折叠共源共栅运放可以通过调整电流源和电阻等参数来实现低功耗设计。

合理选择电流源的大小和类型,可以在满足性能要求的前提下降低功耗。

2.4 适用于集成电路GMID折叠共源共栅运放的结构简单紧凑,适合在集成电路中实现。

它可以利用CMOS工艺来制造,并且可以通过调整晶体管尺寸和工作点等参数来满足具体应用需求。

3. GMID折叠共源共栅运放的基本原理GMID折叠共源共栅运放的基本原理是利用多级级联的结构和Cascode连接方式来增加增益和带宽。

下面将详细介绍其基本原理。

3.1 基本结构GMID折叠共源共栅运放由输入级、中间级和输出级组成。

其中,输入级负责将输入信号转换为差分信号,中间级负责增益放大,输出级负责驱动负载。

3.2 输入级输入级由两个差分对组成,每个差分对包括一个PMOS晶体管和一个NMOS晶体管。

其中,PMOS晶体管的栅极连接到VDD电压,NMOS晶体管的栅极连接到接地。

通过控制差分对的栅极电压,可以实现输入信号的差分放大。

cascode电路密勒补偿全文共四篇示例,供读者参考第一篇示例:Cascode电路是一种常见的放大电路结构,在许多应用中被广泛使用。

Cascode电路由两个二极管管集成在同一个放大电路单元中,并且其效果比普通的单级放大电路要好。

密勒补偿是一种用于改善Cascode电路性能的技术,可以提高增益和减小频率失真。

让我们先了解一下Cascode电路是如何工作的。

在一个普通的单级放大电路中,输出信号与输入信号之间有一个共同的负反馈回路,可以提高增益和稳定性。

由于普通的单级放大电路的输入电阻较低,导致其输入电容也会比较大,从而降低频率响应。

而在Cascode电路中,两个晶体管的输入电容会被分离,一个负责放大,一个负责驱动。

这样就可以减小输入电容,提高频率响应。

Cascode电路还可以提高输入阻抗,降低电压噪声,提高线性度等优点。

Cascode电路也存在一些问题,比如增益较低,频率失真较大等。

为了解决Cascode电路的问题,密勒补偿技术被提出。

密勒补偿是一种用于提高Cascode电路频率响应和增益的技术,可以在一定程度上解决Cascode电路性能不足的问题。

密勒补偿的原理是在Cascode电路上增加一个电容元件,通过调整电容值和电阻值,可以提高Cascode电路的频率响应和增益。

密勒补偿技术的主要作用有以下几个方面:1. 提高频率响应:通过增加反馈电容,可以减小频率失真,提高Cascode电路的频率响应。

2. 提高增益:密勒补偿可以增加Cascode电路的增益,提高整体性能。

3. 改善电阻:通过调整电容和电阻的值,可以改善Cascode电路的输入输出阻抗,提高线性度。

在实际应用中,密勒补偿技术常常用于高频放大电路、射频电路等领域。

通过密勒补偿技术,可以提高Cascode电路的性能,提高整体电路的稳定性和性能。

第二篇示例:Cascode电路是一种常见的电路拓扑结构,它由两个晶体管级联组成,能够提高电路的性能和稳定性。

实现Folded-Cascode放大器快速建立的时钟馈通频率补偿

(英文)

宁宁;于奇;王向展;戴广豪;刘源;杨谟华

【期刊名称】《半导体学报:英文版》

【年(卷),期】2006(27)10

【摘要】基于有源开关电容网络二阶系统最小建立时间( MST)理论和阶跃响应分析,提出了一种用于Folded-Cas-code放大器的频率补偿新方法,即通过MOS电容引入时钟馈通以调整电路阻尼因子η,使其达到MST状态,从而实现快速建立.研究结果表明,补偿后放大器的建立时间缩短了22·7%;当负载电容从0·5变化至2·5pF,其建立时间从3·62ns近似线性地增长到4·46ns ;将采用该补偿方法的放大器应用于可变增益( VGA)系统,当闭环增益变化时,仅需调整MOS电容值仍可实现对应状态下的快速建立.

【总页数】5页(P1737-1741)

【关键词】时钟馈通频率补偿;快速建立;Folded-Cascode放大器;最小建立时间;VGA

【作者】宁宁;于奇;王向展;戴广豪;刘源;杨谟华

【作者单位】电子科技大学微电子与固体电子学院

【正文语种】中文

【中图分类】TN722

【相关文献】

1.一种开关电流电路时钟馈通误差补偿新方法 [J], 蔡良军;王卫东

2.实现折叠共栅共源运放MST的时钟馈通频率补偿方法 [J], 王向展;宁宁;于奇;戴广豪;杨谟华

3.基于晶振频率补偿的高精度数字时钟设计 [J], 姜峰;

4.一种开关电流电路时钟馈通的补偿技术 [J], 李拥平;石寅

5.用于低功耗三级放大器的嵌套式密勒有源电容频率补偿技术(英文) [J], 马海峰;周锋;牛祺;吕昌辉

因版权原因,仅展示原文概要,查看原文内容请购买。

经典全差分运放FullyDifferentialFolded-cascodeOPAMPFully Differential Folded-cascode OPAMP(一)电路架构:1.Design of the biasing circuit:一开始,可以先设计biasing circuit。

偏压电路有许多架构,如果采用wide-swing和constant-g m的合并电路,就必须加入激活电路。

激活电路的设计以不影响偏压电路的正常工作,和低消耗功率为原则。

如Fig.1(b)所示,Q18的W/L是small,因此Q17、Q18所吃的静态电流很小,消耗功率也小。

基本的操作原理在J&M的课本里有详细描述。

但要如何inject激活电路的电流到偏压网络呢?让我们来看看Fig.1(a),注意其中有两个loop和其对称性,只要仔细观察,这两个loop都会形成正回授。

当你用NMOS技术设计时,可以将激活电流inject到标示点X、Y,以产生PMOS(Q14、Q9)的drain电流。

同理,你也可以用PMOS设计激活电路,当然,电流的injecting point就不同了。

Rb值的设计,必须看你要偏压网络流多少电流来计算。

算完后可以做仿真,以得到最佳值,使偏压电流很match。

Fig.1(a)Fig.1(b)2.Design of the main amplifier:由于这个amplifier是one stage的设计,gain会不够,所以必须使用cascode的架构。

又为了增加output swing,故再把PMOS 给折叠下来,形成folded-cascode,最后输出是double-ended output。

先不管fully-differential架构的优点与应用,我们来看看整个架构的内部行为。

首先必须了解电路的大信号行为,最重要的为slewing。

如Fig.2所示,其中没加Q11和Q12。

考虑一个pulse加在Vin-与Vin+之间,当pulse由low 到high,Q1 turn on & Q2 turn off,所以流过Q4的drain电流全部流到Q5,并对node X上的电容充电,Vout-的dc电压会缓缓上升,此即称为positive slewing,slew rate 如下:SR=另一方面,流经Q10和Q9的电流会discharge在node Y上的电荷,这个电流由CMFB所控制。

轨对轨运放cascode补偿

轨对轨运放(Rail-to-Rail Operational Amplifier,RR-OPAMP)是一种运放,其输入和输出的电压范围可以覆盖整个供电电压范围。

传统的运放,输入和输出电压范围受限于供电电压范围,因此在输入和输出靠近供电电压边界时,会造成截断失真。

轨对轨运放采用了一种特殊的电路结构,使得其输入和输出能够达到供电电压边界。

它通常使用增加电源轨极的技术,将两个差分输入级放置在输入信号的正负两侧,以确保输入信号可以驱动差分放大器。

而cascode补偿则是一种用于减小RR-OPAMP中的晶体管工作点漂移和增加增益带宽积的技术。

它通过在RR-OPAMP的输入级和差分对输出级之间插入一个额外的cascode级,将cascode晶体管的基极电压稳定在一个固定的值上。

这样可以大大减小晶体管工作点电流对工作状态和增益的影响,并提高运放的线性度和带宽。

总的来说,轨对轨运放结合cascode补偿技术,能够提供更大的输入和输出电压范围,并减小非线性失真和频率响应损失。

这使得它在需要处理接近供电边界的信号时,具有优势。

折叠共源共栅放大器的零极点分析折叠共源共栅放大器(Folding Cascode Amplifier)是一种常用的放大电路,被广泛应用于射频(RF)电路和通信系统中。

该放大器由共源级和共栅级组成,具有高增益、高输入阻抗和低输出阻抗等特点,适用于宽频带和高频率应用。

在进行零极点分析之前,首先需要明确折叠共源共栅放大器的电路结构和工作原理。

折叠共源共栅放大器的原理图如下:[Image]其中,M1和M2为NMOS管,构成分配级(Source Follower);M3和M4为PMOS管,构成共栅级(Cascode Stage)。

Vin为输入信号,Vout为输出信号。

在理想情况下,输入信号通过分配级放大,并由共栅级输出。

对于折叠共源共栅放大器,可以通过以下步骤进行零极点分析:1.首先,我们需要确定电路中的输入功率和输出功率。

输入功率Pin = VoltageIn × CurrentIn输出功率Pout = VoltageOut × CurrentOut2.接下来,我们可以计算输入阻抗和输出阻抗。

输入阻抗Zin = VoltageIn / CurrentIn输出阻抗Zout = VoltageOut / CurrentOut3.然后,我们可以使用DC分析来确定电路中的直流偏置电压和直流电流。

DC偏置点是电路中的稳定工作点,通过设置电源电压和电阻值来确定。

4.在得到直流偏置电压和电流后,我们可以使用AC分析来确定电路的增益和带宽。

AC分析是一种线性分析方法,可以对电路进行频率响应分析。

5.在AC分析中,可以使用小信号模型来计算电路的增益和带宽。

小信号模型是对电路进行线性化处理,将非线性元件(如晶体管)近似为线性元件(如电流源)。

6.在小信号模型中,可以计算电路的输入导纳和输出导纳。

输入导纳Yin = CurrentIn / VoltageIn输出导纳Yout = CurrentOut / VoltageOut7.最后,我们可以使用输入和输出导纳来计算折叠共源共栅放大器的零极点。

补偿网络对Cascode结构放大器线性度的改善张晓东;王钟;高怀;程建春;吴浩东【期刊名称】《南京大学学报:自然科学版》【年(卷),期】2012(48)5【摘要】宽带功率放大器是现代多频段无线通信系统中的关键器件.Cascode结构由于其良好的带宽特性以及输出阻抗特性,被广泛应用在宽带功率放大器的设计当中.带宽和线性是宽带功率放大器的重要指标.通常用RLC补偿网络可以增加Cascode结构功率放大器的带宽.本文提出通过选择合适的RLC补偿网络电路参数,使得晶体管处于良好的工作状态,可以实现在增加Cascode放大器带宽的同时,改善其线性度.从电路原理上分析了——补偿网络改善功率放大器非线性的原因,并利用Volterra级数方法计算了三阶交调截止点(IP3),证实了IP3可以改善3dB±.采用2μm InGaP/GaAs HBT半导体工艺流片后,测试结果表明,其3dB工作宽带扩展了1GHz(带宽从1.5GHz扩展到2.5GHz),IP3改善了3dB,与计算结果非常一致.【总页数】6页(P671-676)【关键词】补偿网络;Cascode放大器;线性度;Volterra;Series【作者】张晓东;王钟;高怀;程建春;吴浩东【作者单位】近代声学教育部重点实验室,南京大学声学研究所;苏州市射频功率器件及电路工程技术研究中心【正文语种】中文【中图分类】TN948.53【相关文献】1.基于Darlington Cascode结构的SiGe异质结双极晶体管UWB低噪声放大器的设计 [J], 丁春宝;郭振杰;张万荣;金冬月;谢红云;陈亮;沈佩;张东晖;刘波宇;周永强2.基于CASCODE结构的射频功率放大器系统设计 [J], 刘阳;孙亮;张雪鹏;沙鸥3.基于cascode结构的Ka频段CMOS功率放大器设计 [J], 甄建宇;陈娜4.基于cascode结构的Ka频段CMOS功率放大器设计 [J], 甄建宇;陈娜5.实现Folded-Cascode放大器快速建立的时钟馈通频率补偿(英文) [J], 宁宁;于奇;王向展;戴广豪;刘源;杨谟华因版权原因,仅展示原文概要,查看原文内容请购买。